Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

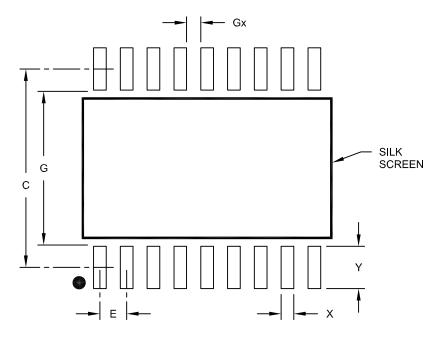

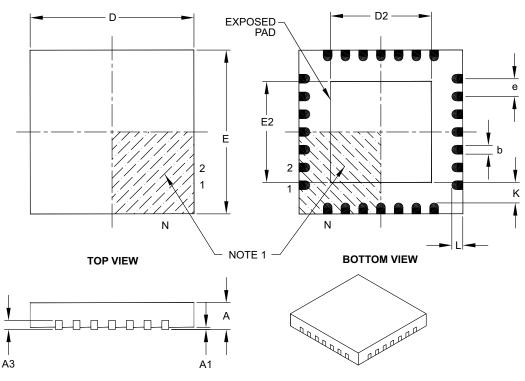

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402-h-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

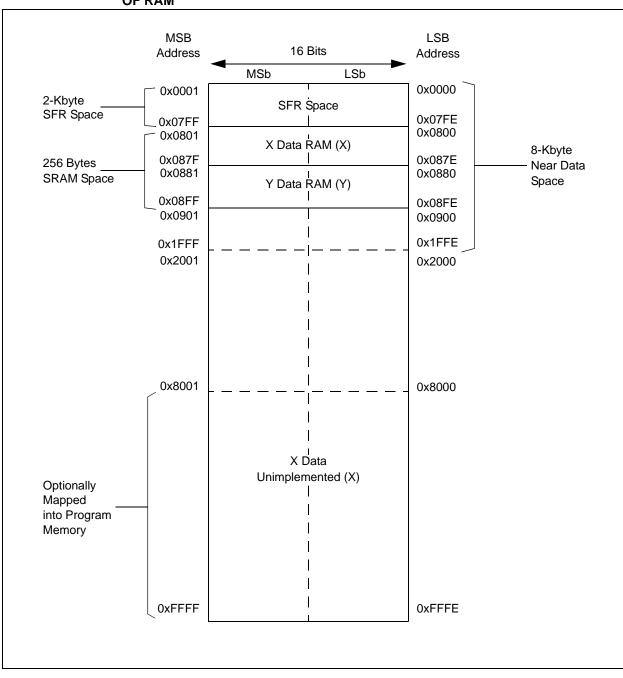

#### FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJ06GS101/102 DEVICES WITH 256 BYTES OF RAM

## TABLE 4-27: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                 | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6          | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|------------------------|--------|----------|----------|----------|----------|----------|-------------|----------------|---------|-----------|----------|----------|----------|----------|---------------|

| ADCON        | 0300        | ADON   | —                      | ADSIDL | SLOWCLK  | —        | GSWTRG   | —        | FORM     | EIE         | ORDER          | SEQSAMP | ASYNCSAMP | —        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _      | -                      | —      | _        | _        |          | _        | —        | _           | _              | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _      | -                      | —      | _        | _        |          | _        | —        | _           | P6RDY          | _       | _         | _        | P2RDY    | P1RDY    | PORDY    | 0000          |

| ADBASE       | 0308        |        | ADBASE<15:1>           |        |          |          |          |          |          |             |                |         | —         | 0000     |          |          |          |               |

| ADCPC0       | 030A        | IRQEN1 | PEND1                  | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0          | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | _      | -                      | —      | _        | _        |          | _        | —        | IRQEN2      | PEND2          | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCPC3       | 0310        | _      |                        | —      | _        | _        | _        | —        | —        | IRQEN6      | PEND6          | SWTRG6  | TRGSRC64  | TRGSRC63 | TRGSRC62 | TRGSRC61 | TRGSRC60 | 0000          |

| ADCBUF0      | 0320        |        |                        |        |          |          |          |          | ADC E    | Data Buffer | 0              |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |        |                        |        |          |          |          |          | ADC E    | Data Buffer | <sup>.</sup> 1 |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |        |                        |        |          |          |          |          | ADC E    | Data Buffer | 2              |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |        |                        |        |          |          |          |          | ADC E    | Data Buffer | 3              |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |        |                        |        |          |          |          |          | ADC E    | Data Buffer | 4              |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |        | ADC Data Buffer 5 xxx  |        |          |          |          |          |          |             |                | xxxx    |           |          |          |          |          |               |

| ADCBUF12     | 0338        |        | ADC Data Buffer 12 xxx |        |          |          |          |          |          |             | xxxx           |         |           |          |          |          |          |               |

| ADCBUF13     | 033A        |        | ADC Data Buffer13 xxxx |        |          |          |          |          |          |             |                | xxxx    |           |          |          |          |          |               |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

## TABLE 4-28: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ16GS402/404 DEVICES ONLY

|              | -                                                                                                  |                                           |                        |        | -        |          |          |          |          |            |       | -       |           |          |          |          |          |               |

|--------------|----------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------|--------|----------|----------|----------|----------|----------|------------|-------|---------|-----------|----------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr                                                                                        | Bit 15                                    | Bit 14                 | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7      | Bit 6 | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADCON        | 0300                                                                                               | ADON                                      | —                      | ADSIDL | SLOWCLK  | _        | GSWTRG   | _        | FORM     | EIE        | ORDER | SEQSAMP | ASYNCSAMP | -        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302                                                                                               | PCFG7 PCFG6 PCFG5 PCFG4 PCFG3 PCFG2 PCFG1 |                        |        |          |          |          |          | PCFG0    | 0000       |       |         |           |          |          |          |          |               |

| ADSTAT       | 0306                                                                                               | _                                         | _                      | _      | _        | —        | _        | _        | _        | _          | _     | _       | _         | P3RDY    | P2RDY    | P1RDY    | P0RDY    | 0000          |

| ADBASE       | 0308                                                                                               | ADBASE<15:1> —                            |                        |        |          |          |          |          |          |            | —     | 0000    |           |          |          |          |          |               |

| ADCPC0       | 030A                                                                                               | IRQEN1                                    | PEND1                  | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0     | PEND0 | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C                                                                                               | IRQEN3                                    | PEND3                  | SWTRG3 | TRGSRC34 | TRGSRC33 | TRGSRC32 | TRGSRC31 | TRGSRC30 | IRQEN2     | PEND2 | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCBUF0      | 0320                                                                                               |                                           |                        |        |          |          |          |          | ADC D    | ata Buffer | 0     |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322                                                                                               |                                           |                        |        |          |          |          |          | ADC D    | ata Buffer | 1     |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324                                                                                               |                                           |                        |        |          |          |          |          | ADC D    | ata Buffer | 2     |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326                                                                                               |                                           |                        |        |          |          |          |          | ADC D    | ata Buffer | 3     |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328                                                                                               |                                           |                        |        |          |          |          |          | ADC D    | ata Buffer | 4     |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A                                                                                               |                                           |                        |        |          |          |          |          | ADC D    | ata Buffer | 5     |         |           |          |          |          |          | xxxx          |

| ADCBUF6      | 032C                                                                                               |                                           | ADC Data Buffer 6 xxxx |        |          |          |          |          |          |            |       | xxxx    |           |          |          |          |          |               |

| ADCBUF7      | 032E                                                                                               | ADC Data Buffer 7 xxxx                    |                        |        |          |          |          |          |          |            | xxxx  |         |           |          |          |          |          |               |

| Legend:      | x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                                           |                        |        |          |          |          |          |          |            |       |         |           |          |          |          |          |               |

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

The address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

## 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

## 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM bits (W register selection) in the MODCON register are any value other than 15 (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed         |

|-------|--------------------------------------------|

|       | Addressing should not be enabled           |

|       | together. If an application attempts to do |

|       | so, Bit-Reversed Addressing will assume    |

|       | priority when active for the X WAGU and X  |

|       | WAGU; Modulo Addressing will be dis-       |

|       | abled. However, Modulo Addressing will     |

|       | continue to function in the X RAGU.        |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx, and three other lines for

power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the Digital Signal Controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data, either in blocks or 'rows' of 64 instructions (192 bytes) at a time, or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

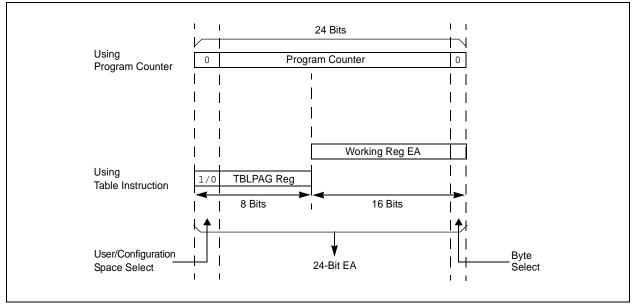

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

© 2008-2014 Microchip Technology Inc.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| <br> | -             |                            |                                         | _ |

|------|---------------|----------------------------|-----------------------------------------|---|

| ;    | Set up NVMCO  | N for row programming open | rations                                 |   |

|      | MOV           | #0x4001, W0                | ;                                       |   |

|      | MOV           | W0, NVMCON                 | ; Initialize NVMCON                     |   |

| ;    | Set up a poir | nter to the first program  | memory location to be written           |   |

| ;    | program memo: | ry selected, and writes en | nabled                                  |   |

|      | MOV           | #0x0000, W0                | ;                                       |   |

|      | MOV           | W0, TBLPAG                 | ; Initialize PM Page Boundary SFR       |   |

|      | MOV           | #0x6000, W0                | ; An example program memory address     |   |

| ;    | Perform the   | TBLWT instructions to writ | te the latches                          |   |

| ;    | 0th_program_v | word                       |                                         |   |

|      | MOV           | #LOW_WORD_0, W2            | i                                       |   |

|      | MOV           | #HIGH_BYTE_0, W3           | ;                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

| ;    | lst_program_  | word                       |                                         |   |

|      | MOV           | #LOW_WORD_1, W2            | ;                                       |   |

|      | MOV           | #HIGH_BYTE_1, W3           | i                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

| ;    | 2nd_program   | _word                      |                                         |   |

|      | MOV           | #LOW_WORD_2, W2            | i                                       |   |

|      | MOV           | #HIGH_BYTE_2, W3           | i                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

|      | •             |                            |                                         |   |

|      | •             |                            |                                         |   |

|      | •             |                            |                                         |   |

| ;    | 63rd_program  |                            |                                         |   |

|      |               | #LOW_WORD_31, W2           | ;                                       |   |

|      |               | #HIGH_BYTE_31, W3          | ;                                       |   |

|      |               | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

|      |               |                            |                                         |   |

EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | <pre>; Block all interrupts with priority &lt;7 ; for next 5 instructions</pre> |

|------|-------------|---------------------------------------------------------------------------------|

| MOV  | #0x55, W0   |                                                                                 |

| MOV  | W0, NVMKEY  | ; Write the 55 key                                                              |

| MOV  | #0xAA, W1   | ;                                                                               |

| MOV  | W1, NVMKEY  | ; Write the AA key                                                              |

| BSET | NVMCON, #WR | ; Start the erase sequence                                                      |

| NOP  |             | ; Insert two NOPs after the                                                     |

| NOP  |             | ; erase command is asserted                                                     |

|      |             |                                                                                 |

## 7.3 Interrupt Control and Status Registers

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices implement 27 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFSx

- IECx

- IPCx

- INTTREG

#### 7.3.1 INTCON1 AND INTCON2

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

#### 7.3.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.3.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

## 7.3.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

## 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit is found in IEC0<0> and the INT0IP bits are found in the first position of IPC0 (IPC0<2:0>).

## 7.3.6 STATUS/CONTROL REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality.

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user can change the current CPU priority level by writing to the IPL bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-35 in the following pages.

| R/W-0        | R-0                                                                                            | U-0                                                          | U-0      | U-0              | U-0             | U-0                | U-0    |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------|------------------|-----------------|--------------------|--------|--|--|--|--|--|

| ALTIVT       | DISI                                                                                           | —                                                            |          | _                | —               |                    |        |  |  |  |  |  |

| oit 15       |                                                                                                |                                                              |          |                  |                 |                    | bit 8  |  |  |  |  |  |

|              |                                                                                                |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

| U-0          | U-0                                                                                            | U-0                                                          | U-0      | U-0              | R/W-0           | R/W-0              | R/W-0  |  |  |  |  |  |

| —            |                                                                                                |                                                              | _        | —                | INT2EP          | INT1EP             | INT0EP |  |  |  |  |  |

| bit 7        |                                                                                                |                                                              |          |                  |                 |                    | bit C  |  |  |  |  |  |

|              |                                                                                                |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

| Legend:      |                                                                                                |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

| R = Readab   |                                                                                                | W = Writable I                                               | oit      | •                | mented bit, rea |                    |        |  |  |  |  |  |

| -n = Value a | t POR                                                                                          | '1' = Bit is set                                             |          | '0' = Bit is cle | eared           | x = Bit is unknown |        |  |  |  |  |  |

|              |                                                                                                |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

| bit 15       |                                                                                                | ALTIVT: Enable Alternate Interrupt Vector Table bit          |          |                  |                 |                    |        |  |  |  |  |  |

|              | 1 = Use alternate vector table<br>0 = Use standard (default) vector table                      |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

| bit 14       |                                                                                                | Instruction Status                                           |          |                  |                 |                    |        |  |  |  |  |  |

| DIT 14       |                                                                                                |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

|              | 1 = DISI instruction is active<br>0 = DISI instruction is not active                           |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

| bit 13-3     |                                                                                                | ented: Read as '0                                            |          |                  |                 |                    |        |  |  |  |  |  |

| bit 2        | -                                                                                              |                                                              |          | t Polaritv Selec | t bit           |                    |        |  |  |  |  |  |

|              | INT2EP: External Interrupt 2 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

|              | 0 = Interrupt on positive edge                                                                 |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

| bit 1        | INT1EP: Ex                                                                                     | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit |          |                  |                 |                    |        |  |  |  |  |  |

|              | 1 = Interrupt on negative edge                                                                 |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

|              | 0 = Interrupt on positive edge                                                                 |                                                              |          |                  |                 |                    |        |  |  |  |  |  |

| bit 0        |                                                                                                | ternal Interrupt 0                                           | •        | t Polarity Selec | t bit           |                    |        |  |  |  |  |  |

|              | •                                                                                              | t on negative edg                                            |          |                  |                 |                    |        |  |  |  |  |  |

|              | 0 – Interrun                                                                                   | t on positive edge                                           | <b>`</b> |                  |                 |                    |        |  |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0           | U-0                                                   | R/W-0                                   | U-0             | U-0               | U-0              | U-0             | U-0     |  |  |  |  |

|---------------|-------------------------------------------------------|-----------------------------------------|-----------------|-------------------|------------------|-----------------|---------|--|--|--|--|

| _             | _                                                     | INT2IE                                  | _               | _                 | _                | _               | _       |  |  |  |  |

| bit 15        |                                                       | 1                                       |                 |                   |                  |                 | bit 8   |  |  |  |  |

|               |                                                       |                                         |                 |                   |                  |                 |         |  |  |  |  |

| U-0           | U-0                                                   | U-0                                     | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

| —             | _                                                     |                                         | INT1IE          | CNIE              | AC1IE            | MI2C1IE         | SI2C1IE |  |  |  |  |

| bit 7         | •                                                     |                                         |                 | 1 1               |                  |                 | bit C   |  |  |  |  |

|               |                                                       |                                         |                 |                   |                  |                 |         |  |  |  |  |

| Legend:       |                                                       |                                         |                 |                   |                  |                 |         |  |  |  |  |

| R = Readabl   | e bit                                                 | W = Writable I                          | oit             | U = Unimplem      | nented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at | POR                                                   | '1' = Bit is set                        |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |

|               |                                                       |                                         |                 |                   |                  |                 |         |  |  |  |  |

| bit 15-14     | Unimplemen                                            | ted: Read as 'd                         | )'              |                   |                  |                 |         |  |  |  |  |

| bit 13        | INT2IE: Exter                                         | INT2IE: External Interrupt 2 Enable bit |                 |                   |                  |                 |         |  |  |  |  |

|               |                                                       | equest enabled                          |                 |                   |                  |                 |         |  |  |  |  |

|               | -                                                     | equest not ena                          |                 |                   |                  |                 |         |  |  |  |  |

| bit 12-5      | •                                                     | ted: Read as '0                         |                 |                   |                  |                 |         |  |  |  |  |

| bit 4         |                                                       | nal Interrupt 1                         |                 |                   |                  |                 |         |  |  |  |  |

|               |                                                       | equest enableo                          |                 |                   |                  |                 |         |  |  |  |  |

| bit 3         | •                                                     | change Notifica                         |                 | Enable bit        |                  |                 |         |  |  |  |  |

| DIT 3         | -                                                     | request enabled                         | •               |                   |                  |                 |         |  |  |  |  |

|               |                                                       | equest not ena                          |                 |                   |                  |                 |         |  |  |  |  |

| bit 2         | AC1IE: Analo                                          | g Comparator                            | 1 Interrupt En  | able bit          |                  |                 |         |  |  |  |  |

|               | 1 = Interrupt r                                       | equest enabled                          | k               |                   |                  |                 |         |  |  |  |  |

|               | 0 = Interrupt r                                       | equest not ena                          | bled            |                   |                  |                 |         |  |  |  |  |

| bit 1         | MI2C1IE: I2C                                          | 1 Master Event                          | ts Interrupt Er | nable bit         |                  |                 |         |  |  |  |  |

|               | 1 = Interrupt request enabled                         |                                         |                 |                   |                  |                 |         |  |  |  |  |

|               | -                                                     | equest not ena                          |                 |                   |                  |                 |         |  |  |  |  |

|               | bit 0 SI2C1IE: I2C1 Slave Events Interrupt Enable bit |                                         |                 |                   |                  |                 |         |  |  |  |  |

| bit 0         |                                                       | 1 Slave Events<br>equest enabled        |                 |                   |                  |                 |         |  |  |  |  |

| R/W-0         | U-0                                                                                | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------|----------------------------------------|---------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|--|

| ROON          | _                                                                                  | ROSSLP                                 | ROSEL         | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |  |  |

| bit 15        |                                                                                    |                                        |               |                       |                       |                       | bit 8                 |  |  |  |  |  |

|               |                                                                                    |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

| U-0           | U-0                                                                                | U-0                                    | U-0           | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |  |  |

|               | _                                                                                  | —                                      |               | —                     | —                     | —                     | —                     |  |  |  |  |  |

| bit 7         |                                                                                    |                                        |               |                       |                       |                       | bit 0                 |  |  |  |  |  |

| Legend:       |                                                                                    |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

| R = Readabl   | e bit                                                                              | W = Writable                           | bit           | U = Unimplen          | nented bit, read      | l as '0'              |                       |  |  |  |  |  |

| -n = Value at | POR                                                                                | '1' = Bit is set                       |               | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |  |  |  |

|               |                                                                                    |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

| bit 15        | ROON: Refer                                                                        | ence Oscillator                        | r Output Enab | ole bit               |                       |                       |                       |  |  |  |  |  |

|               | 1 = Reference oscillator output is enabled on the REFCLK0 pin(2)                   |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               |                                                                                    | e oscillator outp                      |               | ł                     |                       |                       |                       |  |  |  |  |  |

| bit 14        | Unimplemented: Read as '0'                                                         |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

| bit 13        |                                                                                    | ference Oscilla                        |               | -                     |                       |                       |                       |  |  |  |  |  |

|               |                                                                                    | e oscillator outp<br>e oscillator outp |               |                       |                       |                       |                       |  |  |  |  |  |

| bit 12        | ROSEL: Reference Oscillator Source Select bit                                      |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 1 = Oscillator crystal is used as the reference clock                              |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | •                                                                                  | lock is used as                        |               |                       |                       |                       |                       |  |  |  |  |  |

| bit 11-8      | RODIV<3:0>: Reference Oscillator Divider bits <sup>(1)</sup>                       |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 1111 = Reference clock divided by 32,768                                           |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 1110 = Reference clock divided by 16,384                                           |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 1101 = Reference clock divided by 8,192                                            |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 1100 = Reference clock divided by 4,096                                            |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 1011 = Reference clock divided by 2,048<br>1010 = Reference clock divided by 1,024 |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 1001 = Reference clock divided by 512                                              |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               |                                                                                    | ence clock divi                        | -             |                       |                       |                       |                       |  |  |  |  |  |

|               | 0111 = Refer                                                                       | ence clock divi                        | ded by 128    |                       |                       |                       |                       |  |  |  |  |  |

|               | 0110 = Reference clock divided by 64                                               |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 0101 = Reference clock divided by 32                                               |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 0100 = Reference clock divided by 16                                               |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 0011 = Reference clock divided by 8<br>0010 = Reference clock divided by 4         |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               |                                                                                    | ence clock divi<br>ence clock divi     | -             |                       |                       |                       |                       |  |  |  |  |  |

|               | 000T = Velet                                                                       |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

|               | 0000 = Refer                                                                       |                                        |               |                       |                       |                       |                       |  |  |  |  |  |

### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

Note 1: The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

2: This pin is remappable. Refer to Section 10.6 "Peripheral Pin Select" for more information.

## 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices can manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

## 9.1 Clock Frequency and Clock Switching

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

## 9.2 Instruction-Based Power-Saving Modes

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

## 9.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes the items such as the Input Change Notification on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

## EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

|                             | • = • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                           |                                          |     |                                         |                 |          |       |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----------------------------------------|-----------------|----------|-------|--|--|

| U-0                         | U-0                                                                                                                                                                                                                                               | U-0                                      | U-0 | U-0                                     | U-0             | R/W-0    | R/W-0 |  |  |

| —                           | —                                                                                                                                                                                                                                                 | —                                        | —   | —                                       | _               | IC2MD    | IC1MD |  |  |

| it 15                       |                                                                                                                                                                                                                                                   |                                          |     |                                         |                 |          | bit 8 |  |  |

| U-0                         | U-0                                                                                                                                                                                                                                               | U-0                                      | U-0 | U-0                                     | U-0             | R/W-0    | R/W-0 |  |  |

| _                           | —                                                                                                                                                                                                                                                 | —                                        |     | _                                       |                 | OC2MD    | OC1MD |  |  |

| oit 7                       | ·                                                                                                                                                                                                                                                 |                                          |     |                                         |                 |          | bit C |  |  |

| _egend:                     |                                                                                                                                                                                                                                                   |                                          |     |                                         |                 |          |       |  |  |

| R = Readabl                 | e bit                                                                                                                                                                                                                                             | W = Writable                             | bit | U = Unimplem                            | nented bit, rea | d as '0' |       |  |  |

| -n = Value at               | POR                                                                                                                                                                                                                                               | '1' = Bit is set                         |     | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |  |

| bit 15-10<br>bit 9<br>bit 8 | Unimplemented: Read as '0'<br>IC2MD: Input Capture 2 Module Disable bit<br>1 = Input Capture 2 module is disabled<br>0 = Input Capture 2 module is enabled<br>IC1MD: Input Capture 1 Module Disable bit<br>1 = Input Capture 1 module is disabled |                                          |     |                                         |                 |          |       |  |  |

| bit 7-2                     |                                                                                                                                                                                                                                                   | ture 1 module<br>t <b>ed:</b> Read as 'd |     |                                         |                 |          |       |  |  |

| bit 1                       | OC2MD: Output Compare 2 Module Disable bit<br>1 = Output Compare 2 module is disabled<br>0 = Output Compare 2 module is enabled                                                                                                                   |                                          |     |                                         |                 |          |       |  |  |

| bit 0                       | OC1MD: Output Compare 1 Module Disable bit<br>1 = Output Compare 1 module is disabled<br>0 = Output Compare 1 module is enabled                                                                                                                   |                                          |     |                                         |                 |          |       |  |  |

## REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

## 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70193) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

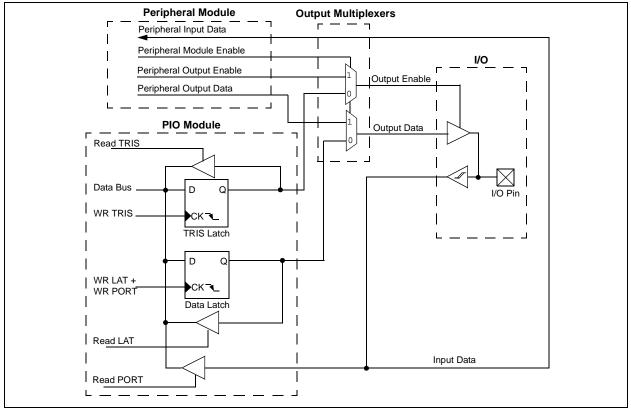

## 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

## FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

© 2008-2014 Microchip Technology Inc.

| Field | Description                                                                                                                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier Working register pair for Square instructions $\in$ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                     |

| Wm*Wn | Multiplicand and Multiplier Working register pair for DSP instructions ∈ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                            |

| Wn    | One of 16 Working registers $\in$ {W0W15}                                                                                                                                                                                                                             |

| Wnd   | One of 16 Destination Working registers ∈ {W0W15}                                                                                                                                                                                                                     |

| Wns   | One of 16 Source Working registers ∈ {W0W15}                                                                                                                                                                                                                          |

| WREG  | W0 (Working register used in file register instructions)                                                                                                                                                                                                              |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                          |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                       |

| Wx    | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                 |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                              |

| Wy    | Y Data Space Prefetch Address register for DSP instructions<br>$\in \{[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2, [W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2, [W11 + W12], none \}$ |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                              |

## TABLE 22-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| TABLE 22-2:        |                      | INSTRUCTION SET OVERVIEW (CONTINUED) |                                     |                                        |   |                |                          |  |  |  |  |

|--------------------|----------------------|--------------------------------------|-------------------------------------|----------------------------------------|---|----------------|--------------------------|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                      | Assembly Syntax                     | Description                            |   | # of<br>Cycles | Status Flags<br>Affected |  |  |  |  |

| 29                 | DIV                  | DIV.S                                | Wm, Wn                              | Signed 16/16-bit Integer Divide        | 1 | 18             | N,Z,C,OV                 |  |  |  |  |

|                    |                      | DIV.SD                               | Wm, Wn                              | Signed 32/16-bit Integer Divide        | 1 | 18             | N,Z,C,OV                 |  |  |  |  |

|                    |                      | DIV.U                                | Wm,Wn                               | Unsigned 16/16-bit Integer Divide      | 1 | 18             | N,Z,C,OV                 |  |  |  |  |

|                    |                      | DIV.UD                               | Wm,Wn                               | Unsigned 32/16-bit Integer Divide      | 1 | 18             | N,Z,C,OV                 |  |  |  |  |

| 30                 | DIVF                 | DIVF                                 | Wm,Wn                               | Signed 16/16-bit Fractional Divide     | 1 | 18             | N,Z,C,OV                 |  |  |  |  |

| 31                 | DO                   | DO                                   | <pre>#lit14,Expr</pre>              | Do code to PC + Expr, lit14 + 1 times  | 2 | 2              | None                     |  |  |  |  |

|                    |                      | DO                                   | Wn,Expr                             | Do code to PC + Expr, (Wn) + 1 times   | 2 | 2              | None                     |  |  |  |  |

| 32                 | ED                   | ED                                   | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance (no accumulate)     | 1 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

| 33                 | EDAC                 | EDAC                                 | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance                     | 1 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

| 34                 | EXCH                 | EXCH                                 | Wns,Wnd                             | Swap Wns with Wnd                      | 1 | 1              | None                     |  |  |  |  |

| 35                 | FBCL                 | FBCL                                 | Ws,Wnd                              | Find Bit Change from Left (MSb) Side   | 1 | 1              | С                        |  |  |  |  |

| 36                 | FF1L                 | FF1L                                 | Ws,Wnd                              | Find First One from Left (MSb) Side    | 1 | 1              | С                        |  |  |  |  |

| 37                 | FF1R                 | FF1R                                 | Ws,Wnd                              | Find First One from Right (LSb) Side   | 1 | 1              | С                        |  |  |  |  |

| 38                 | GOTO                 | GOTO                                 | Expr                                | Go to Address                          | 2 | 2              | None                     |  |  |  |  |

|                    |                      | GOTO                                 | Wn                                  | Go to Indirect                         | 1 | 2              | None                     |  |  |  |  |

| 39                 | INC                  | INC                                  | f                                   | f = f + 1                              | 1 | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC                                  | f,WREG                              | WREG = f + 1                           | 1 | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC                                  | Ws,Wd                               | Wd = Ws + 1                            | 1 | 1              | C,DC,N,OV,Z              |  |  |  |  |

| 40                 | INC2                 | INC2                                 | f                                   | f = f + 2                              | 1 | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC2                                 | f,WREG                              | WREG = f + 2                           | 1 | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC2                                 | Ws,Wd                               | Wd = Ws + 2                            | 1 | 1              | C,DC,N,OV,Z              |  |  |  |  |

| 41                 | IOR                  | IOR                                  | f                                   | f = f .IOR. WREG                       | 1 | 1              | N,Z                      |  |  |  |  |

|                    | -                    | IOR                                  | f,WREG                              | WREG = f .IOR. WREG                    | 1 | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | #lit10,Wn                           | Wd = lit10 .IOR. Wd                    | 1 | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | Wb,Ws,Wd                            | Wd = Wb .IOR. Ws                       | 1 | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | Wb,#lit5,Wd                         | Wd = Wb .IOR. lit5                     | 1 | 1              | N,Z                      |  |  |  |  |

| 42                 | LAC                  | LAC                                  | Wso,#Slit4,Acc                      | Load Accumulator                       | 1 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

| 43                 | LNK                  | LNK                                  | #lit14                              | Link Frame Pointer                     | 1 | 1              | None                     |  |  |  |  |

| 44                 | LSR                  | LSR                                  | f                                   | f = Logical Right Shift f              | 1 | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | f,WREG                              | WREG = Logical Right Shift f           | 1 | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | Ws,Wd                               | Wd = Logical Right Shift Ws            | 1 | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | Wb,Wns,Wnd                          | Wnd = Logical Right Shift Wb by Wns    | 1 | 1              | N,Z                      |  |  |  |  |

|                    |                      | LSR                                  | Wb,#lit5,Wnd                        | Wnd = Logical Right Shift Wb by lit5   | 1 | 1              | N,Z                      |  |  |  |  |

| 45                 | MAC                  | MAC                                  | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Accumulate                | 1 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

|                    |                      | MAC                                  | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd             | Square and Accumulate                  | 1 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |