Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "*dsPIC33F/PIC24H Family Reference Manual*", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 family of 16-bit Digital Signal Controllers (DSC) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")VCAP

- (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP<sup>™</sup> Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu$ F to  $0.001 \ \mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu$ F in parallel with  $0.001 \ \mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

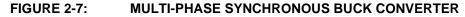

#### FIGURE 2-6: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

#### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/ 16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (for example, ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- Signed or Unsigned DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation | ACC<br>Write Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value that is sign-extended to 40 bits. Integer data is inherently represented as a signed 2's complement value, where the Most Significant bit (MSb) is defined as a sign bit. The range of an N-bit 2's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ .

- For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0.

- For a 32-bit integer, the data range is

-2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a 2's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit 2's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product that has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiply operations.

The MUL instruction can be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

# 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled using the barrel shifter prior to accumulation.

# 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side, and either true or complement data into the other input.

- In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented).

- In the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented.

The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS Register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits, 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block that controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described previously and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS Register bits support saturation and overflow:

- OA: ACCA overflowed into guard bits

- · OB: ACCB overflowed into guard bits

- SA: ACCA saturated (bit 31 overflow and saturation) or

~

or

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation)

• SB: ACCB saturated (bit 31 overflow and saturation)

ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- OAB: Logical OR of OA and OB

- SAB: Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register are set (refer to **Section 7.0 "Interrupt Controller"**). This allows the user application to take immediate action, for example, to correct system gain.

#### TABLE 4-22: I2C1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8                        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|---------|--------|---------|--------|--------|--------|-----------|------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| I2C1RCV      | 0200        | —       | _      |         | _      | _      | —      | —         | - I2C1 Receive Register      |       |       |       |       |       | 0000  |       |       |               |

| I2C1TRN      | 0202        | _       |        | _       | _      |        | _      | _         | I2C1 Transmit Register       |       |       |       |       |       | OOFF  |       |       |               |

| I2C1BRG      | 0204        | _       |        | _       | _      |        | _      | _         | Baud Rate Generator Register |       |       |       |       |       | 0000  |       |       |               |

| I2C1CON      | 0206        | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW    | SMEN                         | GCEN  | STREN | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208        | ACKSTAT | TRSTAT | _       | _      |        | BCL    | GCSTAT    | ADD10                        | IWCOL | I2COV | D_A   | Р     | S     | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A        | _       | _      | _       |        | _      | —      |           | I2C1 Address Register        |       |       |       |       |       | 0000  |       |       |               |

| I2C1MSK      | 020C        | —       | _      |         | _      | _      | _      | AMSK<9:0> |                              |       |       |       |       | 0000  |       |       |       |               |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-23: UART1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15                           | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5 | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|----------------------------------|--------|----------|--------|--------|--------|-------|------------------------|----------|----------|-------|-------------|---------|--------|--------|-------|---------------|

| U1MODE       | 0220        | UARTEN                           | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222        | UTXISEL1                         | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224        | _                                | _      | _        | _      | _      | —      | _     |                        |          |          | UART1 | Transmit Re | egister |        |        |       | xxxx          |

| U1RXREG      | 0226        | _                                | _      | _        | _      | _      | —      | _     | UART1 Receive Register |          |          |       |             |         | 0000   |        |       |               |

| U1BRG        | 0228        | Baud Rate Generator Prescaler 00 |        |          |        |        |        |       |                        |          | 0000     |       |             |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: SPI1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                                         | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|--------|------------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|-------|--------|--------|---------------|

| SPI1STAT     | 0240        | SPIEN  |                                                | SPISIDL | —      |        | —      |       | _     | _     | SPIROV | _     | _     |       |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242        | —      | _                                              | _       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244        | FRMEN  | SPIFSD                                         | FRMPOL  | —      | _      | _      | _     | _     | _     | _      | _     | _     | _     | _     | FRMDLY | —      | 0000          |

| SPI1BUF      | 0248        |        | SPI1 Transmit and Receive Buffer Register 0000 |         |        |        |        |       |       |       | 0000   |       |       |       |       |        |        |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0           | U-0                                             | R/W-0                             | U-0             | U-0               | U-0              | U-0             | U-0     |  |  |  |  |

|---------------|-------------------------------------------------|-----------------------------------|-----------------|-------------------|------------------|-----------------|---------|--|--|--|--|

| _             | _                                               | INT2IE                            | _               | _                 | _                | _               | _       |  |  |  |  |

| bit 15        |                                                 | 1                                 |                 |                   |                  |                 | bit 8   |  |  |  |  |

|               |                                                 |                                   |                 |                   |                  |                 |         |  |  |  |  |

| U-0           | U-0                                             | U-0                               | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

| —             | _                                               |                                   | INT1IE          | CNIE              | AC1IE            | MI2C1IE         | SI2C1IE |  |  |  |  |

| bit 7         | •                                               |                                   |                 | 1 1               |                  |                 | bit C   |  |  |  |  |

|               |                                                 |                                   |                 |                   |                  |                 |         |  |  |  |  |

| Legend:       |                                                 |                                   |                 |                   |                  |                 |         |  |  |  |  |

| R = Readabl   | e bit                                           | W = Writable I                    | oit             | U = Unimplem      | nented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at | POR                                             | '1' = Bit is set                  |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |

|               |                                                 |                                   |                 |                   |                  |                 |         |  |  |  |  |

| bit 15-14     | Unimplemen                                      | ted: Read as 'd                   | )'              |                   |                  |                 |         |  |  |  |  |

| bit 13        | INT2IE: External Interrupt 2 Enable bit         |                                   |                 |                   |                  |                 |         |  |  |  |  |

|               | 1 = Interrupt request enabled                   |                                   |                 |                   |                  |                 |         |  |  |  |  |

|               | -                                               | 0 = Interrupt request not enabled |                 |                   |                  |                 |         |  |  |  |  |

| bit 12-5      | •                                               | ted: Read as '0                   |                 |                   |                  |                 |         |  |  |  |  |

| bit 4         |                                                 | nal Interrupt 1                   |                 |                   |                  |                 |         |  |  |  |  |

|               |                                                 | equest enableo                    |                 |                   |                  |                 |         |  |  |  |  |

| bit 3         | •                                               | change Notifica                   |                 | Enable bit        |                  |                 |         |  |  |  |  |

| DIT 3         | -                                               | request enabled                   | •               |                   |                  |                 |         |  |  |  |  |

|               |                                                 | equest not ena                    |                 |                   |                  |                 |         |  |  |  |  |

| bit 2         | AC1IE: Analo                                    | g Comparator                      | 1 Interrupt En  | able bit          |                  |                 |         |  |  |  |  |

|               | 1 = Interrupt r                                 | equest enabled                    | k               |                   |                  |                 |         |  |  |  |  |

|               | 0 = Interrupt r                                 | equest not ena                    | bled            |                   |                  |                 |         |  |  |  |  |

| bit 1         | MI2C1IE: I2C                                    | 1 Master Event                    | ts Interrupt Er | nable bit         |                  |                 |         |  |  |  |  |

|               | 1 = Interrupt request enabled                   |                                   |                 |                   |                  |                 |         |  |  |  |  |

|               | -                                               | equest not ena                    |                 |                   |                  |                 |         |  |  |  |  |

|               | SI2C1IE: I2C1 Slave Events Interrupt Enable bit |                                   |                 |                   |                  |                 |         |  |  |  |  |

| bit 0         |                                                 | 1 Slave Events<br>equest enabled  |                 |                   |                  |                 |         |  |  |  |  |

| R/W-0           | R-0                                                                                                                                  | R/W-1                                                                 | U-0          | U-0             | R/W-1                                                          | R/W-1           | R/W-1    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|-----------------|----------------------------------------------------------------|-----------------|----------|

| ENAPLL          | APLLCK                                                                                                                               | SELACLK                                                               | _            | —               | APSTSCLR2                                                      | APSTSCLR1       | APSTSCLR |

| bit 15          | •                                                                                                                                    |                                                                       |              |                 |                                                                | •               | bit 0    |

| R/W-0           | R/W-0                                                                                                                                | U-0                                                                   | U-0          | U-0             | U-0                                                            | U-0             | U-0      |

| ASRCSEL         | FRCSEL                                                                                                                               | _                                                                     |              |                 | _                                                              | _               | _        |

| bit 7           |                                                                                                                                      |                                                                       |              |                 |                                                                |                 |          |

| Legend:         |                                                                                                                                      |                                                                       |              |                 |                                                                |                 |          |

| R = Readable    | bit                                                                                                                                  | W = Writable b                                                        | oit          | U = Unimple     | emented bit, read                                              | d as '0'        |          |

| -n = Value at P | OR                                                                                                                                   | '1' = Bit is set                                                      |              | ʻ0' = Bit is c  | leared                                                         | x = Bit is unkn | own      |

| bit 15          | ENAPLL: Au<br>1 = APLL is e<br>0 = APLL is d                                                                                         |                                                                       | ole bit      |                 |                                                                |                 |          |

| bit 14          | 1 = Indicates                                                                                                                        | PLL Locked Statu<br>that auxiliary PL<br>that auxiliary PL            | L is in lock |                 |                                                                |                 |          |

| bit 13          | 1 = Auxiliary                                                                                                                        | oscillators provi                                                     | des the sou  | rce clock for a | Clock Divider bi<br>auxiliary clock div<br>auxiliary clock dir | rider           |          |

| bit 12-11       | •                                                                                                                                    | ited: Read as '0                                                      |              |                 |                                                                | Vider           |          |

| bit 10-8        | -                                                                                                                                    | :2:0>: Auxiliary (                                                    |              | ıt Dividar hits |                                                                |                 |          |

|                 | 111 = Divideo<br>110 = Divideo<br>101 = Divideo<br>100 = Divideo<br>011 = Divideo<br>010 = Divideo<br>001 = Divideo<br>001 = Divideo | d by 1<br>d by 2<br>d by 4<br>d by 8<br>d by 16<br>d by 32<br>d by 64 |              |                 |                                                                |                 |          |

| bit 7           | 1 = Primary o                                                                                                                        | Select Reference<br>oscillator is the c<br>input is selected          | lock source  |                 | ry Clock bit                                                   |                 |          |

| bit 6           |                                                                                                                                      | lect Reference (<br>RC clock for aux                                  |              | e for Auxiliary | PLL bit                                                        |                 |          |

|                 | 0 = Input cloc                                                                                                                       | k source is dete                                                      |              | ASRCSEL bit     | setting                                                        |                 |          |

### REGISTER 8-5: ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER<sup>(1)</sup>

**Note 1:** This register is reset only on a Power-on Reset (POR).

| R/W-0         | U-0                                                                                                                                         | R/W-0                              | R/W-0           | R/W-0                  | R/W-0                  | R/W-0                 | R/W-0                 |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|------------------------|------------------------|-----------------------|-----------------------|--|--|--|--|

| ROON          | _                                                                                                                                           | ROSSLP                             | ROSEL           | RODIV3 <sup>(1)</sup>  | RODIV2 <sup>(1)</sup>  | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |  |

| bit 15        |                                                                                                                                             |                                    |                 |                        |                        |                       | bit 8                 |  |  |  |  |

|               |                                                                                                                                             |                                    |                 |                        |                        |                       |                       |  |  |  |  |

| U-0           | U-0                                                                                                                                         | U-0                                | U-0             | U-0                    | U-0                    | U-0                   | U-0                   |  |  |  |  |

|               | _                                                                                                                                           | —                                  |                 | —                      | —                      | —                     | —                     |  |  |  |  |

| bit 7         |                                                                                                                                             |                                    |                 |                        |                        |                       | bit 0                 |  |  |  |  |

| Legend:       |                                                                                                                                             |                                    |                 |                        |                        |                       |                       |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                       | W = Writable                       | bit             | U = Unimplen           | nented bit, read       | l as '0'              |                       |  |  |  |  |

| -n = Value at | POR                                                                                                                                         | '1' = Bit is set                   |                 | '0' = Bit is cle       |                        | x = Bit is unkr       | iown                  |  |  |  |  |

|               |                                                                                                                                             |                                    |                 |                        |                        |                       |                       |  |  |  |  |

| bit 15        | ROON: Refer                                                                                                                                 | ence Oscillator                    | r Output Enab   | ole bit                |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             |                                    |                 | on the REFCL           | .K0 pin <sup>(2)</sup> |                       |                       |  |  |  |  |

|               |                                                                                                                                             | e oscillator outp                  |                 | ł                      |                        |                       |                       |  |  |  |  |

| bit 14        | Unimplemen                                                                                                                                  | Unimplemented: Read as '0'         |                 |                        |                        |                       |                       |  |  |  |  |

| bit 13        | ROSSLP: Reference Oscillator Run in Sleep bit                                                                                               |                                    |                 |                        |                        |                       |                       |  |  |  |  |

|               | <ul> <li>1 = Reference oscillator output continues to run in Sleep</li> <li>0 = Reference oscillator output is disabled in Sleep</li> </ul> |                                    |                 |                        |                        |                       |                       |  |  |  |  |

| bit 12        | ROSEL: Reference Oscillator Source Select bit                                                                                               |                                    |                 |                        |                        |                       |                       |  |  |  |  |

|               | 1 = Oscillator                                                                                                                              | crystal is used                    | as the refere   | nce clock              |                        |                       |                       |  |  |  |  |

|               | •                                                                                                                                           | lock is used as                    |                 |                        |                        |                       |                       |  |  |  |  |

| bit 11-8      | RODIV<3:0>:                                                                                                                                 | Reference Os                       | cillator Divide | er bits <sup>(1)</sup> |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    | •               |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    | •               | 4                      |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi<br>ence clock divi |                 |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    | -               |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    | •               |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    |                 |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    | -               |                        |                        |                       |                       |  |  |  |  |

|               | 0111 = Refer                                                                                                                                | ence clock divi                    | ded by 128      |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    | -               |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    |                 |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    |                 |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi                    | -               |                        |                        |                       |                       |  |  |  |  |

|               |                                                                                                                                             | ence clock divi<br>ence clock divi | -               |                        |                        |                       |                       |  |  |  |  |

|               | 000T = Velet                                                                                                                                |                                    |                 |                        |                        |                       |                       |  |  |  |  |

|               | 0000 = Refer                                                                                                                                |                                    |                 |                        |                        |                       |                       |  |  |  |  |

#### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

Note 1: The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

2: This pin is remappable. Refer to Section 10.6 "Peripheral Pin Select" for more information.

#### **10.7** Peripheral Pin Select Registers

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices implement 34 registers for remappable peripheral configuration:

- 15 Input Remappable Peripheral Registers

- 17 Output Remappable Peripheral Registers

Note: Input and output register values can only be changed if OSCCON<IOLOCK> = 0. See Section 10.6.3.1 "Control Register Lock" for a specific command sequence. Not all output remappable peripheral registers are implemented on all devices. See the specific register description for further details.

#### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

#### Legend:

| =ogonan           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

#### bit 15-14 Unimplemented: Read as '0'

bit 13-8

bit 7-0

INT1R<5:0>: Assign External Interrupt 1 (INTR1) to the Corresponding RPn Pin bits

111111 = Input tied to Vss

100011 = Input tied to RP35

100010 = Input tied to RP34

100000 = Input tied to RP32

.

.

00000 = Input tied to RP0

Unimplemented: Read as '0'

© 2008-2014 Microchip Technology Inc.

#### REGISTER 15-7: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER<sup>(1,2)</sup>

| R/W-0                                                                | R/W-0                                                                         | R/W-0 | R/W-0    | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|----------|----------|-------|-------|-------|

|                                                                      |                                                                               |       | PDC      | x<15:8>  |       |       |       |

| bit 15                                                               |                                                                               |       |          |          |       |       | bit 8 |

|                                                                      |                                                                               |       |          |          |       |       |       |

| R/W-0                                                                | R/W-0                                                                         | R/W-0 | R/W-0    | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |                                                                               |       | PDC      | \$x<7:0> |       |       |       |

| bit 7                                                                |                                                                               |       |          |          |       |       | bit 0 |

|                                                                      |                                                                               |       |          |          |       |       |       |

| Legend:                                                              |                                                                               |       |          |          |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                               |       | d as '0' |          |       |       |       |

| -n = Value at P                                                      | Value at POR $(1)^2$ = Bit is set $(0)^2$ = Bit is cleared x = Bit is unknown |       |          |          | nown  |       |       |

#### bit 15-0 PDCx<15:0>: PWM Generator # Duty Cycle Value bits

- **Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL. The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period-0x0008.

- 2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

#### **REGISTER 15-8:** SDCx: PWMx SECONDARY DUTY CYCLE REGISTER<sup>(1,2)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|----------------------------------------|-------|-------|-------|

|                 |       |                  | SDC   | x<15:8>                                |       |       |       |

| bit 15          |       |                  |       |                                        |       |       | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | SDC   | x<7:0>                                 |       |       |       |

| bit 7           |       |                  |       |                                        |       |       | bit 0 |

|                 |       |                  |       |                                        |       |       |       |

| Legend:         |       |                  |       |                                        |       |       |       |

| R = Readable    | bit   | W = Writable     | bit   | it U = Unimplemented bit, read as '0'  |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknow |       |       | nown  |

#### bit 15-0 **SDCx<15:0>:** Secondary Duty Cycle for PWMxL Output Pin bits

- **Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle. The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period-0x0008.

- 2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

| R/W-0           | R/W-0        | R/W-0                                    | R/W-0                      | R/W-0                 | R/W-0                 | R/W-0                   | R/W-0  |

|-----------------|--------------|------------------------------------------|----------------------------|-----------------------|-----------------------|-------------------------|--------|

| PENH            | PENL         | POLH                                     | POLL                       | PMOD1 <sup>(1)</sup>  | PMOD0 <sup>(1)</sup>  | OVRENH                  | OVRENL |

| bit 15          |              |                                          |                            |                       |                       |                         | bit    |

| R/W-0           | R/W-0        | R/W-0                                    | R/W-0                      | R/W-0                 | R/W-0                 | R/W-0                   | R/W-0  |

| OVRDAT1         | OVRDAT0      | FLTDAT1 <sup>(2)</sup>                   | FLTDAT0 <sup>(2)</sup>     | CLDAT1 <sup>(2)</sup> | CLDAT0 <sup>(2)</sup> | SWAP                    | OSYNC  |

| bit 7           |              |                                          |                            |                       |                       |                         | bit    |

| Legend:         |              |                                          |                            |                       |                       |                         |        |

| R = Readable    | bit          | W = Writable                             | bit                        | U = Unimplen          | nented bit, read      | l as '0'                |        |

| -n = Value at F | POR          | '1' = Bit is set                         |                            | '0' = Bit is cle      |                       | x = Bit is unkr         | nown   |

| bit 15          | PENH: PWN    | /H Output Pin                            | Ownership bit              |                       |                       |                         |        |

|                 |              | dule controls th                         | -                          |                       |                       |                         |        |

|                 | 0 = GPIO mo  | dule controls th                         | ne PWMxH pin               | 1                     |                       |                         |        |

| bit 14          |              | IL Output Pin C                          | =                          |                       |                       |                         |        |

|                 |              | dule controls th                         |                            |                       |                       |                         |        |

| L:1 40          |              | dule controls th                         |                            |                       |                       |                         |        |

| bit 13          |              | /H Output Pin                            | •                          |                       |                       |                         |        |

|                 |              | oin is active-low<br>oin is active-hig   |                            |                       |                       |                         |        |

| bit 12          | -            | _ Output Pin Po                          |                            |                       |                       |                         |        |

|                 |              | in is active-low                         | •                          |                       |                       |                         |        |

|                 | •            | in is active-hig                         |                            |                       |                       |                         |        |

| bit 11-10       | PMOD<1:0>:   | PWM # I/O P                              | in Mode bits <sup>(1</sup> | )                     |                       |                         |        |

|                 | 11 = PWM I/0 | D pin pair is in t                       | he True Indep              | endent Output         | t mode                |                         |        |

|                 |              | D pin pair is in t                       |                            | •                     |                       |                         |        |

|                 |              | D pin pair is in t<br>D pin pair is in t |                            |                       |                       |                         |        |

|                 |              | Override Enabl                           | •                          |                       | noue                  |                         |        |

| bit 9           | -            | <1> provides d                           |                            |                       |                       |                         |        |

|                 |              | erator provides d                        |                            |                       | n pin                 |                         |        |

| bit 8           | •            | verride Enable                           |                            |                       |                       |                         |        |

|                 |              | <0> provides d                           |                            |                       | pin                   |                         |        |

|                 |              | erator provides                          |                            |                       | - P                   |                         |        |

| bit 7-6         | OVRDAT<1:0   | >: Data for P                            | WMxH and PV                | VMxL Pins if C        | Override is Enab      | led bits                |        |

|                 | If OVERENH   | = 1, then OVR                            | DAT<1> provid              | des data for P\       | WМхН                  |                         |        |

|                 |              | = 1, then OVR                            | -                          |                       |                       |                         |        |

| bit 5-4         | FLTDAT<1:0   | State for P\                             | WMxH and PW                | VMxL Pins if Fl       | LTMOD is Enab         | led bits <sup>(2)</sup> |        |

|                 |              | LTMOD> = 0:                              |                            |                       |                       |                         |        |

|                 |              | ve, then FLTDA<br>ve, then FLTDA         | •                          |                       |                       |                         |        |

|                 |              | TLTMOD > = 1:                            | •                          |                       |                       |                         |        |

|                 |              | t is active, then                        |                            |                       | or PWMxH              |                         |        |

|                 |              |                                          | P                          |                       | PWMxL                 |                         |        |

### REGISTER 15-14: IOCONx: PWMx I/O CONTROL REGISTER

yield unpredictable results.

2: The state represents the active/inactive state of the PWM module depending on the POLH and POLL bit settings.

### 17.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70000195) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit  $(l^2C)$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface, where:

- The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7-bit and 10-bit addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

### REGISTER 19-8: ADCPC3: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup>

| bit 4-0 | TRGSRC6<4:0>: Trigger 6 Source Selection bits<br>Selects trigger source for conversion of Analog Channels AN13 and AN12.<br>11111 = Timer2 period match |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00111 = PWM Generator 4 primary trigger is selected<br>00110 = PWM Generator 3 primary trigger is selected                                              |

- Note 1: This register is only implemented on the dsPIC33FJ16GS502 and dsPIC33FJ16GS504 devices.

- 2: The trigger source must be set as global software trigger prior to setting this bit to '1'. If other conversions are in progress, conversion will be performed when the conversion resources are available.

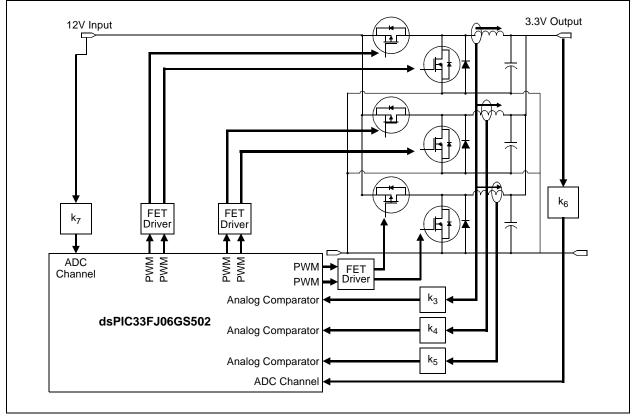

#### FIGURE 24-9: HIGH-SPEED PWMx MODULE FAULT TIMING CHARACTERISTICS

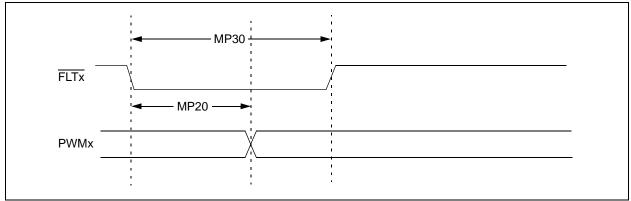

#### FIGURE 24-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 24-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |       |                |

|--------------------|--------|------------------------------------|-------------------------------------------------------|-----|-----|-------|----------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>      | Min                                                   | Тур | Max | Units | Conditions     |

| MP10               | TFPWM  | PWMx Output Fall Time              | —                                                     | 2.5 | —   | ns    |                |

| MP11               | TRPWM  | PWMx Output Rise Time              | —                                                     | 2.5 | —   | ns    |                |

| MP20               | Tfd    | Fault Input ↓ to PWM<br>I/O Change | —                                                     |     | 15  | ns    |                |

| MP30               | Тғн    | Minimum PWMx Fault Pulse<br>Width  | 8                                                     | _   | —   | ns    | DTC<1:0> = 10  |

| MP31               | TPDLY  | Tap Delay                          | 1.04                                                  | —   | —   | ns    | Аськ = 120 MHz |

| MP32               | ACLK   | PWMx Input Clock                   |                                                       | _   | 120 | MHz   | See Note 2     |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: This parameter is a maximum allowed input clock for the PWMx module.

| AC CHARA             | CTERISTICS                               |                                             | Standard Operating<br>(unless otherwise s<br>Operating temperation | stated)<br>ure -40°C ≤ |     |     |

|----------------------|------------------------------------------|---------------------------------------------|--------------------------------------------------------------------|------------------------|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                         | CKE                    | СКР | SMP |

| 15 MHz               | Table 24-31                              | —                                           | —                                                                  | 0,1                    | 0,1 | 0,1 |

| 9 MHz                | —                                        | Table 24-32                                 | —                                                                  | 1                      | 0,1 | 1   |

| 9 MHz                | —                                        | Table 24-33                                 | —                                                                  | 0                      | 0,1 | 1   |

| 15 MHz               | —                                        | —                                           | Table 24-34                                                        | 1                      | 0   | 0   |

| 11 MHz               | —                                        | —                                           | Table 24-35                                                        | 1                      | 1   | 0   |

| 15 MHz               | —                                        | —                                           | Table 24-36                                                        | 0                      | 1   | 0   |

| 11 MHz               |                                          | —                                           | Table 24-37                                                        | 0                      | 0   | 0   |

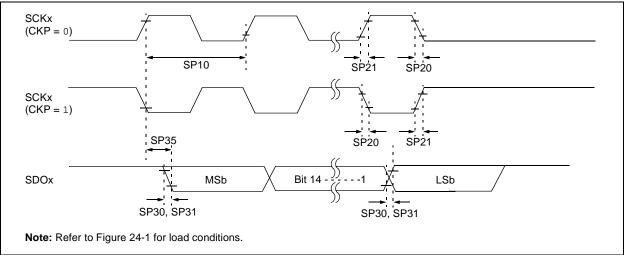

#### FIGURE 24-11: SPIx MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING **CHARACTERISTICS**

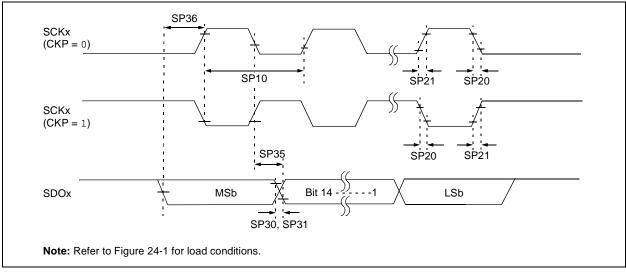

#### SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING FIGURE 24-12: **CHARACTERISTICS**

#### 25.1 High-Temperature DC Characteristics

#### TABLE 25-1: OPERATING MIPS VS. VOLTAGE

|                | VDD Range                   | Temperature Range | Max MIPS                                         |  |

|----------------|-----------------------------|-------------------|--------------------------------------------------|--|

| Characteristic | (in Volts)                  | (in °C)           | dsPIC33FJ06GS101/X02 and<br>dsPIC33FJ16GSX02/X04 |  |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +150°C   | 20                                               |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 24-11 for BOR values.

#### TABLE 25-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| High-Temperature Devices                                                                                                                                                               |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40 | _           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40 | —           | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     |     | PINT + PI/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | Pdmax  | (   | TJ - TA)/θJ | A    | W    |

#### TABLE 25-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARA         | CTERISTIC | S              | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |   |                 |  |  |

|------------------|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---|-----------------|--|--|

| Parameter<br>No. | Symbol    | Characteristic | Min Typ Max Units Conditions                                                                                                                           |     |     |   |                 |  |  |

| Operating V      | Voltage   |                |                                                                                                                                                        |     |     |   |                 |  |  |

| HDC10            | Supply Vo | Itage          |                                                                                                                                                        |     |     |   |                 |  |  |

|                  | Vdd       | —              | 3.0                                                                                                                                                    | 3.3 | 3.6 | V | -40°C to +150°C |  |  |

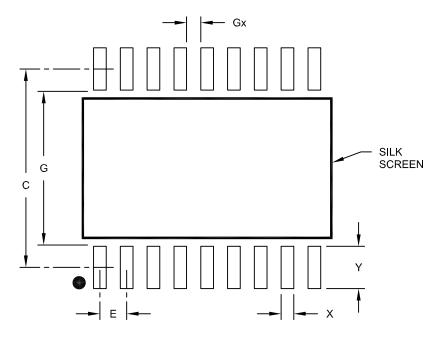

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                       | Units  | N        | S    |      |  |

|-----------------------|--------|----------|------|------|--|

| Dimension             | Limits | MIN      | NOM  | MAX  |  |

| Contact Pitch         | E      | 1.27 BSC |      |      |  |

| Contact Pad Spacing   | С      |          | 9.40 |      |  |

| Contact Pad Width     | Х      |          |      | 0.60 |  |

| Contact Pad Length    | Y      |          |      | 2.00 |  |

| Distance Between Pads | Gx     | 0.67     |      |      |  |

| Distance Between Pads | G      | 7.40     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

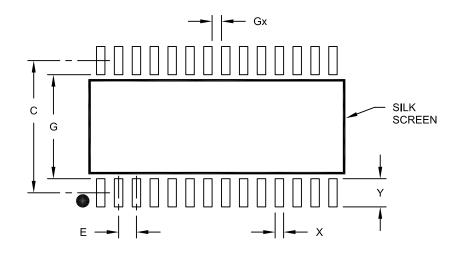

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units            |          |      |      |  |

|--------------------------|------------------|----------|------|------|--|

| Dimension                | Dimension Limits |          |      | MAX  |  |

| Contact Pitch            | E                | 1.27 BSC |      |      |  |

| Contact Pad Spacing      | С                |          | 9.40 |      |  |

| Contact Pad Width (X28)  | X                |          |      | 0.60 |  |

| Contact Pad Length (X28) | Y                |          |      | 2.00 |  |

| Distance Between Pads    | Gx               | 0.67     |      |      |  |

| Distance Between Pads    | G                | 7.40     |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

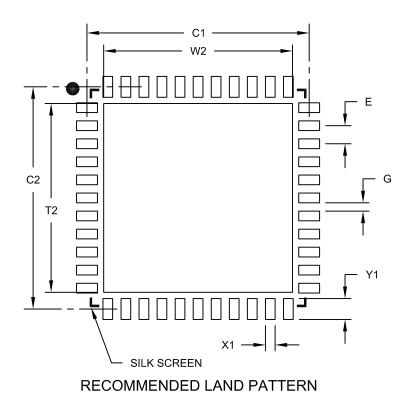

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | N      | <b>ILLIMETER</b> | S    |      |  |

|----------------------------|--------|------------------|------|------|--|

| Dimension                  | Limits | MIN              | NOM  | MAX  |  |

| Contact Pitch              | E      | 0.65 BSC         |      |      |  |

| Optional Center Pad Width  | W2     | 6.60             |      |      |  |

| Optional Center Pad Length | T2     | 6.60             |      |      |  |

| Contact Pad Spacing        | C1     |                  | 8.00 |      |  |

| Contact Pad Spacing        | C2     |                  | 8.00 |      |  |

| Contact Pad Width (X44)    | X1     |                  |      | 0.35 |  |

| Contact Pad Length (X44)   | Y1     |                  |      | 0.85 |  |

| Distance Between Pads      | G      | 0.25             |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M