Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

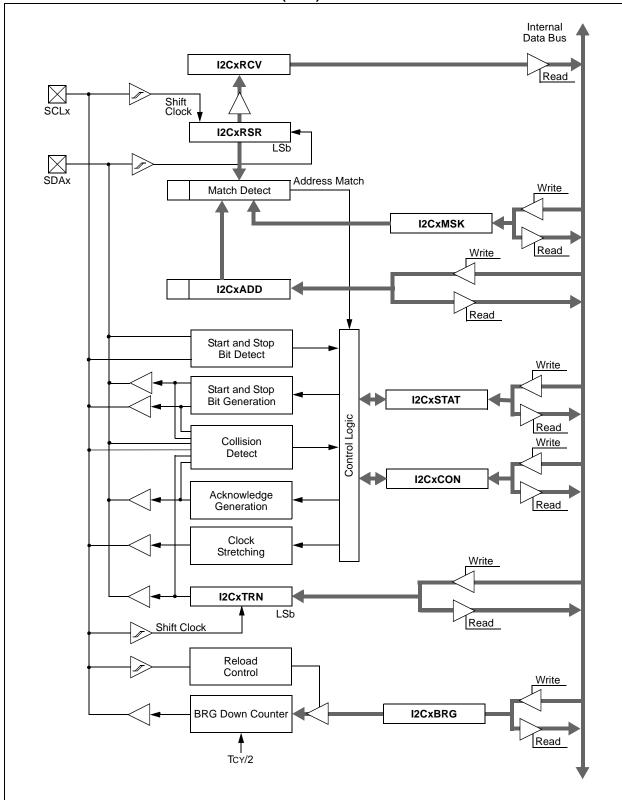

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

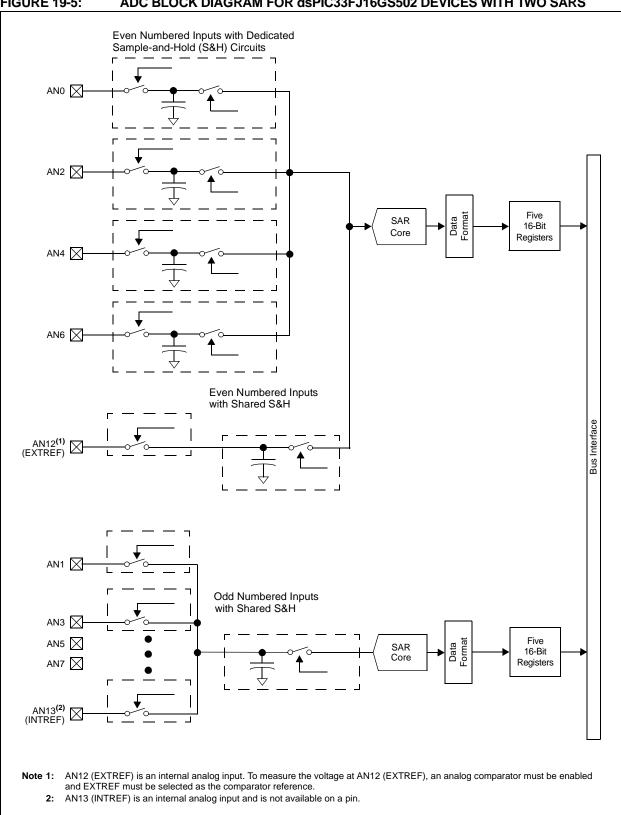

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name | SFR<br>Addr | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9           | Bit 8        | Bit 7 | Bit 6   | Bit 5    | Bit 4          | Bit 3      | Bit 2     | Bit 1      | Bit 0 | All<br>Resets |

|-----------|-------------|----------|----------|----------|----------|----------|----------|-----------------|--------------|-------|---------|----------|----------------|------------|-----------|------------|-------|---------------|

| WREG0     | 0000        |          |          |          |          |          |          | Working Regi    | ster 0       |       |         |          |                |            |           |            |       | 0000          |

| WREG1     | 0002        |          |          |          |          |          |          | Working Regi    | ster 1       |       |         |          |                |            |           |            |       | 0000          |

| WREG2     | 0004        |          |          |          |          |          |          | Working Regi    | ster 2       |       |         |          |                |            |           |            |       | 0000          |

| WREG3     | 0006        |          |          |          |          |          |          | Working Regi    | ster 3       |       |         |          |                |            |           |            |       | 0000          |

| WREG4     | 8000        |          |          |          |          |          |          | Working Regi    | ster 4       |       |         |          |                |            |           |            |       | 0000          |

| WREG5     | 000A        |          |          |          |          |          |          | Working Regi    | ster 5       |       |         |          |                |            |           |            |       | 0000          |

| WREG6     | 000C        |          |          |          |          |          |          | Working Regi    | ster 6       |       |         |          |                |            |           |            |       | 0000          |

| WREG7     | 000E        |          |          |          |          |          |          | Working Regi    | ster 7       |       |         |          |                |            |           |            |       | 0000          |

| WREG8     | 0010        |          |          |          |          |          |          | Working Regi    | ster 8       |       |         |          |                |            |           |            |       | 0000          |

| WREG9     | 0012        |          |          |          |          |          |          | Working Regi    | ster 9       |       |         |          |                |            |           |            |       | 0000          |

| WREG10    | 0014        |          |          |          |          |          |          | Working Regis   | ter 10       |       |         |          |                |            |           |            |       | 0000          |

| WREG11    | 0016        |          |          |          |          |          |          | Working Regis   | ster 11      |       |         |          |                |            |           |            |       | 0000          |

| WREG12    | 0018        |          |          |          |          |          |          | Working Regis   | ter 12       |       |         |          |                |            |           |            |       | 0000          |

| WREG13    | 001A        |          |          |          |          |          |          | Working Regis   | ter 13       |       |         |          |                |            |           |            |       | 0000          |

| WREG14    | 001C        |          |          |          |          |          |          | Working Regis   | ter 14       |       |         |          |                |            |           |            |       | 0000          |

| WREG15    | 001E        |          |          |          |          |          |          | Working Regis   | ter 15       |       |         |          |                |            |           |            |       | 0800          |

| SPLIM     | 0020        |          |          |          |          |          | Sta      | ck Pointer Limi | t Register   |       |         |          |                |            |           |            |       | xxxx          |

| ACCAL     | 0022        |          |          |          |          |          |          | ACCAL           |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCAH     | 0024        |          |          |          |          |          |          | ACCAH           |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCAU     | 0026        | ACCA<39>        | ACCA<39>     |       |         |          | ACCA           | AU         |           |            |       | xxxx          |

| ACCBL     | 0028        |          |          |          |          |          |          | ACCBL           |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCBH     | 002A        |          |          |          |          | -        |          | ACCBH           |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCBU     | 002C        | ACCB<39>        | ACCB<39>     |       |         |          | ACCE           | BU         |           |            |       | XXXX          |

| PCL       | 002E        |          |          |          |          |          | Program  | Counter Low     | Word Regist  | er    |         |          |                |            |           |            |       | 0000          |

| PCH       | 0030        | _        | _        |          | —        | —        | —        | _               | _            |       |         | Program  | Counter H      | igh Byte I | Register  |            |       | 0000          |

| TBLPAG    | 0032        | _        |          | _        | _        | _        | _        | _               | _            |       |         | Table Pa | ge Address     | 8 Pointer  | Register  |            |       | 0000          |

| PSVPAG    | 0034        | _        | —        | -        | -        | _        | —        | -               | —            |       | Program | Memory \ | /isibility Pag | ge Addres  | ss Pointe | r Register | r     | 0000          |

| RCOUNT    | 0036        |          |          |          |          |          | REPE     | AT Loop Coun    | ter Register |       |         |          |                |            |           |            |       | xxxx          |

| DCOUNT    | 0038        |          |          |          |          |          |          | DCOUNT<1        | 5:0>         |       |         |          |                |            |           |            | -     | xxxx          |

| DOSTARTL  | 003A        |          |          |          |          |          | DOS      | STARTL<15:1:    | >            |       |         |          |                |            |           |            | 0     | xxxx          |

| DOSTARTH  | 003C        | _        | _        | _        | _        | _        | _        | _               | _            | _     | _       |          | D              | OSTART     | FH<5:0>   |            |       | 00xx          |

| DOENDL    | 003E        |          |          |          |          |          | DC       | ENDL<15:1>      |              |       |         |          |                |            |           |            | 0     | xxxx          |

| DOENDH    | 0040        | _        | -        |          | _        | —        | _        | —               | _            | —     | _       |          |                | DOEN       | IDH       |            | -     | 00xx          |

| SR        | 0042        | OA       | OB       | SA       | SB       | OAB      | SAB      | DA              | DC           | IPL2  | IPL1    | IPL0     | RA             | N          | OV        | Z          | С     | 0000          |

| CORCON    | 0044        | _        | _        | _        | US       | EDT      | DL2      | DL1             | DL0          | SATA  | SATB    | SATDW    | ACCSAT         | IPL3       | PSV       | RND        | IF    | 0020          |

| MODCON    | 0046        | XMODEN   | YMODEN   | _        | _        | BWM3     | BWM2     | BWM1            | BWM0         | YWM3  | YWM2    | YWM1     | YWM0           | XWM3       | XWM2      | XWM1       | XWM0  | 0000          |

## TABLE 4-1: CPU CORE REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-11: TIMER REGISTER MAP FOR dsPIC33FJ06GS101 AND dsPIC33FJ06GSX02

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7    | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-----------|----------|-------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 0100        |        |        |        |        |        |        |       | Timer1 Re | egister  |       |        |        |       |       |       |       | 0000          |

| PR1          | 0102        |        |        |        |        |        |        |       | Period Re | gister 1 |       |        |        |       |       |       |       | FFFF          |

| T1CON        | 0104        | TON    | —      | TSIDL  | —      | _      | —      | _     | _         | _        | TGATE | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2         | 0106        |        |        |        |        |        |        |       | Timer2 Re | egister  |       |        |        |       |       |       |       | 0000          |

| PR2          | 010C        |        |        |        |        |        |        |       | Period Re | gister 2 |       |        |        |       |       |       |       | FFFF          |

| T2CON        | 0110        | TON    | _      | TSIDL  | _      | —      | _      | _     | —         | _        | TGATE | TCKPS1 | TCKPS0 | _     | _     | TCS   | —     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: TIMER REGISTER MAP FOR dsPIC33FJ16GSX02 AND dsPIC33FJ16GSX04

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8         | Bit 7         | Bit 6       | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|------------|---------------|---------------|-------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 0100        |        |        |        |        |        |        |            | Timer1 Re     | egister       |             |        |        |       |       |       |       | 0000          |

| PR1          | 0102        |        |        |        |        |        |        |            | Period Reg    | gister 1      |             |        |        |       |       |       |       | FFFF          |

| T1CON        | 0104        | TON    | _      | TSIDL  | _      | -      | _      | _          | _             | -             | TGATE       | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| TMR2         | 0106        |        | 5      |        |        |        |        |            |               |               |             |        |        |       | 0000  |       |       |               |

| TMR3HLD      | 0108        |        |        |        |        |        | Timer3 | Holding Re | gister (for 3 | 2-bit timer o | perations o | nly)   |        |       |       |       |       | xxxx          |

| TMR3         | 010A        |        |        |        |        |        |        |            | Timer3 Re     | egister       |             |        |        |       |       |       |       | 0000          |

| PR2          | 010C        |        |        |        |        |        |        |            | Period Reg    | gister 2      |             |        |        |       |       |       |       | FFFF          |

| PR3          | 010E        |        |        |        |        |        |        |            | Period Reg    | gister 3      |             |        |        |       |       |       |       | FFFF          |

| T2CON        | 0110        | TON    |        | TSIDL  | _      | _      | _      |            | —             | _             | TGATE       | TCKPS1 | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON        | 0112        | TON    | _      | TSIDL  | _      | _      | _      |            | _             | _             | TGATE       | TCKPS1 | TCKPS0 |       | -     | TCS   | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: INPUT CAPTURE REGISTER MAP FOR dsPIC33FJ06GS202

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7      | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|------------|------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| IC1BUF       | 0140        |        |        |        |        |        |        | Inpu  | ut Capture | 1 Register |       |       |       |       |       |       |       | xxxx          |

| IC1CON       | 0142        | _      | —      | ICSIDL | _      |        | _      | _     |            | ICTMR      | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-27: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                                                                                                                 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7       | Bit 6          | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|------------------------------------------------------------------------------------------------------------------------|--------|---------|--------|--------|-------|----------|-------------|----------------|---------|-----------|----------|----------|----------|----------|---------------|

| ADCON        | 0300        | ADON   | —                                                                                                                      | ADSIDL | SLOWCLK | —      | GSWTRG | —     | FORM     | EIE         | ORDER          | SEQSAMP | ASYNCSAMP | —        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _      | -                                                                                                                      | —      | _       | _      |        | _     | —        | _           | _              | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _      | -                                                                                                                      | —      | _       | _      |        | _     | —        | _           | P6RDY          | _       | _         | _        | P2RDY    | P1RDY    | PORDY    | 0000          |

| ADBASE       | 0308        |        |                                                                                                                        |        |         |        |        |       | ADBASE<1 | 5:1>        |                |         |           |          |          |          | —        | 0000          |

| ADCPC0       | 030A        | IRQEN1 | VI PENDI SWTRGI TRGSRC14 TRGSRC13 TRGSRC12 TRGSRC11 TRGSRC10 IRQEN0 PEND0 SWTRG0 TRGSRC04 TRGSRC03 TRGSRC02 TRGSRC01 T |        |         |        |        |       |          |             |                |         |           |          | TRGSRC00 | 0000     |          |               |

| ADCPC1       | 030C        | _      | -                                                                                                                      | —      | _       | _      |        | _     | —        | IRQEN2      | PEND2          | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCPC3       | 0310        | _      |                                                                                                                        |        |         |        |        |       |          |             |                |         |           |          | TRGSRC60 | 0000     |          |               |

| ADCBUF0      | 0320        |        |                                                                                                                        |        |         |        |        |       | ADC E    | Data Buffer | 0              |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |        |                                                                                                                        |        |         |        |        |       | ADC E    | Data Buffer | <sup>.</sup> 1 |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |        |                                                                                                                        |        |         |        |        |       | ADC E    | Data Buffer | 2              |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |        |                                                                                                                        |        |         |        |        |       | ADC E    | Data Buffer | 3              |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |        |                                                                                                                        |        |         |        |        |       | ADC E    | Data Buffer | 4              |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |        |                                                                                                                        |        |         |        |        |       | ADC E    | Data Buffer | 5              |         |           |          |          |          |          | xxxx          |

| ADCBUF12     | 0338        |        |                                                                                                                        |        |         |        |        |       | ADC D    | ata Buffer  | 12             |         |           |          |          |          |          | xxxx          |

| ADCBUF13     | 033A        |        |                                                                                                                        |        |         |        |        |       | ADC D    | Data Buffer | 13             |         |           |          |          |          |          | xxxx          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

## TABLE 4-28: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ16GS402/404 DEVICES ONLY

|              | -           |         |                   |            | -           |                 |               |               |              |            |       | -       |           |          |          |          |          |               |

|--------------|-------------|---------|-------------------|------------|-------------|-----------------|---------------|---------------|--------------|------------|-------|---------|-----------|----------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14            | Bit 13     | Bit 12      | Bit 11          | Bit 10        | Bit 9         | Bit 8        | Bit 7      | Bit 6 | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADCON        | 0300        | ADON    | —                 | ADSIDL     | SLOWCLK     | _               | GSWTRG        | _             | FORM         | EIE        | ORDER | SEQSAMP | ASYNCSAMP | -        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _       | _                 | _          | _           | —               | _             | _             | _            | PCFG7      | PCFG6 | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _       | _                 | _          | _           | —               | _             | _             | _            | _          | _     | _       | _         | P3RDY    | P2RDY    | P1RDY    | P0RDY    | 0000          |

| ADBASE       | 0308        |         |                   |            |             |                 |               |               | ADBASE<15    | :1>        |       |         |           |          |          |          | —        | 0000          |

| ADCPC0       | 030A        | IRQEN1  | PEND1             | SWTRG1     | TRGSRC14    | TRGSRC13        | TRGSRC12      | TRGSRC11      | TRGSRC10     | IRQEN0     | PEND0 | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | IRQEN3  | PEND3             | SWTRG3     | TRGSRC34    | TRGSRC33        | TRGSRC32      | TRGSRC31      | TRGSRC30     | IRQEN2     | PEND2 | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCBUF0      | 0320        |         |                   |            |             |                 |               |               | ADC D        | ata Buffer | 0     |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |         |                   |            |             |                 |               |               | ADC D        | ata Buffer | 1     |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |         |                   |            |             |                 |               |               | ADC D        | ata Buffer | 2     |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |         |                   |            |             |                 |               |               | ADC D        | ata Buffer | 3     |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |         |                   |            |             |                 |               |               | ADC D        | ata Buffer | 4     |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |         |                   |            |             |                 |               |               | ADC D        | ata Buffer | 5     |         |           |          |          |          |          | xxxx          |

| ADCBUF6      | 032C        |         | ADC Data Buffer 6 |            |             |                 |               |               |              |            |       |         |           |          |          |          |          | xxxx          |

| ADCBUF7      | 032E        |         |                   |            |             |                 |               |               | ADC D        | ata Buffer | 7     |         |           |          |          |          |          | xxxx          |

| Legend:      | x =         | unknown | value on          | Reset, — = | unimplement | ed, read as '0' | . Reset value | s are shown i | n hexadecima | al.        |       |         |           |          |          |          |          |               |

### TABLE 4-31: ANALOG COMPARATOR CONTROL REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| File<br>Name | ADR  | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4 | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|---------|--------|--------|--------|--------------|-------|--------|--------|--------|-------|---------|-------|--------|-------|---------------|

| CMPCON1      | 0540 | CMPON  |        | CMPSIDL | —      | _      | _      |              | DACOE | INSEL1 | INSEL0 | EXTREF | _     | CMPSTAT | _     | CMPPOL | RANGE | 0000          |

| CMPDAC1      | 0542 | _      | _      | _       | —      |        | -      |              |       |        |        | CMREF  | <9:0> |         |       |        |       | 0000          |

| CMPCON2      | 0544 | CMPON  | _      | CMPSIDL | —      |        | -      | _            | DACOE | INSEL1 | INSEL0 | EXTREF |       | CMPSTAT | _     | CMPPOL | RANGE | 0000          |

| CMPDAC2      | 0546 | _      | —      | _       | —      | _      | _      | - CMREF<9:0> |       |        |        |        |       |         |       |        |       | 0000          |

### TABLE 4-32: ANALOG COMPARATOR CONTROL REGISTER MAP dsPIC33FJ16GS502/504 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------|-------|--------|-------|---------------|

| CMPCON1      | 0540        | CMPON  | _      | CMPSIDL | —      | _      | _      | _     | DACOE | INSEL1 | INSEL0 | EXTREF | —      | CMPSTAT | _     | CMPPOL | RANGE | 0000          |

| CMPDAC1      | 0542        | _      | _      | _       | —      |        | -      |       |       |        |        | CMREF  | -<9:0> |         |       |        |       | 0000          |

| CMPCON2      | 0544        | CMPON  | _      | CMPSIDL | —      |        | -      | _     | DACOE | INSEL1 | INSEL0 | EXTREF | _      | CMPSTAT | _     | CMPPOL | RANGE | 0000          |

| CMPDAC2      | 0546        | _      | _      | _       | —      |        | -      |       |       |        |        | CMREF  | -<9:0> |         |       |        |       | 0000          |

| CMPCON3      | 0548        | CMPON  | _      | CMPSIDL | —      |        | -      | _     | DACOE | INSEL1 | INSEL0 | EXTREF | _      | CMPSTAT | _     | CMPPOL | RANGE | 0000          |

| CMPDAC3      | 054A        | _      | _      | _       | —      |        | -      |       |       |        |        | CMREF  | -<9:0> |         |       |        |       | 0000          |

| CMPCON4      | 054C        | CMPON  | _      | CMPSIDL | —      |        | -      | _     | DACOE | INSEL1 | INSEL0 | EXTREF | _      | CMPSTAT | _     | CMPPOL | RANGE | 0000          |

| CMPDAC4      | 054E        | _      | _      | _       | —      | _      | —      |       |       |        |        | CMREF  | <9:0>  |         |       |        |       | 0000          |

### TABLE 4-45: PMD REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | —      | _      | T2MD   | T1MD   | —      | PWMMD  | —      | I2C1MD | -     | U1MD  |       | SPI1MD | —     |       | ADCMD | 0000          |

| PMD2        | 0772        | _      | —      | _      | —      | _      | —      | —      | IC1MD  | —      |       | _     | _     | _      | —     |       | OC1MD | 0000          |

| PMD3        | 0774        | _      | —      | _      | —      | _      | CMPMD  | —      | _      | —      |       | _     | _     | _      | —     |       | —     | 0000          |

| PMD4        | 0776        | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _     | REFOMD | _     | _     | —     | 0000          |

| PMD6        | 077A        | _      | _      | _      | _      | _      | _      | PWM2MD | PWM1MD | _      | _     | _     | _     | _      | _     | _     | —     | 0000          |

| PMD7        | 077C        | _      | _      | _      | _      | _      | _      | CMP2MD | CMP1MD | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-46: PMD REGISTER MAP FOR dsPIC33FJ16GS402 AND dsPIC33FJ16GS404 DEVICES ONLY

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      |        | T3MD   | T2MD   | T1MD   | _      | PWMMD  | —      | I2C1MD | _     | U1MD  |       | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        |        |        | _      | _      | _      | _      | IC2MD  | IC1MD  | _      | _     | _     | _     | _      | -     | OC2MD | OC1MD | 0000          |

| PMD3        | 0774        |        |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _     | _      | -     | _     | —     | 0000          |

| PMD4        | 0776        |        |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _     | REFOMD | -     | _     | —     | 0000          |

| PMD6        | 077A        |        |        | _      | _      | _      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _     | _      | -     | _     | —     | 0000          |

| PMD7        | 077C        |        |        | _      | _      | _      | _      | _      | _      | _      | _     | _     | _     | _      | -     | _     | _     | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-47: PMD REGISTER MAP FOR dsPIC33FJ16GS502 AND dsPIC33FJ16GS504 DEVICES ONLY

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | -      | _      | T3MD   | T2MD   | T1MD   | _      | PWMMD  | —      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | —     | ADCMD | 0000          |

| PMD2        | 0772        | _      | _      | _      |        | _      | _      | IC2MD  | IC1MD  | _      |       | —     | _     | _      | _     | OC2MD | OC1MD | 0000          |

| PMD3        | 0774        | -      | _      |        |        |        | CMPMD  |        |        | _      |       | _     | —     |        |       |       | —     | 0000          |

| PMD4        | 0776        | -      | _      |        |        |        |        |        |        | _      |       | _     | —     | REFOMD |       |       | —     | 0000          |

| PMD6        | 077A        | _      | _      | _      |        | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      |       | _     | _     | _      | _     | _     | —     | 0000          |

| PMD7        | 077C        | _      | _      |        |        | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      |       | _     | _     | _      |       |       | _     | 0000          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

The address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

## 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM bits (W register selection) in the MODCON register are any value other than 15 (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed         |

|-------|--------------------------------------------|

|       | Addressing should not be enabled           |

|       | together. If an application attempts to do |

|       | so, Bit-Reversed Addressing will assume    |

|       | priority when active for the X WAGU and X  |

|       | WAGU; Modulo Addressing will be dis-       |

|       | abled. However, Modulo Addressing will     |

|       | continue to function in the X RAGU.        |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

| OA OB SA SB OAB SAB DA DC<br>bit 15                                                                                                                                                                                                                                                                                            |                      |                      |                      |       |       |       |       |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| bit 15<br>R/W-0 <sup>(3)</sup> R/W-0 <sup>(3)</sup> R/W-0 <sup>(3)</sup> R-0 R/W-0 R/W-0 R/W-0 R/W<br>IPL2 <sup>(2)</sup> IPL1 <sup>(2)</sup> IPL0 <sup>(2)</sup> RA N OV Z C<br>bit 7                                                                                                                                         | R-0                  | R-0                  | R/C-0                | R/C-0 | R-0   | R/C-0 | R -0  | R/W-0 |

| R/W-0 <sup>(3)</sup> R/W-0 <sup>(3)</sup> R-0         R/W-0         R/W-0         R/W           IPL2 <sup>(2)</sup> IPL1 <sup>(2)</sup> IPL0 <sup>(2)</sup> RA         N         OV         Z         C           bit 7 </td <td>OA</td> <td>OB</td> <td>SA</td> <td>SB</td> <td>OAB</td> <td>SAB</td> <td>DA</td> <td>DC</td> | OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| IPL2 <sup>(2)</sup> IPL0 <sup>(2)</sup> RA         N         OV         Z         C           bit 7                                                                                                                                                                                                                            | bit 15               |                      |                      |       |       |       |       | bit 8 |

| IPL2 <sup>(2)</sup> IPL0 <sup>(2)</sup> RA         N         OV         Z         C           bit 7                                                                                                                                                                                                                            |                      |                      |                      |       |       |       |       |       |

| bit 7                                                                                                                                                                                                                                                                                                                          | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                                                                                                                                                                                                                                                                                                                                | IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N     | OV    | Z     | C     |

| Legend: C = Clearable bit                                                                                                                                                                                                                                                                                                      | bit 7                |                      |                      |       | •     |       |       | bit 0 |

| Legend: C = Clearable bit                                                                                                                                                                                                                                                                                                      |                      |                      |                      |       |       |       |       |       |

|                                                                                                                                                                                                                                                                                                                                | Legend:              |                      | C = Clearable        | bit   |       |       |       |       |

| REGISTER 7-1: SR: CPU S | STATUS REGISTER <sup>(1)</sup> |

|-------------------------|--------------------------------|

|-------------------------|--------------------------------|

| Legend:           | C = Clearable bit |                        |                                    |  |  |

|-------------------|-------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>    |

|---------|------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                           |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                           |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                           |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                           |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                           |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                            |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                            |

|         |                                                                        |

**Note 1:** For complete register details, see Register 3-1.

2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> status bits are read-only when NSTDIS (INTCON1<15>) = 1.

| U-0                                     | U-0   | U-0           | R/W-0               | R/W-0                              | R-0   | R-0              | R-0   |  |

|-----------------------------------------|-------|---------------|---------------------|------------------------------------|-------|------------------|-------|--|

| —                                       | —     | —             | US                  | EDT                                | DL2   | DL1              | DL0   |  |

| bit 15                                  |       |               |                     |                                    |       |                  | bit 8 |  |

|                                         |       |               |                     |                                    |       |                  |       |  |

| R/W-0                                   | R/W-0 | R/W-1         | R/W-0               | R/C-0                              | R/W-0 | R/W-0            | R/W-0 |  |

| SATA                                    | SATB  | SATDW         | ACCSAT              | IPL3 <sup>(2)</sup>                | PSV   | RND              | IF    |  |

| bit 7                                   |       |               |                     |                                    |       |                  | bit 0 |  |

|                                         |       |               |                     |                                    |       |                  |       |  |

| Legend:                                 |       | C = Clearable | bit                 |                                    |       |                  |       |  |

| R = Readable bit W = Writable           |       | W = Writable  | bit -n = Value at P |                                    | POR   | '1' = Bit is set |       |  |

| 0' = Bit is cleared 'x = Bit is unknown |       |               | nown                | U = Unimplemented bit, read as '0' |       |                  |       |  |

|                                         |       |               |                     |                                    |       |                  | ,     |  |

### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

**IPL3:** CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

bit 3

| U-0                          | U-0                                        | U-0                                                                      | U-0                   | U-0                               | U-0             | U-0             | U-0    |  |  |  |  |

|------------------------------|--------------------------------------------|--------------------------------------------------------------------------|-----------------------|-----------------------------------|-----------------|-----------------|--------|--|--|--|--|

| _                            | —                                          |                                                                          | _                     | —                                 | _               | _               |        |  |  |  |  |

| oit 15                       |                                            |                                                                          |                       |                                   |                 |                 | bit    |  |  |  |  |

|                              |                                            |                                                                          |                       |                                   |                 |                 |        |  |  |  |  |

| U-0                          | R/W-1                                      | R/W-0                                                                    | R/W-0                 | U-0                               | R/W-1           | R/W-0           | R/W-0  |  |  |  |  |

| —                            | AC4IP2                                     | AC4IP1                                                                   | AC4IP0                |                                   | AC3IP2          | AC3IP1          | AC3IP0 |  |  |  |  |

| bit 7                        |                                            |                                                                          |                       |                                   |                 |                 | bit    |  |  |  |  |

|                              |                                            |                                                                          |                       |                                   |                 |                 |        |  |  |  |  |

| <b>Legend:</b><br>R = Readat | le bit                                     | W = Writable                                                             | hit                   | II – Unimplen                     | nented bit, rea | d as '0'        |        |  |  |  |  |

| -n = Value a                 |                                            | '1' = Bit is set                                                         |                       | $0^{\circ} = \text{Bit is clear}$ |                 | x = Bit is unkr |        |  |  |  |  |

|                              |                                            |                                                                          |                       |                                   | aleu            |                 | 100011 |  |  |  |  |

| bit 15-7                     | Unimplomon                                 | tod: Pood os '                                                           | 0'                    |                                   |                 |                 |        |  |  |  |  |

|                              | -                                          | Unimplemented: Read as '0'                                               |                       |                                   |                 |                 |        |  |  |  |  |

| bit 6-4                      |                                            | AC4IP<2:0>: Analog Comparator 4 Interrupt Priority bits                  |                       |                                   |                 |                 |        |  |  |  |  |

|                              | ⊥⊥⊥ = Interru                              | 111 = Interrupt is Priority 7 (highest priority)                         |                       |                                   |                 |                 |        |  |  |  |  |

|                              | •                                          |                                                                          |                       |                                   |                 |                 |        |  |  |  |  |

|                              | •                                          |                                                                          |                       |                                   |                 |                 |        |  |  |  |  |

|                              |                                            |                                                                          |                       |                                   |                 |                 |        |  |  |  |  |

|                              | •                                          |                                                                          |                       |                                   |                 |                 |        |  |  |  |  |

|                              | •<br>001 = Interru<br>000 = Interru        | pt is Priority 1<br>pt source is dis                                     | abled                 |                                   |                 |                 |        |  |  |  |  |

| bit 3                        | 000 = Interru                              |                                                                          |                       |                                   |                 |                 |        |  |  |  |  |

| bit 3<br>bit 2-0             | 000 = Interru<br>Unimplemen                | pt source is dis<br>ted: Read as '                                       | 0'                    | upt Priority bits                 |                 |                 |        |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr | upt Priority bits<br>ty)          |                 |                 |        |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '                                       | 0'<br>arator 3 Interr |                                   |                 |                 |        |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr |                                   |                 |                 |        |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr |                                   |                 |                 |        |  |  |  |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '<br>Analog Compa<br>pt is Priority 7 ( | 0'<br>arator 3 Interr |                                   |                 |                 |        |  |  |  |  |

#### REGISTER 7-31: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

| U-0                | U-0                                                                                                                                                                                                           | R/W-1                                                                                                                                                                                                           | R/W-1                                    | R/W-1                      | R/W-1            | R/W-1           | R/W-1   |  |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| —                  | —                                                                                                                                                                                                             | U1CTSR5                                                                                                                                                                                                         | U1CTSR4                                  | U1CTSR3                    | U1CTSR2          | U1CTSR1         | U1CTSR0 |  |  |  |  |  |  |

| bit 15             |                                                                                                                                                                                                               |                                                                                                                                                                                                                 |                                          |                            |                  |                 | bit 8   |  |  |  |  |  |  |

| U-0                | U-0                                                                                                                                                                                                           | R/W-1                                                                                                                                                                                                           | R/W-1                                    | R/W-1                      | R/W-1            | R/W-1           | R/W-1   |  |  |  |  |  |  |

| 0-0                | 0-0                                                                                                                                                                                                           | U1RXR5                                                                                                                                                                                                          | U1RXR4                                   | U1RXR3                     | U1RXR2           | U1RXR1          | U1RXR0  |  |  |  |  |  |  |

| bit 7              |                                                                                                                                                                                                               | UTIVILU                                                                                                                                                                                                         | 01101104                                 | 0110010                    | OTIVITZ          | UIIXI           | bit (   |  |  |  |  |  |  |

|                    |                                                                                                                                                                                                               |                                                                                                                                                                                                                 |                                          |                            |                  |                 |         |  |  |  |  |  |  |

| Legend:            |                                                                                                                                                                                                               |                                                                                                                                                                                                                 |                                          |                            |                  |                 |         |  |  |  |  |  |  |

| R = Readab         | le bit                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                    | bit                                      | U = Unimplen               | nented bit, read | l as '0'        |         |  |  |  |  |  |  |

| -n = Value a       | t POR                                                                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                |                                          | '0' = Bit is cle           | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |

| bit 15-14          | Unimplement                                                                                                                                                                                                   | ted. Dood oo '                                                                                                                                                                                                  | <u>,</u>                                 |                            |                  |                 |         |  |  |  |  |  |  |

|                    | -                                                                                                                                                                                                             | ted: Read as '                                                                                                                                                                                                  |                                          |                            |                  |                 |         |  |  |  |  |  |  |

| bit 13-8           | <b>U1CTSR&lt;5:0&gt;:</b> Assign UART1 Clear-to-Send (U1CTS) to the Corresponding RPn Pin bits                                                                                                                |                                                                                                                                                                                                                 |                                          |                            |                  |                 |         |  |  |  |  |  |  |

|                    |                                                                                                                                                                                                               |                                                                                                                                                                                                                 |                                          | 111111 = Input tied to Vss |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 <b>= I</b> np                                                                                                                                                                                          |                                                                                                                                                                                                                 |                                          |                            |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp                                                                                                                                                                                  | ut tied to RP35                                                                                                                                                                                                 |                                          |                            |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp                                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34                                                                                                                                                                              | ŀ                                        |                            |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                                                                                                                                                           | L<br>3                                   |                            |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34                                                                                                                                                                              | L<br>3                                   |                            |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                                                                                                                                                           | L<br>3                                   |                            |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                                                  | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                                                                                                                                                           | L<br>3                                   |                            |                  |                 |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                                                  | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                                        | L<br>3                                   |                            |                  |                 |         |  |  |  |  |  |  |

| bit 7-6            | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>00000 = Inpu                                                                                                              | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0                                                                                                                       | 4<br>3<br>2                              |                            |                  |                 |         |  |  |  |  |  |  |

| bit 7-6<br>bit 5-0 | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Inpu<br>Unimplemen                                                                                                                    | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '(                                                                                             | L<br>3<br>2                              | IRX) to the Co             | rresponding RF   | Pn Pin bits     |         |  |  |  |  |  |  |

| bit 7-6<br>bit 5-0 | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Inpu<br>Unimplement<br>U1RXR<5:0>                                                                                                     | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART                                                                            | L<br>3<br>2                              | IRX) to the Co             | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Inpu<br>Unimplement<br>U1RXR<5:0><br>111111 = Inp                                                                                     | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART                                                                            | )<br>)<br>1 Receive (U <sup>7</sup>      | IRX) to the Co             | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Inpu<br>Unimplement<br>U1RXR<5:0><br>111111 = Inp<br>100011 = Inp                                                                     | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss                                                          | 1<br>2<br>1 Receive (U <sup>7</sup>      | IRX) to the Co             | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33 | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co             | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34                    | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co             | rresponding RF   | Pn Pin bits     |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33 | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co             | rresponding RF   | 'n Pin bits     |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33 | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co             | rresponding RF   | n Pin bits      |         |  |  |  |  |  |  |

|                    | <pre>111111 = Inp<br/>100011 = Inp<br/>100010 = Inp<br/>100000 = Inp<br/>00000 = Inpu<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre> | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>: Assign UART<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33 | )<br>)<br>1 Receive (U <sup>2</sup><br>5 | IRX) to the Co             | rresponding RF   | Pn Pin bits     |         |  |  |  |  |  |  |

## REGISTER 10-6: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| REGISTER 1      | 1-1: T1CO                                                                | N: TIMER1 C                         | ONTROL RE       | GISTER           |                  |                  |       |  |  |  |

|-----------------|--------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|------------------|------------------|-------|--|--|--|

| R/W-0           | U-0                                                                      | R/W-0                               | U-0             | U-0              | U-0              | U-0              | U-0   |  |  |  |

| TON             | —                                                                        | TSIDL                               | —               | —                | —                | —                |       |  |  |  |

| bit 15          |                                                                          |                                     |                 |                  |                  |                  | bit 8 |  |  |  |

|                 | <b>D</b> 4 4 4                                                           |                                     |                 |                  | 5444.6           | <b>D b b c c</b> |       |  |  |  |

| U-0             | R/W-0                                                                    | R/W-0                               | R/W-0           | U-0              | R/W-0            | R/W-0            | U-0   |  |  |  |

|                 | TGATE                                                                    | TCKPS1                              | TCKPS0          | _                | TSYNC            | TCS              | —     |  |  |  |

| bit 7           |                                                                          |                                     |                 |                  |                  |                  | bit ( |  |  |  |