Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FABLE 1-1:     I       Pin Name | Pin        | I/O DESC<br>Buffer | PPS     | Description                                                           |

|---------------------------------|------------|--------------------|---------|-----------------------------------------------------------------------|

|                                 | Туре       | Туре               | Capable |                                                                       |

| CMP1A                           | I          | Analog             | No      | Comparator 1 Channel A.                                               |

| CMP1B                           | 1          | Analog             | No      | Comparator 1 Channel B.                                               |

| CMP1C                           | 1          | Analog             | No      | Comparator 1 Channel C.                                               |

| CMP1D                           | 1          | Analog             | No      | Comparator 1 Channel D.                                               |

| CMP2A                           | 1          | Analog             | No      | Comparator 2 Channel A.                                               |

| CMP2B                           | 1          | Analog             | No      | Comparator 2 Channel B.                                               |

| CMP2C                           | 1          | Analog             | No      | Comparator 2 Channel C.                                               |

| CMP2D                           | 1          | Analog             | No      | Comparator 2 Channel D.                                               |

| CMP3A                           | i          | Analog             | No      | Comparator 3 Channel A.                                               |

| CMP3B                           | 1          | Analog             | No      | Comparator 3 Channel B.                                               |

| CMP3C                           | 1          | Analog             | No      | Comparator 3 Channel C.                                               |

| CMP3D                           | i          | Analog             | No      | Comparator 3 Channel D.                                               |

| CMP4A                           | i          | Analog             | No      | Comparator 4 Channel A.                                               |

| CMP4B                           | i          | Analog             | No      | Comparator 4 Channel B.                                               |

| CMP4C                           | i          | Analog             | No      | Comparator 4 Channel C.                                               |

| CMP4D                           | l i        | Analog             | No      | Comparator 4 Channel D.                                               |

| DACOUT                          | 0          | 7 (10)             | No      | DAC output voltage.                                                   |

| ACMP1-ACMP4                     | 0          |                    | Yes     | DAC trigger to PWM module.                                            |

| EXTREF                          | 1          |                    | No      | External voltage reference input for the reference DACs.              |

| REFCLKO                         | 0          | Analog             |         |                                                                       |

| REFULKO                         | 0          |                    | Yes     | REFCLKO output signal is a postscaled derivative of the system clock. |

| FLT1-FLT8                       | I          | ST                 | Yes     | Fault Inputs to PWM module.                                           |

| SYNCI1-SYNCI2                   | I          | ST                 | Yes     | External synchronization signal to PWM master time base.              |

| SYNCO1                          | 0          |                    | Yes     | PWM master time base for external device synchronization.             |

| PWM1L                           | 0          |                    | No      | PWM1 low output.                                                      |

| PWM1H                           | 0          |                    | No      | PWM1 high output.                                                     |

| PWM2L                           | 0          |                    | No      | PWM2 low output.                                                      |

| PWM2H                           | Ō          |                    | No      | PWM2 high output.                                                     |

| PWM3L                           | 0          |                    | No      | PWM3 low output.                                                      |

| PWM3H                           | 0          |                    | No      | PWM3 high output.                                                     |

| PWM4L                           | 0          |                    | Yes     | PWM4 low output.                                                      |

| PWM4H                           | 0          | _                  | Yes     | PWM4 high output.                                                     |

| PGED1                           | I/O        | ST                 | No      | Data I/O pin for programming/debugging Communication Channel 1.       |

| PGEC1                           | 1          | ST                 | No      | Clock input pin for programming/debugging Communication               |

|                                 |            | _                  | -       | Channel 1.                                                            |

| PGED2                           | I/O        | ST                 | No      | Data I/O pin for programming/debugging Communication Channel 2.       |

| PGEC2                           | ., C       | ST                 | No      | Clock input pin for programming/debugging Communication               |

| . 0101                          |            | 01                 |         | Channel 2.                                                            |

| PGED3                           | I/O        | ST                 | No      | Data I/O pin for programming/debugging Communication Channel 3        |

| PGEC3                           | 1/0        | ST                 | No      | Clock input pin for programming/debugging Communication Channel 3.    |

| TOLOG                           | · ·        | 01                 | NO      | Channel 3.                                                            |

| MCLR                            | I/P        | ST                 | No      | Master Clear (Reset) input. This pin is an active-low Reset to the    |

|                                 | UT.        | 51                 | NU      | device.                                                               |

| AVDD                            | Р          | Р                  | No      | Positive supply for analog modules. This pin must be connected at     |

| ////DD                          |            | I                  |         | all times. AVDD is connected to VDD.                                  |

| AVss                            | Р          | Р                  | No      | Ground reference for analog modules. AVss is connected to Vss.        |

| VDD                             | P          |                    | No      | Positive supply for peripheral logic and I/O pins.                    |

| VCAP                            | P          |                    | No      | CPU logic filter capacitor connection.                                |

| Vss                             | P          |                    | No      | Ground reference for logic and I/O pins.                              |

|                                 | -          | <br>compatible     |         |                                                                       |

|                                 |            | gger input v       |         |                                                                       |

|                                 | Fransistor |                    |         |                                                                       |

#### . . . . .

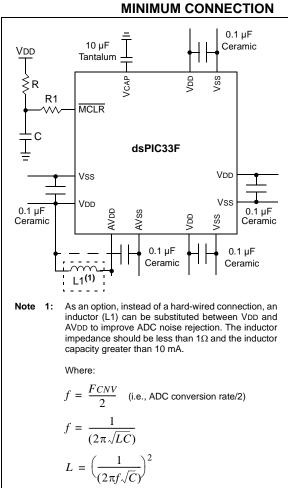

RECOMMENDED

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 µF to 47 µF.

#### 2.3 **Capacitor on Internal Voltage Regulator (VCAP)**

A low-ESR (<5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7 µF and 10 µF, 16V connected to ground. The type can be ceramic or tantalum. Refer to Section 24.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to Section 21.2 "On-Chip Voltage Regulator" for details.

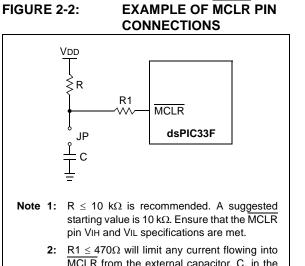

#### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- · Device programming and debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

MCLR from the external capacitor, C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

FIGURE 2-1:

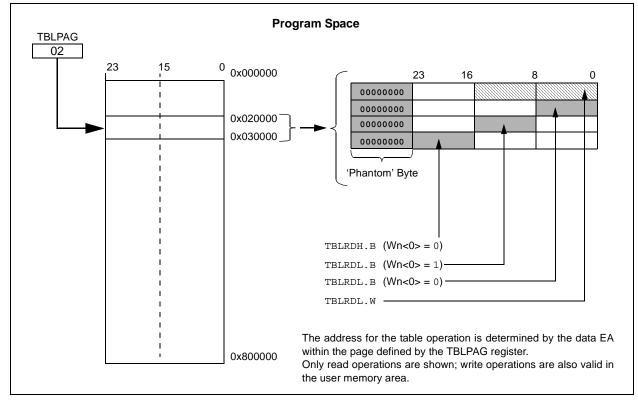

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

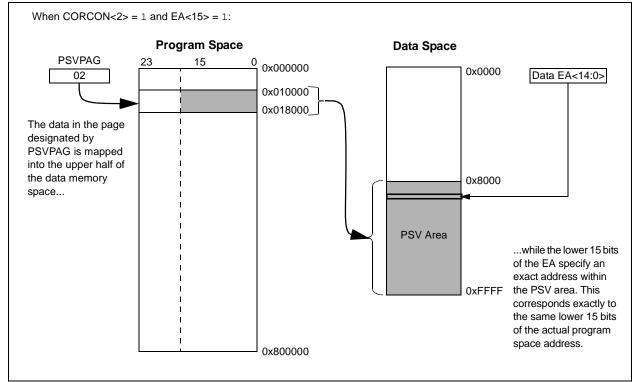

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and Program Space Visibility (PSV) is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 8000h and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during Table Reads/Writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

| R/W-0           | R/W-0                                                                                              | U-0                               | U-0            | U-0               | U-0             | R/W-0           | R/W-0  |

|-----------------|----------------------------------------------------------------------------------------------------|-----------------------------------|----------------|-------------------|-----------------|-----------------|--------|

| ADCP1IE         | ADCP0IE                                                                                            | —                                 | —              | —                 | _               | AC4IE           | AC3IE  |

| bit 15          |                                                                                                    |                                   |                |                   |                 |                 | bit    |

| R/W-0           | U-0                                                                                                | U-0                               | U-0            | U-0               | U-0             | R/W-0           | R/W-0  |

| AC2IE           |                                                                                                    | _                                 | _              |                   | _               | PWM4IE          | PWM3IE |

| bit 7           |                                                                                                    |                                   |                |                   |                 |                 | bit (  |

| Legend:         |                                                                                                    |                                   |                |                   |                 |                 |        |

| R = Readable    | bit                                                                                                | W = Writable                      | bit            | U = Unimplem      | nented bit. rea | d as '0'        |        |

| -n = Value at F | POR                                                                                                | '1' = Bit is set                  |                | '0' = Bit is clea |                 | x = Bit is unkr | iown   |

|                 |                                                                                                    |                                   |                |                   |                 |                 |        |

| bit 15          | ADCP1IE: AD                                                                                        | DC Pair 1 Conv                    | ersion Done    | Interrupt Enable  | e bit           |                 |        |

|                 |                                                                                                    | equest is enab                    |                |                   |                 |                 |        |

|                 |                                                                                                    | request is not e                  |                |                   |                 |                 |        |

| bit 14          |                                                                                                    |                                   |                | Interrupt Enable  | bit             |                 |        |

|                 | •                                                                                                  | equest is enab<br>equest is not e |                |                   |                 |                 |        |

| bit 13-10       | •                                                                                                  | ted: Read as '                    |                |                   |                 |                 |        |

| bit 9           | -                                                                                                  | g Comparator                      |                | able bit          |                 |                 |        |

|                 |                                                                                                    | equest is enab                    |                |                   |                 |                 |        |

|                 |                                                                                                    | equest is not e                   |                |                   |                 |                 |        |

| bit 8           | AC3IE: Analo                                                                                       | g Comparator                      | 3 Interrupt Er | nable bit         |                 |                 |        |

|                 |                                                                                                    | equest is enab                    |                |                   |                 |                 |        |

|                 |                                                                                                    | equest is not e                   |                |                   |                 |                 |        |

| bit 7           | AC2IE: Analog Comparator 2 Interrupt Enable bit                                                    |                                   |                |                   |                 |                 |        |

|                 | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                   |                |                   |                 |                 |        |

| bit 6-2         | •                                                                                                  | ted: Read as '                    |                |                   |                 |                 |        |

| bit 1           | -                                                                                                  | /M4 Interrupt E                   |                |                   |                 |                 |        |

|                 |                                                                                                    | equest is enab                    |                |                   |                 |                 |        |

|                 | •                                                                                                  | equest is not e                   |                |                   |                 |                 |        |

| bit 0           | PWM3IE: PW                                                                                         | /M3 Interrupt E                   | nable bit      |                   |                 |                 |        |

|                 |                                                                                                    | equest is enab                    |                |                   |                 |                 |        |

#### REGISTER 7-17: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

| U-0          | R/W-1              | R/W-0                                                                                                                 | R/W-0             | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |  |

|--------------|--------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|-----------------|----------|--|--|--|

| _            | CNIP2              | CNIP1                                                                                                                 | CNIP0             | _                 | AC1IP2           | AC1IP1          | AC1IP0   |  |  |  |

| bit 15       |                    |                                                                                                                       |                   |                   |                  |                 | bit      |  |  |  |

|              |                    |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

| U-0          | R/W-1              | R/W-0                                                                                                                 | R/W-0             | U-0               | R/W-1            | R/W-0           | R/W-0    |  |  |  |

|              | MI2C1IP2           | MI2C1IP1                                                                                                              | MI2C1IP0          | —                 | SI2C1IP2         | SI2C1IP1        | SI2C1IP0 |  |  |  |

| bit 7        |                    |                                                                                                                       |                   |                   |                  |                 | bit      |  |  |  |

| Legend:      |                    |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

| R = Readab   | le bit             | W = Writable                                                                                                          | bit               | U = Unimple       | mented bit, read | d as '0'        |          |  |  |  |

| -n = Value a | t POR              | '1' = Bit is set                                                                                                      | t                 | '0' = Bit is cle  | eared            | x = Bit is unkr | nown     |  |  |  |

| hit 15       | Unimplement        | <b>ted:</b> Dood oo '                                                                                                 | 0'                |                   |                  |                 |          |  |  |  |

| bit 15       | -                  | nted: Read as '                                                                                                       |                   | Duiouitus hito    |                  |                 |          |  |  |  |

| bit 14-12    |                    | Change Notifica                                                                                                       | -                 | -                 |                  |                 |          |  |  |  |

|              | •                  | ipt is i nonty i                                                                                                      | (ingriest priorit | y interrupt)      |                  |                 |          |  |  |  |

|              | •                  |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

|              | •                  | unt in Duinuity d                                                                                                     |                   |                   |                  |                 |          |  |  |  |

|              |                    | ipt is Priority 1<br>ipt source is dis                                                                                | sabled            |                   |                  |                 |          |  |  |  |

| bit 11       |                    | nted: Read as '                                                                                                       |                   |                   |                  |                 |          |  |  |  |

| bit 10-8     | -                  |                                                                                                                       |                   | upt Priority bits | S                |                 |          |  |  |  |

|              |                    | AC1IP<2:0>: Analog Comparator 1 Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                   |                   |                  |                 |          |  |  |  |

|              | •                  |                                                                                                                       |                   | • • • •           |                  |                 |          |  |  |  |

|              | •                  |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

|              | •<br>001 = Interru | pt is Priority 1                                                                                                      |                   |                   |                  |                 |          |  |  |  |

|              |                    | ipt source is dis                                                                                                     | abled             |                   |                  |                 |          |  |  |  |

| bit 7        | Unimplemer         | nted: Read as '                                                                                                       | 0'                |                   |                  |                 |          |  |  |  |

| bit 6-4      | MI2C1IP<2:0        | D>: I2C1 Maste                                                                                                        | r Events Interr   | upt Priority bit  | S                |                 |          |  |  |  |

|              | 111 = Interru      | pt is Priority 7                                                                                                      | (highest priorit  | y interrupt)      |                  |                 |          |  |  |  |

|              | •                  |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

|              | •                  |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

|              | 001 = Interru      | pt is Priority 1                                                                                                      |                   |                   |                  |                 |          |  |  |  |

|              |                    | pt source is dis                                                                                                      | sabled            |                   |                  |                 |          |  |  |  |

| bit 3        | Unimplemer         | nted: Read as '                                                                                                       | 0'                |                   |                  |                 |          |  |  |  |

| bit 2-0      | SI2C1IP<2:0        | >: I2C1 Slave I                                                                                                       | Events Interru    | ot Priority bits  |                  |                 |          |  |  |  |

|              | 111 = Interru      | pt is Priority 7                                                                                                      | (highest priorit  | y interrupt)      |                  |                 |          |  |  |  |

|              | •                  |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

|              | •                  |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

|              | 001 = Interru      | upt is Priority 1                                                                                                     |                   |                   |                  |                 |          |  |  |  |

|              |                    |                                                                                                                       |                   |                   |                  |                 |          |  |  |  |

#### ----

| R/W-0           | R-0                                                                                                                                                                                                  | R/W-1                                                                 | U-0          | U-0             | R/W-1                                                          | R/W-1           | R/W-1    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|-----------------|----------------------------------------------------------------|-----------------|----------|

| ENAPLL          | APLLCK                                                                                                                                                                                               | SELACLK                                                               | _            | —               | APSTSCLR2                                                      | APSTSCLR1       | APSTSCLR |

| bit 15          | •                                                                                                                                                                                                    |                                                                       |              |                 |                                                                | •               | bit 0    |

| R/W-0           | R/W-0                                                                                                                                                                                                | U-0                                                                   | U-0          | U-0             | U-0                                                            | U-0             | U-0      |

| ASRCSEL         | FRCSEL                                                                                                                                                                                               | _                                                                     | _            |                 | _                                                              | _               | _        |

| bit 7           |                                                                                                                                                                                                      |                                                                       |              |                 |                                                                |                 |          |

| Legend:         |                                                                                                                                                                                                      |                                                                       |              |                 |                                                                |                 |          |

| R = Readable    | bit                                                                                                                                                                                                  | W = Writable b                                                        | oit          | U = Unimple     | emented bit, read                                              | d as '0'        |          |

| -n = Value at P | OR                                                                                                                                                                                                   | '1' = Bit is set                                                      |              | ʻ0' = Bit is c  | leared                                                         | x = Bit is unkn | own      |

| bit 15          | ENAPLL: Au<br>1 = APLL is e<br>0 = APLL is d                                                                                                                                                         |                                                                       | ole bit      |                 |                                                                |                 |          |

| bit 14          | 1 = Indicates                                                                                                                                                                                        | PLL Locked Statu<br>that auxiliary PL<br>that auxiliary PL            | L is in lock |                 |                                                                |                 |          |

| bit 13          | 1 = Auxiliary                                                                                                                                                                                        | oscillators provi                                                     | des the sou  | rce clock for a | Clock Divider bi<br>auxiliary clock div<br>auxiliary clock dir | rider           |          |

| bit 12-11       | •                                                                                                                                                                                                    | ited: Read as '0                                                      |              |                 |                                                                | Vider           |          |

| bit 10-8        | -                                                                                                                                                                                                    | :2:0>: Auxiliary (                                                    |              | ıt Dividar hits |                                                                |                 |          |

|                 | 111 = Divideo<br>110 = Divideo<br>101 = Divideo<br>100 = Divideo<br>011 = Divideo<br>010 = Divideo<br>001 = Divideo<br>001 = Divideo                                                                 | d by 1<br>d by 2<br>d by 4<br>d by 8<br>d by 16<br>d by 32<br>d by 64 |              |                 |                                                                |                 |          |

| bit 7           | ASRCSEL: Select Reference Clock Source for Auxiliary Clock bit<br>1 = Primary oscillator is the clock source<br>0 = No clock input is selected                                                       |                                                                       |              |                 |                                                                |                 |          |

| bit 6           | <ul> <li>FRCSEL: Select Reference Clock Source for Auxiliary PLL bit</li> <li>1 = Select FRC clock for auxiliary PLL</li> <li>0 = Input clock source is determined by ASRCSEL bit setting</li> </ul> |                                                                       |              |                 |                                                                |                 |          |

|                 | 0 = Input cloc                                                                                                                                                                                       |                                                                       |              | ASRCSEL bit     | setting                                                        |                 |          |

### REGISTER 8-5: ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER<sup>(1)</sup>

**Note 1:** This register is reset only on a Power-on Reset (POR).

#### 9.2.2 IDLE MODE

The following occur in Idle mode:

- The CPU stops executing instructions

- The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active

The device will wake-up from Idle mode on any of these events:

- Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

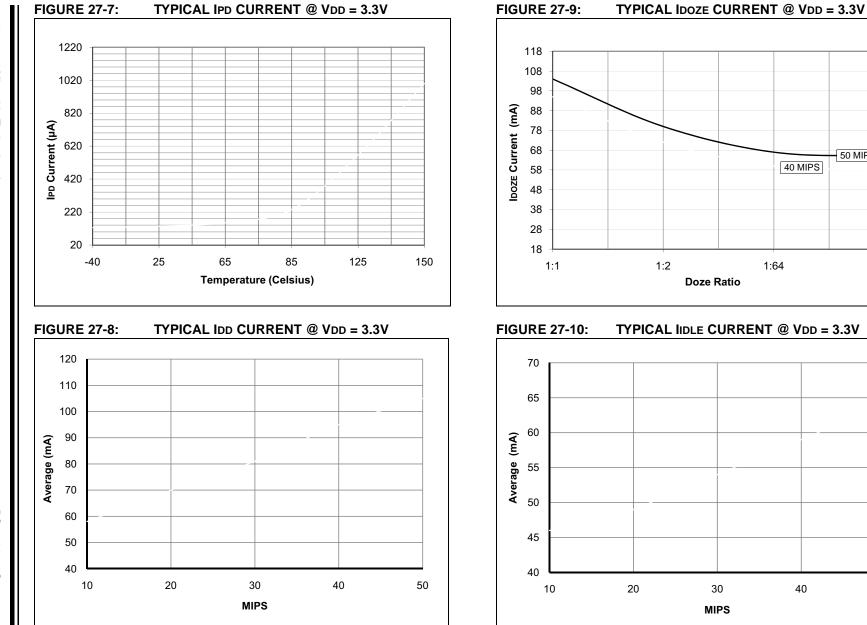

### 9.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

### 9.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

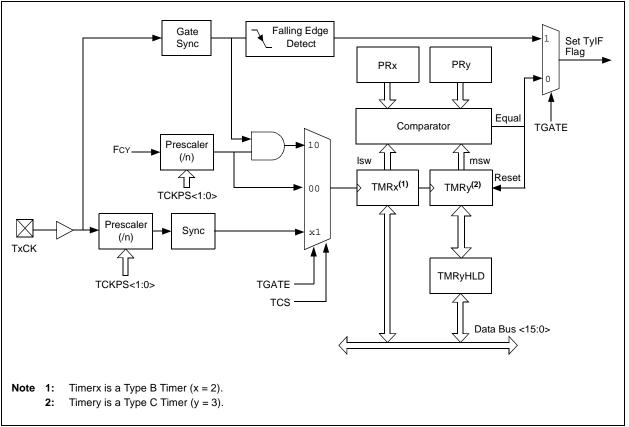

#### FIGURE 12-3: 32-BIT TIMER BLOCK DIAGRAM

### 15.2 Feature Description

The PWM module is designed for applications that require:

- High-resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode, and Push-Pull mode outputs

- The ability to create multiphase PWM outputs

For Center-Aligned mode, the duty cycle, period phase and dead-time resolutions will be 8.32 ns.

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

Phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable. Multiphase PWM is often used to improve DC/DC Converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC Converters are often operated in parallel, but phase-shifted in time. A single PWM output operating at 250 kHz has a period of 4  $\mu$ s, but an array of four PWM channels, staggered by 1  $\mu$ s each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

Variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50%, and the power flow is controlled by varying the relative phase shift between the two PWM generators.

| REGISTER 1            | 8-1: UxMO               | DE: UARTx N                                       |                     | STER                 |                  |                   |               |

|-----------------------|-------------------------|---------------------------------------------------|---------------------|----------------------|------------------|-------------------|---------------|

| R/W-0                 | U-0                     | R/W-0                                             | R/W-0               | R/W-0                | U-0              | R/W-0             | R/W-0         |

| UARTEN <sup>(1)</sup> |                         | USIDL                                             | IREN <sup>(2)</sup> | RTSMD                | —                | UEN1              | UEN0          |

| bit 15                | ·                       |                                                   |                     |                      |                  |                   | bit           |

| R/W-0, HC             | R/W-0                   | R/W-0, HC                                         | R/W-0               | R/W-0                | R/W-0            | R/W-0             | R/W-0         |

| WAKE                  | LPBACK                  | ABAUD                                             | URXINV              | BRGH                 | PDSEL1           | PDSEL0            | STSEL         |

| bit 7                 | EI BROR                 | //B/(OD                                           | OTOXINV             | BROM                 | TDOLLI           | 1 DOLLO           | bit           |

|                       |                         |                                                   | 0                   | •.                   |                  |                   |               |

| Legend:               | 1.12                    | HC = Hardwa                                       |                     |                      |                  |                   |               |

| R = Readable          |                         | W = Writable                                      |                     | -                    | nented bit, read |                   |               |

| -n = Value at F       | POR                     | '1' = Bit is set                                  |                     | '0' = Bit is cle     | ared             | x = Bit is unkn   | own           |

| bit 15                | UARTEN: UA              | ARTx Enable bi                                    | <sub>t</sub> (1)    |                      |                  |                   |               |

|                       | 1 = UARTx is            | s enabled; all U                                  | ARTx pins are       | e controlled by      | UARTx as defi    | ned by UEN<1:     | 0>            |

|                       |                         |                                                   | UARTx pins a        | are controlled I     | by port latches  | , UARTx power     | consumptio    |

| bit 14                | is minima               | ai<br>i <b>ted:</b> Read as 'i                    | ר'                  |                      |                  |                   |               |

| bit 13                | -                       | Tx Stop in Idle I                                 |                     |                      |                  |                   |               |

| bit 13                |                         | ues module op                                     |                     | device enters        | Idle mode        |                   |               |

|                       |                         | s module operation                                |                     |                      |                  |                   |               |

| bit 12                | IREN: IrDA <sup>®</sup> | Encoder and D                                     | ecoder Enable       | e bit <sup>(2)</sup> |                  |                   |               |

|                       | 1 = IrDA enc            | oder and deco                                     | der are enable      | ed                   |                  |                   |               |

|                       | 0 = IrDA enc            | oder and deco                                     | der are disable     | ed                   |                  |                   |               |

| bit 11                |                         | le Selection for                                  |                     | it                   |                  |                   |               |

|                       |                         | in is in Simple»<br>in is in Flow Co              |                     |                      |                  |                   |               |

| bit 10                | Unimplemen              | ted: Read as '                                    | כ'                  |                      |                  |                   |               |

| bit 9-8               |                         | IARTx Enable b                                    |                     |                      |                  |                   |               |

|                       | 10 = UxTX, L            | JxRX, <u>UxCTS</u> a                              | ind UxRTS pir       | ns are enabled       | and used         | controlled by po  |               |

|                       |                         | nd UxRX pins a                                    |                     |                      |                  | /BCLK pins are    |               |

| bit 7                 | WAKE: Wake              | -up on Start bit                                  | Detect During       | g Sleep Mode         | Enable bit       |                   |               |

|                       |                         | vill continue to s<br>are on the follo            |                     |                      | pt is generated  | on falling edge,  | bit is cleare |

|                       |                         | -up is enabled                                    | wing naing eu       | ge                   |                  |                   |               |

| bit 6                 |                         | RTx Loopback                                      | Mode Select         | bit                  |                  |                   |               |

|                       |                         | Loopback mod                                      |                     |                      |                  |                   |               |

|                       |                         | k mode is disat                                   |                     |                      |                  |                   |               |

| bit 5                 | ABAUD: Auto             | o-Baud Enable                                     | bit                 |                      |                  |                   |               |

|                       | before ot               | aud rate meas<br>her data; cleare<br>e measuremen | ed in hardwar       | e upon comple        | tion             | eception of a Sy  | nc field (55  |

| Note 1: Rei           |                         |                                                   |                     |                      |                  | anual" for inform | ation on      |

|                       | abling the UART         |                                                   |                     |                      | ,                |                   |               |

| <b>2:</b> Thi         | s feature is only       | / available for t                                 | he 16x BRG n        | node (BRGH =         | = 0).            |                   |               |

### REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| DC CHARA         | CTERISTIC              | S                | (unless ot | Operating Co<br>herwise state<br>temperature | $-40^{\circ}C \le TA \le +3$ | to 3.6V<br>85°C for Industrial<br>125°C for Extended |

|------------------|------------------------|------------------|------------|----------------------------------------------|------------------------------|------------------------------------------------------|

| Parameter<br>No. | Typical <sup>(1)</sup> | Мах              | Units      |                                              |                              | Conditions                                           |

| Operating C      | Current (IDD)          | ) <sup>(2)</sup> |            |                                              |                              |                                                      |

| DC20d            | 55                     | 70               | mA         | -40°C                                        |                              |                                                      |

| DC20a            | 55                     | 70               | mA         | +25°C                                        | 3.3V                         | 10 MIPS                                              |

| DC20b            | 55                     | 70               | mA         | +85°C                                        | 3.3V                         | See Note 2                                           |

| DC20c            | 55                     | 70               | mA         | +125°C                                       |                              |                                                      |

| DC21d            | 68                     | 85               | mA         | -40°C                                        |                              |                                                      |

| DC21a            | 68                     | 85               | mA         | +25°C                                        | 3.3V                         | 16 MIPS                                              |

| DC21b            | 68                     | 85               | mA         | +85°C                                        | 3.3V                         | See Note 2 and Note 3                                |

| DC21c            | 68                     | 85               | mA         | +125°C                                       |                              |                                                      |

| DC22d            | 78                     | 95               | mA         | -40°C                                        |                              |                                                      |

| DC22a            | 78                     | 95               | mA         | +25°C                                        | 3.3V                         | 20 MIPS                                              |

| DC22b            | 78                     | 95               | mA         | +85°C                                        | 3.3V                         | See Note 2 and Note 3                                |

| DC22c            | 78                     | 95               | mA         | +125°C                                       |                              |                                                      |

| DC23d            | 88                     | 110              | mA         | -40°C                                        |                              |                                                      |

| DC23a            | 88                     | 110              | mA         | +25°C                                        | 3.3V                         | 30 MIPS                                              |

| DC23b            | 88                     | 110              | mA         | +85°C                                        | 3.3V                         | See Note 2 and Note 3                                |

| DC23c            | 88                     | 110              | mA         | +125°C                                       |                              |                                                      |

| DC24d            | 98                     | 120              | mA         | -40°C                                        |                              |                                                      |

| DC24a            | 98                     | 120              | mA         | +25°C                                        | 3.3V                         | 40 MIPS                                              |

| DC24b            | 98                     | 120              | mA         | +85°C                                        | 5.5 v                        | See Note 2                                           |

| DC24c            | 98                     | 120              | mA         | +125°C                                       |                              |                                                      |

| DC25d            | 128                    | 160              | mA         | -40°C                                        |                              | 40 MIPS                                              |

| DC25a            | 125                    | 150              | mA         | +25°C                                        | 3.3V                         | See Note 2, except PWM is                            |

| DC25b            | 121                    | 150              | mA         | +85°C                                        | 5.5V                         | operating at maximum speed                           |

| DC25c            | 119                    | 150              | mA         | +125°C                                       |                              | (PTCON2 = 0x0000)                                    |

| DC26d            | 115                    | 140              | mA         | -40°C                                        |                              | 40 MIPS                                              |

| DC26a            | 112                    | 140              | mA         | +25°C                                        | 3.3V                         | See Note 2, except PWM is                            |

| DC26b            | 110                    | 140              | mA         | +85°C                                        | 5.5V                         | operating at 1/2 speed                               |

| DC26c            | 108                    | 140              | mA         | +125°C                                       |                              | (PTCON2 = 0x0001)                                    |

#### TABLE 24-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**2:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU executing while (1) statement

- JTAG disabled

- **3:** These parameters are characterized but not tested in manufacturing.

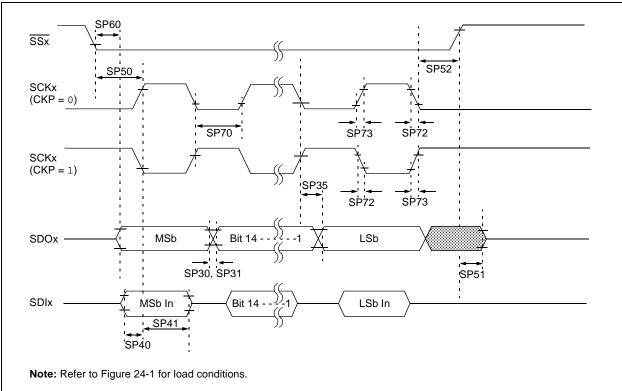

# FIGURE 24-15: SPIx SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# TABLE 24-36:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | Standard Op<br>(unless othe<br>Operating ter | erwise st          | <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|------------------------|----------|-----------------------------------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                          | Тур <sup>(2)</sup> | Max                    | Units    | Conditions                                                      |

| SP70               | TscP                  | Maximum SCKx Input<br>Frequency                              | _                                            | —                  | 15                     | MHz      | See Note 3                                                      |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                            | _                  |                        | ns       | See Parameter DO32 and <b>Note 4</b>                            |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                            | _                  | _                      | ns       | See Parameter DO31 and <b>Note 4</b>                            |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                            | —                  | _                      | ns       | See Parameter DO32 and <b>Note 4</b>                            |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | —                                            | _                  | _                      | ns       | See Parameter DO31 and <b>Note 4</b>                            |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                            | 6                  | 20                     | ns       |                                                                 |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                           | _                  |                        | ns       |                                                                 |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                           | —                  |                        | ns       |                                                                 |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                           | —                  |                        | ns       |                                                                 |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                          | —                  | _                      | ns       |                                                                 |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                           | —                  | 50                     | ns       | See Note 4                                                      |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                 | —                  |                        | ns       | See Note 4                                                      |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

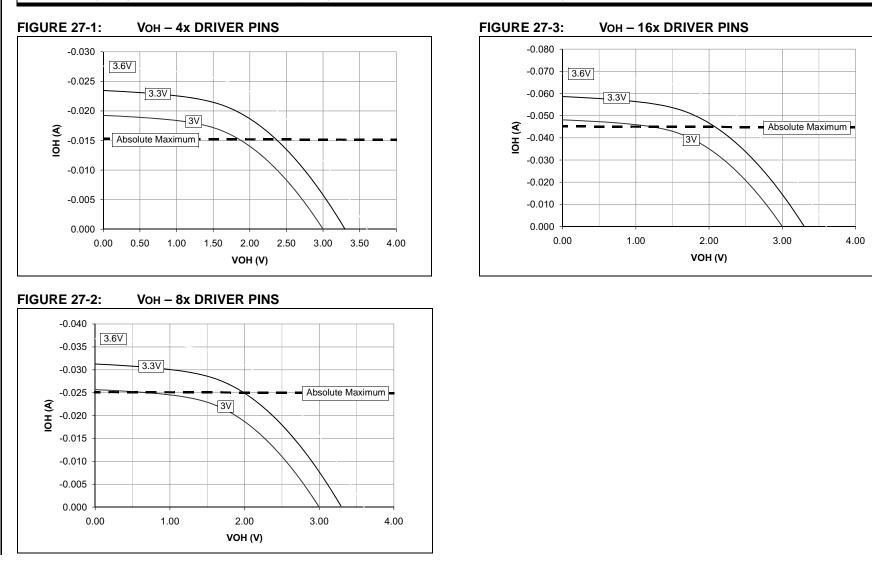

### 27.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

50 MIPS

1:128

50

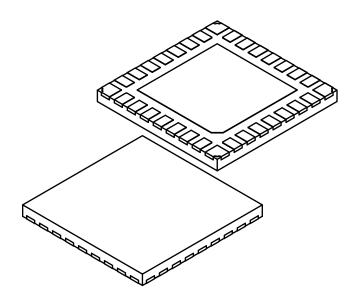

# 28-Lead Plastic Quad Flat, No Lead Package (MX) - 6x6x0.5mm Body [UQFN] Ultra-Thin with 0.40 x 0.60 mm Terminal Width/Length and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Ν      | ILLIMETER | S         |      |

|-------------------------|--------|-----------|-----------|------|

| Dimension               | Limits | MIN       | NOM       | MAX  |

| Number of Pins          | N      |           | 28        |      |

| Pitch                   | е      |           | 0.65 BSC  |      |

| Overall Height          | Α      | 0.40      | 0.50      | 0.60 |

| Standoff                | A1     | 0.00      | 0.02      | 0.05 |

| Terminal Thickness      | (A3)   |           | 0.127 REF |      |

| Overall Width           | E      | 6.00 BSC  |           |      |

| Exposed Pad Width       | E2     |           | 4.00      |      |

| Overall Length          | D      |           | 6.00 BSC  |      |

| Exposed Pad Length      | D2     |           | 4.00      |      |

| Terminal Width          | b      | 0.35      | 0.40      | 0.45 |

| Corner Pad              | b2     | 0.25      | 0.40      | 0.45 |

| Terminal Length         | L      | 0.55      | 0.60      | 0.65 |

| Terminal-to-Exposed Pad | K      | 0.20      | -         | -    |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 4. Outermost portions of corner structures may vary slightly.

Microchip Technology Drawing C04-0209B Sheet 2 of 2

| TABLE A-2: | MAJOR SECTION UPDATES (CONTINUED) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Section Name                                                          | Update Description                                                                                                            |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Section 8.0 "Oscillator                                               | Added Note 2 to the Oscillator System Diagram (see Figure 8-1).                                                               |

| Configuration"                                                        | Added a paragraph regarding FRC accuracy at the end of <b>Section 8.1.1</b> "System Clock Sources".                           |

|                                                                       | Added Note 1 and Note 2 to the OSCON register (see Register ).                                                                |

|                                                                       | Added Note 1 to the OSCTUN register (see Register 8-4).                                                                       |

|                                                                       | Added Note 3 to Section 8.4.2 "Oscillator Switching Sequence".                                                                |

| Section 10.0 "I/O Ports"                                              | Removed Table 9-1 and added reference to pin diagrams for I/O pin availability and functionality.                             |

|                                                                       | Added paragraph on ADPCFG register default values to <b>Section 10.3</b><br>"Configuring Analog Port Pins".                   |

|                                                                       | Added Note box regarding PPS functionality with input mapping to <b>Section 10.6.2.1 "Input Mapping"</b> .                    |

| Section 15.0 "High-Speed PWM"                                         | Updated Note 2 in the PTCON register (see Register 15-1).                                                                     |

|                                                                       | Added Note 4 to the PWMCONx register (see Register 15-6).                                                                     |

|                                                                       | Updated Notes for the PHASEx and SPHASEx registers (see Register 15-9 and Register 15-10, respectively).                      |

| Section 16.0 "Serial Peripheral<br>Interface (SPI)"                   | Added Note 2 and Note 3 to the SPIxCON1 register (see Register 16-2).                                                         |

| Section 18.0 "Universal                                               | Updated the Notes in the UxMode register (see Register 18-1).                                                                 |

| Asynchronous Receiver Transmitter<br>(UART)"                          | Updated the UTXINV bit settings in the UxSTA register and added Note 1 (see Register 18-2).                                   |

| Section 19.0 "High-Speed 10-bit<br>Analog-to-Digital Converter (ADC)" | Updated the SLOWCLK and ADCS<2:0> bit settings and updated Note 1in the ADCON register (see Register 19-1).                   |

|                                                                       | Removed all notes in the ADPCFG register and replaced them with a single note (see Register 19-4).                            |

|                                                                       | Updated the SWTRGx bit settings in the ADCPCx registers (see Register 19-5, Register 19-6, Register 19-7, and Register 19-8). |

| Section Name                                 | Update Description                                                                                                                                                                 |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 24.0 "Electrical<br>Characteristics" | Updated Typical values for Thermal Packaging Characteristics (see Table 24-3).                                                                                                     |

|                                              | Updated Min and Max values for Parameter DC12 (RAM Data Retention Voltage) and added Note 4 (see Table 24-4).                                                                      |