Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

XFI

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 21                                                                                 |

| Program Memory Size        | 16KB (16K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 28-VQFN Exposed Pad                                                                |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402t-50i-mm |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3 Special MCU Features

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices feature a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (1.0).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices support 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

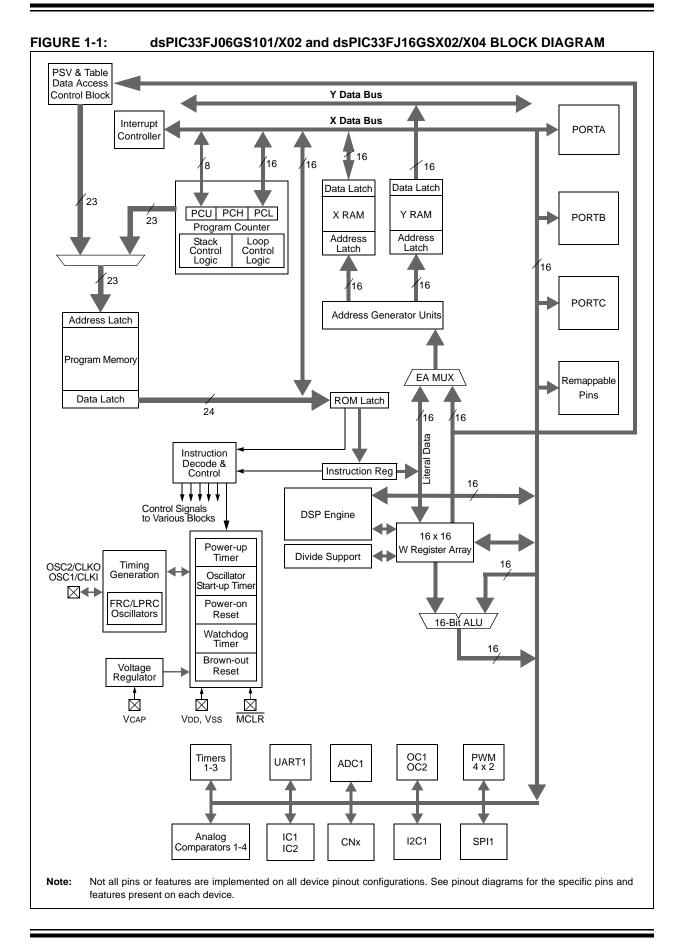

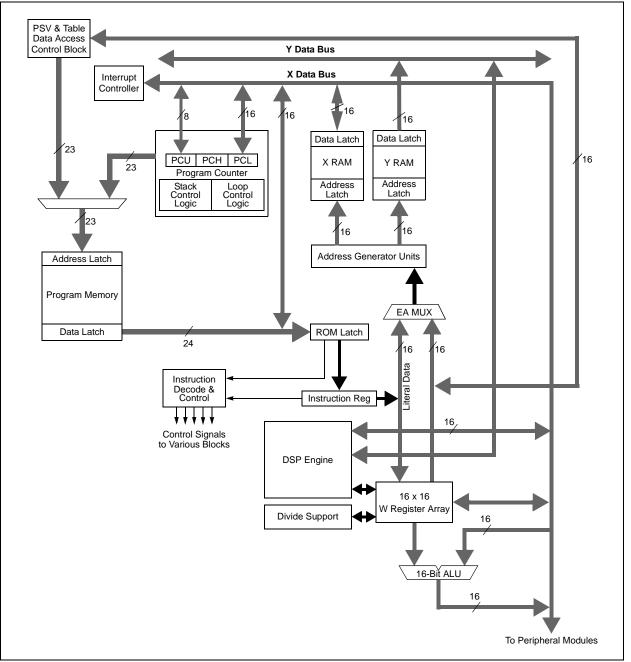

FIGURE 3-1: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 CPU CORE BLOCK DIAGRAM

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3          | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------|----------|----------|----------------|----------|----------|----------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | —        | MATHERR  | ADDRERR        | STKERR   | OSCFAIL  | _        | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     |          |          | _       |          | _        | _        | _        | _        | _        | _        | _              | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084        | _       | —        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | —        | T1IF           | OC1IF    | IC1IF    | INTOIF   | 0000          |

| IFS1         | 0086        | _       | _        | INT2IF   | _        | —       | _        | _        | _        | —        | _        | _        | INT1IF   | CNIF           | _        | MI2C1IF  | SI2C1IF  | 0000          |

| IFS3         | 008A        | -       |          | _        | _        | _       | _        | PSEMIF   | _        | _        | _        | _        | _        | _              | _        | _        | _        | 0000          |

| IFS4         | 008C        | -       |          | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _              | _        | U1EIF    | _        | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF   | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _              | _        | _        | _        | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _              | _        | _        | PWM3IF   | 0000          |

| IFS7         | 0092        | _       | _        | —        | _        | —       | —        | —        |          | —        | _        | —        | —        |                |          | ADCP3IF  | ADCP2IF  | 0000          |

| IEC0         | 0094        | -       | _        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | —        | T1IE           | OC1IE    | IC1IE    | INTOIE   | 0000          |

| IEC1         | 0096        | -       | _        | INT2IE   | —        | _       |          | —        |          | -        |          | —        | INT1IE   | CNIE           |          | MI2C1IE  | SI2C1IE  | 0000          |

| IEC3         | 009A        | -       | _        | —        | —        | _       |          | PSEMIE   |          | -        |          | —        | _        |                |          |          | _        | 0000          |

| IEC4         | 009C        | -       | _        | —        | —        | _       |          | —        |          | -        |          | —        | _        |                |          | U1EIE    | _        | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE   | —        | —        | _       |          | —        |          | -        |          | —        | _        |                |          |          | _        | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  | —        | —        | _       |          | —        |          | -        |          | —        | _        |                |          |          | PWM3IE   | 0000          |

| IEC7         | 00A2        | -       | _        | —        | —        | _       |          | —        |          | -        |          | —        | _        |                |          | ADCP3IE  | ADCP2IE  | 0000          |

| IPC0         | 00A4        | -       | T1IP2    | T1IP1    | T1IP0    | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0   |                | INT0IP2  | INT0IP1  | INT0IP2  | 4444          |

| IPC1         | 00A6        | -       | T2IP2    | T2IP1    | T2IP0    | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0   |                |          |          | _        | 4440          |

| IPC2         | 00A8        | -       | U1RXIP2  | U1RXIP1  | U1RXIP0  | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 |                | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA        | _       | _        | _        | —        | _       | _        | -        |          | -        | ADIP2    | ADIP1    | ADIP0    |                | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC        | —       | CNIP2    | CNIP1    | CNIP0    | —       | _        | —        | _        | —        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | -              | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4044          |

| IPC5         | 00AE        | _       | _        | _        | —        | _       | _        | -        |          | -        |          | -        | -        |                | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC7         | 00B2        | —       | —        | —        | —        | —       | _        | —        | _        | —        | INT2IP2  | INT2IP1  | INT2IP0  | -              | -        | -        | —        | 0040          |

| IPC14        | 00C0        | —       | —        | —        | —        | —       | _        | —        | _        | —        | PSEMIP2  | PSEMIP1  | PSEMIP0  | -              | -        | -        | —        | 0040          |

| IPC16        | 00C4        | -       | _        | —        | —        | _       |          | —        |          | -        | U1EIP2   | U1EIP1   | U1EIP0   |                |          |          | _        | 0040          |

| IPC23        | 00D2        | _       | PWM2IP2  | PWM2IP1  | PWM2IP0  | —       | PWM1IP2  | PWM1IP1  | PWM1IP0  |          |          | —        |          | _              | _        |          | _        | 4400          |

| IPC24        | 00D4        | _       | —        | _        | —        | —       | _        | —        | —        | —        | _        | —        | —        | _              | PWM3IP2  | PWM3IP1  | PWM3IP0  | 0004          |

| IPC27        | 00DA        | _       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | —       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 |          |          | _        |          |                |          | -        | _        | 4400          |

| IPC28        | 00DC        | _       |          | _        | _        | —       |          | _        | _        | —        | ADCP3IP2 | ADCP3IP1 | ADCP3IP0 | _              | ADCP2IP2 | ADCP2IP1 | ADCP2IP0 | 0044          |

| INTTREG      | 00E0        | _       | _        | _        | _        | ILR3    | ILR2     | ILR1     | ILR0     | _        | VECNUM6  | VECNUM5  | VECNUM4  | <b>VECNUM3</b> | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

#### TABLE 4-8. INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33E.116GS402/404 DEVICES ONLY

Legend: x = unknown value on Reset, ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.2 RTSP Operation

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 24-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the Table Write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

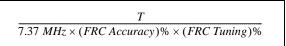

The programming time depends on the FRC accuracy (see Table 24-20) and the value of the FRC Oscillator Tuning register (see Register 8-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time, and Word Write Cycle Time parameters (see Table 24-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 8-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

#### 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

| R/W-0        | R-0                                                                       | U-0                | U-0      | U-0              | U-0             | U-0             | U-0    |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------|--------------------|----------|------------------|-----------------|-----------------|--------|--|--|--|--|--|

| ALTIVT       | DISI                                                                      | —                  |          | _                | —               |                 |        |  |  |  |  |  |

| oit 15       |                                                                           |                    |          |                  |                 |                 | bit 8  |  |  |  |  |  |

|              |                                                                           |                    |          |                  |                 |                 |        |  |  |  |  |  |

| U-0          | U-0                                                                       | U-0                | U-0      | U-0              | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |  |

| —            |                                                                           |                    | _        | —                | INT2EP          | INT1EP          | INT0EP |  |  |  |  |  |

| bit 7        |                                                                           |                    |          |                  |                 |                 | bit C  |  |  |  |  |  |

|              |                                                                           |                    |          |                  |                 |                 |        |  |  |  |  |  |

| Legend:      |                                                                           |                    |          |                  |                 |                 |        |  |  |  |  |  |

| R = Readab   |                                                                           | W = Writable I     | oit      | •                | mented bit, rea |                 |        |  |  |  |  |  |

| -n = Value a | t POR                                                                     | '1' = Bit is set   |          | '0' = Bit is cle | eared           | x = Bit is unkr | nown   |  |  |  |  |  |

|              |                                                                           |                    |          |                  |                 |                 |        |  |  |  |  |  |

| bit 15       | ALTIVT: Enable Alternate Interrupt Vector Table bit                       |                    |          |                  |                 |                 |        |  |  |  |  |  |

|              | 1 = Use alternate vector table<br>0 = Use standard (default) vector table |                    |          |                  |                 |                 |        |  |  |  |  |  |

| bit 14       |                                                                           | · · ·              |          |                  |                 |                 |        |  |  |  |  |  |

| DIT 14       | DISI Instruction Status bit                                               |                    |          |                  |                 |                 |        |  |  |  |  |  |

|              | 1 = DISI instruction is active<br>0 = DISI instruction is not active      |                    |          |                  |                 |                 |        |  |  |  |  |  |

| bit 13-3     |                                                                           | ented: Read as '0  |          |                  |                 |                 |        |  |  |  |  |  |

| bit 2        | INT2EP: External Interrupt 2 Edge Detect Polarity Select bit              |                    |          |                  |                 |                 |        |  |  |  |  |  |

|              | 1 = Interrupt on negative edge                                            |                    |          |                  |                 |                 |        |  |  |  |  |  |

|              | 0 = Interrupt on positive edge                                            |                    |          |                  |                 |                 |        |  |  |  |  |  |

| bit 1        | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit              |                    |          |                  |                 |                 |        |  |  |  |  |  |

|              | 1 = Interrupt on negative edge                                            |                    |          |                  |                 |                 |        |  |  |  |  |  |

|              | 0 = Interrup                                                              | t on positive edge | Э        |                  |                 |                 |        |  |  |  |  |  |

| bit 0        |                                                                           | ternal Interrupt 0 | •        | t Polarity Selec | t bit           |                 |        |  |  |  |  |  |

|              | •                                                                         | t on negative edg  |          |                  |                 |                 |        |  |  |  |  |  |

|              | 0 – Interrun                                                              | t on positive edge | <b>`</b> |                  |                 |                 |        |  |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0          | R/W-1                                                            | R/W-0                    | R/W-0           | U-0             | R/W-1            | R/W-0           | R/W-0    |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------|--------------------------|-----------------|-----------------|------------------|-----------------|----------|--|--|--|--|--|--|

| —            | ADCP5IP2                                                         | ADCP5IP1                 | ADCP5IP0        | —               | ADCP4IP2         | ADCP4IP1        | ADCP4IP0 |  |  |  |  |  |  |

| bit 15       |                                                                  |                          |                 |                 |                  |                 | bit      |  |  |  |  |  |  |

|              | <b>D</b> 444 4                                                   | DAM 0                    | DAM 0           |                 |                  | <b>D</b> 4440   | DAMA     |  |  |  |  |  |  |

| U-0          | R/W-1                                                            | R/W-0                    | R/W-0           | U-0             | R/W-1            | R/W-0           | R/W-0    |  |  |  |  |  |  |

| <br>bit 7    | ADCP3IP2                                                         | ADCP3IP1                 | ADCP3IP0        |                 | ADCP2IP2         | ADCP2IP1        | ADCP2IP( |  |  |  |  |  |  |

| DIL 7        |                                                                  |                          |                 |                 |                  |                 | bit      |  |  |  |  |  |  |

| Legend:      |                                                                  |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

| R = Readab   | le bit                                                           | W = Writable             | bit             | U = Unimple     | mented bit, read | l as '0'        |          |  |  |  |  |  |  |

| -n = Value a | t POR                                                            | '1' = Bit is set         |                 | '0' = Bit is cl | eared            | x = Bit is unkr | nown     |  |  |  |  |  |  |

|              |                                                                  |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

| bit 15       | Unimplemen                                                       | ted: Read as '           | 0'              |                 |                  |                 |          |  |  |  |  |  |  |

| bit 14-12    | ADCP5IP<2:                                                       | 0>: ADC Pair 5           | Conversion E    | Oone Interrupt  | Priority bits    |                 |          |  |  |  |  |  |  |

|              | 111 = Interru                                                    | pt is Priority 7 (       | highest priorit | y interrupt)    |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                    |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 000 = Interru                                                    | pt source is dis         | abled           |                 |                  |                 |          |  |  |  |  |  |  |

| bit 11       | Unimplemen                                                       | ted: Read as '           | 0'              |                 |                  |                 |          |  |  |  |  |  |  |

| bit 10-8     | ADCP4IP<2:0>: ADC Pair 4 Conversion Done Interrupt Priority bits |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)       |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                    |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 000 = Interru                                                    | pt source is dis         | abled           |                 |                  |                 |          |  |  |  |  |  |  |

| bit 7        | Unimplemen                                                       | ted: Read as '           | 0'              |                 |                  |                 |          |  |  |  |  |  |  |

| bit 6-4      | ADCP3IP<2:0>: ADC Pair 3 Conversion Done Interrupt Priority bits |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)       |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                    |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 000 = Interrupt source is disabled                               |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

| bit 3        | Unimplemen                                                       | ted: Read as '           | 0'              |                 |                  |                 |          |  |  |  |  |  |  |

| bit 2-0      | ADCP2IP<2:                                                       | <b>0&gt;:</b> ADC Pair 2 | Conversion      | Oone Interrupt  | Priority bits    |                 |          |  |  |  |  |  |  |

|              | 111 = Interru                                                    | pt is Priority 7 (       | highest priorit | y interrupt)    |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | •                                                                |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              |                                                                  |                          |                 |                 |                  |                 |          |  |  |  |  |  |  |

|              | 001 = Interru                                                    | ot is Prioritv 1         |                 |                 |                  |                 |          |  |  |  |  |  |  |

#### IDC20. INTERRURT PRIORITY CONTROL RECIETER 20

NOTES:

| R/W-0            | R/W-0                                                                      | R/W-0                                                                                                    | R/W-0                                                                                 | R/W-0                                                | R/W-0             | R/W-0           | R/W-0 |

|------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|-----------------|-------|

| PHR              | PHF                                                                        | PLR                                                                                                      | PLF                                                                                   | FLTLEBEN                                             | CLLEBEN           | LEB6            | LEB5  |

| bit 15           |                                                                            |                                                                                                          |                                                                                       |                                                      |                   |                 | bit 8 |

| R/W-0            | R/W-0                                                                      | R/W-0                                                                                                    | R/W-0                                                                                 | R/W-0                                                | U-0               | U-0             | U-0   |

| LEB4             | LEB3                                                                       | LEB2                                                                                                     | LEB1                                                                                  | LEB0                                                 |                   |                 | _     |

| bit 7            | 2200                                                                       |                                                                                                          |                                                                                       | 2200                                                 |                   |                 | bit ( |

| Legend:          |                                                                            |                                                                                                          |                                                                                       |                                                      |                   |                 |       |

| R = Readable     | bit                                                                        | W = Writable                                                                                             | bit                                                                                   | U = Unimplen                                         | nented bit, read  | as '0'          |       |

| -n = Value at I  | POR                                                                        | '1' = Bit is set                                                                                         |                                                                                       | '0' = Bit is clea                                    |                   | x = Bit is unkr | nown  |

| bit 14<br>bit 13 | PHF: PWMH<br>1 = Falling ec<br>0 = LEB ignor<br>PLR: PWML<br>1 = Rising ed | res the rising e<br>Falling Edge T<br>Ige of PWMxH<br>res the falling e<br>Rising Edge Tr<br>ge of PWMxL | rigger Enable<br>will trigger the<br>edge of PWM<br>rigger Enable<br>will trigger the | e bit<br>e LEB counter<br>xH<br>bit<br>e LEB counter |                   |                 |       |

| bit 12           | PLF: PWML I<br>1 = Falling ed                                              | res the rising e<br>Falling Edge Ti<br>Ige of PWMxL<br>res the falling e                                 | igger Enable<br>will trigger the                                                      | bit<br>e LEB counter                                 |                   |                 |       |

| bit 11           | 1 = Leading-E                                                              |                                                                                                          | is applied to s                                                                       | selected Fault in<br>to selected Fau                 |                   |                 |       |

| bit 10           | 1 = Leading-E                                                              |                                                                                                          | is applied to s                                                                       | selected current<br>to selected cur                  |                   |                 |       |

| bit 9-3          | The value is 8                                                             | 3.32 nsec incre                                                                                          | ments.                                                                                | urrent-Limit and                                     | Fault Inputs bits | 5               |       |

| bit 2-0          | Unimplemen                                                                 | ted: Read as '                                                                                           | 0'                                                                                    |                                                      |                   |                 |       |

| 51120            | •                                                                          |                                                                                                          |                                                                                       |                                                      |                   |                 |       |

### REGISTER 15-18: LEBCONx: LEADING-EDGE BLANKING CONTROL REGISTER<sup>(1)</sup>

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | <b>URXINV:</b> UARTx Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <b>BRGH:</b> High Baud Rate Enable bit<br>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)<br>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode) |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                              |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                                      |

- **Note 1:** Refer to "**UART**" (DS70188) in the "*dsPIC33F/PIC24H Family Reference Manual*" for information on enabling the UART module for receive or transmit operation.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5  | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <ul> <li>1 = Address Detect mode is enable; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                    |

| bit 4  | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                            |

|        | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                           |

| bit 3  | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                       |

|        | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                     |

| bit 2  | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                      |

|        | <ul> <li>1 = Framing error has been detected for the current character (character at the top of the receive<br/>FIFO)</li> </ul>                                                                                                |

|        | 0 = Framing error has not been detected                                                                                                                                                                                         |

| bit 1  | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                                 |

|        | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) will reset<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0  | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                      |

|        | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                   |

| Note 1 | Poter to "ILAPT" (DS70188) in the "deDIC22E/DIC24H Family Poteronee Manual" for information on                                                                                                                                  |

**Note 1:** Refer to "**UART**" (DS70188) in the "*dsPIC33F/PIC24H Family Reference Manual*" for information on enabling the UART module for transmit operation.

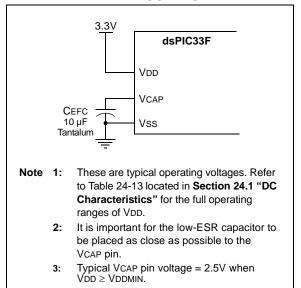

#### 21.2 On-Chip Voltage Regulator

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 21-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 24-13 located in **Section 24.1 "DC Characteristics"**.

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 21-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### 21.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

### 22.0 INSTRUCTION SET SUMMARY

**Note:** This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest sections in the "dsPIC33F/PIC24H Family Reference Manual", which are available on the Microchip web site (www.microchip.com).

The dsPIC33F instruction set is identical to that of the dsPIC30F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 22-1 shows the general symbols used in describing the instructions.

The dsPIC33F instruction set summary in Table 22-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could be either the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register, 'Wn', or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

#### 23.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 23.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 23.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 23.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 23.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### 24.2 AC Characteristics and Timing Parameters

This section defines dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 AC characteristics and timing parameters.

#### TABLE 24-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V                                 |  |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                    | (unless otherwise stated)                                                   |  |  |  |  |  |  |  |

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |  |  |  |  |  |  |

|                    | -40°C $\leq$ TA $\leq$ +125°C for Extended                                  |  |  |  |  |  |  |  |

|                    | Operating voltage VDD range as described in Table 24-1.                     |  |  |  |  |  |  |  |

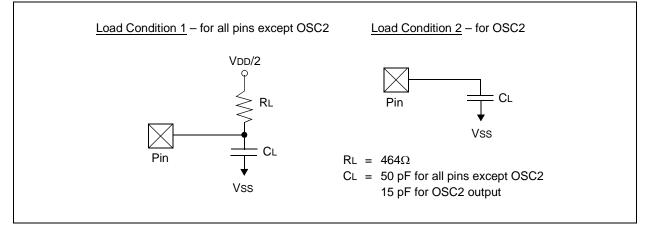

#### FIGURE 24-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 24-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Max | Units | Conditions                                                      |

|--------------|--------|-----------------------|-----|-----|-----|-------|-----------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              |     | _   | 15  | -     | In XT and HS modes when external<br>clock is used to drive OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —   | —   | 50  | pF    | EC mode                                                         |

| DO58         | Св     | SCLx, SDAx            | _   | _   | 400 | pF    | In I <sup>2</sup> C™ mode                                       |

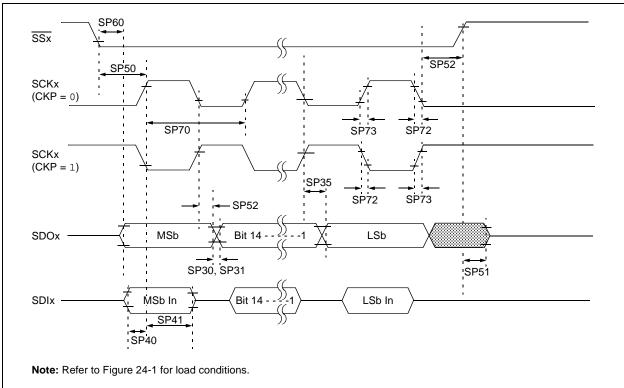

# FIGURE 24-16: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

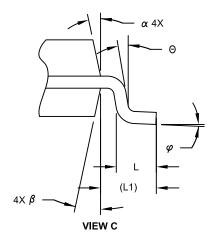

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | N         | MILLIMETERS |           |      |  |  |  |

|--------------------------|-----------|-------------|-----------|------|--|--|--|

| Dimension                | Limits    | MIN         | NOM       | MAX  |  |  |  |

| Number of Pins           | N         |             | 28        |      |  |  |  |

| Pitch                    | е         |             | 1.27 BSC  |      |  |  |  |

| Overall Height           | A         | -           | -         | 2.65 |  |  |  |

| Molded Package Thickness | A2        | 2.05        | -         | -    |  |  |  |

| Standoff §               | A1        | 0.10        | -         | 0.30 |  |  |  |

| Overall Width            | E         |             | 10.30 BSC |      |  |  |  |

| Molded Package Width     | E1        | 7.50 BSC    |           |      |  |  |  |

| Overall Length           | D         |             | 17.90 BSC |      |  |  |  |

| Chamfer (Optional)       | h         | 0.25        | -         | 0.75 |  |  |  |

| Foot Length              | L         | 0.40        | -         | 1.27 |  |  |  |

| Footprint                | L1        | 1.40 REF    |           |      |  |  |  |

| Lead Angle               | Θ         | 0°          | -         | -    |  |  |  |

| Foot Angle               | $\varphi$ | 0°          | -         | 8°   |  |  |  |

| Lead Thickness           | С         | 0.18        | -         | 0.33 |  |  |  |

| Lead Width               | b         | 0.31        | -         | 0.51 |  |  |  |

| Mold Draft Angle Top     | α         | 5°          | -         | 15°  |  |  |  |

| Mold Draft Angle Bottom  | β         | 5°          | -         | 15°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

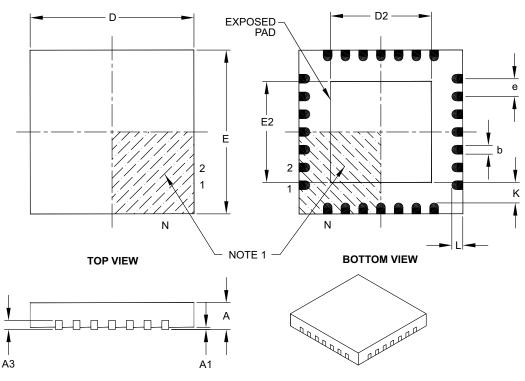

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units       |          | MILLIMETERS | 5    |

|------------------------|-------------|----------|-------------|------|

| Dimens                 | sion Limits | MIN      | NOM         | MAX  |

| Number of Pins         | Ν           |          | 28          |      |

| Pitch                  | е           |          | 0.65 BSC    |      |

| Overall Height         | А           | 0.80     | 0.90        | 1.00 |

| Standoff               | A1          | 0.00     | 0.02        | 0.05 |

| Contact Thickness      | A3          | 0.20 REF |             |      |

| Overall Width          | E           | 6.00 BSC |             |      |

| Exposed Pad Width      | E2          | 3.65     | 3.70        | 4.70 |

| Overall Length         | D           |          | 6.00 BSC    |      |

| Exposed Pad Length     | D2          | 3.65     | 3.70        | 4.70 |

| Contact Width          | b           | 0.23     | 0.38        | 0.43 |

| Contact Length         | L           | 0.30     | 0.40        | 0.50 |

| Contact-to-Exposed Pad | К           | 0.20     | -           | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124B

| TABLE A-1: | MAJOR SECTION UPDATES (CONTINUED) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Section Name                                 | Update Description                                                                                                                                                                                                                            |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 23.0 "Electrical<br>Characteristics" | Updated Typ values for Thermal Packaging Characteristics (Table 23-3).                                                                                                                                                                        |

|                                              | Removed Typ value for DC Temperature and Voltage Specifications Parameter DC12 (Table 23-4).                                                                                                                                                  |

|                                              | Updated all Typ values and conditions for DC Characteristics: Operating Current (IDD), updated last sentence in Note 2 (Table 23-5).                                                                                                          |

|                                              | Updated all Typ values for DC Characteristics: Idle Current (IIDLE) (see Table 23-6).                                                                                                                                                         |

|                                              | Updated all Typ values for DC Characteristics: Power Down Current (IPD) (see Table 23-7).                                                                                                                                                     |

|                                              | Updated all Typ values for DC Characteristics: Doze Current (IDOZE) (see Table 23-8).                                                                                                                                                         |

|                                              | Added Note 4 (reference to new table containing digital-only and analog pin information, as well as Current Sink/Source capabilities) in the I/O Pin Input Specifications (Table 23-9).                                                       |

|                                              | Updated Max value for BOR electrical characteristics Parameter BO10 (see Table 23-11).                                                                                                                                                        |

|                                              | Swapped Min and Typ values for Program Memory Parameters D136 and D137 (Table 23-12).                                                                                                                                                         |

|                                              | Updated Typ values for Internal RC Accuracy Parameter F20 and added Extended temperature range to table heading (see Table 23-19).                                                                                                            |

|                                              | Removed all values for Reset, Watchdog Timer, Oscillator Start-up Timer, and Power-up Timer Parameter SY20 and updated conditions, which now refers to <b>Section 20.4 "Watchdog Timer (WDT)</b> " and LPRC Parameter F21a (see Table 23-22). |

|                                              | Added specifications to High-Speed PWM Module Timing Requirements for Tap Delay (Table 23-29).                                                                                                                                                |

|                                              | Updated Min and Max values for 10-bit High-Speed Analog-to-Digital Module Parameters AD01 and AD11 (see Table 23-36).                                                                                                                         |

|                                              | Updated Max value and unit of measure for DAC AC Specification (see Table 23-40).                                                                                                                                                             |

NOTES:

NOTES: