Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402t-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

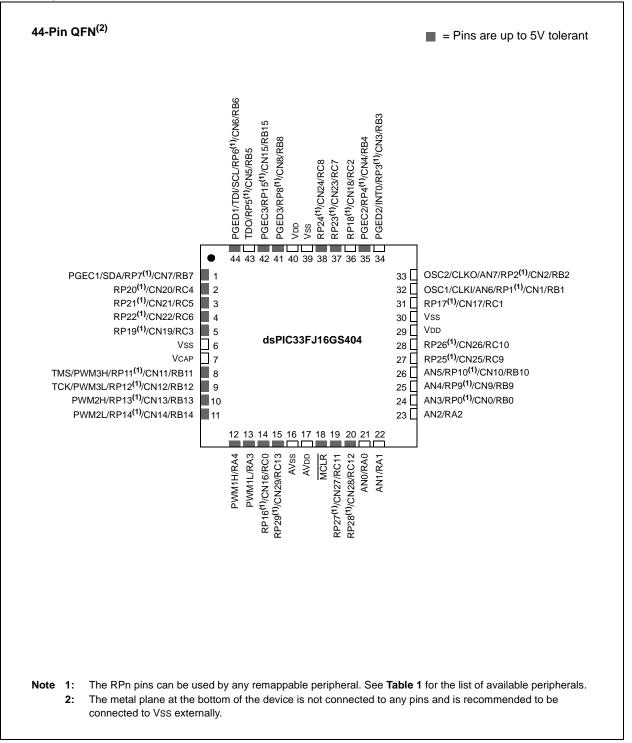

### Pin Diagrams (Continued)

| File Name | SFR<br>Addr | Bit 15   | Bit 14              | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9           | Bit 8        | Bit 7 | Bit 6   | Bit 5    | Bit 4          | Bit 3      | Bit 2     | Bit 1      | Bit 0 | All<br>Resets |

|-----------|-------------|----------|---------------------|----------|----------|----------|----------|-----------------|--------------|-------|---------|----------|----------------|------------|-----------|------------|-------|---------------|

| WREG0     | 0000        |          |                     |          |          |          |          | Working Regi    | ster 0       |       |         |          |                |            |           |            |       | 0000          |

| WREG1     | 0002        |          |                     |          |          |          |          | Working Regi    | ster 1       |       |         |          |                |            |           |            |       | 0000          |

| WREG2     | 0004        |          |                     |          |          |          |          | Working Regi    | ster 2       |       |         |          |                |            |           |            |       | 0000          |

| WREG3     | 0006        |          |                     |          |          |          |          | Working Regi    | ster 3       |       |         |          |                |            |           |            |       | 0000          |

| WREG4     | 8000        |          |                     |          |          |          |          | Working Regi    | ster 4       |       |         |          |                |            |           |            |       | 0000          |

| WREG5     | 000A        |          |                     |          |          |          |          | Working Regi    | ster 5       |       |         |          |                |            |           |            |       | 0000          |

| WREG6     | 000C        |          |                     |          |          |          |          | Working Regi    | ster 6       |       |         |          |                |            |           |            |       | 0000          |

| WREG7     | 000E        |          |                     |          |          |          |          | Working Regi    | ster 7       |       |         |          |                |            |           |            |       | 0000          |

| WREG8     | 0010        |          |                     |          |          |          |          | Working Regi    | ster 8       |       |         |          |                |            |           |            |       | 0000          |

| WREG9     | 0012        |          |                     |          |          |          |          | Working Regi    | ster 9       |       |         |          |                |            |           |            |       | 0000          |

| WREG10    | 0014        |          |                     |          |          |          |          | Working Regis   | ter 10       |       |         |          |                |            |           |            |       | 0000          |

| WREG11    | 0016        |          |                     |          |          |          |          | Working Regis   | ster 11      |       |         |          |                |            |           |            |       | 0000          |

| WREG12    | 0018        |          |                     |          |          |          |          | Working Regis   | ter 12       |       |         |          |                |            |           |            |       | 0000          |

| WREG13    | 001A        |          |                     |          |          |          |          | Working Regis   | ter 13       |       |         |          |                |            |           |            |       | 0000          |

| WREG14    | 001C        |          |                     |          |          |          |          | Working Regis   | ter 14       |       |         |          |                |            |           |            |       | 0000          |

| WREG15    | 001E        |          | Working Register 15 |          |          |          |          | 0800            |              |       |         |          |                |            |           |            |       |               |

| SPLIM     | 0020        |          |                     |          |          |          | Sta      | ck Pointer Limi | t Register   |       |         |          |                |            |           |            |       | xxxx          |

| ACCAL     | 0022        |          |                     |          |          |          |          | ACCAL           |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCAH     | 0024        |          |                     |          |          |          |          | ACCAH           |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCAU     | 0026        | ACCA<39> | ACCA<39>            | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39>        | ACCA<39>     |       |         |          | ACCA           | AU         |           |            |       | xxxx          |

| ACCBL     | 0028        |          |                     |          |          |          |          | ACCBL           |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCBH     | 002A        |          |                     |          |          | -        |          | ACCBH           |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCBU     | 002C        | ACCB<39> | ACCB<39>            | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39>        | ACCB<39>     |       |         |          | ACCE           | BU         |           |            |       | XXXX          |

| PCL       | 002E        |          |                     |          |          |          | Program  | Counter Low     | Word Regist  | er    |         |          |                |            |           |            |       | 0000          |

| PCH       | 0030        | _        | _                   |          | —        | —        | —        | _               | _            |       |         | Program  | Counter H      | igh Byte I | Register  |            |       | 0000          |

| TBLPAG    | 0032        | _        |                     | _        | _        | _        | _        | _               | _            |       |         | Table Pa | ge Address     | 8 Pointer  | Register  |            |       | 0000          |

| PSVPAG    | 0034        | _        | —                   | -        | -        | _        | —        | -               | —            |       | Program | Memory \ | /isibility Pag | ge Addres  | ss Pointe | r Register | r     | 0000          |

| RCOUNT    | 0036        |          |                     |          |          |          | REPE     | AT Loop Coun    | ter Register |       |         |          |                |            |           |            |       | xxxx          |

| DCOUNT    | 0038        |          |                     |          |          |          |          | DCOUNT<1        | 5:0>         |       |         |          |                |            |           |            | -     | xxxx          |

| DOSTARTL  | 003A        |          |                     |          |          |          | DOS      | STARTL<15:1:    | >            |       |         |          |                |            |           |            | 0     | xxxx          |

| DOSTARTH  | 003C        | _        | DOSTARTH<5:0>       |          |          |          | 00xx     |                 |              |       |         |          |                |            |           |            |       |               |

| DOENDL    | 003E        |          |                     |          |          |          | DC       | ENDL<15:1>      |              |       |         |          |                |            |           |            | 0     | xxxx          |

| DOENDH    | 0040        | _        | -                   |          | _        | —        | _        | —               | _            | _     | _       |          |                | DOEN       | IDH       |            | -     | 00xx          |

| SR        | 0042        | OA       | OB                  | SA       | SB       | OAB      | SAB      | DA              | DC           | IPL2  | IPL1    | IPL0     | RA             | N          | OV        | Z          | С     | 0000          |

| CORCON    | 0044        | _        | _                   | _        | US       | EDT      | DL2      | DL1             | DL0          | SATA  | SATB    | SATDW    | ACCSAT         | IPL3       | PSV       | RND        | IF    | 0020          |

| MODCON    | 0046        | XMODEN   | YMODEN              | _        | _        | BWM3     | BWM2     | BWM1            | BWM0         | YWM3  | YWM2    | YWM1     | YWM0           | XWM3       | XWM2      | XWM1       | XWM0  | 0000          |

### TABLE 4-1: CPU CORE REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 8.2 Auxiliary Clock Generation

The auxiliary clock generation is used for a peripherals that need to operate at a frequency unrelated to the system clock such as a PWM or ADC.

The primary oscillator and internal FRC oscillator sources can be used with an auxiliary PLL to obtain the auxiliary clock. The auxiliary PLL has a fixed 16x multiplication factor.

The auxiliary clock has the following configuration restrictions:

- For proper PWM operation, auxiliary clock generation must be configured for 120 MHz (see Parameter OS56 in Table 24-18 in Section 24.0 "Electrical Characteristics"). If a slower frequency is desired, the PWM Input Clock Prescaler (Divider) Select bits (PCLKDIV<2:0>) should be used.

- To achieve 1.04 ns PWM resolution, the auxiliary clock must use the 16x auxiliary PLL (APLL). All other clock sources will have a minimum PWM resolution of 8 ns.

- If the primary PLL is used as a source for the auxiliary clock, the primary PLL should be configured up to a maximum operation of 30 MIPS or less

#### 8.3 Reference Clock Generation

The reference clock output logic provides the user with the ability to output a clock signal based on the system clock or the crystal oscillator on a device pin. The user application can specify a wide range of clock scaling prior to outputting the reference clock.

#### 9.2.2 IDLE MODE

The following occur in Idle mode:

- The CPU stops executing instructions

- The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active

The device will wake-up from Idle mode on any of these events:

- Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

### 9.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 9.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

| <b>REGISTER 9-</b>                 | 3: PMD | 3: PERIPHER | AL MODULE                          | DISABLE C | ONTROL RE | GISTER 3 |       |

|------------------------------------|--------|-------------|------------------------------------|-----------|-----------|----------|-------|

| U-0                                | U-0    | U-0         | U-0                                | U-0       | R/W-0     | U-0      | U-0   |

| _                                  | —      | —           | —                                  | —         | CMPMD     | —        | —     |

| bit 15                             |        |             |                                    |           |           |          | bit 8 |

|                                    |        |             |                                    |           |           |          |       |

| U-0                                | U-0    | U-0         | U-0                                | U-0       | U-0       | U-0      | U-0   |

| —                                  | —      | —           | —                                  | —         | —         | —        | —     |

| bit 7                              |        |             |                                    |           |           |          | bit 0 |

|                                    |        |             |                                    |           |           |          |       |

| Legend:                            |        |             |                                    |           |           |          |       |

| R = Readable bit W = Writable bit  |        | bit         | U = Unimplemented bit, read as '0' |           |           |          |       |

| -n = Value at POR '1' = Bit is set |        |             | '0' = Bit is cleared x = Bit is    |           |           | nown     |       |

|                                    |        |             |                                    |           |           |          |       |

| bit 15-11 | Unimplemented: Read as '0'                               |

|-----------|----------------------------------------------------------|

| bit 10    | CMPMD: Analog Comparator Module Disable bit              |

|           | <ol> <li>Analog comparator module is disabled</li> </ol> |

|           | 0 = Analog comparator module is enabled                  |

| bit 9-0   | Unimplemented: Read as '0'                               |

#### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 3 **REFOMD**: Reference Clock Generator Module Disable bit

1 = Reference clock generator module is disabled

- 0 = Reference clock generator module is enabled

- bit 2-0 Unimplemented: Read as '0'

#### 10.6.2.3 Virtual Pins

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices support four virtual RPn pins (RP32, RP33, RP34 and RP35), which are identical in functionality to all other RPn pins, with the exception of pinouts. These four pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP32 and the PWM Fault input can be configured for RP32 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

# 10.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 10.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C language functions for unlocking the OSCCON register: |

|-------|--------------------------------------------------------------------------------------------------|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                     |

|       | See the MPLAB C30 Help files for more information.                                               |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 10.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent many write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP19R5 | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

**RP18R3**

**RP18R2**

**RP18R1**

**RP18R0**

bit 0

RP18R4

### REGISTER 10-24: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

**RP18R5**

bit 7

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP19R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP19 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP18R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP18 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

| U-0                                | U-0        | R/W-0          | R/W-0                                    | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |

|------------------------------------|------------|----------------|------------------------------------------|------------------------------------|--------|--------|--------|--|

| _                                  |            | RP21R5         | RP21R4                                   | RP21R3                             | RP21R2 | RP21R1 | RP21R0 |  |

| bit 15                             |            |                |                                          |                                    |        |        | bit 8  |  |

|                                    |            |                |                                          |                                    |        |        |        |  |

| U-0                                | U-0        | R/W-0          | R/W-0                                    | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |

| —                                  | —          | RP20R5         | RP20R4                                   | RP20R3                             | RP20R2 | RP20R1 | RP20R0 |  |

| bit 7                              |            |                |                                          |                                    |        | •      | bit 0  |  |

|                                    |            |                |                                          |                                    |        |        |        |  |

| Legend:                            |            |                |                                          |                                    |        |        |        |  |

| R = Readable                       | bit        | W = Writable   | bit                                      | U = Unimplemented bit, read as '0' |        |        |        |  |

| -n = Value at POR '1' = Bit is set |            |                | 0' = Bit is cleared $x = Bit is unknown$ |                                    |        |        |        |  |

|                                    |            |                |                                          |                                    |        |        |        |  |

| bit 15-14                          | Unimplemen | ted: Read as ' | כ'                                       |                                    |        |        |        |  |

### REGISTER 10-25: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10<sup>(1)</sup>

| bit 13-8 | <b>RP21R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP21 Output Pin bits (see Table 10-2 for peripheral function numbers) |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                               |

|          |                                                                                                                                          |

bit 5-0 **RP20R<5:0>:** Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 10-2 for peripheral function numbers)

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

| HS/HC-0      | ) HS/HC-0                | HS/HC-0                                                        | R/W-0                        | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

|--------------|--------------------------|----------------------------------------------------------------|------------------------------|------------------|----------------------|----------------------|---------------------|

| FLTSTAT(     | 1) CLSTAT <sup>(1)</sup> | TRGSTAT                                                        | FLTIEN                       | CLIEN            | TRGIEN               | ITB <sup>(3)</sup>   | MDCS <sup>(3)</sup> |

| bit 15       | ł                        |                                                                |                              |                  |                      |                      | bit 8               |

|              |                          |                                                                |                              |                  |                      |                      |                     |

| R/W-0        | R/W-0                    | U-0                                                            | U-0                          | U-0              | R/W-0                | R/W-0                | R/W-0               |

| DTC1         | DTC0                     | —                                                              | —                            |                  | CAM <sup>(2,3)</sup> | XPRES <sup>(4)</sup> | IUE                 |

| bit 7        |                          |                                                                |                              |                  |                      |                      | bit                 |

| Legend:      |                          | HC = Hardware                                                  | Clearable bit                | HS = Hardw       | are Settable bi      | it                   |                     |

| R = Readal   | hle hit                  | W = Writable bit                                               |                              |                  | mented bit, rea      |                      |                     |

| -n = Value a |                          | '1' = Bit is set                                               |                              | '0' = Bit is cle |                      | x = Bit is unl       | nown                |

|              |                          | 1 – Dit 13 Set                                                 |                              |                  | caleu                |                      | NIOWII              |

| bit 15       | FLTSTAT: F               | ault Interrupt Statu                                           | us bit <sup>(1)</sup>        |                  |                      |                      |                     |

|              |                          | rrupt is pending                                               |                              |                  |                      |                      |                     |

|              |                          | interrupt is pendin                                            | g; this bit is cle           | ared by setting  | FLTIEN = 0           |                      |                     |

| bit 14       | CLSTAT: Cu               | urrent-Limit Interru                                           | pt Status bit <sup>(1)</sup> |                  |                      |                      |                     |

|              |                          | mit interrupt is per<br>nt-limit interrupt is                  | Q                            | t is cleared by  | setting CLIEN        | = 0                  |                     |

| bit 13       | TRGSTAT: Tr              | rigger Interrupt Sta                                           | itus bit                     |                  |                      |                      |                     |

|              |                          | terrupt is pending                                             |                              |                  |                      |                      |                     |

|              | 0 = No trigge            | r interrupt is pendi                                           | ng; this bit is cl           | eared by settin  | g TRGIEN = 0         | )                    |                     |

| bit 12       | FLTIEN: Fai              | ult Interrupt Enable                                           | e bit                        |                  |                      |                      |                     |

|              |                          | 1 = Fault interrupt is enabled                                 |                              |                  |                      |                      |                     |

|              |                          | 0 = Fault interrupt is disabled and the FLTSTAT bit is cleared |                              |                  |                      |                      |                     |

| bit 11       |                          | rent-Limit Interrupt                                           |                              |                  |                      |                      |                     |

|              |                          | mit interrupt is ena<br>mit interrupt is dis                   |                              | CLSTAT bit is c  | leared               |                      |                     |

| bit 10       | TRGIEN: Trig             | ger Interrupt Enat                                             | ole bit                      |                  |                      |                      |                     |

|              |                          | event generates a<br>vent interrupts are                       |                              |                  | it is cleared        |                      |                     |

| bit 9        | ITB: Indepe              | ndent Time Base I                                              | Mode bit <sup>(3)</sup>      |                  |                      |                      |                     |

|              | 1 = PHASEx/              | /SPHASEx registe<br>egister provides tir                       | r provides time              |                  | r this PWM ge        | enerator             |                     |

| bit 8        |                          | ster Duty Cycle Re                                             | -                            |                  |                      |                      |                     |

|              |                          | ister provides duty<br>Cx register provid                      |                              |                  |                      | erator               |                     |

| bit 7-6      |                          | ead-Time Control                                               |                              |                  | lie i till gene      |                      |                     |

|              | 11 = Reserve             |                                                                | 513                          |                  |                      |                      |                     |

|              |                          | ne function is disa                                            | bled                         |                  |                      |                      |                     |

|              |                          | e dead time is acti<br>dead time is activ                      |                              |                  |                      |                      |                     |

| bit 5-3      |                          | ited: Read as '0'                                              | - ,                          |                  |                      |                      |                     |

| Note 1:      | Software must clo        | ar the interrupt sta                                           | tue here and th              | e correspondir   | a IFSy hit in t      | he interrupt or      | ontroller           |

| 2:           |                          | Time Base mode (                                               |                              |                  | -                    | -                    |                     |

| 3:           | These bits should        | be changed only v                                              | when PTEN = 0                | . Changing the   | e clock selectio     | on during ope        | ration will         |

|              |                          | d unpredictable results.                                       |                              |                  |                      |                      |                     |

#### REGISTER 15-6: PWMCONx: PWMx CONTROL REGISTER

4: To operate in External Period Reset mode, configure FCLCONx<CLMOD> = 0 and PWMCONx<ITB> = 1.

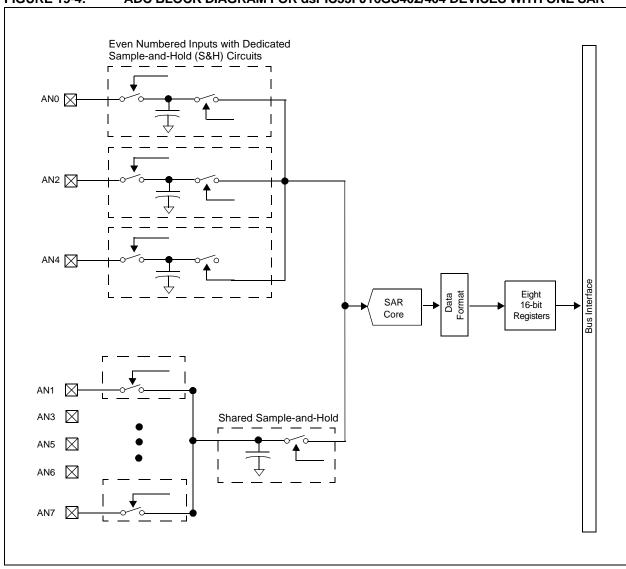

## FIGURE 19-4: ADC BLOCK DIAGRAM FOR dsPIC33FJ16GS402/404 DEVICES WITH ONE SAR

## 19.4 ADC Control Registers

The ADC module uses the following control and status registers:

- ADCON: Analog-to-Digital Control Register

- ADSTAT: Analog-to-Digital Status Register

- ADBASE: Analog-to-Digital Base Register(1,2)

- ADPCFG: Analog-to-Digital Port Configuration Register

- ADCPC0: Analog-to-Digital Convert Pair Control Register 0

- ADCPC1: Analog-to-Digital Convert Pair Control Register 1

- ADCPC2: Analog-to-Digital Convert Pair Control Register 2(1)

- ADCPC3: Analog-to-Digital Convert Pair Control Register 3(1)

The ADCON register controls the operation of the ADC module. The ADSTAT register displays the status of the conversion processes. The ADPCFG registers configure the port pins as analog inputs or as digital I/O. The ADCPCx registers control the triggering of the ADC conversions. See Register 19-1 through Register 19-8 for detailed bit configurations.

Note: A unique feature of the ADC module is its ability to sample inputs in an asynchronous manner. Individual Sample-and-Hold circuits can be triggered independently of each other.

#### REGISTER 19-1: ADCON: ANALOG-TO-DIGITAL CONTROL REGISTER (CONTINUED)

#### bit 4 ASYNCSAMP: Asynchronous Dedicated S&H Sampling Enable bit<sup>(1)</sup>

- 1 = The dedicated S&H is constantly sampling and then terminates sampling as soon as the trigger pulse is detected

- 0 = The dedicated S&H starts sampling when the trigger event is detected and completes the sampling process in two ADC clock cycles

- bit 3 Unimplemented: Read as '0'

- bit 2-0 ADCS<2:0>: Analog-to-Digital Conversion Clock Divider Select bits<sup>(1)</sup>

- 111 = FADC/8

- 110 = FADC/7

- 101 = FADC/6

- 100 = FADC/5

- 011 = FADC/4 (default)

- 010 = FADC/3

- 001 = FADC/2

- 000 = FADC/1

- Note 1: These control bits can only be changed while ADC is disabled (ADON = 0).

- 2: These bits are only available on devices with one SAR.

#### REGISTER 19-7: ADCPC2: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 2<sup>(1)</sup> (CONTINUED)

| bit 12-8 | TRGSRC5<4:0>: Trigger 5 Source Selection bits                                                                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Selects trigger source for conversion of Analog Channels AN11 and AN10.<br>11111 = Timer2 period match                                                                                                                                                  |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | 11011 = Reserved<br>11010 = PWM Generator 4 current-limit ADC trigger<br>11001 = PWM Generator 3 current-limit ADC trigger<br>1000 = PWM Generator 2 current-limit ADC trigger<br>10111 = PWM Generator 1 current-limit ADC trigger<br>10110 = Reserved |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | 10010 = Reserved                                                                                                                                                                                                                                        |

|          | 10001 = PWM Generator 4 secondary trigger is selected                                                                                                                                                                                                   |

|          | 10000 = PWM Generator 3 secondary trigger is selected                                                                                                                                                                                                   |

|          | 01111 = PWM Generator 2 secondary trigger is selected<br>01110 = PWM Generator 1 secondary trigger is selected                                                                                                                                          |

|          | 01101 = Reserved                                                                                                                                                                                                                                        |

|          | 01100 = Timer1 period match                                                                                                                                                                                                                             |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | 01000 = Reserved                                                                                                                                                                                                                                        |

|          | 00111 = PWM Generator 4 primary trigger is selected<br>00110 = PWM Generator 3 primary trigger is selected                                                                                                                                              |

|          | 00101 = PWM Generator 2 primary trigger is selected                                                                                                                                                                                                     |

|          | 00100 = PWM Generator 1 primary trigger is selected                                                                                                                                                                                                     |

|          | 00011 = PWM Special Event Trigger is selected                                                                                                                                                                                                           |

|          | 00010 = Global software trigger is selected                                                                                                                                                                                                             |

|          | 00001 = Individual software trigger is selected                                                                                                                                                                                                         |

|          | 00000 = No conversion is enabled                                                                                                                                                                                                                        |

| bit 7    | IRQEN4: Interrupt Request Enable 4 bit                                                                                                                                                                                                                  |

|          | <ul> <li>1 = Enables IRQ generation when requested conversion of Channels AN9 and AN8 is completed</li> <li>0 = IRQ is not generated</li> </ul>                                                                                                         |

| bit 6    | PEND4: Pending Conversion Status 4 bit                                                                                                                                                                                                                  |

|          | <ul> <li>1 = Conversion of Channels AN9 and AN8 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul>                                                                                                        |

| bit 5    | SWTRG4: Software Trigger 4 bit                                                                                                                                                                                                                          |

|          | <ul> <li>1 = Starts conversion of AN9 and AN8 (if selected by the TRGSRCx bits)<sup>(2)</sup></li> <li>This bit is automatically cleared by hardware when the PEND4 bit is set.</li> </ul>                                                              |

|          | 0 = Conversion has not started                                                                                                                                                                                                                          |

| Note 1:  | This register is only implemented in the dsPIC33FJ16GS504 devices.                                                                                                                                                                                      |

2: The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

## 21.0 SPECIAL FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33F/PIC24H Family Reference Manual" sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

- Brown-out Reset (BOR)

## 21.1 Configuration Bits

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices provide nonvolatile memory implementations for device Configuration bits. Refer to **"Device Configuration"** (DS70194) in the *"dsPIC33F/PIC24H Family Reference Manual"* for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 21-2.

Note that address, 0xF80000, is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFF), which can only be accessed using Table Reads and Table Writes.

The device Configuration register map is shown in Table 21-1.

| Address  | Name     | Bit 7               | Bit 6               | Bit 5   | Bit 4  | Bit 3                   | Bit 2    | Bit 1    | Bit 0    |

|----------|----------|---------------------|---------------------|---------|--------|-------------------------|----------|----------|----------|

| 0xF80000 | FBS      | —                   | _                   |         | _      | BSS2                    | BSS1     | BSS0     | BWRP     |

| 0xF80002 | Reserved | —                   |                     | _       | —      | —                       | _        | _        |          |

| 0xF80004 | FGS      | —                   | _                   | —       |        |                         | GSS1     | GSS0     | GWRP     |

| 0xF80006 | FOSCSEL  | IESO                | _                   | —       |        | _                       |          | FNOSC1   | FNOSC0   |

| 0xF80008 | FOSC     | FCKSM1              | FCKSM0              | IOL1WAY |        |                         | OSCIOFNC | POSCMD1  | POSCMD0  |

| 0xF8000A | FWDT     | FWDTEN              | WINDIS              | —       | WDTPRE | WDTPOST3                | WDTPOST2 | WDTPOST1 | WDTPOST0 |

| 0xF8000C | FPOR     | —                   | _                   | —       |        | Reserved <sup>(2)</sup> | FPWRT2   | FPWRT1   | FPWRT0   |

| 0xF8000E | FICD     | Reser               | ved <sup>(1)</sup>  | JTAGEN  | —      | —                       | —        | ICS1     | ICS0     |

| 0xF80010 | FUID0    | User Unit ID Byte 0 |                     |         |        |                         |          |          |          |

| 0xF80012 | FUID1    |                     | User Unit ID Byte 1 |         |        |                         |          |          |          |

### TABLE 21-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: These bits are reserved for use by development tools and must be programmed to '1'.

2: This bit reads the current programmed value.

| DC CHARACTERISTICS |        |                                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                         |  |

|--------------------|--------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                              | Min                                                                                                                                                                                                                                                                               | Typ <sup>(1)</sup> | Max | Units | Conditions              |  |

| Operating Voltage  |        |                                                                             |                                                                                                                                                                                                                                                                                   |                    |     |       |                         |  |

| DC10               | Vdd    | Supply Voltage <sup>(4)</sup>                                               | 3.0                                                                                                                                                                                                                                                                               | _                  | 3.6 | V     | Industrial and Extended |  |

| DC12               | Vdr    | RAM Data Retention Voltage <sup>(2)</sup>                                   | 1.8                                                                                                                                                                                                                                                                               | _                  | —   | V     |                         |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal            | —                                                                                                                                                                                                                                                                                 | _                  | Vss | V     |                         |  |

| DC17               | SVDD   | VDD Rise Rate <sup>(3)</sup><br>to Ensure Internal<br>Power-on Reset Signal | 0.03                                                                                                                                                                                                                                                                              | —                  |     | V/ms  | 0V-3.0V in 0.1 seconds  |  |

## TABLE 24-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: This is the limit to which VDD may be lowered without losing RAM data.

3: These parameters are characterized but not tested in manufacturing.

**4:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 24-11 for BOR values.

| AC CHARACTERISTICS |        |                                                            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                    |     |       |                                          |

|--------------------|--------|------------------------------------------------------------|------------------------------------------------------|-----|--------------------|-----|-------|------------------------------------------|

| Param<br>No.       | Symbol | Character                                                  | ristic                                               | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                               |

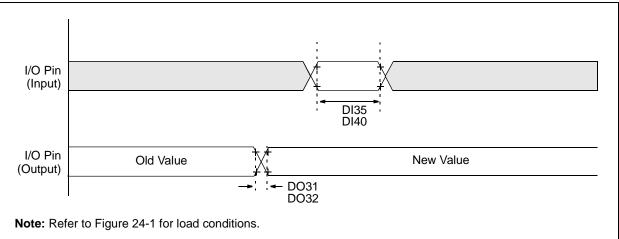

| DO31               | TioR   | Port Output Rise Tim                                       | ne:                                                  |     |                    |     |       |                                          |

|                    |        | 4x Source Driver Pir<br>RB0-RB2, RB5-RB1<br>RC2, RC9, RC10 | ,                                                    | _   | 10                 | 25  | ns    | Refer to Figure 24-1 for test conditions |

|                    |        | 8x Source Driver Pins – RC0,<br>RC3-RC8, RC11-RC13         |                                                      |     | 8                  | 20  | ns    |                                          |

|                    |        | ,                                                          |                                                      | 6   | 15                 | ns  |       |                                          |

| DO32               | TIOF   | Port Output Fall Time                                      | e:                                                   |     |                    |     |       |                                          |

|                    |        | 4x Source Driver Pin<br>RB0-RB2, RB5-RB1<br>RC2, RC9, RC10 | ,                                                    | _   | 10                 | 25  | ns    | Refer to Figure 24-1 for test conditions |

|                    |        | 8x Source Driver Pir<br>RC3-RC8, RC11-RC                   |                                                      |     | 8                  | 20  | ns    |                                          |

|                    |        | 16x Source Driver P<br>RA4, RB3, RB4, RB                   |                                                      | _   | 6                  | 15  | ns    |                                          |

| DI35               | TINP   | INTx Pin High or Lov                                       | v Time (input)                                       | 20  | —                  |     | ns    |                                          |

| DI40               | Trbp   | CNx High or Low Tin                                        | ne (input)                                           | 2   | _                  |     | Тсү   |                                          |

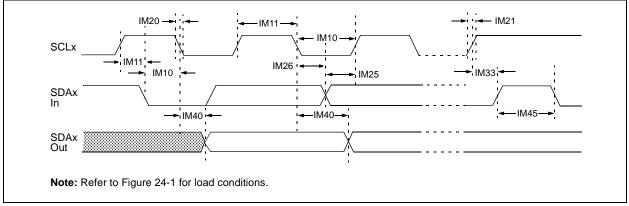

#### TABLE 24-21: I/O TIMING REQUIREMENTS

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

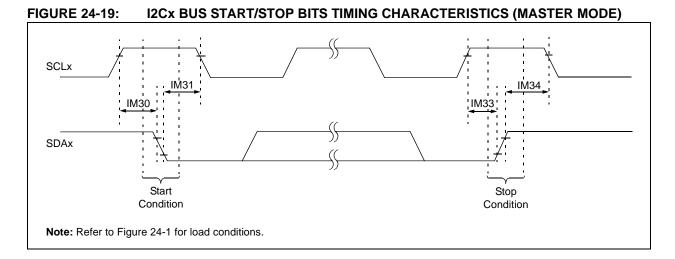

| AC CHARA     | CTERISTICS            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|--------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               | —   | 10  | 25  | ns    |            |  |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 28  | _   |     | ns    |            |  |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 35  | —   |     | ns    |            |  |

#### TABLE 25-9: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

### TABLE 25-10: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |

| HSP35              | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               |     | 10  | 25  | ns    |            |  |

| HSP36              | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                            | 35  | _   | _   | ns    |            |  |

| HSP40              | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 28  | _   | _   | ns    |            |  |

| HSP41              | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 35  |     |     | ns    |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

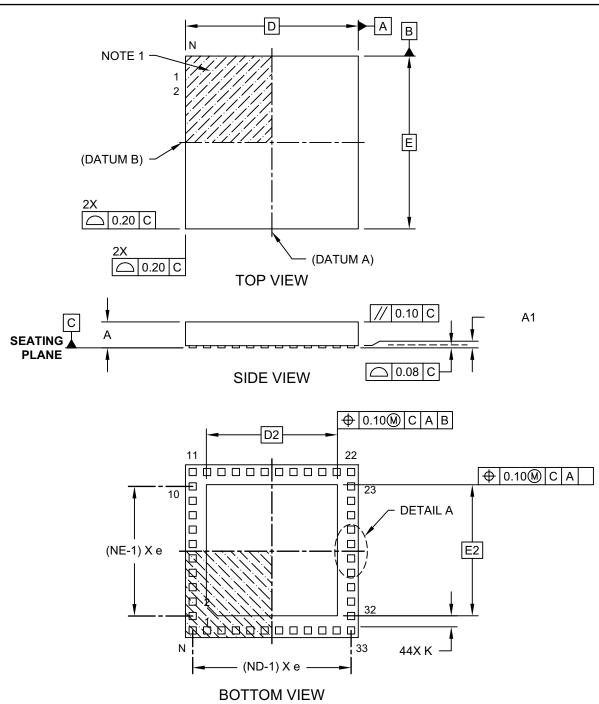

## 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157D Sheet 1 of 2

## TABLE A-4: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                              | Update Description                                                                                                                                            |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 26.0 "50 MIPS Electrical<br>Characteristics"      | Added new chapter in support of 50 MIPS devices.                                                                                                              |

| Section 27.0 "DC and AC Device<br>Characteristics Graphs" | Added new chapter.                                                                                                                                            |

| Section 28.0 "Packaging<br>Information"                   | Added 44-pin VTLA package marking information and diagrams (see Section 28.1 "Package Marking Information" and Section 28.2 "Package Details", respectively). |

| "Product Identification System"                           | Added the TL package definition.                                                                                                                              |

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205 China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

03/25/14