Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs402t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

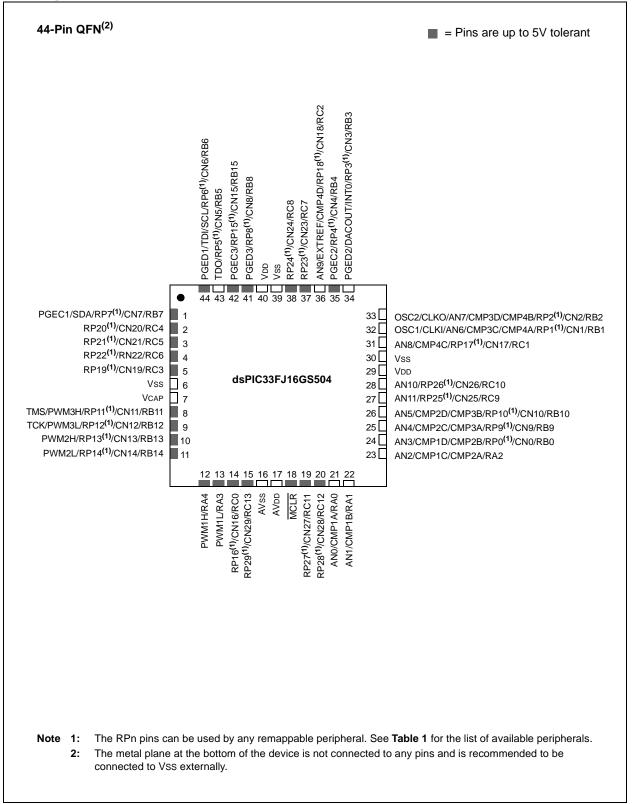

#### **Pin Diagrams (Continued)**

#### 2.5 ICSP<sup>™</sup> Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

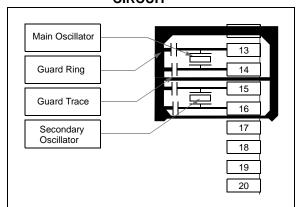

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < FIN < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV, and PLLFBD to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

### © 2008-2014 Microchip Technology Inc.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.3.2 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator writeback operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### 3.6.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF.

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000.

The Most Significant bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

#### 3.6.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 and 31 for right shifts, and between bit positions 0 and 16 for left shifts.

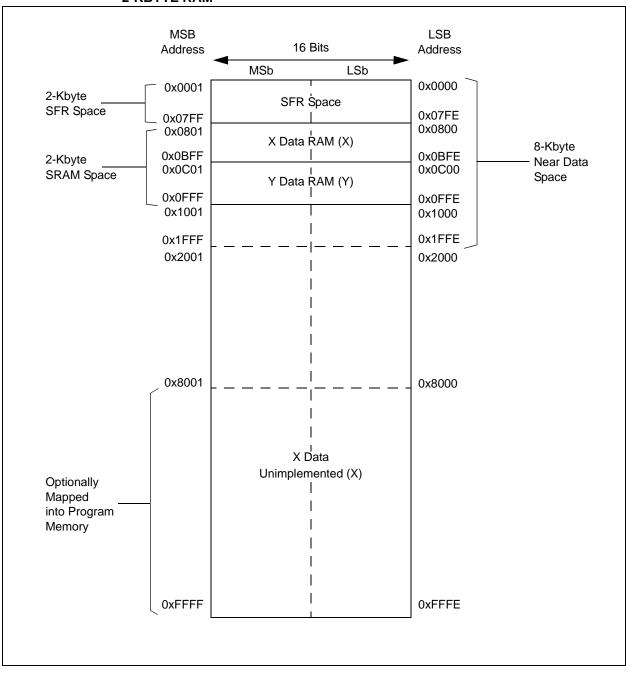

# FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJ16GS402/404/502/504 DEVICES WITH 2-KBYTE RAM

| dsPIC33FJ06GS101/X02  |

|-----------------------|

| 01/X02 and dsPIC33FJ1 |

| PIC33FJ16GS           |

| 116GSX02/X04          |

#### TABLE 4-18: HIGH-SPEED PWM GENERATOR 1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15     | Bit 14                                                                                    | Bit 13  | Bit 12         | Bit 11   | Bit 10  | Bit 9   | Bit 8  | Bit 7      | Bit 6      | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|------------|-------------------------------------------------------------------------------------------|---------|----------------|----------|---------|---------|--------|------------|------------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON1      | 0420        | FLTSTAT    | CLSTAT                                                                                    | TRGSTAT | FLTIEN         | CLIEN    | TRGIEN  | ITB     | MDCS   | DTC1       | DTC0       | —        | —        | —        | CAM      | XPRES    | IUE      | 0000          |

| IOCON1       | 0422        | PENH       | PENL                                                                                      | POLH    | POLL           | PMOD1    | PMOD0   | OVRENH  | OVRENL | OVRDAT1    | OVRDAT0    | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON1      | 0424        | IFLTMOD    | CLSRC4                                                                                    | CLSRC3  | CLSRC2         | CLSRC1   | CLSRC0  | CLPOL   | CLMOD  | FLTSRC4    | FLTSRC3    | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC1         | 0426        |            | PDC1<15:0> 0000                                                                           |         |                |          |         |         |        |            |            | 0000     |          |          |          |          |          |               |

| PHASE1       | 0428        |            |                                                                                           |         |                |          |         |         | P      | HASE1<15:  | 0>         |          |          |          |          |          |          | 0000          |

| DTR1         | 042A        |            | _                                                                                         |         | DTR1<13:0> 000 |          |         |         |        |            |            | 0000     |          |          |          |          |          |               |

| ALTDTR1      | 042C        |            | _                                                                                         |         |                |          |         |         |        | AL         | TDTR1<13:0 | )>       |          |          |          |          |          | 0000          |

| SDC1         | 042E        |            |                                                                                           |         |                |          |         |         | ;      | SDC1<15:0: | >          |          |          |          |          |          |          | 0000          |

| SPHASE1      | 0430        |            |                                                                                           |         |                |          |         |         | SF     | PHASE1<15  | :0>        |          |          |          |          |          |          | 0000          |

| TRIG1        | 0432        |            |                                                                                           |         |                |          | ٦       | rrgcmp< | 15:3>  |            |            |          |          |          | —        | _        | _        | 0000          |

| TRGCON1      | 0434        | TRGDIV3    | TRGDIV2                                                                                   | TRGDIV1 | TRGDIV0        | _        | —       | _       | _      | DTM        | _          | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG1       | 0436        |            |                                                                                           |         |                |          | S       | TRGCMP< | <15:3> |            |            |          |          |          | -        | _        |          | 0000          |

| PWMCAP1      | 0438        |            |                                                                                           |         |                |          | Р       | WMCAP1< | <15:3> |            |            |          |          |          | _        | _        |          | 0000          |

| LEBCON1      | 043A        | PHR        | PHF                                                                                       | PLR     | PLF            | FLTLEBEN | CLLEBEN | LEB6    | LEB5   | LEB4       | LEB3       | LEB2     | LEB1     | LEB0     |          |          |          | 0000          |

| Legend:      | x = U       | nknown val | wn value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |         |                |          |         |         |        |            |            |          |          |          |          |          |          |               |

#### TABLE 4-19: HIGH-SPEED PWM GENERATOR 2 REGISTER MAP FOR dsPIC33FJ06GS102/202 AND dsPIC33FJ16GSX02/X04 DEVICES ONLY

|         | SFR<br>Addr | Bit 15  | Bit 14                                                                                                   | Bit 13  | Bit 12  | Bit 11   | Bit 10  | Bit 9   | Bit 8  | Bit 7     | Bit 6       | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|---------|-------------|---------|----------------------------------------------------------------------------------------------------------|---------|---------|----------|---------|---------|--------|-----------|-------------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2 | 0440        | FLTSTAT | CLSTAT                                                                                                   | TRGSTAT | FLTIEN  | CLIEN    | TRGIEN  | ITB     | MDCS   | DTC1      | DTC0        |          | _        | _        | CAM      | XPRES    | IUE      | 0000          |

| IOCON2  | 0442        | PENH    | I PENL POLH POLL PMOD1 PMOD0 OVRENH OVRENL OVRDAT1 OVRDAT0 FLTDAT1 FLTDAT0 CLDAT1 CLDAT0 SWAP OSYNC 0000 |         |         |          |         |         |        |           |             |          |          |          |          |          |          |               |

| FCLCON2 | 0444        | IFLTMOD | CLSRC4                                                                                                   | CLSRC3  | CLSRC2  | CLSRC1   | CLSRC0  | CLPOL   | CLMOD  | FLTSRC4   | FLTSRC3     | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC2    | 0446        |         | PDC2<15:0> 0000                                                                                          |         |         |          |         |         |        |           |             |          |          |          |          |          |          |               |

| PHASE2  | 0448        |         | PHASE2<15:0> 0000                                                                                        |         |         |          |         |         |        |           |             |          |          |          |          |          |          |               |

| DTR2    | 044A        | _       | — — DTR2<13:0> 0000                                                                                      |         |         |          |         |         |        |           |             |          |          |          |          |          |          |               |

| ALTDTR2 | 044C        | _       | _                                                                                                        |         |         |          |         |         |        | AL        | .TDTR2<13:0 | )>       |          |          |          |          |          | 0000          |

| SDC2    | 044E        |         |                                                                                                          |         |         |          |         |         |        | SDC2<15:0 | >           |          |          |          |          |          |          | 0000          |

| SPHASE2 | 0450        |         |                                                                                                          |         |         |          |         |         | SI     | PHASE2<15 | :0>         |          |          |          |          |          |          | 0000          |

| TRIG2   | 0452        |         |                                                                                                          |         |         |          |         | TRGCMP< | :15:3> |           |             |          |          |          | _        | _        | —        | 0000          |

| TRGCON2 | 0454        | TRGDIV3 | TRGDIV2                                                                                                  | TRGDIV1 | TRGDIV0 | _        | —       | _       | _      | DTM       | _           | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG2  | 0456        |         |                                                                                                          |         |         |          | 5       | STRGCMP | <15:3> |           |             |          |          |          | _        | —        | _        | 0000          |

| PWMCAP2 | 0458        |         |                                                                                                          |         |         |          | F       | WMCAP2  | <15:3> |           |             |          |          |          |          | _        | _        | 0000          |

| LEBCON2 | 045A        | PHR     | PHF                                                                                                      | PLR     | PLF     | FLTLEBEN | CLLEBEN | LEB6    | LEB5   | LEB4      | LEB3        | LEB2     | LEB1     | LEB0     | -        | _        | _        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

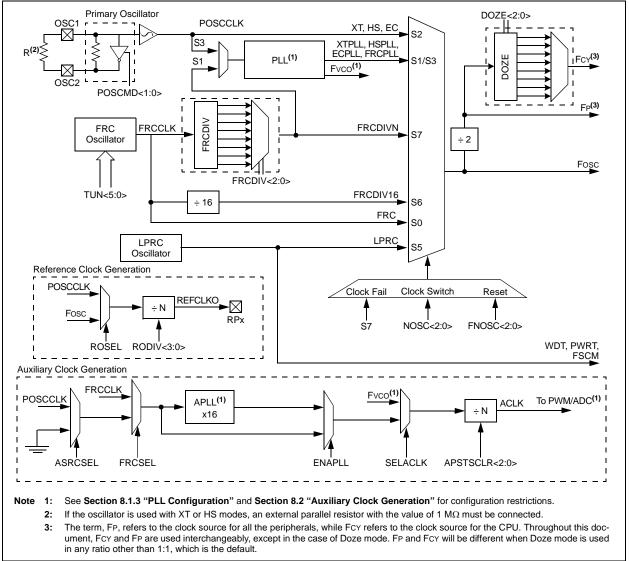

### 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase-Locked Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- A Clock Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

- Auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 8-1.

#### FIGURE 8-1: OSCILLATOR SYSTEM DIAGRAM

| U-0          | U-0                                                          | R/W-1                                                                                        | R/W-1       | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

|--------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------|------------------|------------------|-----------------|--------|

| _            | _                                                            | FLT5R5                                                                                       | FLT5R4      | FLT5R3           | FLT5R2           | FLT5R1          | FLT5R0 |

| bit 15       | •                                                            |                                                                                              |             |                  |                  |                 | bit    |

|              |                                                              |                                                                                              |             |                  |                  |                 |        |

| U-0          | U-0                                                          | R/W-1                                                                                        | R/W-1       | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

| —            | —                                                            | FLT4R5                                                                                       | FLT4R4      | FLT4R3           | FLT4R2           | FLT4R1          | FLT4R0 |

| bit 7        |                                                              |                                                                                              |             |                  |                  |                 | bit    |

| Legend:      |                                                              |                                                                                              |             |                  |                  |                 |        |

| R = Readab   | le bit                                                       | W = Writable                                                                                 | bit         | U = Unimpler     | nented bit, read | l as '0'        |        |

| -n = Value a | t POR                                                        | '1' = Bit is set                                                                             |             | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15-14    | Unimplemen                                                   | ted: Read as '                                                                               | כ'          |                  |                  |                 |        |

|              | 100010 = Inp<br>100001 = Inp                                 | t tied to RP35<br>but tied to RP34<br>but tied to RP33<br>but tied to RP32<br>t tied to RP32 | 3           |                  |                  |                 |        |

| bit 7-6      | Unimplemen                                                   | ted: Read as '                                                                               | י'          |                  |                  |                 |        |

| bit 5-0      | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp | •                                                                                            | ;<br>;<br>; | FLT4) to the Co  | orresponding R   | Pn Pin bits     |        |

#### REGISTER 10-11: RPINR31: PERIPHERAL PIN SELECT INPUT REGISTER 31

|                    | U-0                                                                                                                  | R/W-1                                                                                                                                                             | R/W-1                                      | R/W-1                       | R/W-1            | R/W-1            | R/W-1    |

|--------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------|------------------|------------------|----------|

|                    | _                                                                                                                    | SYNCI1R5                                                                                                                                                          | SYNCI1R4                                   | SYNCI1R3                    | SYNCI1R2         | SYNCI1R1         | SYNCI1R0 |

| bit 15             |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  | bit      |

|                    |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  |          |

| U-0                | U-0                                                                                                                  | R/W-1                                                                                                                                                             | R/W-1                                      | R/W-1                       | R/W-1            | R/W-1            | R/W-1    |

|                    | —                                                                                                                    | FLT8R5                                                                                                                                                            | FLT8R4                                     | FLT8R3                      | FLT8R2           | FLT8R1           | FLT8R0   |

| bit 7              |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  | bit      |

|                    |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  |          |

| Legend:            |                                                                                                                      |                                                                                                                                                                   |                                            |                             | 6 11 K           |                  |          |

| R = Readab         |                                                                                                                      | W = Writable                                                                                                                                                      |                                            | -                           | nented bit, read |                  |          |

| -n = Value a       | t POR                                                                                                                | '1' = Bit is set                                                                                                                                                  |                                            | '0' = Bit is cle            | ared             | x = Bit is unkr  | nown     |

|                    |                                                                                                                      |                                                                                                                                                                   | - <b>1</b>                                 |                             |                  |                  |          |

| bit 15-14          | =                                                                                                                    | ted: Read as '                                                                                                                                                    |                                            |                             |                  |                  |          |

| bit 13-8           |                                                                                                                      | <b>)&gt;:</b> Assign PW<br>g RPn Pin bits                                                                                                                         | M Master Time                              | e Base Externa              | al Synchronizat  | ion Signal to th | е        |

|                    | 1111111 = Inp                                                                                                        | -                                                                                                                                                                 |                                            |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP35                                                                                                                                                   | 5                                          |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP34                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    | 100001 - Inn                                                                                                         |                                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP33                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP33<br>ut tied to RP32                                                                                                                                |                                            |                             |                  |                  |          |

|                    |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    | 100000 = Inp<br>•<br>•                                                                                               | ut tied to RP32                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP32                                                                                                                                                   |                                            |                             |                  |                  |          |

| bit 7-6            | 100000 = Inp<br>•<br>•<br>00000 = Inpu                                                                               | ut tied to RP32                                                                                                                                                   | 2                                          |                             |                  |                  |          |

| bit 7-6<br>bit 5-0 | 100000 = Inp<br>•<br>•<br>00000 = Inpu<br>Unimplemen                                                                 | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '(                                                                                                        | 2<br>0'                                    | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>00000 = Inpu<br>Unimplemen<br>FLT8R<5:0>:<br>111111 = Inp                                 | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as 'd<br>Assign PWM F<br>ut tied to Vss                                                                      | 2<br><sub>0</sub> '<br>Fault Input 8 (I    | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>00000 = Inpu<br>Unimplemen<br>FLT8R<5:0>:<br>111111 = Inp<br>100011 = Inp                 | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35                                                   | 2<br><sub>0</sub> '<br>Fault Input 8 (I    | <sup>-</sup> LT8) to the Co | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>00000 = Inpu<br>Unimplement<br>FLT8R<5:0>:<br>11111 = Inp<br>100011 = Inp<br>100010 = Inp | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34                                | 2<br>0'<br>Fault Input 8 (I<br>5           | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•         | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33             | 2<br>0'<br>Fault Input 8 (I<br>5<br>4<br>3 | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•         | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34                                | 2<br>0'<br>Fault Input 8 (I<br>5<br>4<br>3 | <sup>-</sup> LT8) to the Co | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•         | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33             | 2<br>0'<br>Fault Input 8 (I<br>5<br>4<br>3 | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•         | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33             | 2<br>0'<br>Fault Input 8 (I<br>5<br>4<br>3 | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•         | ut tied to RP32<br>t tied to RP0<br>ted: Read as '(<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32 | 2<br>0'<br>Fault Input 8 (I<br>5<br>4<br>3 | <sup>-</sup> LT8) to the Co | orresponding R   | Pn Pin bits      |          |

#### REGISTER 10-13: RPINR33: PERIPHERAL PIN SELECT INPUT REGISTER 33

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP3R5 | RP3R4 | RP3R3 | RP3R2 | RP3R1 | RP3R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|        | _   | RP2R5 | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

#### REGISTER 10-16: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP3R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                             |

| bit 5-0   | <b>RP2R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-2 for peripheral function numbers) |

#### REGISTER 10-17: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP5R5 | RP5R4 | RP5R3 | RP5R2 | RP5R1 | RP5R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP4R5 | RP4R4 | RP4R3 | RP4R2 | RP4R1 | RP4R0 |

| bit 7  |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 13-8 **RP5R<5:0>:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP4R<5:0>:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 0

| REGISTER 14-1: | OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2) |

|----------------|------------------------------------------------------|

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | OCSIDL | —   | —   | _   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R-0, HC | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|---------|--------|-------|-------|-------|

| —     | —   | —   | OCFLT   | OCTSEL | OCM2  | OCM1  | OCM0  |

| bit 7 |     |     |         |        |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit |                                    |                    |

|-------------------|-----------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                                                                                                                   |

|           | 1 = Output Compare x halts in CPU Idle mode                                                                                                                                            |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                                                                                                                             |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                             |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                  |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in hardware only)</li> <li>0 = No PWM Fault condition has occurred (this bit is only used when OCM&lt;2:0&gt; = 111)</li> </ul> |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                                                                                                                                |

|           | 1 = Timer3 is the clock source for Output Compare x                                                                                                                                    |

|           | 0 = Timer2 is the clock source for Output Compare x                                                                                                                                    |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                                                                                                                              |

|           | 111 = PWM mode on OCx, Fault pin is enabled                                                                                                                                            |

|           | 110 = PWM mode on OCx, Fault pin is disabled                                                                                                                                           |

|           | 101 = Initializes OCx pin low, generates continuous output pulses on OCx pin                                                                                                           |

|           | 100 = Initializes OCx pin low, generates single output pulse on OCx pin                                                                                                                |

|           | <ul> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initializes OCx pin high, compare event forces OCx pin low</li> </ul>                                                      |

|           | 001 = Initializes OCx pin low, compare event forces OCx pin low                                                                                                                        |

|           | 000 = Output compare channel is disabled                                                                                                                                               |

|           |                                                                                                                                                                                        |

| R/W-0           | U-0                  | R/W-0                             | R/W-1, HC        | R/W-0             | R/W-0                          | R/W-0               | R/W-0           |

|-----------------|----------------------|-----------------------------------|------------------|-------------------|--------------------------------|---------------------|-----------------|

| I2CEN           | —                    | I2CSIDL                           | SCLREL           | IPMIEN            | A10M                           | DISSLW              | SMEN            |

| bit 15          |                      |                                   |                  |                   |                                |                     | bit 8           |

| R/W-0           | R/W-0                | R/W-0                             | R/W-0, HC        | R/W-0, HC         | R/W-0, HC                      | R/W-0, HC           | R/W-0, HC       |

| GCEN            | STREN                | ACKDT                             | ACKEN            | RCEN              | PEN                            | RSEN                | SEN             |

| bit 7           |                      |                                   | /                |                   |                                |                     | bit (           |

| Legend:         |                      |                                   | mented bit, re   | ad as 'O'         |                                |                     |                 |

| R = Readable    | hit                  | W = Writable                      |                  |                   | re Clearable bit               |                     |                 |

| -n = Value at F |                      | '1' = Bit is se                   |                  | 0' = Bit is clear |                                | x = Bit is unkno    | nwn             |

|                 |                      |                                   |                  |                   |                                |                     |                 |

| bit 15          | 12CEN: 120           | Cx Enable bit                     |                  |                   |                                |                     |                 |

|                 | -                    |                                   | odule, and cor   | nfigures the SE   | Ax and SCLx pir                | ns as serial port r | oins            |

|                 |                      |                                   |                  |                   | trolled by port fur            |                     |                 |

| bit 14          | Unimplem             | ented: Read                       | <b>as</b> '0'    |                   |                                |                     |                 |

| bit 13          | I2CSIDL:             | 2Cx Stop in Ic                    | lle Mode bit     |                   |                                |                     |                 |

|                 |                      | tinues module<br>ues module o     | •                |                   | ers an Idle mode               |                     |                 |

| bit 12          | SCLREL:              | SCLx Release                      | e Control bit (\ | when operating    | as l <sup>2</sup> C slave)     |                     |                 |

|                 |                      | ses SCLx cloc<br>SCLx clock lo    |                  | ch)               |                                |                     |                 |

|                 | If STREN =           |                                   | ,                | ,                 |                                |                     |                 |

|                 |                      | •                                 |                  |                   | h and write '1' to             | ,                   | Hardware clea   |

|                 | -                    | -                                 | nsmission. Ha    | ardware clear a   | t end of slave ree             | ception.            |                 |

|                 | If STREN =           |                                   | can only wri     | te '1' to releas  | se clock). Hardw               | are clear at heri   | nning of slav   |

|                 | transmissio          | •                                 | can only wi      |                   |                                | are clear at begi   | Thing of Slave  |

| bit 11          | IPMIEN: In           | ntelligent Perip                  | heral Manage     | ement Interface   | e (IPMI) Enable b              | bit                 |                 |

|                 | 1 = IPMI m           | node is enable                    | d; all address   | es are Acknow     | . ,                            |                     |                 |

|                 |                      | node is disable                   |                  |                   |                                |                     |                 |

| bit 10          |                      | Bit Slave Add                     |                  | _                 |                                |                     |                 |

|                 |                      | DD is a 10-bit<br>DD is a 7-bit s |                  | 5                 |                                |                     |                 |

| bit 9           |                      | Disable Slew I                    |                  | oit               |                                |                     |                 |

|                 |                      | ate control is o                  |                  |                   |                                |                     |                 |

|                 |                      | ate control is e                  |                  |                   |                                |                     |                 |

| bit 8           | SMEN: SM             | Bus Input Le                      | vels bit         |                   |                                |                     |                 |

|                 |                      | es I/O pin three<br>es SMBus inp  |                  | ant with SMBu     | s specification                |                     |                 |

| bit 7           | GCEN: Ge             | eneral Call Ena                   | able bit (when   | operating as I    | <sup>2</sup> C slave)          |                     |                 |

|                 | 1 = Enable<br>recept |                                   | nen a general    | call address is   | received in the la             | 2CxRSR (module      | e is enabled fo |

|                 |                      | al call addres                    | s is disabled    |                   |                                |                     |                 |

| bit 6           | STREN: S             | CLx Clock Str                     | etch Enable b    | oit (when opera   | ting as I <sup>2</sup> C slave | )                   |                 |

|                 |                      | njunction with                    |                  |                   |                                |                     |                 |

|                 |                      | es software or                    |                  | -                 |                                |                     |                 |

|                 | v = v sable          | es sonware of                     | receive clock    | stretching        |                                |                     |                 |

#### REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

NOTES:

#### REGISTER 19-1: ADCON: ANALOG-TO-DIGITAL CONTROL REGISTER (CONTINUED)

#### bit 4 ASYNCSAMP: Asynchronous Dedicated S&H Sampling Enable bit<sup>(1)</sup>

- 1 = The dedicated S&H is constantly sampling and then terminates sampling as soon as the trigger pulse is detected

- 0 = The dedicated S&H starts sampling when the trigger event is detected and completes the sampling process in two ADC clock cycles

- bit 3 Unimplemented: Read as '0'

- bit 2-0 ADCS<2:0>: Analog-to-Digital Conversion Clock Divider Select bits<sup>(1)</sup>

- 111 = FADC/8

- 110 = FADC/7

- 101 = FADC/6

- 100 = FADC/5

- 011 = FADC/4 (default)

- 010 = FADC/3

- 001 = FADC/2

- 000 = FADC/1

- Note 1: These control bits can only be changed while ADC is disabled (ADON = 0).

- 2: These bits are only available on devices with one SAR.

### REGISTER 19-8: ADCPC3: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup>

| bit 4-0 | TRGSRC6<4:0>: Trigger 6 Source Selection bits<br>Selects trigger source for conversion of Analog Channels AN13 and AN12.<br>11111 = Timer2 period match |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00111 = PWM Generator 4 primary trigger is selected<br>00110 = PWM Generator 3 primary trigger is selected                                              |

- Note 1: This register is only implemented on the dsPIC33FJ16GS502 and dsPIC33FJ16GS504 devices.

- 2: The trigger source must be set as global software trigger prior to setting this bit to '1'. If other conversions are in progress, conversion will be performed when the conversion resources are available.

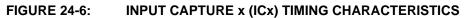

#### TABLE 24-26: INPUT CAPTURE x TIMING REQUIREMENTS

| AC CHARACTERISTICS            |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                       |              |     |       |                                  |

|-------------------------------|------|------------------------------------------------------|-----------------------|--------------|-----|-------|----------------------------------|

| Param<br>No. Symbol Character |      |                                                      | ristic <sup>(1)</sup> | Min          | Мах | Units | Conditions                       |

| IC10                          | TccL | ICx Input Low Time                                   | No prescaler          | 0.5 Tcy + 20 | _   | ns    |                                  |

|                               |      |                                                      | With prescaler        | 10           | —   | ns    |                                  |

| IC11                          | TccH | ICx Input High Time                                  | No prescaler          | 0.5 TCY + 20 | —   | ns    |                                  |

|                               |      |                                                      | With prescaler        | 10           | —   | ns    |                                  |

| IC15                          | TccP | ICx Input Period                                     |                       | (Tcy + 40)/N | —   | ns    | N = Prescale<br>value (1, 4, 16) |

**Note 1:** These parameters are characterized but not tested in manufacturing.

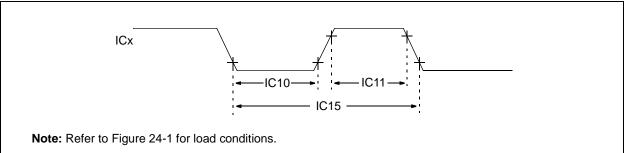

#### FIGURE 24-7: OUTPUT COMPARE x MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 24-27: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                    |  |

|--------------------|--------|-------------------------------|------------------------------------------------------|-----|-----|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                                                  | Тур | Max | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | —                                                    | —   |     | ns    | See Parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                    | _   | _   | ns    | See Parameter DO31 |  |

Note 1: These parameters are characterized but not tested in manufacturing.

<sup>© 2008-2014</sup> Microchip Technology Inc.

| AC CHARACTERISTICS   |                                          |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extend} \end{array}$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                         | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 24-31                              | —                                           | —                                                                                                                                                                                                                                                                                  | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | —                                        | Table 24-32                                 | —                                                                                                                                                                                                                                                                                  | 1   | 0,1 | 1   |  |  |

| 9 MHz                | —                                        | Table 24-33                                 | —                                                                                                                                                                                                                                                                                  | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 24-34                                                                                                                                                                                                                                                                        | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 24-35                                                                                                                                                                                                                                                                        | 1   | 1   | 0   |  |  |

| 15 MHz               | —                                        | —                                           | Table 24-36                                                                                                                                                                                                                                                                        | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 24-37                                                                                                                                                                                                                                                                        | 0   | 0   | 0   |  |  |

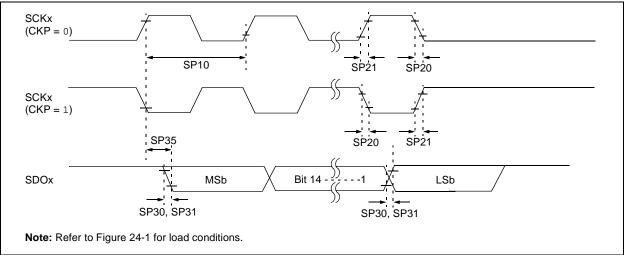

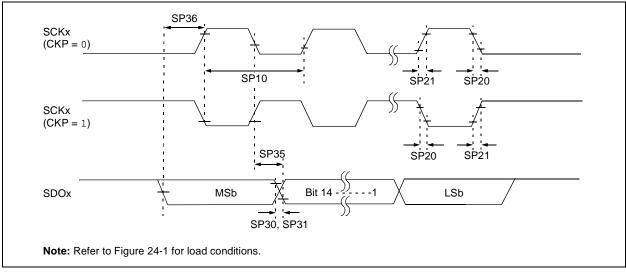

#### FIGURE 24-11: SPIx MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING **CHARACTERISTICS**

#### SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING FIGURE 24-12: **CHARACTERISTICS**

|               |         |                                                                    | Standard Operating Conditions (see Note 1): 3.0V to 3.6V<br>Operating temperature: $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |       |               |       |                                                                                                |  |

|---------------|---------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------|------------------------------------------------------------------------------------------------|--|

| Param.<br>No. | Symbol  | Characteristic                                                     | Min                                                                                                                                                                                              | Тур   | Max           | Units | Comments                                                                                       |  |

| DA10          | RLOAD   | Resistive Output Load<br>Impedance                                 | ЗК                                                                                                                                                                                               | _     | —             | Ω     |                                                                                                |  |

| DA11          | CLOAD   | Output Load Capacitance                                            | —                                                                                                                                                                                                | 20    | 35            | pF    |                                                                                                |  |

| DA12          | Ιουτ    | Output Current Drive<br>Strength                                   | -1740                                                                                                                                                                                            | ±1400 | +1770         | μA    | Sink and source                                                                                |  |

| DA13          | VRANGE  | Full Output Drive Strength<br>Voltage Range                        | AVss + 250 mV                                                                                                                                                                                    |       | AVDD – 900 mV | V     |                                                                                                |  |

| DA14          | VLRANGE | Output Drive Voltage<br>Range at Reduced<br>Current Drive of 50 μA | AVss + 50 mV                                                                                                                                                                                     | _     | AVDD – 500 mV | V     |                                                                                                |  |

| DA15          | IDD     | Current Consumed when<br>Module is Enabled,<br>High-Power Mode     | 369                                                                                                                                                                                              | 626   | 948           | μΑ    | Module will always<br>consume this<br>current even if no<br>load is connected to<br>the output |  |

| DA16          | ROUTON  | Output Impedance when<br>Module is Enabled                         | —                                                                                                                                                                                                | 1200  | —             | Ω     |                                                                                                |  |

#### TABLE 24-44: DAC OUTPUT BUFFER DC SPECIFICATIONS

**Note 1:** Module is functional at VBOR < VDD < VDDMIN, but with degraded performance. Module functionality is tested but not characterized.

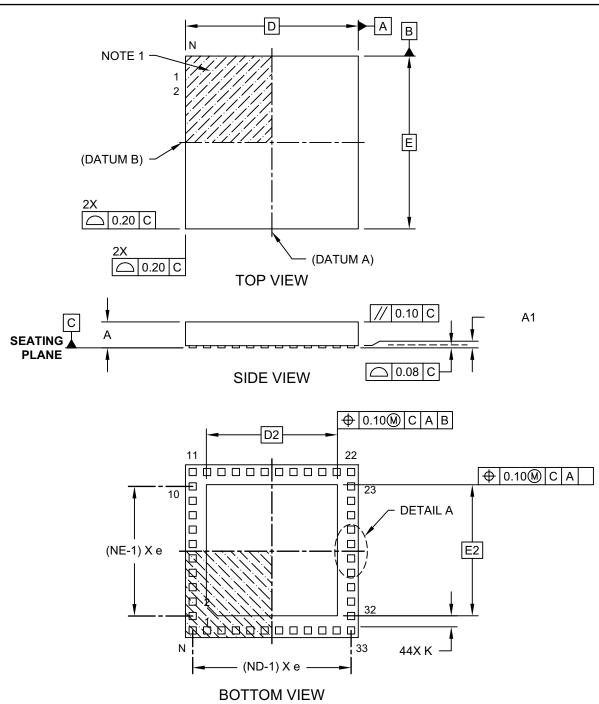

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units |          |          |      |  |

|-------------------------|-------|----------|----------|------|--|

| Dimension               | MIN   | NOM      | MAX      |      |  |

| Number of Pins          | Ν     |          | 44       |      |  |

| Pitch                   | е     |          | 0.65 BSC |      |  |

| Overall Height          | А     | 0.80     | 0.90     | 1.00 |  |

| Standoff                | A1    | 0.00     | 0.02     | 0.05 |  |

| Terminal Thickness      | A3    | 0.20 REF |          |      |  |

| Overall Width           | E     | 8.00 BSC |          |      |  |

| Exposed Pad Width       | E2    | 6.25     | 6.45     | 6.60 |  |

| Overall Length          | D     | 8.00 BSC |          |      |  |

| Exposed Pad Length      | D2    | 6.25     | 6.45     | 6.60 |  |

| Terminal Width          | b     | 0.20     | 0.30     | 0.35 |  |

| Terminal Length         | L     | 0.30     | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | К     | 0.20     | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

### 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157D Sheet 1 of 2