Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 2K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs404-50i-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

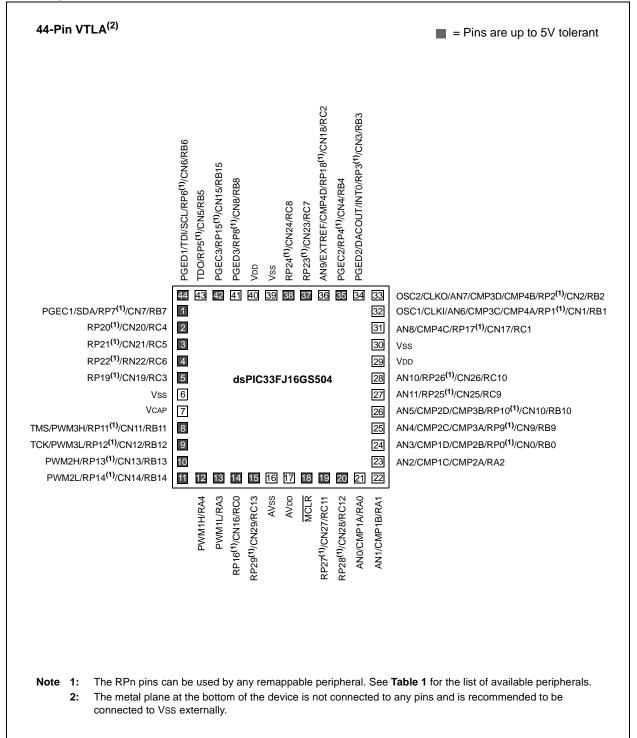

#### **Pin Diagrams (Continued)**

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

- bit 1 RND: Rounding Mode Select bit 1 = Biased (conventional) rounding is enabled

- 0 = Unbiased (convergent) rounding is enabled

- bit 0 IF: Integer or Fractional Multiplier Mode Select bit

- 1 = Integer mode is enabled for DSP multiply ops

- 0 = Fractional mode is enabled for DSP multiply ops

- Note 1: This bit will always read as '0'.

- 2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts (Part IV)" (DS70300) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 CPU. It has the following features:

- Up to eight processor exceptions and software traps

- Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

#### 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors, consisting of eight nonmaskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR). Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices implement up to 35 unique interrupts and 4 non-maskable traps. These are summarized in Table 7-1.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices clear their registers in response to a Reset, which forces the PC to zero. The Digital Signal Controller then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit |

|-------|----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                       |

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| REGISTER 7-34: | IPC29: INTERRUPT PRIORITY CONTROL REGISTER 29 |

|----------------|-----------------------------------------------|

|----------------|-----------------------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0      | U-0      | U-0      |

|--------|-----|-----|-----|-----|----------|----------|----------|

| —      | —   | —   | —   | _   | —        | —        | —        |

| bit 15 |     |     |     |     |          |          | bit 8    |

|        |     |     |     |     |          |          |          |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1    | R/W-0    | R/W-0    |

| —      | —   | —   | —   | —   | ADCP6IP2 | ADCP6IP1 | ADCP6IP0 |

| bit 7  | •   |     |     |     |          |          | bit 0    |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 ADCP6IP<2:0>: ADC Pair 6 Conversion Done Interrupt 1 Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0    | U-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0   |

|--------|-----|-----|-----|------|------|------|-------|

| —      |     | _   | _   | ILR3 | ILR2 | ILR1 | ILR0  |

| bit 15 |     |     |     |      |      |      | bit 8 |

#### REGISTER 7-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0   | R-0     |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:      |                                                  |                                           |                        |                    |  |  |  |  |  |  |

|--------------|--------------------------------------------------|-------------------------------------------|------------------------|--------------------|--|--|--|--|--|--|

| •            | R = Readable bit W = Writable bit                |                                           | U = Unimplemented bit, | , read as '0'      |  |  |  |  |  |  |

| -n = Value a | t POR                                            | '1' = Bit is set                          | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |  |  |

| bit 15-12    | Unimplen                                         | nented: Read as '0'                       |                        |                    |  |  |  |  |  |  |

| bit 11-8     | •                                                | Unimplemented: Read as '0'                |                        |                    |  |  |  |  |  |  |

|              |                                                  |                                           |                        |                    |  |  |  |  |  |  |

|              | 1111 <b>= C</b>                                  | 1111 = CPU Interrupt Priority Level is 15 |                        |                    |  |  |  |  |  |  |

|              | •                                                | •                                         |                        |                    |  |  |  |  |  |  |

|              | •                                                |                                           |                        |                    |  |  |  |  |  |  |

|              | • ODU la termat Drivite Level is 4               |                                           |                        |                    |  |  |  |  |  |  |

|              |                                                  | PU Interrupt Priority Level is            |                        |                    |  |  |  |  |  |  |

|              |                                                  | PU Interrupt Priority Level i             | 50                     |                    |  |  |  |  |  |  |

| bit 7        | Unimplen                                         | nented: Read as '0'                       |                        |                    |  |  |  |  |  |  |

| bit 6-0      | VECNUM                                           | <6:0>: Vector Number of P                 | ending Interrupt bits  |                    |  |  |  |  |  |  |

|              | 0111111 = Interrupt vector pending is Number 135 |                                           |                        |                    |  |  |  |  |  |  |

|              | •                                                |                                           |                        |                    |  |  |  |  |  |  |

|              | •                                                |                                           |                        |                    |  |  |  |  |  |  |

|              | •                                                |                                           |                        |                    |  |  |  |  |  |  |

|              | 0000001                                          | = Interrupt vector pending i              | is Number 9            |                    |  |  |  |  |  |  |

|              | 0000000                                          | = Interrupt vector pending i              | is Number 8            |                    |  |  |  |  |  |  |

|              |                                                  |                                           |                        |                    |  |  |  |  |  |  |

| REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |     |                  |     |                                     |       |                 |       |  |  |

|------------------------------------------------------------------|-----|------------------|-----|-------------------------------------|-------|-----------------|-------|--|--|

| U-0                                                              | U-0 | U-0              | U-0 | U-0                                 | R/W-0 | U-0             | U-0   |  |  |

| _                                                                | —   | —                | —   | —                                   | CMPMD | —               | —     |  |  |

| bit 15                                                           |     |                  |     |                                     |       |                 | bit 8 |  |  |

|                                                                  |     |                  |     |                                     |       |                 |       |  |  |

| U-0                                                              | U-0 | U-0              | U-0 | U-0                                 | U-0   | U-0             | U-0   |  |  |

| —                                                                | —   | —                | —   | —                                   | —     | —               | —     |  |  |

| bit 7                                                            |     |                  |     |                                     |       |                 | bit 0 |  |  |

|                                                                  |     |                  |     |                                     |       |                 |       |  |  |

| Legend:                                                          |     |                  |     |                                     |       |                 |       |  |  |

| R = Readable b                                                   | bit | W = Writable     | bit | U = Unimplemented bit, read as '0'  |       |                 |       |  |  |

| -n = Value at P                                                  | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unk |       | x = Bit is unkr | nown  |  |  |

|                                                                  |     |                  |     |                                     |       |                 |       |  |  |

| bit 15-11 | Unimplemented: Read as '0'                               |

|-----------|----------------------------------------------------------|

| bit 10    | CMPMD: Analog Comparator Module Disable bit              |

|           | <ol> <li>Analog comparator module is disabled</li> </ol> |

|           | 0 = Analog comparator module is enabled                  |

| bit 9-0   | Unimplemented: Read as '0'                               |

#### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 3 **REFOMD**: Reference Clock Generator Module Disable bit

1 = Reference clock generator module is disabled

- 0 = Reference clock generator module is enabled

- bit 2-0 Unimplemented: Read as '0'

#### 10.2 Open-Drain Configuration

In addition to the PORTx, LATx and TRISx registers for data control, some digital-only port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (for example, 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to **"Pin Diagrams"** for the available pins and their functionality.

#### 10.3 Configuring Analog Port Pins

The ADPCFG and TRISx registers control the operation of the Analog-to-Digital (A/D) port pins. The port pins that are to function as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The ADPCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORTx register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 10.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP. An example is shown in Example 10-1.

#### 10.5 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 30 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a Change-of-State.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when the push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on Change Notification pins should always be disabled when the port pin is configured as a digital output.

#### EQUATION 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| BTSS | PORTB, #13 | ; | Next Instruction                |

|      |            |   |                                 |

NOTES:

#### © 2008-2014 Microchip Technology Inc.

#### REGISTER 19-5: ADCPC0: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 0 (CONTINUED)

```

bit 4-0

TRGSRC0<4:0>: Trigger 0 Source Selection bits

Selects trigger source for conversion of Analog Channels AN1 and AN0.

11111 = Timer2 period match

11011 = Reserved

11010 = PWM Generator 4 current-limit ADC trigger

11001 = PWM Generator 3 current-limit ADC trigger

11000 = PWM Generator 2 current-limit ADC trigger

10111 = PWM Generator 1 current-limit ADC trigger

10110 = \text{Reserved}

10010 = Reserved

10001 = PWM Generator 4 secondary trigger is selected

10000 = PWM Generator 3 secondary trigger is selected

01111 = PWM Generator 2 secondary trigger is selected

01110 = PWM Generator 1 secondary trigger is selected

01101 = Reserved

01100 = Timer1 period match

01000 = Reserved

00111 = PWM Generator 4 primary trigger is selected

00110 = PWM Generator 3 primary trigger is selected

00101 = PWM Generator 2 primary trigger is selected

00100 = PWM Generator 1 primary trigger is selected

00011 = PWM Special Event Trigger is selected

00010 = Global software trigger is selected

00001 = Individual software trigger is selected

00000 = No conversion is enabled

```

**Note 1:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

#### REGISTER 19-7: ADCPC2: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 2<sup>(1)</sup> (CONTINUED)

| bit 12-8 | TRGSRC5<4:0>: Trigger 5 Source Selection bits                                                                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Selects trigger source for conversion of Analog Channels AN11 and AN10.<br>11111 = Timer2 period match                                                                                                                                                  |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | 11011 = Reserved<br>11010 = PWM Generator 4 current-limit ADC trigger<br>11001 = PWM Generator 3 current-limit ADC trigger<br>1000 = PWM Generator 2 current-limit ADC trigger<br>10111 = PWM Generator 1 current-limit ADC trigger<br>10110 = Reserved |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | 10010 = Reserved                                                                                                                                                                                                                                        |

|          | 10001 = PWM Generator 4 secondary trigger is selected                                                                                                                                                                                                   |

|          | 10000 = PWM Generator 3 secondary trigger is selected                                                                                                                                                                                                   |

|          | 01111 = PWM Generator 2 secondary trigger is selected<br>01110 = PWM Generator 1 secondary trigger is selected                                                                                                                                          |

|          | 01101 = Reserved                                                                                                                                                                                                                                        |

|          | 01100 = Timer1 period match                                                                                                                                                                                                                             |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                                       |

|          | 01000 = Reserved                                                                                                                                                                                                                                        |

|          | 00111 = PWM Generator 4 primary trigger is selected<br>00110 = PWM Generator 3 primary trigger is selected                                                                                                                                              |

|          | 00101 = PWM Generator 2 primary trigger is selected                                                                                                                                                                                                     |

|          | 00100 = PWM Generator 1 primary trigger is selected                                                                                                                                                                                                     |

|          | 00011 = PWM Special Event Trigger is selected                                                                                                                                                                                                           |

|          | 00010 = Global software trigger is selected                                                                                                                                                                                                             |

|          | 00001 = Individual software trigger is selected                                                                                                                                                                                                         |

|          | 00000 = No conversion is enabled                                                                                                                                                                                                                        |

| bit 7    | IRQEN4: Interrupt Request Enable 4 bit                                                                                                                                                                                                                  |

|          | <ul> <li>1 = Enables IRQ generation when requested conversion of Channels AN9 and AN8 is completed</li> <li>0 = IRQ is not generated</li> </ul>                                                                                                         |

| bit 6    | PEND4: Pending Conversion Status 4 bit                                                                                                                                                                                                                  |

|          | <ul> <li>1 = Conversion of Channels AN9 and AN8 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul>                                                                                                        |

| bit 5    | SWTRG4: Software Trigger 4 bit                                                                                                                                                                                                                          |

|          | <ul> <li>1 = Starts conversion of AN9 and AN8 (if selected by the TRGSRCx bits)<sup>(2)</sup></li> <li>This bit is automatically cleared by hardware when the PEND4 bit is set.</li> </ul>                                                              |

|          | 0 = Conversion has not started                                                                                                                                                                                                                          |

| Note 1:  | This register is only implemented in the dsPIC33FJ16GS504 devices.                                                                                                                                                                                      |

2: The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

# 21.8 Code Protection and CodeGuard<sup>™</sup> Security

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices offer the intermediate implementation of CodeGuard<sup>™</sup> Security. CodeGuard Security enables multiple parties to securely share resources (memory, interrupts and peripherals) on a single chip. This feature helps protect individual Intellectual Property (IP) in collaborative system designs.

When coupled with software encryption libraries, Code-Guard<sup>™</sup> Security can be used to securely update Flash even when multiple IPs reside on a single chip.

# TABLE 21-3:CODE FLASH SECURITY<br/>SEGMENT SIZES FOR<br/>6-Kbyte DEVICES

| Configuration Bits     |              |                                                                           |

|------------------------|--------------|---------------------------------------------------------------------------|

|                        | VS = 256 IW  | 000000h<br>0001FEh                                                        |

| BSS<2:0> = x11<br>0K   | GS = 1792 IW | 000200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h<br>000FFEh<br>000FFEh |

|                        |              | 002BFEh                                                                   |

|                        | VS = 256 IW  | 000000h<br>0001FEh                                                        |

|                        | BS = 256 IW  | 000200h<br>0003FEh                                                        |

| BSS<2:0> = x10<br>256  | GS = 1536 IW | 000400h<br>0007FEh<br>000800h<br>000FFEh<br>001000h                       |

|                        |              | 002BFEh                                                                   |

|                        | VS = 256 IW  | 000000h<br>00015Eh                                                        |

| BSS<2:0> = x01         | BS = 768 IW  | 000200h<br>0003FEh<br>000400h<br>0007FEh                                  |

| 768                    | GS = 1024 IW | 000800h<br>000FFEh<br>001000h                                             |

|                        |              | 002BFEh                                                                   |

|                        | VS = 256 IW  | 000000h<br>0001FEh                                                        |

| BSS<2:0> = x00<br>1792 | BS = 1792 IW | 000200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h<br>000FFEh<br>001000h |

|                        |              | 002BFEh                                                                   |

The code protection features are controlled by the Configuration registers: FBS and FGS.

Secure segment and RAM protection is not implemented in dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices.

| Note: | Refer  | to     | "CodeGuard™ |           | Secur  | ity"     |      |

|-------|--------|--------|-------------|-----------|--------|----------|------|

|       | (DS701 | 199)   | for         | further   | infor  | mation   | on   |

|       | CodeG  | iuard  | Sec         | urity usa | ge, co | onfigura | tion |

|       | and op | eratio | on.         |           |        |          |      |

#### TABLE 21-4: CODE FLASH SECURITY SEGMENT SIZES FOR 16-Kbyte DEVICES

| Configuration Bits          |              |                                                                                        |

|-----------------------------|--------------|----------------------------------------------------------------------------------------|

|                             | VS = 256 IW  | 000000h<br>0001FEh                                                                     |

| BSS<2:0> = x11<br>0K        | GS = 5376 IW | 0002200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h<br>000FFEh<br>0006FFEh<br>001000h |

|                             |              | 002BFEh                                                                                |

|                             | VS = 256 IW  | 000000h<br>0001FEh<br>000200h                                                          |

| BSS<2:0> = x10              | BS = 256 IW  | 0003FEh<br>000400h                                                                     |

| 256                         |              | 0007FEh<br>000800h<br>000FFEh<br>001000h                                               |

|                             | GS = 5120 IW | 002BFEh                                                                                |

|                             | VS = 256 IW  | 000000h<br>0001FEh                                                                     |

| <b>BSS&lt;2:0&gt; =</b> x01 | BS = 768 IW  | 000200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h                                    |

| 768                         |              | 000800h<br>000FFEh<br>001000h                                                          |

|                             | GS = 4608 IW | 002BFEh                                                                                |

|                             | VS = 256 IW  | 000000h<br>0001FEh                                                                     |

| BSS<2:0> = x00              | BS = 1792 IW | 000200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h                                    |

|                             | GS = 3584 IW | 000FFEh<br>001000h<br>002BFEh                                                          |

| DC CHARACT       | ERISTICS               |              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |        |         |                        |

|------------------|------------------------|--------------|-------------------------------------------------------|--------|---------|------------------------|

| Parameter<br>No. | Typical <sup>(1)</sup> | Max          | Units Conditions                                      |        |         |                        |

| Idle Current (I  | IDLE): Core Of         | f Clock On I | Base Current <sup>(2</sup>                            | 2)     |         |                        |

| DC40d            | 48                     |              | mA                                                    | -40°C  |         |                        |

| DC40a            | 48                     | _            | mA                                                    | +25°C  | 3.3V    | 10 MIPS                |

| DC40b            | 48                     | _            | mA                                                    | +85°C  | 3.3V    | 10 101173              |

| DC40c            | 48                     |              | mA                                                    | +125°C | 1       |                        |

| DC41d            | 60                     | _            | mA                                                    | -40°C  | 3.3V    | 16 MIPS <sup>(3)</sup> |

| DC41a            | 60                     | _            | mA                                                    | +25°C  |         |                        |

| DC41b            | 60                     |              | mA                                                    | +85°C  |         |                        |

| DC41c            | 60                     |              | mA                                                    | +125°C |         |                        |

| DC42d            | 68                     | _            | mA                                                    | -40°C  |         | 20 MIPS <sup>(3)</sup> |

| DC42a            | 68                     |              | mA                                                    | +25°C  |         |                        |

| DC42b            | 68                     |              | mA                                                    | +85°C  | - 3.3V  |                        |

| DC42c            | 68                     | _            | mA                                                    | +125°C |         |                        |

| DC43d            | 77                     | _            | mA                                                    | -40°C  |         |                        |

| DC43a            | 77                     |              | mA                                                    | +25°C  | 2.21/   | 30 MIPS <sup>(3)</sup> |

| DC43b            | 77                     |              | mA                                                    | +85°C  | - 3.3V  | 30 MIPS(0)             |

| DC43c            | 77                     | _            | mA                                                    | +125°C | 1       |                        |

| DC44d            | 86                     | _            | mA                                                    | -40°C  |         |                        |

| DC44a            | 86                     |              | mA                                                    | +25°C  | 2.21/   |                        |

| DC44b            | 86                     | _            | mA                                                    | +85°C  | 3.3V 40 | 40 MIPS                |

| DC44c            | 86                     | _            | mA                                                    | +125°C | 1       |                        |

#### TABLE 24-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: Base Idle current (IIDLE) is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- · JTAG is disabled

- **3:** These parameters are characterized but not tested in manufacturing.

| Section Name                                 | Update Description                                                                                                                                                                                            |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 19.0 "High-Speed 10-bit              | Updated Note 1 in the ADCPC0 register (see Register 19-5).                                                                                                                                                    |

| Analog-to-Digital Converter (ADC)"           | Updated Note 3 in the ADCPC1 register (see Register 19-6).                                                                                                                                                    |

|                                              | Updated Note 2 in the ADCPC2 and ADCPC3 registers (see Register 19-7 and Register 19-8).                                                                                                                      |

| Section 21.0 "Special Features"              | Updated the second paragraph and removed the fourth paragraph in <b>Section 21.1 "Configuration Bits"</b> .                                                                                                   |

|                                              | Updated the Device Configuration Register Map (see Table 21-1).                                                                                                                                               |

| Section 24.0 "Electrical<br>Characteristics" | Updated the Absolute Maximum Ratings for high temperature and added Note 4.                                                                                                                                   |

|                                              | Updated Idle Current (IIDLE) Typical values in Table 24-6.                                                                                                                                                    |

|                                              | Updated the Typ and Max values for Parameter DI50 in the I/O Pin Input Specifications table (see Table 24-9).                                                                                                 |

|                                              | Updated the Typ and Max values for Parameters DO10 and DO27 and the Min and Typ values for Parameter DO20 in the I/O Pin Output Specifications (see Table 24-10).                                             |

|                                              | Added parameter numbers to the Auxiliary PLL Clock Timing Specifications (see Table 24-18).                                                                                                                   |

|                                              | Added parameters numbers and updated the Internal RC Accuracy Min, Typ, and Max values (see Table 24-19 and Table 24-20).                                                                                     |

|                                              | Added parameter numbers, Note 2, updated the Min and Typ parameter values for MP31 and MP32, and removed the conditions for MP10 and MP11 in the High-Speed PWM Module Timing Requirements (see Table 24-29). |

|                                              | Updated the SPIx Module Slave Mode (CKE = 1) Timing Characteristics (see Table 24-14).                                                                                                                        |

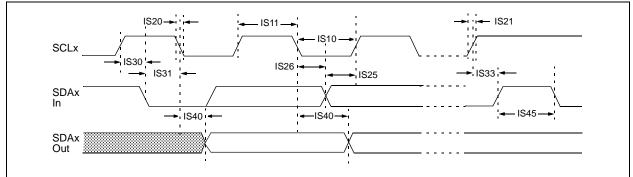

|                                              | Added Parameter IM51 to the I2Cx Bus Data Timing Requirements (Master Mode) (see Table 24-34).                                                                                                                |

|                                              | Updated the Max value for Parameter AD33 in the 10-bit High-Speed Analog-to-Digital Module Specifications (see Table 24-36).                                                                                  |

|                                              | Updated the titles and added parameter numbers to the Comparator and DAC Module Specifications (see Table 24-38 and Table 24-39) and the DAC Output Buffer Specifications (see Table 24-40).                  |

#### TABLE A-3: MAJOR SECTION UPDATES (CONTINUED)

#### INDEX

| Α                           |                 |

|-----------------------------|-----------------|

| AC Characteristics          | . 300, 338, 345 |

| Internal FRC Accuracy       |                 |

| Internal LPRC Accuracy      |                 |

| Load Conditions             | 300, 338        |

| ADC                         |                 |

| Control Registers           |                 |

| Functionality               |                 |

| Arithmetic Logic Unit (ALU) |                 |

| Assembler                   |                 |

| MPASM Assembler             |                 |

| Auxiliary Clock Generation  | 138             |

#### В

| Barrel Shifter                               |

|----------------------------------------------|

| Bit-Reversed Addressing                      |

| Example                                      |

| Implementation76                             |

| Sequence Table (16-Entry)77                  |

| Block Diagrams                               |

| 16-Bit Timer1 Module183                      |

| Connections for On-Chip Voltage Regulator270 |

| DSP Engine                                   |

| dsPIC33F06GS101 Devices with 1 SAR240        |

| dsPIC33F06GS102 Devices with 1 SAR241        |

| dsPIC33F06GS202 Devices with 1 SAR242        |

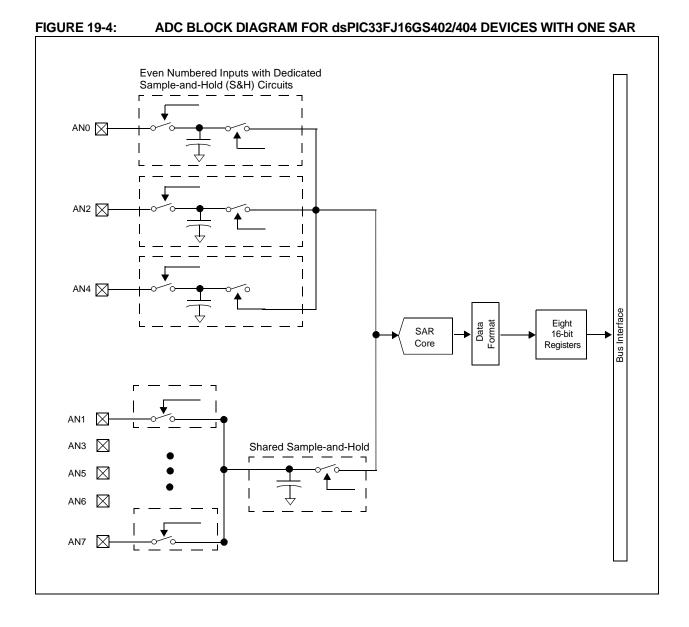

| dsPIC33F16GS402/404 Devices with 1 SAR243    |

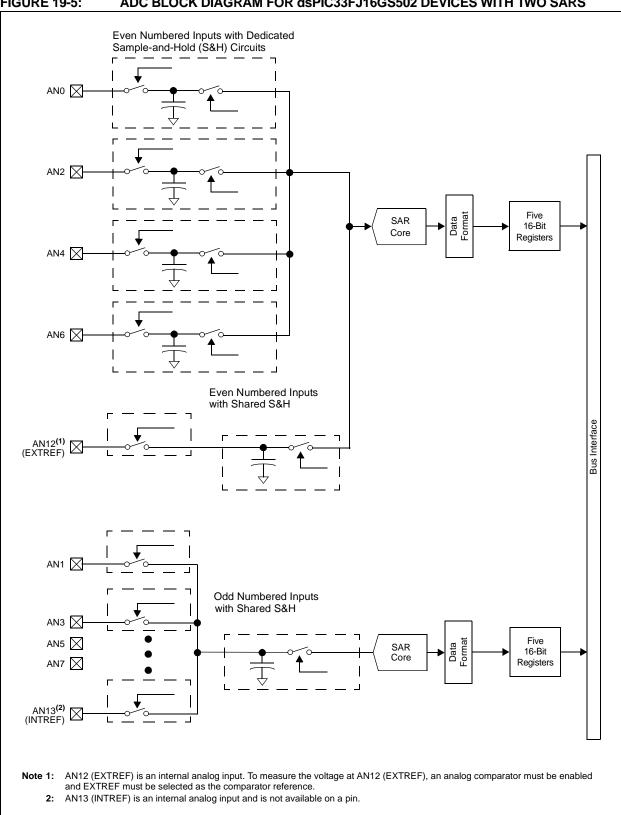

| dsPIC33F16GS502 Devices with 2 SARs244       |

| dsPIC33F16GS504 Devices with 2 SARs245       |

| dsPIC33FJ06GS101/X02 and                     |

| dsPIC33FJ16GSX02/X0418                       |

| dsPIC33FJ06GS101/X02 and                     |

| dsPIC33FJ16GSX02/X04 CPU Core32              |

| High-Speed Analog Comparator                 |

| I2CX Module226                               |

| Input Capture x191                           |

| Multiplexing of Remappable Output for RPn159 |

| Oscillator System 135                        |

| Output Compare x Module193                   |

| Partitioned Output Pair, Complementary       |

| PWM Mode200                                  |

| PLL137                                       |

| Remappable MUX Input for U1RX157             |

| Reset System                                 |

| Shared Port Structure155                     |

| Simplified Conceptual High-Speed PWM199      |

| SPIx Module219                               |

| Timer2/3 (32-Bit)                            |

| Type B Timer185                              |

| Type C Timer                                 |

| UART1                                        |

| Watchdog Timer (WDT)271                      |

| Brown-out Reset (BOR)                        |

#### С

| C Compilers        |  |

|--------------------|--|

| MPLAB XC Compilers |  |

| Clock Switching    |  |

| Enabling           |  |

| Sequence           |  |

| •                  |  |

| Code Examples                        |         |

|--------------------------------------|---------|

| Erasing a Program Memory Page        | 87      |

| Initiating a Programming Sequence    | 88      |

| Loading Write Buffers                | 88      |

| Port Write/Read                      | 156     |

| PWRSAV Instruction Syntax            | 147     |

| Code Protection                      | 67, 273 |

| CodeGuard Security                   | 267     |

| Configuration Bits                   | 267     |

| Description                          | 268     |

| Configuration Register Map           | 267     |

| Configuring Analog Port Pins         | 156     |

| CPU                                  |         |

| Control Registers                    | 34      |

| CPU Clocking System                  | 136     |

| PLL Configuration                    | 137     |

| Selection                            | 136     |

| Sources                              | 136     |

| Customer Change Notification Service | 392     |

| Customer Notification Service        |         |

| Customer Support                     | 392     |

#### D

| DAC                                                                  | 264    |

|----------------------------------------------------------------------|--------|

| Output Range                                                         | 264    |

| Data Accumulators and Adder/Subtracter                               | -      |

| Data Space Write Saturation                                          | 42     |

| Overflow and Saturation                                              | 40     |

| Round Logic                                                          | 41     |

| Write Back                                                           | 41     |

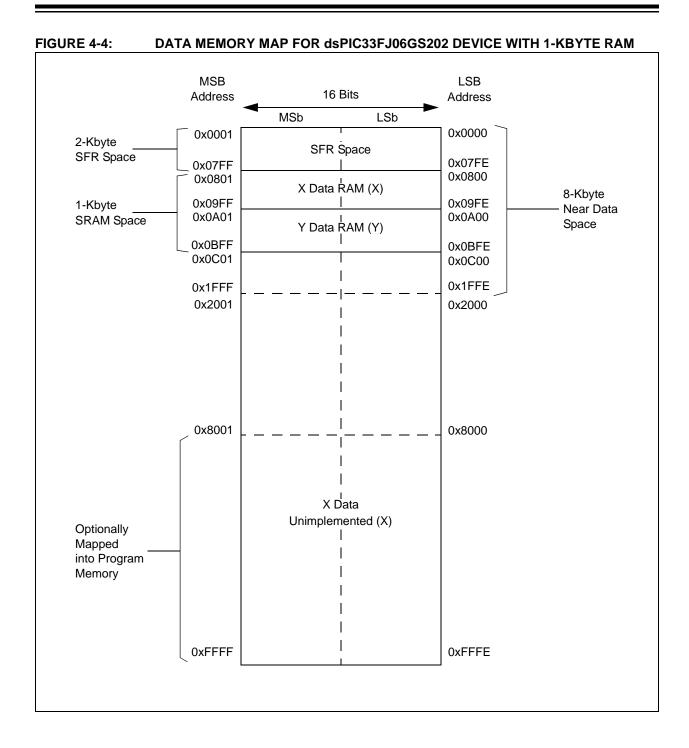

| Data Address Space                                                   | 45     |

| Alignment                                                            | 45     |

| Memory Map for dsPIC33FJ06GS101/102 Devices<br>with 256 Bytes of RAM |        |

| Memory Map for dsPIC33FJ06GS202 Device                               |        |

| with 1-Kbyte RAM                                                     |        |

| Memory Map for dsPIC33FJ16GS402/404/502/504                          |        |

| Devices with 2-Kbyte RAM                                             |        |

| Near Data Space                                                      |        |

| Software Stack                                                       |        |

| Width                                                                | 45     |

| Data Addressing                                                      |        |

| Overview                                                             | 31     |

| DC and AC Characteristics                                            |        |

| Graphs and Tables                                                    | 347    |

| DC Characteristics 288                                               | 3, 342 |

| Doze Current (IDOZE) 294                                             | 4, 344 |

| High Temperature                                                     | 334    |

| I/O Pin Input Specifications                                         | 295    |

| I/O Pin Output Specifications                                        | 7, 336 |

| Idle Current (IIDLE)                                                 | 2, 343 |

| Operating Current (IDD)                                              | ), 342 |

| Operating MIPS vs. Voltage                                           | -      |

| Power-Down Current (IPD)                                             |        |

| Program Memory 299                                                   |        |

| Temperature and Voltage                                              |        |

| Temperature and Voltage Specifications                               |        |

| Thermal Operating Conditions                                         |        |

|                                                                      |        |