Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 2K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 44-VTLA (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs404-50i-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

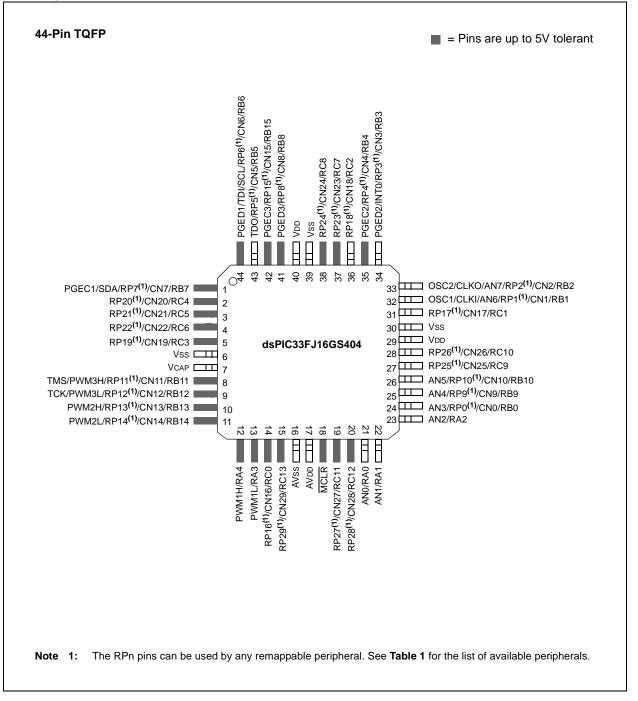

# Pin Diagrams (Continued)

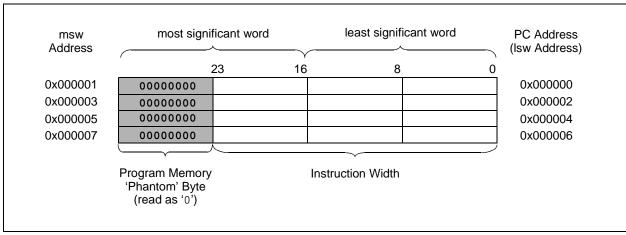

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate consider each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (see Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during the code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

### TABLE 4-22: I2C1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8                     | Bit 7 | Bit 6 | Bit 5     | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|---------|--------|---------|--------|--------|--------|-----------------------|---------------------------|-------|-------|-----------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200        | —       | _      |         | _      | _      | —      | —                     | – – I2C1 Receive Register |       |       |           |             |              |       |       | 0000  |               |

| I2C1TRN      | 0202        | _       |        | _       | _      |        | _      | _                     |                           |       |       | I         | 2C1 Transn  | nit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204        | _       |        | _       | _      |        | _      | _                     |                           |       |       | Baud Rate | e Generator | Register     |       |       |       | 0000          |

| I2C1CON      | 0206        | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN                      | GCEN  | STREN | ACKDT     | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208        | ACKSTAT | TRSTAT | _       | _      |        | BCL    | GCSTAT                | ADD10                     | IWCOL | I2COV | D_A       | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A        | _       | _      | _       |        | _      | —      | I2C1 Address Register |                           |       |       |           |             |              | 0000  |       |       |               |

| I2C1MSK      | 020C        | —       | _      |         | _      | _      | _      | AMSK<9:0>             |                           |       |       |           |             |              | 0000  |       |       |               |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-23: UART1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15   | Bit 14                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5 | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------------|----------|-------------------------------|----------|--------|--------|--------|-------|------------------------|----------|----------|-------|-------------|---------|--------|--------|-------|---------------|

| U1MODE       | 0220        | UARTEN   | —                             | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222        | UTXISEL1 | UTXINV                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224        | _        | _                             | _        | _      | _      | —      | _     |                        |          |          | UART1 | Transmit Re | egister |        |        |       | xxxx          |

| U1RXREG      | 0226        | _        | _                             | _        | _      | _      | —      | _     | UART1 Receive Register |          |          |       |             |         | 0000   |        |       |               |

| U1BRG        | 0228        |          | Baud Rate Generator Prescaler |          |        |        |        |       |                        |          |          | 0000  |             |         |        |        |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: SPI1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15                                    | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|-------------------------------------------|--------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|-------|--------|--------|---------------|

| SPI1STAT     | 0240        | SPIEN                                     |        | SPISIDL | —      |        | —      |       | _     | _     | SPIROV | _     | _     |       |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242        | —                                         | _      | _       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244        | FRMEN                                     | SPIFSD | FRMPOL  | —      | _      | _      | _     | _     | _     | _      | _     | _     | _     | _     | FRMDLY | —      | 0000          |

| SPI1BUF      | 0248        | SPI1 Transmit and Receive Buffer Register |        |         |        |        |        |       |       |       | 0000   |       |       |       |       |        |        |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| REGISTER 7    | 7-5: IFS0:                                                | INTERRUPT                        | FLAG STAT        | US REGISTE                        | ER 0             |                 |        |  |  |  |

|---------------|-----------------------------------------------------------|----------------------------------|------------------|-----------------------------------|------------------|-----------------|--------|--|--|--|

| U-0           | U-0                                                       | R/W-0                            | R/W-0            | R/W-0                             | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| —             |                                                           | ADIF                             | U1TXIF           | U1RXIF                            | SPI1IF           | SPI1EIF         | T3IF   |  |  |  |

| oit 15        |                                                           |                                  |                  |                                   |                  |                 | bit    |  |  |  |

| R/W-0         | R/W-0                                                     | R/W-0                            | U-0              | R/W-0                             | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| T2IF          | OC2IF                                                     | IC2IF                            |                  | T1IF                              | OC1IF            | IC1IF           | INTOIF |  |  |  |

| bit 7         | 0021                                                      | 10211                            |                  |                                   | 0011             | 10111           | bit    |  |  |  |

| Legend:       |                                                           |                                  |                  |                                   |                  |                 |        |  |  |  |

| R = Readable  | hit                                                       | W = Writable                     | hit              | LI – Unimplor                     | mented bit, read | d ac 'O'        |        |  |  |  |

| -n = Value at |                                                           | '1' = Bit is se                  |                  | 0 = 0 minipler<br>0' = Bit is cle |                  | x = Bit is unkn | 0000   |  |  |  |

|               | FÜR                                                       | 1 = DIL 15 50                    | ι                |                                   | aleu             |                 | OWI    |  |  |  |

| bit 15-14     | Unimplemer                                                | nted: Read as                    | ʻ0'              |                                   |                  |                 |        |  |  |  |

| bit 13        | ADIF: ADC C                                               | Group Convers                    | ion Complete I   | Interrupt Flag S                  | Status bit       |                 |        |  |  |  |

|               |                                                           | request has oc<br>request has no |                  |                                   |                  |                 |        |  |  |  |

| bit 12        | U1TXIF: UA                                                | RT1 Transmitte                   | r Interrupt Flag | g Status bit                      |                  |                 |        |  |  |  |

|               |                                                           | request has oc                   |                  |                                   |                  |                 |        |  |  |  |

|               | •                                                         | request has no                   |                  |                                   |                  |                 |        |  |  |  |

| bit 11        |                                                           | RT1 Receiver I                   |                  | Status bit                        |                  |                 |        |  |  |  |

|               |                                                           | request has oc<br>request has no |                  |                                   |                  |                 |        |  |  |  |

| bit 10        | -                                                         | Event Interrup                   |                  | oit                               |                  |                 |        |  |  |  |

|               |                                                           | request has oc                   | -                |                                   |                  |                 |        |  |  |  |

|               | •                                                         | request has no                   |                  |                                   |                  |                 |        |  |  |  |

| bit 9         | SPI1EIF: SP                                               | I1 Fault Interru                 | pt Flag Status   | bit                               |                  |                 |        |  |  |  |

|               |                                                           | request has oc                   |                  |                                   |                  |                 |        |  |  |  |

| L:1 0         | -                                                         | request has no                   |                  |                                   |                  |                 |        |  |  |  |

| bit 8         |                                                           | Interrupt Flag<br>request has oc |                  |                                   |                  |                 |        |  |  |  |

|               |                                                           | request has no                   |                  |                                   |                  |                 |        |  |  |  |

| bit 7         | -                                                         | Interrupt Flag                   |                  |                                   |                  |                 |        |  |  |  |

|               | 1 = Interrupt                                             | request has oc                   | curred           |                                   |                  |                 |        |  |  |  |

|               | •                                                         | request has no                   |                  |                                   |                  |                 |        |  |  |  |

| bit 6         |                                                           | out Compare Cl                   |                  | upt Flag Status                   | s bit            |                 |        |  |  |  |

|               |                                                           | request has oc<br>request has no |                  |                                   |                  |                 |        |  |  |  |

| bit 5         | •                                                         | Capture Chanr                    |                  | Flag Status bit                   |                  |                 |        |  |  |  |

|               | -                                                         | request has oc                   | -                | lag claide bit                    |                  |                 |        |  |  |  |

|               |                                                           | request has no                   |                  |                                   |                  |                 |        |  |  |  |

| bit 4         | Unimplemer                                                | nted: Read as                    | ʻ0'              |                                   |                  |                 |        |  |  |  |

| bit 3         | T1IF: Timer1                                              | Interrupt Flag                   | Status bit       |                                   |                  |                 |        |  |  |  |

|               | •                                                         | request has oc<br>request has no |                  |                                   |                  |                 |        |  |  |  |

| bit 2         | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |                                  |                  |                                   |                  |                 |        |  |  |  |

|               | -                                                         | request has oc                   |                  | -                                 |                  |                 |        |  |  |  |

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0              | R/W-1                                                                                  | R/W-0                                                                          | R/W-0                                                      | U-0               | R/W-1            | R/W-0           | R/W-0  |

|------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------|-------------------|------------------|-----------------|--------|

| _                | T2IP2                                                                                  | T2IP1                                                                          | T2IP0                                                      |                   | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15           | ·                                                                                      |                                                                                |                                                            |                   | •                | ·               | bit 8  |

|                  |                                                                                        | R/W-0                                                                          | R/W-0                                                      |                   |                  |                 |        |

| U-0              | R/W-1                                                                                  | 1                                                                              | 1                                                          | U-0               | U-0              | U-0             | U-0    |

| <br>bit 7        | IC2IP2                                                                                 | IC2IP1                                                                         | IC2IP0                                                     | —                 | —                | _               | bit    |

|                  |                                                                                        |                                                                                |                                                            |                   |                  |                 |        |

| Legend:          |                                                                                        |                                                                                |                                                            |                   |                  |                 |        |

| R = Readab       | le bit                                                                                 | W = Writable                                                                   | bit                                                        | U = Unimpler      | mented bit, read | d as '0'        |        |

| -n = Value a     | t POR                                                                                  | '1' = Bit is set                                                               |                                                            | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                  |                                                                                        |                                                                                |                                                            |                   |                  |                 |        |

| bit 15           | Unimplemer                                                                             | nted: Read as '                                                                | 0'                                                         |                   |                  |                 |        |

| bit 14-12        |                                                                                        | Timer2 Interrupt                                                               | •                                                          |                   |                  |                 |        |

|                  | 111 = Interru                                                                          | pt is Priority 7 (                                                             | highest priori                                             | ty interrupt)     |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                            |                   |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                            |                   |                  |                 |        |

|                  | 001 = Interru                                                                          | pt is Priority 1                                                               |                                                            |                   |                  |                 |        |

|                  | 000 = Interru                                                                          | pt source is dis                                                               | abled                                                      |                   |                  |                 |        |

| bit 11           | Unimplemer                                                                             | nted: Read as '                                                                | 0'                                                         |                   |                  |                 |        |

| bit 10-8         | OC2IP<2:0>                                                                             | : Output Compa                                                                 | are Channel 2                                              | 2 Interrupt Prior | ity bits         |                 |        |

|                  | 111 = Interru                                                                          | pt is Priority 7 (                                                             | highest priori                                             | ty interrunt)     |                  |                 |        |

|                  |                                                                                        |                                                                                | ingiloot phon                                              | ty interrupt)     |                  |                 |        |

|                  | •                                                                                      |                                                                                | ingridet priori                                            | ty interrupty     |                  |                 |        |

|                  | •<br>•                                                                                 |                                                                                | ingricet priori                                            | ty interrupty     |                  |                 |        |

|                  | •<br>•<br>001 = Interru                                                                | ipt is Priority 1                                                              | ingreet profi                                              | ty monopty        |                  |                 |        |

|                  |                                                                                        | ipt is Priority 1<br>ipt source is dis                                         |                                                            |                   |                  |                 |        |

| bit 7            | 000 = Interru                                                                          |                                                                                | abled                                                      |                   |                  |                 |        |

|                  | 000 = Interru<br>Unimplemer                                                            | pt source is dis                                                               | abled<br>0'                                                |                   | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '                                           | abled<br>0'<br>Channel 2 Inte                              | errupt Priority b | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | abled<br>0'<br>Channel 2 Inte                              | errupt Priority b | its              |                 |        |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | abled<br>0'<br>Channel 2 Inte                              | errupt Priority b | its              |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•                  | ipt source is dis<br>nted: Read as '<br>Input Capture (                        | abled<br>0'<br>Channel 2 Inte                              | errupt Priority b | its              |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru | ipt source is dis<br>nted: Read as '<br>Input Capture (<br>ipt is Priority 7 ( | abled<br><sup>0'</sup><br>Channel 2 Inte<br>highest priori | errupt Priority b | its              |                 |        |

# REGISTER 7-20: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

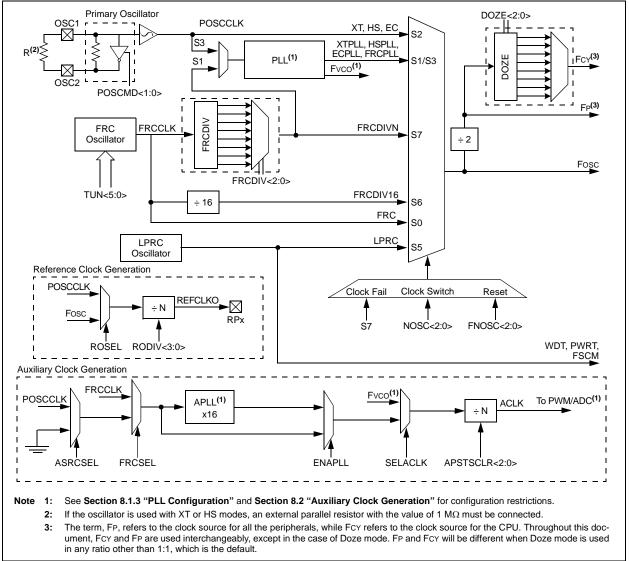

# 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase-Locked Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- A Clock Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

- Auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 8-1.

## FIGURE 8-1: OSCILLATOR SYSTEM DIAGRAM

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| REGISTER 8      | -2: CLKDI                                                    | V: CLOCK D               | IVISOR REC                           | SISTER <sup>(1)</sup>                 |                  |                    |              |

|-----------------|--------------------------------------------------------------|--------------------------|--------------------------------------|---------------------------------------|------------------|--------------------|--------------|

| R/W-0           | R/W-0                                                        | R/W-1                    | R/W-1                                | R/W-0                                 | R/W-0            | R/W-0              | R/W-0        |

| ROI             | DOZE2                                                        | DOZE1                    | DOZE0                                | DOZEN <sup>(2)</sup>                  | FRCDIV2          | FRCDIV1            | FRCDIVC      |

| bit 15          |                                                              |                          |                                      |                                       |                  |                    | bit          |

| R/W-0           | R/W-1                                                        | U-0                      | R/W-0                                | R/W-0                                 | R/W-0            | R/W-0              | R/W-0        |

| PLLPOST1        | PLLPOST0                                                     | _                        | PLLPRE4                              | PLLPRE3                               | PLLPRE2          | PLLPRE1            | PLLPRE       |

| bit 7           |                                                              |                          |                                      |                                       |                  |                    | bit          |

| Legend:         |                                                              |                          |                                      |                                       |                  |                    |              |

| R = Readable    | hit                                                          | W = Writable             | hit                                  |                                       | antad hit raa    |                    |              |

|                 |                                                              |                          |                                      | -                                     | nented bit, read |                    |              |

| -n = Value at F | <u>'OR</u>                                                   | '1' = Bit is se          | [                                    | '0' = Bit is clea                     | ared             | x = Bit is unkr    | IOWN         |

| bit 15          | ROI: Recover                                                 | on Interrupt b           | it                                   |                                       |                  |                    |              |

|                 |                                                              | -                        |                                      | d the processo                        | r clock/periphe  | ral clock ratio is | s set to 1:1 |

|                 |                                                              |                          | t on the DOZE                        |                                       |                  |                    |              |

| bit 14-12       | DOZE<2:0>:                                                   | Processor Clo            | ck Reduction S                       | Select bits                           |                  |                    |              |

|                 | 111 = Fcy/12                                                 | 8                        |                                      |                                       |                  |                    |              |

|                 | 110 = FCY/64                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 101 = FCY/32                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 100 = FCY/16                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 011 = FCY/8 (<br>010 = FCY/4                                 | delault)                 |                                      |                                       |                  |                    |              |

|                 | 001 = FCY/2                                                  |                          |                                      |                                       |                  |                    |              |

|                 | 000 = Fcy/1                                                  |                          |                                      |                                       |                  |                    |              |

| bit 11          | DOZEN: Doze                                                  | e Mode Enable            | e bit <sup>(2)</sup>                 |                                       |                  |                    |              |

|                 |                                                              |                          | ies the ratio be<br>eral clock ratio |                                       | pheral clocks a  | and the process    | or clocks    |

| bit 10-8        | FRCDIV<2:0>                                                  | : Internal Fas           | t RC Oscillator                      | Postscaler bits                       | 6                |                    |              |

|                 | 111 = FRC di<br>110 = FRC di<br>101 = FRC di<br>100 = FRC di | vide-by-64<br>vide-by-32 |                                      |                                       |                  |                    |              |

|                 | 011 = FRC di                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 010 = FRC di                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 001 = FRC di                                                 | •                        |                                      |                                       |                  |                    |              |

| h# 7 C          | 000 = FRC di                                                 | <b>,</b> (               | ,                                    | Calaat hita (al                       |                  |                    | eeler)       |

| bit 7-6         |                                                              |                          | Output Divider                       | Select bits (all                      | so denoted as    | 'N2', PLL posts    | caler)       |

|                 | 11 = Output/8<br>10 = Reserve                                |                          |                                      |                                       |                  |                    |              |

|                 | 01 = Output/4                                                |                          |                                      |                                       |                  |                    |              |

|                 | 00 = Output/2                                                | •                        |                                      |                                       |                  |                    |              |

| bit 5           | Unimplement                                                  | t <b>ed:</b> Read as     | 0'                                   |                                       |                  |                    |              |

| bit 4-0         | PLLPRE<4:0                                                   | >: PLL Phase             | Detector Input                       | Divider bits (a                       | so denoted as    | 'N1', PLL prese    | caler)       |

|                 | 11111 <b>= I</b> npu                                         |                          |                                      | , , , , , , , , , , , , , , , , , , , |                  | · •                | ,            |

|                 | •                                                            |                          |                                      |                                       |                  |                    |              |

|                 | •                                                            |                          |                                      |                                       |                  |                    |              |

|                 | •                                                            | 10                       |                                      |                                       |                  |                    |              |

|                 | 00001 = Inpu                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 00000 = Inpu                                                 | t/2 (default)            |                                      |                                       |                  |                    |              |

#### CIGTED 0 2

Note 1: This register is reset only on a Power-on Reset (POR).

2: This bit is cleared when the ROI bit is set and an interrupt occurs.

# 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices can manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 9.1 Clock Frequency and Clock Switching

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

### 9.2 Instruction-Based Power-Saving Modes

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

### 9.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes the items such as the Input Change Notification on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

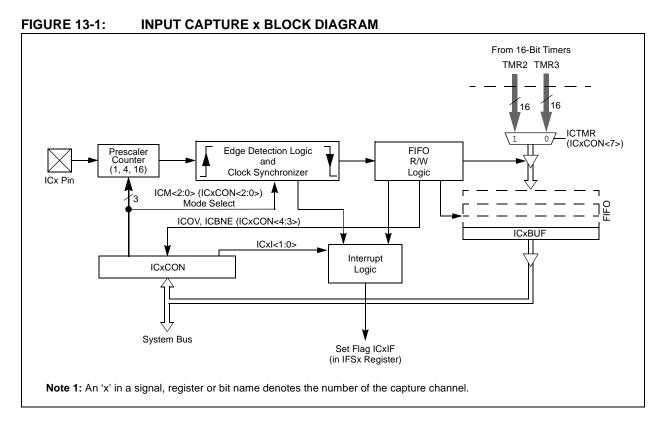

# 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70198) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices support up to two input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select one of the two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Use of input capture to provide additional sources of external interrupts

© 2008-2014 Microchip Technology Inc.

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

NOTES:

| R/W-0           | R/W-0                       | R/W-0                                    | R/W-0                      | R/W-0                 | R/W-0                 | R/W-0                   | R/W-0  |  |  |  |

|-----------------|-----------------------------|------------------------------------------|----------------------------|-----------------------|-----------------------|-------------------------|--------|--|--|--|

| PENH            | PENL                        | POLH                                     | POLL                       | PMOD1 <sup>(1)</sup>  | PMOD0 <sup>(1)</sup>  | OVRENH                  | OVRENL |  |  |  |

| bit 15          |                             |                                          |                            |                       |                       |                         | bit    |  |  |  |

| R/W-0           | R/W-0                       | R/W-0                                    | R/W-0                      | R/W-0                 | R/W-0                 | R/W-0                   | R/W-0  |  |  |  |

| OVRDAT1         | OVRDAT0                     | FLTDAT1 <sup>(2)</sup>                   | FLTDAT0 <sup>(2)</sup>     | CLDAT1 <sup>(2)</sup> | CLDAT0 <sup>(2)</sup> | SWAP                    | OSYNC  |  |  |  |

| bit 7           |                             |                                          |                            |                       |                       |                         | bit    |  |  |  |

| Legend:         |                             |                                          |                            |                       |                       |                         |        |  |  |  |

| R = Readable    | bit                         | W = Writable                             | bit                        | U = Unimplen          | nented bit, read      | l as '0'                |        |  |  |  |

| -n = Value at F | POR                         | '1' = Bit is set                         |                            | '0' = Bit is cle      |                       | x = Bit is unkr         | nown   |  |  |  |

| bit 15          | PENH: PWN                   | /H Output Pin                            | Ownership bit              |                       |                       |                         |        |  |  |  |

|                 |                             | dule controls th                         | -                          |                       |                       |                         |        |  |  |  |

|                 | 0 = GPIO mo                 | dule controls th                         | ne PWMxH pin               | 1                     |                       |                         |        |  |  |  |

| bit 14          |                             | IL Output Pin C                          | =                          |                       |                       |                         |        |  |  |  |

|                 |                             | dule controls th                         |                            |                       |                       |                         |        |  |  |  |

| L:1 40          |                             | dule controls th                         |                            |                       |                       |                         |        |  |  |  |

| bit 13          |                             | /H Output Pin                            | •                          |                       |                       |                         |        |  |  |  |

|                 |                             | oin is active-low<br>oin is active-hig   |                            |                       |                       |                         |        |  |  |  |

| bit 12          | -                           | _ Output Pin Po                          |                            |                       |                       |                         |        |  |  |  |

|                 | 1 = PWMxL pin is active-low |                                          |                            |                       |                       |                         |        |  |  |  |

|                 | •                           | in is active-hig                         |                            |                       |                       |                         |        |  |  |  |

| bit 11-10       | PMOD<1:0>:                  | PWM # I/O P                              | in Mode bits <sup>(1</sup> | )                     |                       |                         |        |  |  |  |

|                 | 11 = PWM I/0                | D pin pair is in t                       | he True Indep              | endent Output         | t mode                |                         |        |  |  |  |

|                 |                             | D pin pair is in t                       |                            | •                     |                       |                         |        |  |  |  |

|                 |                             | D pin pair is in t<br>D pin pair is in t |                            |                       |                       |                         |        |  |  |  |

|                 |                             | Override Enabl                           | •                          |                       | noue                  |                         |        |  |  |  |

| bit 9           | -                           | <1> provides d                           |                            |                       |                       |                         |        |  |  |  |

|                 |                             | erator provides d                        |                            |                       | n pin                 |                         |        |  |  |  |

| bit 8           | •                           | verride Enable                           |                            |                       |                       |                         |        |  |  |  |

|                 |                             | <0> provides d                           |                            |                       | pin                   |                         |        |  |  |  |

|                 |                             | erator provides                          |                            |                       | - P                   |                         |        |  |  |  |

| bit 7-6         | OVRDAT<1:0                  | >: Data for P                            | WMxH and PV                | VMxL Pins if C        | Override is Enab      | led bits                |        |  |  |  |

|                 | If OVERENH                  | = 1, then OVR                            | DAT<1> provid              | des data for P\       | WМхН                  |                         |        |  |  |  |

|                 |                             | = 1, then OVR                            | -                          |                       |                       |                         |        |  |  |  |

| bit 5-4         | FLTDAT<1:0                  | State for P\                             | WMxH and PW                | VMxL Pins if Fl       | LTMOD is Enab         | led bits <sup>(2)</sup> |        |  |  |  |

|                 |                             | LTMOD> = 0:                              |                            |                       |                       |                         |        |  |  |  |

|                 |                             | ve, then FLTDA<br>ve, then FLTDA         | •                          |                       |                       |                         |        |  |  |  |

|                 |                             | TLTMOD > = 1:                            | •                          |                       |                       |                         |        |  |  |  |

|                 |                             | t is active, then                        |                            |                       | or PWMxH              |                         |        |  |  |  |

|                 |                             |                                          | P                          |                       | PWMxL                 |                         |        |  |  |  |

# REGISTER 15-14: IOCONx: PWMx I/O CONTROL REGISTER

yield unpredictable results.

2: The state represents the active/inactive state of the PWM module depending on the POLH and POLL bit settings.

#### REGISTER 15-14: IOCONx: PWMx I/O CONTROL REGISTER (CONTINUED)

| bit 3-2 | CLDAT<1:0>: State for PWMxH and PWMxL Pins if CLMODE is Enabled bits <sup>(2)</sup>                          |

|---------|--------------------------------------------------------------------------------------------------------------|

|         | FCLCONx <ifltmod> = 0: Normal Fault mode:</ifltmod>                                                          |

|         | If current-limit is active, then CLDAT<1> provides the state for PWMxH                                       |

|         | If current-limit is active, then CLDAT<0> provides the state for PWMxL                                       |

|         | FCLCONx <ifltmod> = 1: Independent Fault mode:</ifltmod>                                                     |

|         | CLDAT<1:0> bits are ignored.                                                                                 |

| bit 1   | SWAP<1:0>: Swap PWMxH and PWMxL pins                                                                         |

|         | 1 = PWMxH output signal is connected to the PWMxL pin and the PWMxL signal is connected to the<br>PWMxH pins |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                 |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                   |

|         | 1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWM time base                          |

|         | 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary                           |

| Note 1: | These bits should be changed only when PTEN = 0. Changing the clock selection during operation will          |

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 2: The state represents the active/inactive state of the PWM module depending on the POLH and POLL bit settings.

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | <b>URXINV:</b> UARTx Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <b>BRGH:</b> High Baud Rate Enable bit<br>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)<br>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode) |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                              |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                                      |

- **Note 1:** Refer to "**UART**" (DS70188) in the "*dsPIC33F/PIC24H Family Reference Manual*" for information on enabling the UART module for receive or transmit operation.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 19-6: ADCPC1: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 1 (CONTINUED)

TRGSRC2<4:0>: Trigger 2 Source Selection bits<sup>(2)</sup> bit 4-0 Selects trigger source for conversion of Analog Channels AN5 and AN4. 11111 = Timer2 period match 11011 = Reserved 11010 = PWM Generator 4 current-limit ADC trigger 11001 = PWM Generator 3 current-limit ADC trigger 11000 = PWM Generator 2 current-limit ADC trigger 10111 = PWM Generator 1 current-limit ADC trigger 10110 = Reserved 10010 = Reserved 10001 = PWM Generator 4 secondary trigger is selected 10000 = PWM Generator 3 secondary trigger is selected 01111 = PWM Generator 2 secondary trigger is selected 01110 = PWM Generator 1 secondary trigger is selected 01101 = Reserved 01100 = Timer1 period match 01000 = Reserved 00111 = PWM Generator 4 primary trigger is selected 00110 = PWM Generator 3 primary trigger is selected 00101 = PWM Generator 2 primary trigger is selected 00100 = PWM Generator 1 primary trigger is selected 00011 = PWM Special Event Trigger is selected 00010 = Global software trigger is selected 00001 = Individual software trigger is selected 00000 = No conversion is enabled

- Note 1: These bits are available in the dsPIC33FJ16GS402/404, dsPIC33FJ16GS504, dsPIC33FJ16GS502 and dsPIC33FJ06GS101 devices only.

- 2: These bits are available in the dsPIC33FJ16GS502, dsPIC33FJ16GS504, dsPIC33FJ06GS102, dsPIC33FJ06GS202 and dsPIC33FJ16GS402/404 devices only.

- **3:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

| Bit Field    | Register | RTSP Effect | Description                                                                                                                                                                                                                                                                                                                                |

|--------------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POSCMD<1:0>  | FOSC     | Immediate   | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                          |

| FWDTEN       | FWDT     | Immediate   | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN bit in the RCON register will have no effect)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul> |

| WINDIS       | FWDT     | Immediate   | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                             |

| WDTPRE       | FWDT     | Immediate   | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                                                      |

| WDTPOST<3:0> | FWDT     | Immediate   | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                      |

| FPWRT<2:0>   | FPOR     | Immediate   | Power-on Reset Timer Value Select bits<br>111 = PWRT = 128 ms<br>110 = PWRT = 64 ms<br>101 = PWRT = 32 ms<br>100 = PWRT = 16 ms<br>011 = PWRT = 8 ms<br>010 = PWRT = 4 ms<br>001 = PWRT = 2 ms<br>000 = PWRT = Disabled                                                                                                                    |

| JTAGEN       | FICD     | Immediate   | JTAG Enable bit<br>1 = JTAG is enabled<br>0 = JTAG is disabled                                                                                                                                                                                                                                                                             |

| ICS<1:0>     | FICD     | Immediate   | ICD Communication Channel Select Enable bits<br>11 = Communicates on PGEC1 and PGED1<br>10 = Communicates on PGEC2 and PGED2<br>01 = Communicates on PGEC3 and PGED3<br>00 = Reserved, do not use.                                                                                                                                         |

#### TABLE 21-2: dsPIC33F CONFIGURATION BITS DESCRIPTION (CONTINUED)

| AC CHARA            | CTERISTICS            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |    |     |     |       |            |  |  |

|---------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|-------|------------|--|--|

| Param<br>No. Symbol |                       | Characteristic <sup>(1)</sup>                                                                                                                               |    | Тур | Max | Units | Conditions |  |  |

| HSP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                   | —  | 10  | 25  | ns    |            |  |  |

| HSP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                  | 28 | _   |     | ns    |            |  |  |

| HSP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                   | 35 | —   |     | ns    |            |  |  |

### TABLE 25-9: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

# TABLE 25-10: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHAR      | ACTERISTICS           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |

|--------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |

| HSP35        | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               |     | 10  | 25  | ns    |            |

| HSP36        | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                            | 35  | _   | _   | ns    |            |

| HSP40        | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 28  | _   | _   | ns    |            |

| HSP41        | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 35  |     |     | ns    |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

| Section Name             | Update Description                                                                                                                                                             |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 24.0 "Electrical | Updated the Absolute Maximum Ratings.                                                                                                                                          |

| Characteristics"         | Updated the Operating MIPS vs. Voltage (see Table 24-1).                                                                                                                       |

|                          | Updated Parameter DC10 and Note 4, and removed Parameter DC18 from the DC Temperature and Voltage Specifications (see Table 24-4).                                             |

|                          | Updated Note 2 in the IDD Operating Current specification (see Table 24-5                                                                                                      |

|                          | Updated all Typical values and Note 2 in the IIDLE Operating Current specification (see Table 24-6).                                                                           |

|                          | Updated Typical values for Parameters DC60d, DC60a, DC60b, and DC60c, and Note 2 in the IPD Operating Current specification (see Table 24-7).                                  |

|                          | Added all Typical values and Note 2 in the IDOZE Operating Current specification (see Table 24-8).                                                                             |

|                          | Updated Parameters DI19 and DI50, added Parameters DI128, DI129, DI60a, DI60b, and DI60c, and removed Parameter DI57 in the I/O Pin Inpu Specifications (see Table 24-9).      |

|                          | Revised all I/O Pinout Output Specifications (see Table 24-10).                                                                                                                |

|                          | Added Notes 2 and 3 to the BOR Electrical Characteristics (see Table 24-<br>11).                                                                                               |

|                          | Added Note 1 to Internal Voltage Regulator Specifications (see Table 24-13).                                                                                                   |

|                          | Updated the External Clock Timing diagram (see Figure 24-2).                                                                                                                   |

|                          | Added Note 2 to the PLL Clock Timing Specifications (see Table 24-17).                                                                                                         |

|                          | Removed Note 2 from the Internal FRC Accuracy (see Table 24-19).                                                                                                               |

|                          | Updated Parameters DO31 and DO32 in the I/O Timing Requirements (see Table 24-21).                                                                                             |

|                          | Updated the External Clock Timing Requirements for Timer1, Timer2, and Timer3 (see Table 24-23, Table 24-24, and Table 24-25, respectively).                                   |

|                          | Updated Parameters OC15 and OC20 in the Simple OC/PWM Mode Timin Requirements (see Table 24-28).                                                                               |

|                          | Revised all SPIx Module Timing Characteristics diagrams and all Timing Requirements (see Figure 24-11 through Figure 24-18 and Table 24-30 through Table 24-37, respectively). |

|                          | Added Note 2 to the 10-bit High-Speed ADC Module Specifications (see Table 24-40).                                                                                             |

|                          | Added Note 2 to the 10-bit High-Speed ADC Module Timing Requirements (see Table 24-41).                                                                                        |

|                          | Added Note 2 to the Comparator Module Specifications (see Table 24-42).                                                                                                        |

|                          | Added Parameter DA08 and Note 2 in the DAC Module Specifications (see Table 24-43).                                                                                            |

|                          | Updated Parameter DA16 and Note 2 in the DAC Output Buffer DC Specifications (see Table 24-44).                                                                                |

# TABLE A-4: MAJOR SECTION UPDATES (CONTINUED)

| IFS5 (Interrupt Flag Status 5)109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|