Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

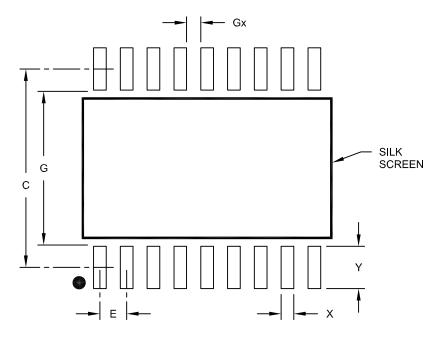

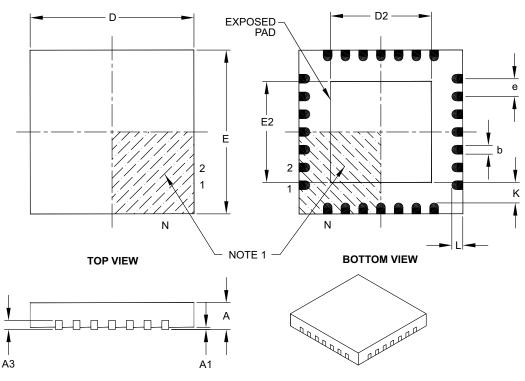

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs404-e-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the primary reference for the operation of a particular module or device feature.

| Note: | To access the documents listed below,<br>browse to the documentation section<br>of the dsPIC33FJ16GS504 product<br>page of the Microchip web site<br>(www.microchip.com). |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | In addition to parameters, features, and<br>other documentation, the resulting page<br>provides links to the related family<br>reference manual sections.                 |

- "Introduction" (DS70197)

- "CPU" (DS70204)

- "Data Memory" (DS70202)

- "Program Memory" (DS70203)

- "Flash Programming" (DS70191)

- "Reset" (DS70192)

- "Watchdog Timer (WDT) and Power-Saving Modes" (DS70196)

- "I/O Ports" (DS70193)

- "Timers" (DS70205)

- "Input Capture" (DS70198)

- "Output Compare" (DS70005157)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70188)

- "Serial Peripheral Interface (SPI)" (DS70206)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195)

- "CodeGuard™ Security (DS70199)

- "Programming and Diagnostics" (DS70207)

- "Device Configuration" (DS70194)

- "Interrupts (Part IV)" (DS70300)

- "Oscillator (Part IV)" (DS70307)

- "High- Speed PWM Module" (DS70000323)

- "High-Speed 10-Bit ADC" (DS70000321)

- "High-Speed Analog Comparator" (DS70296)

- "Oscillator (Part VI)" (DS70644)

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0         | All<br>Resets |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|---------------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  |          | MATHERR  | ADDRERR | STKERR   | OSCFAIL  |               | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     | -        | _        | _       |          | _        |          | -        | _        |          | _        | _       | INT2EP   | INT1EP   | INT0EP        | 0000          |

| IFS0         | 0084        | _       | _        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  |          | T2IF     | _        |          | -        | T1IF    | OC1IF    | _        | <b>INT0IF</b> | 0000          |

| IFS1         | 0086        | _       | _        | INT2IF   | _        | _       |          | _        |          | -        | _        |          | INT1IF   | CNIF    | _        | MI2C1IF  | SI2C1IF       | 0000          |

| IFS3         | 008A        | _       | _        | _        | _        | _       | _        | PSEMIF   | _        | _        | _        | _        | _        | _       |          |          | _             | 0000          |

| IFS4         | 008C        | —       | _        | _        | _        | _       | -        | —        | _        | _        | —        | _        | _        | _       | —        | U1EIF    | _             | 0000          |

| IFS5         | 008E        | —       | PWM1IF   | _        | _        | _       | -        | —        | _        | _        | —        | _        | _        | _       | —        | _        | _             | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | _        | _       | _        | —        | _        | _        | —        | _        | _        | _       | —        | PWM4IF   | _             | 0000          |

| IFS7         | 0092        |         | _        | _        | _        |         | _        | _        | _        | _        | —        | _        | _        | -       | -        | ADCP3IF  | _             | 0000          |

| IEC0         | 0094        |         | _        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  | _        | T2IE     | _        | _        | _        | T1IE    | OC1IE    |          | INT0IE        | 0000          |

| IEC1         | 0096        | _       | _        | INT2IE   | —        | _       | _        | —        | _        |          | —        |          | INT1IE   | CNIE    | _        | MI2C1IE  | SI2C1IE       | 0000          |

| IEC2         | 0098        | _       | _        |          | —        | _       | _        | —        | _        |          | —        |          | _        | _       | _        | _        |               | 0000          |

| IEC3         | 009A        | _       |          |          | —        | _       |          | PSEMIE   |          |          | _        |          |          | _       | _        | _        |               | 0000          |

| IEC4         | 009C        | _       |          |          | —        | _       |          | _        |          |          | _        |          |          | _       | _        | U1EIE    |               | 0000          |

| IEC5         | 009E        | -       | PWM1IE   |          | —        | _       |          | -        |          |          | _        |          |          | _       | _        | _        |               | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  | _        | —        | _       | -        | —        | -        | -        | —        | -        | —        | —       | _        | PWM4IE   | _             | 0000          |

| IEC7         | 00A2        | _       | —        | _        | —        | _       | -        | —        | -        | -        | —        | -        | —        | —       | _        | ADCP3IE  | _             | 0000          |

| IPC0         | 00A4        | _       | T1IP2    | T1IP1    | T1IP0    | _       | OC1IP2   | OC1IP1   | OC1IP0   | -        | —        | -        | —        | —       | INT0IP2  | INT0IP1  | INT0IP2       | 4404          |

| IPC1         | 00A6        | _       | T2IP2    | T2IP1    | T2IP0    | _       | -        | —        | -        | -        | —        | -        | —        | —       | _        | _        | _             | 4000          |

| IPC2         | 00A8        | —       | U1RXIP2  | U1RXIP1  | U1RXIP0  | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 | _       | —        | _        | _             | 4440          |

| IPC3         | 00AA        | —       | _        | _        | —        | —       | _        | —        | _        |          | ADIP2    | ADIP1    | ADIP0    | _       | U1TXIP2  | U1TXIP1  | U1TXIP0       | 0044          |

| IPC4         | 00AC        | —       | CNIP2    | CNIP1    | CNIP0    | —       | _        | —        | _        | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0      | 4044          |

| IPC5         | 00AE        | —       | _        | _        | —        | —       | _        | —        | _        | _        | —        | _        | _        | _       | INT1IP2  | INT1IP21 | INT1IP0       | 0004          |

| IPC7         | 00B2        | —       | —        | _        | —        | —       |          | —        | _        | _        | INT2IP2  | INT2IP1  | INT2IP0  | —       | —        | —        | _             | 0040          |

| IPC14        | 00C0        | —       | —        | _        | —        | —       |          | —        | _        | _        | PSEMIP2  | PSEMIP1  | PSEMIP0  | —       | —        | —        | _             | 0040          |

| IPC16        | 00C4        | —       | —        | _        | —        | —       |          | —        | _        | _        | U1EIP2   | U1EIP1   | U1EIP0   | —       | —        | —        | _             | 0400          |

| IPC23        | 00D2        | —       | —        | _        | —        | —       | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | —        | _        | —        | —       | —        | —        | _             | 0040          |

| IPC24        | 00D4        | —       | —        | —        | —        | —       | —        | —        | —        | _        | PWM4IP2  | PWM4IP1  | PWM4IP0  | —       | —        | —        | _             | 4400          |

| IPC27        | 00DA        | —       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | _       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _        | —        | _        | —        | _       | —        | _        | _             | 0040          |

| IPC28        | 00DC        | _       |          |          | —        | _       |          | —        |          |          | ADCP3IP2 | ADCP3IP1 | ADCP3IP0 | _       | _        | _        | _             | 0000          |

| INTTREG      | 00E0        |         | _        | _        | _        | ILR3    | ILR2     | ILR1     | ILR0     |          | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0       | 0000          |

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06GS101 DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-14: INPUT CAPTURE REGISTER MAP FOR dsPIC33FJ16GSX02 AND dsPIC33FJ16GSX04

| SFR<br>Addr | Bit 15                       | Bit 14                             | Bit 13                                            | Bit 12                                                           | Bit 11                                                                          | Bit 10                                                                                         | Bit 9                                                                                                         | Bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bit 7                                                                                                                                     | Bit 6                                                                                                                                                                                                                                                                                   | Bit 5                                                                                                                                                                 | Bit 4                                                                                                                                                                               | Bit 3                                                                                                                                                                                             | Bit 2                                                                                                                                                                                                           | Bit 1                                                                                                                                                                                                                         | Bit 0                                                                                                                                                                                                                                       | All<br>Resets                                                                                                                                                            |

|-------------|------------------------------|------------------------------------|---------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0140        |                              |                                    |                                                   |                                                                  |                                                                                 |                                                                                                | Inpu                                                                                                          | t Capture 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Register                                                                                                                                  |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                             | xxxx                                                                                                                                                                     |

| 0142        |                              |                                    | ICSIDL                                            | _                                                                | -                                                                               | _                                                                                              | _                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ICTMR                                                                                                                                     | ICI1                                                                                                                                                                                                                                                                                    | ICI0                                                                                                                                                                  | ICOV                                                                                                                                                                                | ICBNE                                                                                                                                                                                             | ICM2                                                                                                                                                                                                            | ICM1                                                                                                                                                                                                                          | ICM0                                                                                                                                                                                                                                        | 0000                                                                                                                                                                     |

| 0144        |                              |                                    |                                                   |                                                                  |                                                                                 |                                                                                                | Inpu                                                                                                          | t Capture 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Register                                                                                                                                  |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                             | xxxx                                                                                                                                                                     |

| 0146        |                              |                                    | ICSIDL                                            | _                                                                | -                                                                               | _                                                                                              | _                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ICTMR                                                                                                                                     | ICI1                                                                                                                                                                                                                                                                                    | ICI0                                                                                                                                                                  | ICOV                                                                                                                                                                                | ICBNE                                                                                                                                                                                             | ICM2                                                                                                                                                                                                            | ICM1                                                                                                                                                                                                                          | ICM0                                                                                                                                                                                                                                        | 0000                                                                                                                                                                     |

| _           | Addr<br>0140<br>0142<br>0144 | Addr         Bit 15           0140 | Addr         Bit 15         Bit 14           0140 | Addr         Bit 15         Bit 14         Bit 13           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 30           0140         0142         -         -         IcSIDL         -         -         -         -         -         -         -         -         -         -         0144         Input         Input         Input         Input         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <t< td=""><td>Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 3           0140        </td><td>Addr     Bit 15     Bit 14     Bit 13     Bit 12     Bit 11     Bit 10     Bit 9     Bit 8     Bit 7       0140     0142     -     -     Input Capture 1 Register       0142     -     -     ICSIDL     -     -     -     ICTMR       0144     -     -     -     -     -     2 Register</td><td>Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6           0140        </td><td>Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5           0140        </td><td>Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 8         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4           0140        </td><td>Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 10         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3           0140        </td><td>Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 10         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2           0140        </td><td>Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1           0140        </td><td>Addr         Bit 13         Bit 13         Bit 12         Bit 11         Bit 10         Bit 20         Bit 30         Bit 2         Bit 12         Bit 10           0140        </td></t<> | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 3           0140 | Addr     Bit 15     Bit 14     Bit 13     Bit 12     Bit 11     Bit 10     Bit 9     Bit 8     Bit 7       0140     0142     -     -     Input Capture 1 Register       0142     -     -     ICSIDL     -     -     -     ICTMR       0144     -     -     -     -     -     2 Register | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 8         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 10         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 10         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2           0140 | Addr         Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1           0140 | Addr         Bit 13         Bit 13         Bit 12         Bit 11         Bit 10         Bit 20         Bit 30         Bit 2         Bit 12         Bit 10           0140 |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: OUTPUT COMPARE REGISTER MAP FOR dsPIC33FJ06GS101 AND dsPIC33FJ06GSX02

|        | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7      | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------|------|--------|--------|--------|--------|--------|--------|------------|-------------|------------|--------|-------|-------|--------|-------|-------|-------|---------------|

| OC1RS  | 0180 |        |        |        |        |        |        | Output Con | npare 1 Sec | ondary Reg | gister |       |       |        |       |       |       | xxxx          |

| OC1R   | 0182 |        |        |        |        |        |        | Outpu      | It Compare  | 1 Register |        |       |       |        |       |       |       | xxxx          |

| OC1CON | 0184 | —      | _      | OCSIDL | —      | _      | _      | _          | _           | —          | —      | —     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

|        |      | —      | —      | OCSIDL | —      | —      |        |            |             |            | _      | _     | OCFLT | OCTSEL | OCM2  | OCM1  |       | OCM0          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-16: OUTPUT COMPARE REGISTER MAP FOR dsPIC33FJ16GSX02 AND dsPIC33FJ06GSX04

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8      | Bit 7      | Bit 6   | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-----------|------------|------------|---------|-------|-------|--------|-------|-------|-------|---------------|

| OC1RS        | 0180        |        |        |        |        |        |        | Output Co | mpare 1 Se | condary Re | egister |       |       |        |       |       |       | xxxx          |

| OC1R         | 0182        |        |        |        |        |        |        | Outp      | ut Compare | 1 Register | r       |       |       |        |       |       |       | xxxx          |

| OC1CON       | 0184        | _      | _      | OCSIDL | _      | _      | _      | _         | _          | _          | _       | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC2RS        | 0186        |        |        |        |        |        |        | Output Co | mpare 2 Se | condary Re | egister |       |       |        |       |       |       | xxxx          |

| OC2R         | 0188        |        |        |        |        |        |        | Outp      | ut Compare | 2 Register | r       |       |       |        |       |       |       | xxxxx         |

| OC2CON       | 018A        | _      | _      | OCSIDL | _      | _      | _      |           | _          | _          | _       | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-17: HIGH-SPEED PWM REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8    | Bit 7    | Bit 6 | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|---------|----------|----------|-------|----------|----------|---------|----------|----------|----------|---------------|

| PTCON        | 0400        | PTEN   | _      | PTSIDL | SESTAT | SEIEN  | EIPU   | SYNCPOL | SYNCOEN  | SYNCEN   | _     | SYNCSRC1 | SYNCSRC0 | SEVTPS3 | SEVTPS2  | SEVTPS1  | SEVTPS0  | 0000          |

| PTCON2       | 0402        |        | _      | _      |        | _      |        | _       | _        | -        | _     | _        | _        | _       | PCLKDIV2 | PCLKDIV1 | PCLKDIV0 | 0000          |

| PTPER        | 0404        |        |        |        |        |        |        |         |          |          |       |          |          |         | FFF8     |          |          |               |

| SEVTCMP      | 0406        |        |        |        |        |        |        | SEVTC   | MP<15:3> |          |       |          |          |         | _        | _        | _        | 0000          |

| MDC          | 040A        |        |        |        |        |        |        |         |          | MDC<15:0 | )>    |          |          |         |          |          |          | 0000          |

© 2008-2014 Microchip Technology Inc.

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-27: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6          | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|--------|--------|----------|----------|----------|----------|----------|-------------|----------------|---------|-----------|----------|----------|----------|----------|---------------|

| ADCON        | 0300        | ADON   | —      | ADSIDL | SLOWCLK  | —        | GSWTRG   | _        | FORM     | EIE         | ORDER          | SEQSAMP | ASYNCSAMP | —        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _      | -      | —      | _        | _        |          | _        | —        | _           | _              | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _      | -      | —      | _        | _        |          | _        | —        | _           | P6RDY          | _       | _         | _        | P2RDY    | P1RDY    | PORDY    | 0000          |

| ADBASE       | 0308        |        |        |        |          |          |          |          | ADBASE<1 | 5:1>        |                |         |           |          |          |          | —        | 0000          |

| ADCPC0       | 030A        | IRQEN1 | PEND1  | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0          | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | _      | -      | —      | _        | _        |          | _        | —        | IRQEN2      | PEND2          | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCPC3       | 0310        | _      |        | —      | _        | _        | _        | —        | —        | IRQEN6      | PEND6          | SWTRG6  | TRGSRC64  | TRGSRC63 | TRGSRC62 | TRGSRC61 | TRGSRC60 | 0000          |

| ADCBUF0      | 0320        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 0              |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |        |        |        |          |          |          |          | ADC E    | Data Buffer | <sup>.</sup> 1 |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 2              |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 3              |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 4              |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |        |        |        |          |          |          |          | ADC E    | Data Buffer | 5              |         |           |          |          |          |          | xxxx          |

| ADCBUF12     | 0338        |        |        |        |          |          |          |          | ADC D    | ata Buffer  | 12             |         |           |          |          |          |          | xxxx          |

| ADCBUF13     | 033A        |        |        |        |          |          |          |          | ADC D    | Data Buffer | 13             |         |           |          |          |          |          | xxxx          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

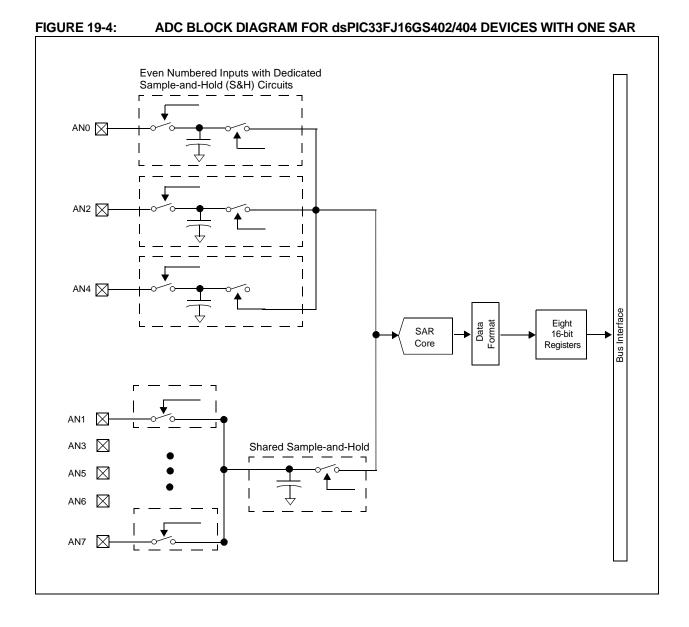

# TABLE 4-28: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ16GS402/404 DEVICES ONLY

|              | -           |         |          |            | -           |                 |               |               |              |            |       | -       |           |          |          |          |          |               |

|--------------|-------------|---------|----------|------------|-------------|-----------------|---------------|---------------|--------------|------------|-------|---------|-----------|----------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13     | Bit 12      | Bit 11          | Bit 10        | Bit 9         | Bit 8        | Bit 7      | Bit 6 | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADCON        | 0300        | ADON    | —        | ADSIDL     | SLOWCLK     | _               | GSWTRG        | _             | FORM         | EIE        | ORDER | SEQSAMP | ASYNCSAMP | -        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _       | _        | _          | _           | —               | _             | _             | _            | PCFG7      | PCFG6 | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _       | _        | _          | _           | —               | _             | _             | _            | _          | _     | _       | _         | P3RDY    | P2RDY    | P1RDY    | P0RDY    | 0000          |

| ADBASE       | 0308        |         |          |            |             |                 |               |               | ADBASE<15    | :1>        |       |         |           |          |          |          | —        | 0000          |

| ADCPC0       | 030A        | IRQEN1  | PEND1    | SWTRG1     | TRGSRC14    | TRGSRC13        | TRGSRC12      | TRGSRC11      | TRGSRC10     | IRQEN0     | PEND0 | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | IRQEN3  | PEND3    | SWTRG3     | TRGSRC34    | TRGSRC33        | TRGSRC32      | TRGSRC31      | TRGSRC30     | IRQEN2     | PEND2 | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCBUF0      | 0320        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 0     |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 1     |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 2     |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 3     |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 4     |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 5     |         |           |          |          |          |          | xxxx          |

| ADCBUF6      | 032C        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 6     |         |           |          |          |          |          | xxxx          |

| ADCBUF7      | 032E        |         |          |            |             |                 |               |               | ADC D        | ata Buffer | 7     |         |           |          |          |          |          | xxxx          |

| Legend:      | x =         | unknown | value on | Reset, — = | unimplement | ed, read as '0' | . Reset value | s are shown i | n hexadecima | al.        |       |         |           |          |          |          |          |               |

|              |               |                  |                 |                   | 11.0             |                 | 11.0    |

|--------------|---------------|------------------|-----------------|-------------------|------------------|-----------------|---------|

| U-0          | U-0           | R/W-0            | U-0             | U-0               | U-0              | U-0             | U-0     |

|              | —             | INT2IF           | —               | —                 | —                | —               |         |

| bit 15       |               |                  |                 |                   |                  |                 | bit     |

| U-0          | U-0           | U-0              | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

|              | —             | _                | INT1IF          | CNIF              | AC1IF            | MI2C1IF         | SI2C1IF |

| bit 7        |               |                  |                 |                   |                  |                 | bit     |

|              |               |                  |                 |                   |                  |                 |         |

| Legend:      |               |                  |                 |                   |                  |                 |         |

| R = Readab   | le bit        | W = Writable     | bit             | U = Unimplen      | nented bit, read | d as '0'        |         |

| -n = Value a | t POR         | '1' = Bit is set |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|              |               |                  |                 |                   |                  |                 |         |

| bit 15-14    | Unimplemer    | nted: Read as '  | 0'              |                   |                  |                 |         |

| bit 13       | INT2IF: Exte  | rnal Interrupt 2 | Flag Status bi  | t                 |                  |                 |         |

|              |               | request has oc   |                 |                   |                  |                 |         |

|              | 0 = Interrupt | request has no   | t occurred      |                   |                  |                 |         |

| bit 12-5     | Unimplemer    | nted: Read as '  | 0'              |                   |                  |                 |         |

| bit 4        | INT1IF: Exte  | rnal Interrupt 1 | Flag Status bi  | t                 |                  |                 |         |

|              |               | request has oc   |                 |                   |                  |                 |         |

|              | 0 = Interrupt | request has no   | t occurred      |                   |                  |                 |         |

| bit 3        | CNIF: Input ( | Change Notifica  | ation Interrupt | Flag Status bit   |                  |                 |         |

|              |               | request has oc   |                 |                   |                  |                 |         |

|              | •             | request has no   |                 |                   |                  |                 |         |

| bit 2        | AC1IF: Analo  | og Comparator    | 1 Interrupt Fla | g Status bit      |                  |                 |         |

|              |               | request has oc   |                 |                   |                  |                 |         |

|              | •             | request has no   |                 |                   |                  |                 |         |

| bit 1        |               | C1 Master Even   | •               | ag Status bit     |                  |                 |         |

|              |               | request has oc   |                 |                   |                  |                 |         |

|              |               | request has no   |                 |                   |                  |                 |         |

| bit 0        |               | 1 Slave Events   |                 | Status bit        |                  |                 |         |

|              |               | request has oc   |                 |                   |                  |                 |         |

|              | 0 = Interrupt | request has no   | t occurred      |                   |                  |                 |         |

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| U-0    | U-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0   |

|--------|-----|-----|-----|------|------|------|-------|

| —      | —   | _   | _   | ILR3 | ILR2 | ILR1 | ILR0  |

| bit 15 |     |     |     |      |      |      | bit 8 |

### REGISTER 7-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0   | R-0     |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:      |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                    |  |  |  |  |  |  |

|--------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|--|--|--|--|--|--|

| R = Readab   | le bit                                               | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U = Unimplemented bit, | , read as '0'      |  |  |  |  |  |  |

| -n = Value a | t POR                                                | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |  |  |