Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 35                                                                                 |

| Program Memory Size        | 16KB (16K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 44-TQFP                                                                            |

| Supplier Device Package    | 44-TQFP (10x10)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs404t-50i-pt |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0         | R/W-0                                                                              | U-0                                             | U-0           | U-0                   | U-0              | R/W-0             | R/W-0        |  |  |  |

|---------------|------------------------------------------------------------------------------------|-------------------------------------------------|---------------|-----------------------|------------------|-------------------|--------------|--|--|--|

| TRAPR         | IOPUWR                                                                             |                                                 |               |                       |                  | СМ                | VREGS        |  |  |  |

| bit 15        |                                                                                    |                                                 |               |                       |                  |                   | bit 8        |  |  |  |

| DAMO          | DAVO                                                                               | DANO                                            | DAMO          | DAMO                  | D/M/ O           |                   |              |  |  |  |

| R/W-0         | R/W-0                                                                              | R/W-0<br>SWDTEN <sup>(2)</sup>                  | R/W-0         | R/W-0                 | R/W-0            | R/W-1             | R/W-1        |  |  |  |

| EXTR<br>bit 7 | SWR                                                                                | SWDIEN                                          | WDTO          | SLEEP                 | IDLE             | BOR               | POR<br>bit ( |  |  |  |

|               |                                                                                    |                                                 |               |                       |                  |                   |              |  |  |  |

| Legend:       |                                                                                    |                                                 |               |                       |                  |                   |              |  |  |  |

| R = Readable  | e bit                                                                              | W = Writable b                                  | bit           | U = Unimpler          | nented bit, rea  | d as '0'          |              |  |  |  |

| -n = Value at | POR                                                                                | '1' = Bit is set                                |               | '0' = Bit is cle      | ared             | x = Bit is unk    | nown         |  |  |  |

| bit 15        | TRAPR: Trap                                                                        | Reset Flag bit                                  |               |                       |                  |                   |              |  |  |  |

|               | •                                                                                  | onflict Reset has                               | s occurred    |                       |                  |                   |              |  |  |  |

|               | 0 = A Trap Co                                                                      | onflict Reset has                               | s not occurre | d                     |                  |                   |              |  |  |  |

| bit 14        | IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit                    |                                                 |               |                       |                  |                   |              |  |  |  |

|               | •                                                                                  | l opcode detec                                  |               | gal address mo        | ode or Uninitia  | lized W registe   | er used as a |  |  |  |

|               |                                                                                    | Pointer caused<br>I opcode or Unit              |               | egister Reset h       | as not occurre   | d                 |              |  |  |  |

| bit 13-10     |                                                                                    | ted: Read as '0                                 |               | og.oto: 11000111      |                  | -                 |              |  |  |  |

| bit 9         | -                                                                                  | ation Mismatch                                  |               |                       |                  |                   |              |  |  |  |

|               | -                                                                                  | uration Mismatc                                 | -             | occurred              |                  |                   |              |  |  |  |

|               | 0 = A Configu                                                                      | uration Mismatc                                 | h Reset has   | NOT occurred          |                  |                   |              |  |  |  |

| bit 8         | VREGS: Volta                                                                       | EGS: Voltage Regulator Standby During Sleep bit |               |                       |                  |                   |              |  |  |  |

|               |                                                                                    | egulator is activ                               |               |                       |                  |                   |              |  |  |  |

| h:+ 7         | -                                                                                  | egulator goes in                                | -             | node during Sie       | ер               |                   |              |  |  |  |

| bit 7         | EXTR: External Reset Pin (MCLR) bit<br>1 = A Master Clear (pin) Reset has occurred |                                                 |               |                       |                  |                   |              |  |  |  |

|               |                                                                                    | Clear (pin) Res                                 |               |                       |                  |                   |              |  |  |  |

| bit 6         |                                                                                    | re Reset Flag (                                 |               |                       |                  |                   |              |  |  |  |

|               |                                                                                    | instruction has                                 |               |                       |                  |                   |              |  |  |  |

|               | 0 = A reset                                                                        | instruction has                                 | not been exe  | ecuted                |                  |                   |              |  |  |  |

| bit 5         | SWDTEN: So                                                                         | oftware Enable/I                                | Disable of W  | DT bit <sup>(2)</sup> |                  |                   |              |  |  |  |

|               | 1 = WDT is e<br>0 = WDT is di                                                      |                                                 |               |                       |                  |                   |              |  |  |  |

| bit 4         |                                                                                    | hdog Timer Tim                                  | e-out Flag bi | it                    |                  |                   |              |  |  |  |

|               | 1 = WDT time                                                                       | e-out has occuri<br>e-out has not oc            | ed            |                       |                  |                   |              |  |  |  |

| bit 3         | SLEEP: Wak                                                                         | e-up from Sleep                                 | Flag bit      |                       |                  |                   |              |  |  |  |

|               |                                                                                    | as been in Sleep                                | -             |                       |                  |                   |              |  |  |  |

|               | 0 = Device ha                                                                      | as not been in S                                | leep mode     |                       |                  |                   |              |  |  |  |

| bit 2         |                                                                                    | up from Idle Fla                                | g bit         |                       |                  |                   |              |  |  |  |

|               |                                                                                    | as in Idle mode<br>as not in Idle m             | ode           |                       |                  |                   |              |  |  |  |

|               | of the Reset sta<br>use a device Re                                                | atus bits can be                                |               | d in software. S      | etting one of th | nese bits in soft | ware does no |  |  |  |

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| U-0                                                                  | U-0 | U-0 | U-0 | U-0 | U-0  | R/W-0           | U-0   |

|----------------------------------------------------------------------|-----|-----|-----|-----|------|-----------------|-------|

| —                                                                    | _   | _   | —   | _   | _    | PSEMIF          | —     |

| bit 15                                                               |     |     |     |     |      |                 | bit 8 |

|                                                                      |     |     |     |     |      |                 |       |

| U-0                                                                  | U-0 | U-0 | U-0 | U-0 | U-0  | U-0             | U-0   |

| _                                                                    |     | _   | —   |     |      |                 |       |

| bit 7                                                                |     |     |     |     |      |                 | bit 0 |

|                                                                      |     |     |     |     |      |                 |       |

| Legend:                                                              |     |     |     |     |      |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |     |     |     |      | as '0'          |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared              |     |     |     |     | ared | x = Bit is unkr | nown  |

|                                                                      |     |     |     |     |      |                 |       |

#### REGISTER 7-7: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| bit 15-10 | Unimplemented: Read as '0'                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------|

| bit 9     | PSEMIF: PWM Special Event Match Interrupt Flag Status bit                                           |

|           | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 8-0   | Unimplemented: Read as '0'                                                                          |

#### REGISTER 7-8: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | —   | U1EIF | —     |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 U1EIF: UART1 Error Interrupt Flag Status bit

I = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 0 Unimplemented: Read as '0'

| U-0           | U-0             | U-0                              | U-0            | U-0              | U-0              | U-0             | U-0     |  |  |  |  |

|---------------|-----------------|----------------------------------|----------------|------------------|------------------|-----------------|---------|--|--|--|--|

| 0-0           | 0-0             | 0-0                              | 0-0            | 0-0              | 0-0              | 0-0             | 0-0     |  |  |  |  |

|               |                 |                                  |                |                  |                  |                 |         |  |  |  |  |

| bit 15        |                 |                                  |                |                  |                  |                 | bit 8   |  |  |  |  |

|               |                 |                                  |                | -                | <b>D</b> 444 a   | <b>D A A A</b>  | -       |  |  |  |  |

| U-0           | U-0             | U-0                              | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |

|               |                 |                                  | ADCP6IF        | ADCP5IF          | ADCP4IF          | ADCP3IF         | ADCP2IF |  |  |  |  |

| bit 7 bit 0   |                 |                                  |                |                  |                  |                 |         |  |  |  |  |

|               |                 |                                  |                |                  |                  |                 |         |  |  |  |  |

| Legend:       |                 |                                  |                |                  |                  |                 |         |  |  |  |  |

| R = Readable  | e bit           | W = Writable                     | bit            | U = Unimpler     | nented bit, read | l as '0'        |         |  |  |  |  |

| -n = Value at | POR             | '1' = Bit is set                 |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |

|               |                 |                                  |                |                  |                  |                 |         |  |  |  |  |

| bit 15-5      | Unimplemen      | ted: Read as '                   | 0'             |                  |                  |                 |         |  |  |  |  |

| bit 4         | ADCP6IF: AD     | DC Pair 6 Conv                   | ersion Done li | nterrupt Flag S  | tatus bit        |                 |         |  |  |  |  |

|               | 1 = Interrupt r | equest has oc                    | curred         |                  |                  |                 |         |  |  |  |  |

|               | 0 = Interrupt r | equest has not                   | occurred       |                  |                  |                 |         |  |  |  |  |

| bit 3         | ADCP5IF: AD     | DC Pair 5 Conv                   | ersion Done I  | nterrupt Flag S  | tatus bit        |                 |         |  |  |  |  |

|               |                 | equest has oc                    |                |                  |                  |                 |         |  |  |  |  |

|               | 0 = Interrupt r | equest has not                   | occurred       |                  |                  |                 |         |  |  |  |  |

| bit 2         |                 | DC Pair 4 Conv                   |                | nterrupt Flag S  | tatus bit        |                 |         |  |  |  |  |

|               |                 | equest has oc                    |                |                  |                  |                 |         |  |  |  |  |

|               | •               | equest has not                   |                |                  |                  |                 |         |  |  |  |  |

| bit 1         |                 | DC Pair 3 Conv                   |                | nterrupt Flag S  | tatus bit        |                 |         |  |  |  |  |

|               |                 | equest has oc                    |                |                  |                  |                 |         |  |  |  |  |

| h:1.0         | •               | equest has not                   |                |                  | 4 - 4            |                 |         |  |  |  |  |

| bit 0         |                 | C Pair 2 Conv                    |                | nterrupt Flag S  | tatus bit        |                 |         |  |  |  |  |

|               |                 | equest has oco<br>equest has not |                |                  |                  |                 |         |  |  |  |  |

|               |                 | equest has no                    | occurreu       |                  |                  |                 |         |  |  |  |  |

#### REGISTER 7-11: IFS7: INTERRUPT FLAG STATUS REGISTER 7

| U-0                 | R/W-1                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                             | U-0                            | R/W-1            | R/W-0           | R/W-0    |  |

|---------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------|------------------|-----------------|----------|--|

| —                   | ADCP1IP2                                                                                  | ADCP1IP1                                                                                                                              | ADCP1IP0                                                          | —                              | ADCP0IP2         | ADCP0IP1        | ADCP0IP0 |  |

| oit 15              |                                                                                           |                                                                                                                                       | •                                                                 |                                |                  |                 | bit 8    |  |

|                     |                                                                                           |                                                                                                                                       |                                                                   |                                |                  |                 |          |  |

| U-0                 | U-0                                                                                       | U-0                                                                                                                                   | U-0                                                               | U-0                            | U-0              | U-0             | U-0      |  |

| _                   | —                                                                                         | —                                                                                                                                     | —                                                                 | —                              | —                |                 | _        |  |

| oit 7               | ·                                                                                         | •                                                                                                                                     |                                                                   |                                |                  |                 | bit 0    |  |

|                     |                                                                                           |                                                                                                                                       |                                                                   |                                |                  |                 |          |  |

| Legend:             |                                                                                           |                                                                                                                                       |                                                                   |                                |                  |                 |          |  |

| R = Readable        | e bit                                                                                     | W = Writable                                                                                                                          | bit                                                               | U = Unimpler                   | mented bit, read | l as '0'        |          |  |

| -n = Value at       | POR                                                                                       | '1' = Bit is set                                                                                                                      |                                                                   | '0' = Bit is cle               | ared             | x = Bit is unkr | nown     |  |

|                     |                                                                                           |                                                                                                                                       |                                                                   |                                |                  |                 |          |  |

| bit 15              | Unimplemen                                                                                | ted: Read as '                                                                                                                        | 0'                                                                |                                |                  |                 |          |  |

| L 1 4 4 4 0         |                                                                                           |                                                                                                                                       |                                                                   |                                |                  |                 |          |  |

| DIT 14-12           | ADCP1IP<2:0                                                                               | D>: ADC Pair 1                                                                                                                        | Conversion E                                                      | Oone Interrupt                 | Priority bits    |                 |          |  |

| Dit 14-12           |                                                                                           | D>: ADC Pair 1<br>ot is Priority 7 (                                                                                                  |                                                                   | •                              | Priority bits    |                 |          |  |

| dit 14-12           |                                                                                           |                                                                                                                                       |                                                                   | •                              | Priority bits    |                 |          |  |

| dit 14-12           |                                                                                           |                                                                                                                                       |                                                                   | •                              | Priority bits    |                 |          |  |

| DIT 14-12           |                                                                                           | ot is Priority 7 (                                                                                                                    |                                                                   | •                              | Priority bits    |                 |          |  |

| dit 14-12           | 111 = Interrup<br>•<br>•<br>001 = Interrup                                                | ot is Priority 7 (                                                                                                                    | highest priorit                                                   | •                              | Priority bits    |                 |          |  |

| bit 14-12<br>bit 11 | <pre>111 = Interrup</pre>                                                                 | ot is Priority 7 (<br>ot is Priority 1                                                                                                | highest priorit <u>i</u><br>abled                                 | •                              | Priority bits    |                 |          |  |

|                     | <pre>111 = Interrup</pre>                                                                 | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis                                                                            | highest priorit <u>;</u><br>abled<br>0'                           | y interrupt)                   |                  |                 |          |  |

| pit 11              | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>ADCP0IP<2:0 | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '                                                   | highest priority<br>abled<br>0'<br>) Conversion E                 | y interrupt)<br>Done Interrupt |                  |                 |          |  |

| pit 11              | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>ADCP0IP<2:0 | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '<br><b>)&gt;:</b> ADC Pair 0                       | highest priority<br>abled<br>0'<br>) Conversion E                 | y interrupt)<br>Done Interrupt |                  |                 |          |  |

| pit 11              | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>ADCP0IP<2:0 | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '<br><b>)&gt;:</b> ADC Pair 0                       | highest priority<br>abled<br>0'<br>) Conversion E                 | y interrupt)<br>Done Interrupt |                  |                 |          |  |

| pit 11              | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>ADCP0IP<2:0 | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '<br><b>D&gt;:</b> ADC Pair 0<br>ot is Priority 7 ( | highest priority<br>abled<br>0'<br>) Conversion E                 | y interrupt)<br>Done Interrupt |                  |                 |          |  |

| pit 11              | <pre>111 = Interrup</pre>                                                                 | ot is Priority 7 (<br>ot is Priority 1<br>ot source is dis<br><b>ted:</b> Read as '<br><b>D&gt;:</b> ADC Pair 0<br>ot is Priority 7 ( | highest priorit<br>abled<br>o'<br>Conversion E<br>highest priorit | y interrupt)<br>Done Interrupt |                  |                 |          |  |

#### REGISTER 7-32: IPC27: INTERRUPT PRIORITY CONTROL REGISTER 27

| R/W-0           | R-0                                                                                                                                            | R/W-1                                                                 | U-0          | U-0             | R/W-1                                                          | R/W-1           | R/W-1    |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|-----------------|----------------------------------------------------------------|-----------------|----------|--|

| ENAPLL          | APLLCK                                                                                                                                         | SELACLK                                                               | _            | —               | APSTSCLR2                                                      | APSTSCLR1       | APSTSCLR |  |

| bit 15          | •                                                                                                                                              |                                                                       |              |                 |                                                                | •               | bit 0    |  |

| R/W-0           | R/W-0                                                                                                                                          | U-0                                                                   | U-0          | U-0             | U-0                                                            | U-0             | U-0      |  |

| ASRCSEL         | FRCSEL                                                                                                                                         | _                                                                     |              |                 | _                                                              | _               | _        |  |

| bit 7           |                                                                                                                                                |                                                                       |              |                 |                                                                |                 |          |  |

| Legend:         |                                                                                                                                                |                                                                       |              |                 |                                                                |                 |          |  |

| R = Readable    | bit                                                                                                                                            | W = Writable b                                                        | oit          | U = Unimple     | emented bit, read                                              | d as '0'        |          |  |

| -n = Value at P | OR                                                                                                                                             | '1' = Bit is set                                                      |              | ʻ0' = Bit is c  | leared                                                         | x = Bit is unkn | own      |  |

| bit 15          | ENAPLL: Au<br>1 = APLL is e<br>0 = APLL is d                                                                                                   |                                                                       | ole bit      |                 |                                                                |                 |          |  |

| bit 14          | 1 = Indicates                                                                                                                                  | PLL Locked Statu<br>that auxiliary PL<br>that auxiliary PL            | L is in lock |                 |                                                                |                 |          |  |

| bit 13          | 1 = Auxiliary                                                                                                                                  | oscillators provi                                                     | des the sou  | rce clock for a | Clock Divider bi<br>auxiliary clock div<br>auxiliary clock dir | rider           |          |  |

| bit 12-11       | •                                                                                                                                              | ited: Read as '0                                                      |              |                 |                                                                | Vider           |          |  |

| bit 10-8        | -                                                                                                                                              | :2:0>: Auxiliary (                                                    |              | ıt Dividar hits |                                                                |                 |          |  |

|                 | 111 = Divideo<br>110 = Divideo<br>101 = Divideo<br>100 = Divideo<br>011 = Divideo<br>010 = Divideo<br>001 = Divideo<br>001 = Divideo           | d by 1<br>d by 2<br>d by 4<br>d by 8<br>d by 16<br>d by 32<br>d by 64 |              |                 |                                                                |                 |          |  |

| bit 7           | ASRCSEL: Select Reference Clock Source for Auxiliary Clock bit<br>1 = Primary oscillator is the clock source<br>0 = No clock input is selected |                                                                       |              |                 |                                                                |                 |          |  |

| bit 6           |                                                                                                                                                | lect Reference (<br>RC clock for aux                                  |              | e for Auxiliary | PLL bit                                                        |                 |          |  |

|                 | 0 = Input cloc                                                                                                                                 | k source is dete                                                      |              | ASRCSEL bit     | setting                                                        |                 |          |  |

#### REGISTER 8-5: ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER<sup>(1)</sup>

**Note 1:** This register is reset only on a Power-on Reset (POR).

#### 10.2 Open-Drain Configuration

In addition to the PORTx, LATx and TRISx registers for data control, some digital-only port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (for example, 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to **"Pin Diagrams"** for the available pins and their functionality.

#### 10.3 Configuring Analog Port Pins

The ADPCFG and TRISx registers control the operation of the Analog-to-Digital (A/D) port pins. The port pins that are to function as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The ADPCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORTx register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 10.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP. An example is shown in Example 10-1.

#### 10.5 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 30 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a Change-of-State.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when the push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on Change Notification pins should always be disabled when the port pin is configured as a digital output.

#### EQUATION 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| BTSS | PORTB, #13 | ; | Next Instruction                |

|      |            |   |                                 |

#### **10.7** Peripheral Pin Select Registers

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices implement 34 registers for remappable peripheral configuration:

- 15 Input Remappable Peripheral Registers

- 17 Output Remappable Peripheral Registers

Note: Input and output register values can only be changed if OSCCON<IOLOCK> = 0. See Section 10.6.3.1 "Control Register Lock" for a specific command sequence. Not all output remappable peripheral registers are implemented on all devices. See the specific register description for further details.

#### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

#### Legend:

| =ogonan           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

#### bit 15-14 Unimplemented: Read as '0'

bit 13-8

bit 7-0

INT1R<5:0>: Assign External Interrupt 1 (INTR1) to the Corresponding RPn Pin bits

111111 = Input tied to Vss

100011 = Input tied to RP35

100010 = Input tied to RP34

100000 = Input tied to RP32

.

.

00000 = Input tied to RP0

Unimplemented: Read as '0'

© 2008-2014 Microchip Technology Inc.

#### 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

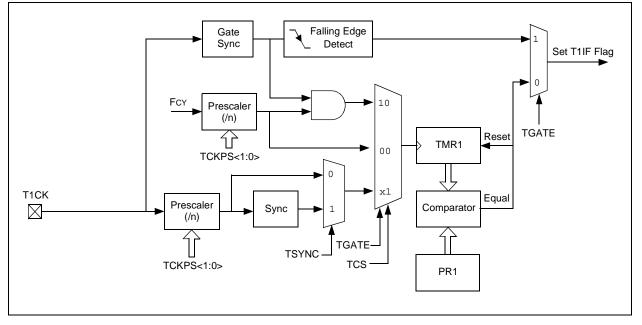

The Timer1 module is a 16-bit timer, which can serve as a time counter for the Real-Time Clock (RTC), or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low-power 32 kHz crystal oscillator available on the device

- Can be operated in Asynchronous Counter mode from an external clock source

- Optionally, the external clock input (T1CK) can be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 11-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

The timer control bit settings for different operating modes are given in the Table 11-1.

| TABLE 11-1: TIN | ER MODE SETTINGS |

|-----------------|------------------|

|-----------------|------------------|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | x     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| HS/HC-0      | ) HS/HC-0                | HS/HC-0                                       | R/W-0                        | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

|--------------|--------------------------|-----------------------------------------------|------------------------------|------------------|----------------------|----------------------|---------------------|

| FLTSTAT(     | 1) CLSTAT <sup>(1)</sup> | TRGSTAT                                       | FLTIEN                       | CLIEN            | TRGIEN               | ITB <sup>(3)</sup>   | MDCS <sup>(3)</sup> |

| bit 15       | ł                        |                                               |                              |                  |                      |                      | bit 8               |

|              |                          |                                               |                              |                  |                      |                      |                     |

| R/W-0        | R/W-0                    | U-0                                           | U-0                          | U-0              | R/W-0                | R/W-0                | R/W-0               |

| DTC1         | DTC0                     | —                                             | —                            |                  | CAM <sup>(2,3)</sup> | XPRES <sup>(4)</sup> | IUE                 |

| bit 7        |                          |                                               |                              |                  |                      |                      | bit                 |

| Legend:      |                          | HC = Hardware                                 | Clearable bit                | HS = Hardw       | are Settable bi      | it                   |                     |

| R = Readal   | hle hit                  | W = Writable bit                              |                              |                  | mented bit, rea      |                      |                     |

| -n = Value a |                          | '1' = Bit is set                              |                              | '0' = Bit is cle |                      | x = Bit is unl       | nown                |

|              |                          | 1 – Dit 13 Set                                |                              |                  | caleu                |                      | NIOWII              |

| bit 15       | FLTSTAT: F               | ault Interrupt Statu                          | us bit <sup>(1)</sup>        |                  |                      |                      |                     |

|              |                          | rrupt is pending                              |                              |                  |                      |                      |                     |

|              |                          | interrupt is pendin                           | g; this bit is cle           | ared by setting  | FLTIEN = 0           |                      |                     |

| bit 14       | CLSTAT: Cu               | urrent-Limit Interru                          | pt Status bit <sup>(1)</sup> |                  |                      |                      |                     |

|              |                          | mit interrupt is per<br>nt-limit interrupt is | Q                            | t is cleared by  | setting CLIEN        | = 0                  |                     |

| bit 13       | TRGSTAT: Tr              | rigger Interrupt Sta                          | itus bit                     |                  |                      |                      |                     |

|              |                          | terrupt is pending                            |                              |                  |                      |                      |                     |

|              | 0 = No trigge            | r interrupt is pendi                          | ng; this bit is cl           | eared by settin  | g TRGIEN = 0         | )                    |                     |

| bit 12       | FLTIEN: Fai              | ult Interrupt Enable                          | e bit                        |                  |                      |                      |                     |

|              |                          | rrupt is enabled                              |                              |                  |                      |                      |                     |

|              |                          | rrupt is disabled a                           |                              | T bit is cleared |                      |                      |                     |

| bit 11       |                          | rent-Limit Interrupt                          |                              |                  |                      |                      |                     |

|              |                          | mit interrupt is ena<br>mit interrupt is dis  |                              | CLSTAT bit is c  | leared               |                      |                     |

| bit 10       | TRGIEN: Trig             | ger Interrupt Enat                            | ole bit                      |                  |                      |                      |                     |

|              |                          | event generates a<br>vent interrupts are      |                              |                  | it is cleared        |                      |                     |

| bit 9        | ITB: Indepe              | ndent Time Base I                             | Mode bit <sup>(3)</sup>      |                  |                      |                      |                     |

|              | 1 = PHASEx/              | /SPHASEx registe<br>egister provides tir      | r provides time              |                  | r this PWM ge        | enerator             |                     |

| bit 8        |                          | ster Duty Cycle Re                            | -                            |                  |                      |                      |                     |

|              |                          | ister provides duty<br>Cx register provid     |                              |                  |                      | erator               |                     |

| bit 7-6      |                          | ead-Time Control                              |                              |                  | lie i till gene      |                      |                     |

|              | 11 = Reserve             |                                               | 513                          |                  |                      |                      |                     |

|              |                          | ne function is disa                           | bled                         |                  |                      |                      |                     |

|              |                          | e dead time is acti<br>dead time is activ     |                              |                  |                      |                      |                     |

| bit 5-3      |                          | ited: Read as '0'                             | - ,                          |                  |                      |                      |                     |

| Note 1:      | Software must clo        | ar the interrupt sta                          | tue here and th              | e correspondir   | a IFSy hit in t      | he interrupt or      | ontroller           |

| 2:           |                          | Time Base mode (                              |                              |                  | -                    | -                    |                     |

| 3:           | -                        | be changed only v                             | when PTEN = 0                | . Changing the   | e clock selectio     | on during ope        | ration will         |

|              |                          | real Dariad Deast                             | modo confirm                 |                  |                      |                      |                     |

#### REGISTER 15-6: PWMCONx: PWMx CONTROL REGISTER

4: To operate in External Period Reset mode, configure FCLCONx<CLMOD> = 0 and PWMCONx<ITB> = 1.

#### REGISTER 15-11: DTRx: PWMx DEAD-TIME REGISTER

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| —               | _     |                  |       | DTR>             | <13:8>          |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | DTR   | 2x<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-14Unimplemented: Read as '0'bit 13-0DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 15-12: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| —               | _     |                  |       | ALTDTI           | Rx<13:8>        |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | ALTD  | TR <7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen     | nented bit, rea | ad as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

| REGISTER 1            | 8-1: UxMO               | DE: UARTx N                                       |                     | STER                 |                  |                   |               |

|-----------------------|-------------------------|---------------------------------------------------|---------------------|----------------------|------------------|-------------------|---------------|

| R/W-0                 | U-0                     | R/W-0                                             | R/W-0               | R/W-0                | U-0              | R/W-0             | R/W-0         |

| UARTEN <sup>(1)</sup> |                         | USIDL                                             | IREN <sup>(2)</sup> | RTSMD                | —                | UEN1              | UEN0          |

| bit 15                | ·                       |                                                   |                     |                      |                  |                   | bit           |

| R/W-0, HC             | R/W-0                   | R/W-0, HC                                         | R/W-0               | R/W-0                | R/W-0            | R/W-0             | R/W-0         |

| WAKE                  | LPBACK                  | ABAUD                                             | URXINV              | BRGH                 | PDSEL1           | PDSEL0            | STSEL         |

| bit 7                 | EI BROR                 | //B/(OD                                           | OTOXINV             | BROM                 | TDOLLI           | 1 DOLLO           | bit           |

|                       |                         |                                                   | 0                   | •.                   |                  |                   |               |

| Legend:               | 1.12                    | HC = Hardwa                                       |                     |                      |                  |                   |               |

| R = Readable          |                         | W = Writable                                      |                     | -                    | nented bit, read |                   |               |

| -n = Value at F       | POR                     | '1' = Bit is set                                  |                     | '0' = Bit is cle     | ared             | x = Bit is unkn   | own           |

| bit 15                | UARTEN: UA              | ARTx Enable bi                                    | <sub>t</sub> (1)    |                      |                  |                   |               |

|                       | 1 = UARTx is            | s enabled; all U                                  | ARTx pins are       | e controlled by      | UARTx as defi    | ned by UEN<1:     | 0>            |

|                       |                         |                                                   | UARTx pins a        | are controlled I     | by port latches  | , UARTx power     | consumptio    |

| bit 14                | is minima               | ai<br>i <b>ted:</b> Read as 'i                    | ר'                  |                      |                  |                   |               |

| bit 13                | -                       | Tx Stop in Idle I                                 |                     |                      |                  |                   |               |

| bit 13                |                         | ues module op                                     |                     | device enters        | Idle mode        |                   |               |

|                       |                         | s module operation                                |                     |                      |                  |                   |               |

| bit 12                | IREN: IrDA <sup>®</sup> | Encoder and D                                     | ecoder Enable       | e bit <sup>(2)</sup> |                  |                   |               |

|                       | 1 = IrDA enc            | oder and deco                                     | der are enable      | ed                   |                  |                   |               |

|                       | 0 = IrDA enc            | oder and deco                                     | der are disable     | ed                   |                  |                   |               |

| bit 11                |                         | le Selection for                                  |                     | it                   |                  |                   |               |

|                       |                         | in is in Simple»<br>in is in Flow Co              |                     |                      |                  |                   |               |

| bit 10                | Unimplemen              | ted: Read as '                                    | כ'                  |                      |                  |                   |               |

| bit 9-8               |                         | IARTx Enable b                                    |                     |                      |                  |                   |               |

|                       | 10 = UxTX, L            | JxRX, <u>UxCTS</u> a                              | ind UxRTS pir       | ns are enabled       | and used         | controlled by po  |               |

|                       |                         | nd UxRX pins a                                    |                     |                      |                  | /BCLK pins are    |               |

| bit 7                 | WAKE: Wake              | -up on Start bit                                  | Detect During       | g Sleep Mode         | Enable bit       |                   |               |

|                       |                         | vill continue to s<br>are on the follo            |                     |                      | pt is generated  | on falling edge,  | bit is cleare |

|                       |                         | -up is enabled                                    | wing naing eu       | ge                   |                  |                   |               |

| bit 6                 |                         | RTx Loopback                                      | Mode Select         | bit                  |                  |                   |               |

|                       |                         | Loopback mod                                      |                     |                      |                  |                   |               |

|                       |                         | k mode is disat                                   |                     |                      |                  |                   |               |

| bit 5                 | ABAUD: Auto             | o-Baud Enable                                     | bit                 |                      |                  |                   |               |

|                       | before ot               | aud rate meas<br>her data; cleare<br>e measuremen | ed in hardwar       | e upon comple        | tion             | eception of a Sy  | nc field (55  |

| Note 1: Rei           |                         |                                                   |                     |                      |                  | anual" for inform | ation on      |

|                       | abling the UART         |                                                   |                     |                      | ,                |                   |               |

| <b>2:</b> Thi         | s feature is only       | / available for t                                 | he 16x BRG n        | node (BRGH =         | = 0).            |                   |               |

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER

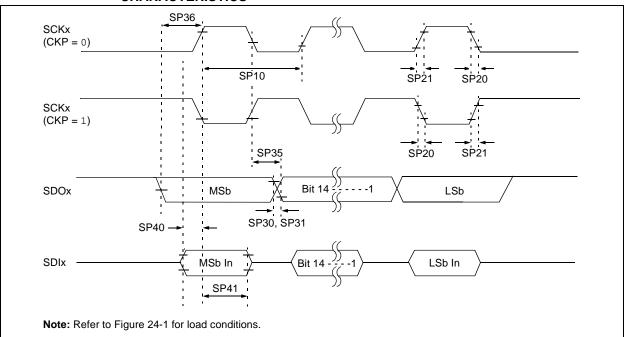

# FIGURE 24-13: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 24-32:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHA       | RACTERIST             | ICS                                           | (unless o | I Operatin<br>otherwise<br>g temperat | <b>stated)</b><br>ture -40 | °C ≤ Ta ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------|-----------------------|-----------------------------------------------|-----------|---------------------------------------|----------------------------|-----------|-----------------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min       | Тур <sup>(2)</sup>                    | Max                        | Units     | Conditions                                                      |

| SP10         | TscP                  | Maximum SCKx Frequency                        | —         | _                                     | 9                          | MHz       | See Note 3                                                      |

| SP20         | TscF                  | SCKx Output Fall Time                         | —         | -                                     | _                          | ns        | See Parameter DO32 and <b>Note 4</b>                            |

| SP21         | TscR                  | SCKx Output Rise Time                         | —         | —                                     | _                          | ns        | See Parameter DO31 and <b>Note 4</b>                            |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    | —         | —                                     | _                          | ns        | See Parameter DO32 and <b>Note 4</b>                            |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | —         | -                                     | _                          | ns        | See Parameter DO31 and <b>Note 4</b>                            |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | —         | 6                                     | 20                         | ns        |                                                                 |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30        | _                                     | _                          | ns        |                                                                 |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30        | —                                     | —                          | ns        |                                                                 |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30        | _                                     |                            | ns        |                                                                 |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

| AC CHA       | ARACTER | ISTICS           |                           | Standard Operatin<br>(unless otherwise<br>Operating tempera | e stated)<br>iture -40 | )°C ≤ TA ≤ | <b>DV to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |  |

|--------------|---------|------------------|---------------------------|-------------------------------------------------------------|------------------------|------------|------------------------------------------------------------------|--|

| Param<br>No. | Symbol  | Charact          | teristic                  | Min <sup>(1)</sup>                                          | Max                    | Units      | Conditions                                                       |  |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 1)                                             | _                      | μS         |                                                                  |  |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 1)                                             | _                      | μs         |                                                                  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                             | _                      | μs         |                                                                  |  |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 1)                                             | _                      | μs         |                                                                  |  |

|              |         |                  | 400 kHz mode              | Tcy/2 (BRG + 1)                                             | _                      | μs         |                                                                  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                             | —                      | μS         |                                                                  |  |

| IM20         | TF:SCL  | SDAx and SCLx    | 100 kHz mode              | _                                                           | 300                    | ns         | CB is specified to be                                            |  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                    | ns         | from 10 pF to 400 pF                                             |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                           | 100                    | ns         |                                                                  |  |

| IM21         | TR:SCL  | SDAx and SCLx    | 100 kHz mode              | _                                                           | 1000                   | ns         | CB is specified to be                                            |  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                    | ns         | from 10 pF to 400 pF                                             |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                           | 300                    | ns         |                                                                  |  |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                         | —                      | ns         |                                                                  |  |

|              |         | Setup Time       | 400 kHz mode              | 100                                                         | —                      | ns         |                                                                  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 40                                                          | —                      | ns         |                                                                  |  |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                                                           | —                      | μS         |                                                                  |  |

|              |         | Hold Time        | 400 kHz mode              | 0                                                           | 0.9                    | μS         |                                                                  |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                         | —                      | μS         |                                                                  |  |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 1)                                             | —                      | μS         | Only relevant for                                                |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 1)                                             | —                      | μS         | Repeated Start                                                   |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                             | —                      | μS         | condition                                                        |  |

| IM31         | THD:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 1)                                             | —                      | μS         | After this period the                                            |  |