Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 16KB (16K × 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs404t-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1:                     | PINOUT I/O DESCRIPTIONS |                        |                          |                                                                                                                                                                                                       |  |  |

|--------------------------------|-------------------------|------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                       | Pin<br>Type             | Buffer<br>Type         | PPS<br>Capable           | Description                                                                                                                                                                                           |  |  |

| AN0-AN11                       | I                       | Analog                 | No                       | Analog input channels                                                                                                                                                                                 |  |  |

| CLKI                           | I                       | ST/CMOS                | No                       | External clock source input. Always associated with OSC1 pin                                                                                                                                          |  |  |

| CLKO                           | ο                       | _                      | No                       | function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC<br>modes. Always associated with OSC2 pin function. |  |  |

| OSC1                           | I                       | ST/CMOS                | No                       | Oscillator crystal input. ST buffer when configured in RC mode;                                                                                                                                       |  |  |

| OSC2                           | I/O                     | _                      | No                       | CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC<br>modes.                                     |  |  |

| CN0-CN29                       | I                       | ST                     | No                       | Change Notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                      |  |  |

| IC1-IC2                        | ļ                       | ST                     | Yes                      | Capture Inputs 1/2.                                                                                                                                                                                   |  |  |

| OCFA<br>OC1-OC2                | I<br>O                  | ST<br>—                | Yes<br>Yes               | Compare Fault A input (for Compare Channels 1 and 2)<br>Compare Outputs 1 through 2.                                                                                                                  |  |  |

| INT0<br>INT1<br>INT2           |                         | ST<br>ST<br>ST         | No<br>Yes<br>Yes         | External Interrupt 0.<br>External Interrupt 1.<br>External Interrupt 2.                                                                                                                               |  |  |

| RA0-RA4                        | I/O                     | ST                     | No                       | PORTA is a bidirectional I/O port.                                                                                                                                                                    |  |  |

| RB0-RB15                       | I/O                     | ST                     | No                       | PORTB is a bidirectional I/O port.                                                                                                                                                                    |  |  |

| RC0-RC13                       | I/O                     | ST                     | No                       | PORTC is a bidirectional I/O port.                                                                                                                                                                    |  |  |

| RP0-RP29                       | I/O                     | ST                     | No                       | Remappable I/O pins.                                                                                                                                                                                  |  |  |

| T1CK<br>T2CK<br>T3CK           |                         | ST<br>ST<br>ST         | Yes<br>Yes<br>Yes        | Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.                                                                                                          |  |  |

| U1CTS<br>U1RTS<br>U1RX<br>U1TX | <br>  0<br>  0          | ST<br>—<br>ST<br>—     | Yes<br>Yes<br>Yes<br>Yes | UART1 Clear-To-Send.<br>UART1 Ready-To-Send.<br>UART1 receive.<br>UART1 transmit.                                                                                                                     |  |  |

| SCK1<br>SDI1                   | I/O<br>I                | ST<br>ST               | Yes<br>Yes               | Synchronous serial clock input/output for SPI1.<br>SPI1 data in.                                                                                                                                      |  |  |

| <u>SDO1</u><br>SS1             | 0<br>I/O                | ST<br>ST               | Yes<br>Yes               | SPI1 data out.<br>SPI1 slave synchronization or frame pulse I/O.                                                                                                                                      |  |  |

| SCL1<br>SDA1                   | I/O<br>I/O              | ST<br>ST               | No<br>No                 | Synchronous serial clock input/output for I2C1.<br>Synchronous serial data input/output for I2C1.                                                                                                     |  |  |

| TMS<br>TCK<br>TDI<br>TDO       | <br> <br> <br> <br>0    | TTL<br>TTL<br>TTL<br>— | No<br>No<br>No<br>No     | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.                                                                                   |  |  |

| Legend: CMO                    | S = CMOS                | compatible             | input or o               | Analog = Analog input I = Input                                                                                                                                                                       |  |  |

####

s compatible input or output yena: ST = Schmitt Trigger input with CMOS levels P = Power TTL = Transistor-Transistor Logic

Analog = Analog input PPS = Peripheral Pin Select

O = Output

### 4.2 Data Address Space

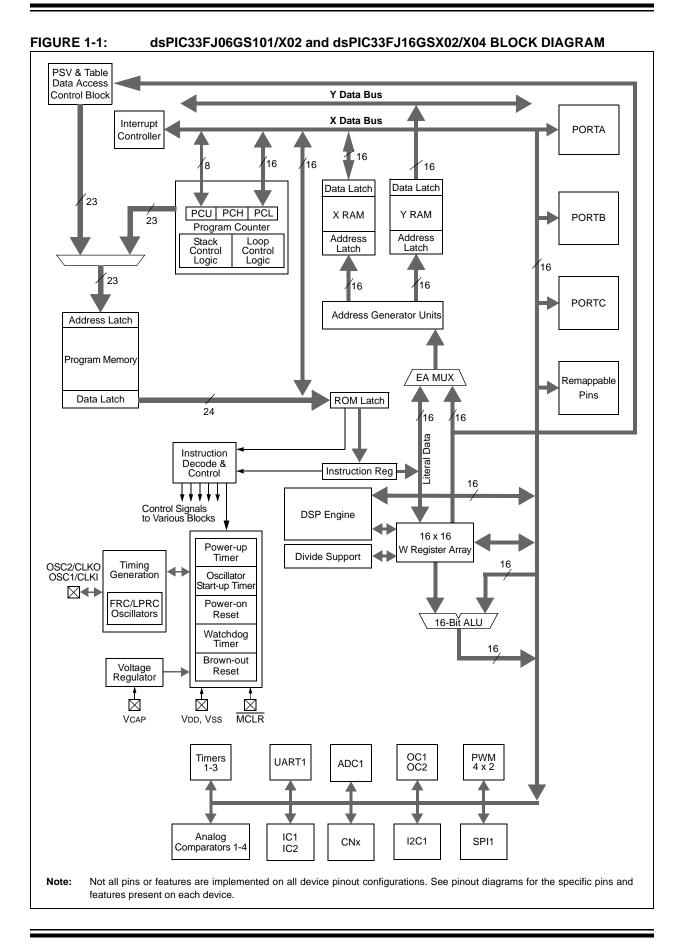

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 CPU has a separate, 16-bit-wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices implement up to 2 Kbytes of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] that results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

| Note: | The actual set of peripheral features and interrupts varies by the device. Refer to |  |  |  |  |  |

|-------|-------------------------------------------------------------------------------------|--|--|--|--|--|

|       | the corresponding device tables and                                                 |  |  |  |  |  |

|       | pinout diagrams for device-specific                                                 |  |  |  |  |  |

|       | information.                                                                        |  |  |  |  |  |

#### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field or by using Indirect Addressing mode using a Working register as an Address Pointer.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-0            | R/W-0                                                                                                                                                                                                                | U-0                                                                                                                                                                                                     | U-0                                     | U-0              | U-0             | R/W-0           | R/W-0  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|-----------------|-----------------|--------|--|--|

| ADCP1IF          | ADCP0IF                                                                                                                                                                                                              | _                                                                                                                                                                                                       | _                                       | _                | _               | AC4IF           | AC3IF  |  |  |

| bit 15           |                                                                                                                                                                                                                      |                                                                                                                                                                                                         |                                         |                  |                 |                 | bit    |  |  |

| R/W-0            | U-0                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                     | U-0                                     | U-0              | U-0             | R/W-0           | R/W-0  |  |  |

| AC2IF            | _                                                                                                                                                                                                                    | _                                                                                                                                                                                                       | _                                       | _                | _               | PWM4IF          | PWM3IF |  |  |

| bit 7            |                                                                                                                                                                                                                      |                                                                                                                                                                                                         |                                         |                  |                 |                 | bit    |  |  |

| Legend:          |                                                                                                                                                                                                                      |                                                                                                                                                                                                         |                                         |                  |                 |                 |        |  |  |

| R = Readable     | bit                                                                                                                                                                                                                  | W = Writable                                                                                                                                                                                            | bit                                     | U = Unimplen     | nented bit, rea | ıd as '0'       |        |  |  |

| -n = Value at F  | POR                                                                                                                                                                                                                  | '1' = Bit is set                                                                                                                                                                                        |                                         | '0' = Bit is cle | ared            | x = Bit is unkn | nown   |  |  |

| bit 15<br>bit 14 | 1 = Interrupt r<br>0 = Interrupt r<br>ADCP0IF: AD<br>1 = Interrupt r                                                                                                                                                 | equest has oc<br>equest has no                                                                                                                                                                          | t occurred<br>rersion Done Ir<br>curred |                  |                 |                 |        |  |  |

| bit 13-10        | •                                                                                                                                                                                                                    | ted: Read as '                                                                                                                                                                                          |                                         |                  |                 |                 |        |  |  |

| bit 9            | 1 = Interrupt r                                                                                                                                                                                                      | g Comparator<br>equest has oc<br>equest has no                                                                                                                                                          |                                         | g Status bit     |                 |                 |        |  |  |

| bit 8            | AC3IF: Analo                                                                                                                                                                                                         | g Comparator<br>equest has oc                                                                                                                                                                           | 3 Interrupt Fla<br>curred               | g Status bit     |                 |                 |        |  |  |

| bit 7            | <ul> <li>0 = Interrupt request has not occurred</li> <li>AC2IF: Analog Comparator 2 Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                                                                                                                                                                                         |                                         |                  |                 |                 |        |  |  |

| bit 6-2          | •                                                                                                                                                                                                                    | ted: Read as '                                                                                                                                                                                          |                                         |                  |                 |                 |        |  |  |

| bit 1            | <b>PWM4IF:</b> PWM4 Interrupt Flag Status bit<br>1 = Interrupt request has occurred                                                                                                                                  |                                                                                                                                                                                                         |                                         |                  |                 |                 |        |  |  |

| bit 0            | 1 = Interrupt r                                                                                                                                                                                                      | <ul> <li>a Interrupt request has occurred</li> <li><b>PWM3IF:</b> PWM3 Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                         |                  |                 |                 |        |  |  |

#### REGISTER 7-10: IFS6: INTERRUPT FLAG STATUS REGISTER 6

### **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,2)</sup> (CONTINUED)

- bit 3 **CF:** Clock Fail Detect bit (read/clear by application)

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.

- 2: This register is reset only on a Power-on Reset (POR).

- 3: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

#### 10.2 Open-Drain Configuration

In addition to the PORTx, LATx and TRISx registers for data control, some digital-only port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (for example, 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to **"Pin Diagrams"** for the available pins and their functionality.

#### 10.3 Configuring Analog Port Pins

The ADPCFG and TRISx registers control the operation of the Analog-to-Digital (A/D) port pins. The port pins that are to function as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The ADPCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORTx register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 10.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP. An example is shown in Example 10-1.

#### 10.5 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 30 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a Change-of-State.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when the push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on Change Notification pins should always be disabled when the port pin is configured as a digital output.

#### EQUATION 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| BTSS | PORTB, #13 | ; | Next Instruction                |

|      |            |   |                                 |

| U-0                | U-0                                                                                                                                                          | R/W-1                                                                                                                                                                                                                  | R/W-1                                              | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|------------------|-----------------|--------|

| _                  |                                                                                                                                                              | T3CKR5                                                                                                                                                                                                                 | T3CKR4                                             | T3CKR3            | T3CKR2           | T3CKR1          | T3CKR0 |

| bit 15             |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 | bit    |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |

| U-0                | U-0                                                                                                                                                          | R/W-1                                                                                                                                                                                                                  | R/W-1                                              | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|                    |                                                                                                                                                              | T2CKR5                                                                                                                                                                                                                 | T2CKR4                                             | T2CKR3            | T2CKR2           | T2CKR1          | T2CKR0 |

| bit 7              |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 | bit    |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |

| Legend:            | la h:t                                                                                                                                                       |                                                                                                                                                                                                                        | L:4                                                |                   | antad hit waar   | L == (0)        |        |

| R = Readab         |                                                                                                                                                              | W = Writable                                                                                                                                                                                                           |                                                    | •                 | nented bit, read |                 |        |

| -n = Value a       | t POR                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                                                       |                                                    | '0' = Bit is clea | ared             | x = Bit is unkr | IOWN   |

| bit 15-14          | Unimploment                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                         | o'                                                 |                   |                  |                 |        |

|                    | -                                                                                                                                                            |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |

| bit 13-8           |                                                                                                                                                              | -                                                                                                                                                                                                                      | 3 External Clo                                     | ck (T3CK) to th   | ne Correspondi   | ng RPn Pin bits | 6      |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |

|                    | 111111 = Inp                                                                                                                                                 |                                                                                                                                                                                                                        | _                                                  |                   |                  |                 |        |

|                    | 100011 <b>= Inp</b>                                                                                                                                          | ut tied to RP35                                                                                                                                                                                                        |                                                    |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp                                                                                                                                 | out tied to RP35<br>out tied to RP34                                                                                                                                                                                   | 1                                                  |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                               | 1<br>3                                             |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34                                                                                                                                                                                   | 1<br>3                                             |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                               | 1<br>3                                             |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                               | 1<br>3                                             |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                 | ut tied to RP34<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                                               | 1<br>3                                             |                   |                  |                 |        |

| hit 7-6            | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                 | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32                                                                                                                             | 4<br>3<br>2                                        |                   |                  |                 |        |

| bit 7-6            | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>00000 = Inpu<br>Unimplemen                                                               | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '                                                                                                     | 4<br>3<br>2<br>0'                                  | ole (T2CK) to th  | oo Corroopondi   | ng PDn Din hit  |        |

| bit 7-6<br>bit 5-0 | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | ut tied to RP35<br>out tied to RP33<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer?                                                                               | 4<br>3<br>2<br>0'                                  | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP32<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer:<br>out tied to Vss                                                             | 1<br>3<br>2<br>0'<br>2 External Clo                | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 5      |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP32<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer<br>out tied to Vss<br>out tied to RP35                                          | 1<br>3<br>2<br>0'<br>2 External Clo                | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP34<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>out tied to RP35<br>out tied to RP34                                                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1      | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>out tied to RP34<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>out tied to RP35<br>out tied to RP34                                                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ie Correspondi   | ng RPn Pin bits | 5      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33                 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>tut tied to RP32<br>tut tied to RP33<br>tut tied to RP33<br>tut tied to RP34<br>t tied to RP0<br><b>ted:</b> Read as '<br>t tied to RP35<br>tut tied to RP34<br>tut tied to RP32<br>tut tied to RP32 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

# 12.0 TIMER2/3 FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

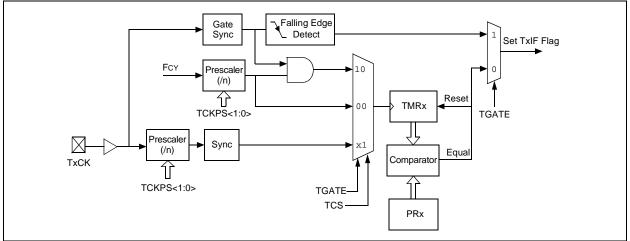

Timer2 is a Type B timer that offers the following major features:

- A Type B timer can be concatenated with a Type C timer to form a 32-bit timer

- External clock input (TxCK) is always synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

Figure 12-1 shows a block diagram of the Type B timer.

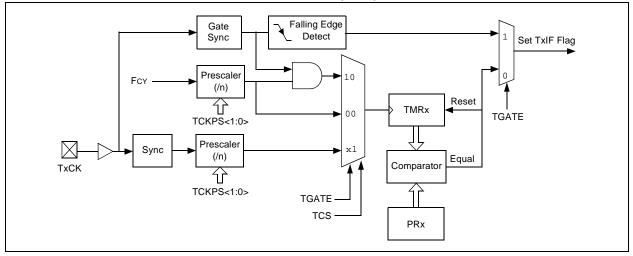

Timer3 is a Type C timer that offers the following major features:

- A Type C timer can be concatenated with a Type B timer to form a 32-bit timer

- The external clock input (TxCK) is always synchronized to the internal device clock and the clock synchronization is performed before the prescaler

A block diagram of the Type C timer is shown in Figure 12-2.

**Note:** Timer3 is not available on all devices.

### FIGURE 12-1: TYPE B TIMER BLOCK DIAGRAM (x = 2)

#### FIGURE 12-2: TYPE C TIMER BLOCK DIAGRAM (x = 3)

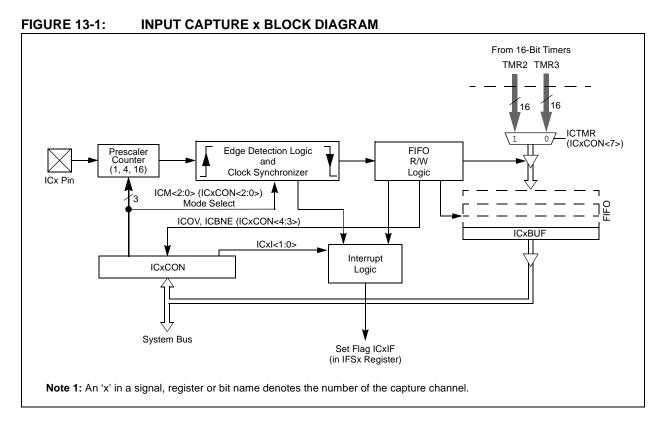

### 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70198) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices support up to two input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select one of the two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Use of input capture to provide additional sources of external interrupts

© 2008-2014 Microchip Technology Inc.

| U-0                                | U-0   | U-0              | U-0         | U-0             | U-0      | R/W-0 | R/W-0 |

|------------------------------------|-------|------------------|-------------|-----------------|----------|-------|-------|

| _                                  |       | —                | _           | _               |          | AMSk  | <9:8> |

| bit 15                             | ·     |                  |             |                 | -        |       | bit 8 |

|                                    |       |                  |             |                 |          |       |       |

| R/W-0                              | R/W-0 | R/W-0            | R/W-0       | R/W-0           | R/W-0    | R/W-0 | R/W-0 |

|                                    |       |                  | AMS         | K<7:0>          |          |       |       |

| bit 7                              |       |                  |             |                 |          |       | bit 0 |

|                                    |       |                  |             |                 |          |       |       |

| Legend:                            |       |                  |             |                 |          |       |       |

| R = Readable bit W = Writable bit  |       | bit              | U = Unimple | mented bit, rea | d as '0' |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cle | eared       | x = Bit is unkr | nown     |       |       |

#### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Mask for Address bit x Select bits

1 = Enables masking for bit x of incoming message address; bit match is not required in this position

0 = Disables masking for bit x; bit match is required in this position

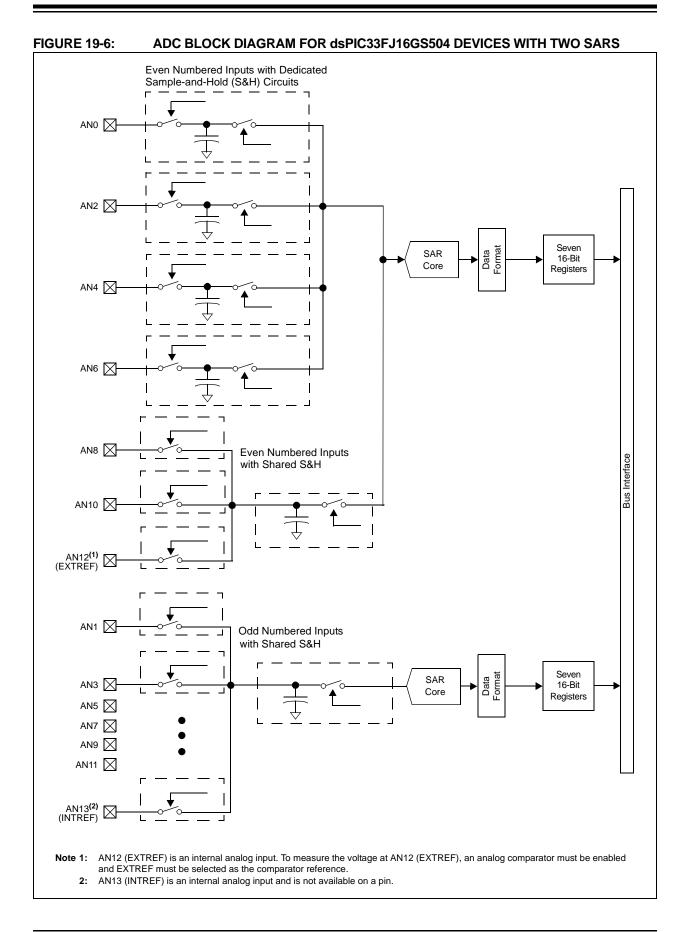

## 19.0 HIGH-SPEED 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed 10-Bit Analog-to-Digital Converter (ADC)" (DS70000321) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices provide high-speed, successive approximation Analog-to-Digital conversions to support applications, such as AC/DC and DC/DC power converters.

### **19.1 Features Overview**

The ADC module comprises the following features:

- 10-bit resolution

- Unipolar inputs

- Up to two Successive Approximation Registers (SARs)

- Up to 12 external input channels

- Up to two internal analog inputs

- · Dedicated result register for each analog input

- ±1 LSB accuracy at 3.3V

- Single supply operation

- 4 Msps conversion rate at 3.3V (devices with two SARs)

- 2 Msps conversion rate at 3.3V (devices with one SAR)

- Low-power CMOS technology

### 19.2 Module Description

This ADC module is designed for applications that require low latency between the request for conversion and the resultant output data. Typical applications include:

- AC/DC power supplies

- DC/DC Converters

- Power Factor Correction (PFC)

This ADC works with the high-speed PWM module in power control applications that require high-frequency control loops. This module can sample and convert two analog inputs in a 0.5 microsecond when two SARs are used. This small conversion delay reduces the "phase lag" between measurement and control system response.

Up to five inputs may be sampled at a time (four inputs from the dedicated Sample-and-Hold circuits and one from the shared Sample-and-Hold circuit). If multiple inputs request conversion, the ADC will convert them in a sequential manner, starting with the lowest order input.

This ADC design provides each pair of analog inputs (AN1, AN0), (AN3, AN2),..., the ability to specify its own trigger source out of a maximum of sixteen different trigger sources. This capability allows this ADC to sample and convert analog inputs that are associated with PWM generators operating on Independent Time Bases (ITBs).

The user application typically requires synchronization between analog data sampling and PWM output to the application circuit. The very high-speed operation of this ADC module allows "data on demand".

In addition, several hardware features have been added to the peripheral interface to improve real-time performance in a typical DSP-based application.

- · Result alignment options

- Automated sampling

- External conversion start control

- Two internal inputs to monitor the INTREF internal reference and the EXTREF input signal

### 19.3 Module Functionality

The high-speed, 10-bit ADC module is designed to support power conversion applications when used with the high-speed PWM module. The ADC may have one or two SAR modules, depending on the device variant. If two SARs are present on a device, two conversions can be processed at a time, yielding 4 Msps conversion rate. If only one SAR is present on a device, only one conversion can be processed at a time, yielding 2 Msps conversion rate. The high-speed 10-bit ADC produces two 10-bit conversion results in a 0.5 microsecond.

The ADC module supports up to 12 external analog inputs and two internal analog inputs. To monitor reference voltage, two internal inputs, AN12 and AN13, are connected to the EXTREF and INTREF voltages, respectively.

The analog reference voltage is defined as the device supply voltage (AVDD/AVSS).

Block diagrams of the ADC module are shown in Figure 19-1 through Figure 19-6.

| U-0             | U-0                                                                                                                                                                                                                                               | U-0                              | U-0         | U-0              | U-0              | U-0               | U-0          |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------|------------------|------------------|-------------------|--------------|

| —               | —                                                                                                                                                                                                                                                 | —                                | —           | —                | _                |                   |              |

| bit 15          |                                                                                                                                                                                                                                                   |                                  |             |                  |                  |                   | bit 8        |

| DANIO           | DAMO                                                                                                                                                                                                                                              | DANO                             | DAMO        | DAMO             | DAMO             | DAMO              | DAMO         |

| R/W-0           | R/W-0                                                                                                                                                                                                                                             | R/W-0                            | R/W-0       | R/W-0            | R/W-0            | R/W-0             | R/W-0        |

| IRQEN6          | PEND6                                                                                                                                                                                                                                             | SWTRG6                           |             |                  | TRGSRC6<4:0      | >                 |              |

| bit 7           |                                                                                                                                                                                                                                                   |                                  |             |                  |                  |                   | bit C        |

| Legend:         |                                                                                                                                                                                                                                                   |                                  |             |                  |                  |                   |              |

| R = Readable    | bit                                                                                                                                                                                                                                               | W = Writable I                   | oit         | U = Unimpler     | mented bit, read | as '0'            |              |

| -n = Value at F | POR                                                                                                                                                                                                                                               | '1' = Bit is set                 |             | '0' = Bit is cle |                  | x = Bit is unkn   | iown         |

|                 |                                                                                                                                                                                                                                                   |                                  | . 1         |                  |                  |                   |              |

| bit 15-8        | •                                                                                                                                                                                                                                                 | ted: Read as '                   |             |                  |                  |                   |              |

| bit 7           |                                                                                                                                                                                                                                                   | rrupt Request E                  |             |                  |                  |                   |              |

|                 | 1 = Enables I<br>0 = IRQ is no                                                                                                                                                                                                                    |                                  | when reques | ted conversion   | of Channels AN   | N13 and AN12      | is completed |

| h               |                                                                                                                                                                                                                                                   | 0                                |             |                  |                  |                   |              |

| bit 6           |                                                                                                                                                                                                                                                   | ding Conversior                  |             |                  |                  |                   |              |

|                 |                                                                                                                                                                                                                                                   | on of Channels<br>on is complete | AN13 and Ar | N 12 is pending  | ; set when seled | cted trigger is a | isserted     |

| bit 5           | SWTRG6: So                                                                                                                                                                                                                                        | oftware Trigger                  | 6 bit       |                  |                  |                   |              |

|                 | <ul> <li>1 = Starts conversion of AN13 (INTREF) and AN12 (EXTREF) (if selected by the TRGSRCx bits)<sup>(2)</sup><br/>This bit is automatically cleared by hardware when the PEND6 bit is set.</li> <li>0 = Conversion has not started</li> </ul> |                                  |             |                  |                  |                   |              |

| Note 1: This    |                                                                                                                                                                                                                                                   |                                  |             | 33FJ16GS502      | and dsPIC33F     | J16GS504 devi     | ces.         |

### REGISTER 19-8: ADCPC3: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup>

2: The trigger source must be set as global software trigger prior to setting this bit to '1'. If other conversions are in progress, conversion will be performed when the conversion resources are available.

#### 20.3 Module Applications

This module provides a means for the SMPS dsPIC<sup>®</sup> DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator and an associated 10-bit DAC that provides a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- Generate an Interrupt

- Trigger an ADC Sample and Convert Process

- Truncate the PWM Signal (current limit)

- Truncate the PWM Period (current minimum)

- Disable the PWM Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWM output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

### 20.4 DAC

The range of the DAC is controlled through an analog multiplexer that selects either AVDD/2, an internal reference source, INTREF, or an external reference source, EXTREF. The full range of the DAC (AVDD/2) will typically be used when the chosen input source pin is shared with the ADC. The reduced range option (INTREF) will likely be used when monitoring current levels using a current sense resistor. Usually, the measured voltages in such applications are small (<1.25V); therefore the option of using a reduced reference range for the comparator extends the available DAC resolution in these applications. The use of an external reference enables the user to connect to a reference that better suits their application.

DACOUT, shown in Figure 20-1, can only be associated with a single comparator at a given time.

Note: It should be ensured in software that multiple DACOE bits are not set. The output on the DACOUT pin will be indeterminate if multiple comparators enable the DAC output.

#### 20.5 Interaction with I/O Buffers

If the comparator module is enabled and a pin has been selected as the source for the comparator, then the chosen I/O pad must disable the digital input buffer associated with the pad to prevent excessive currents in the digital buffer due to analog input voltages.

#### 20.6 Digital Logic

The CMPCONx register (see Register 20-1) provides the control logic that configures the comparator module. The digital logic provides a glitch filter for the comparator output to mask transient signals in less than two instruction cycles. In Sleep or Idle mode, the glitch filter is bypassed to enable an asynchronous path from the comparator to the interrupt controller. This asynchronous path can be used to wake-up the processor from Sleep or Idle mode.

The comparator can be disabled while in Idle mode if the CMPSIDL bit is set. If a device has multiple comparators, if any CMPSIDL bit is set, then the entire group of comparators will be disabled while in Idle mode. This behavior reduces complexity in the design of the clock control logic for this module.

The digital logic also provides a one TCY width pulse generator for triggering the ADC and generating interrupt requests.

The CMPDACx (see Register 20-2) register provides the digital input value to the reference DAC.

If the module is disabled, the DAC and comparator are disabled to reduce power consumption.

#### 20.7 Comparator Input Range

The comparator has a limitation for the input Common-Mode Range (CMR) of (AVDD - 1.5V), typical. This means that both inputs should not exceed this range. As long as one of the inputs is within the Common-Mode Range, the comparator output will be correct. However, any input exceeding the CMR limitation will cause the comparator input to be saturated.

If both inputs exceed the CMR, the comparator output will be indeterminate.

#### 20.8 DAC Output Range

The DAC has a limitation for the maximum reference voltage input of (AVDD - 1.6) volts. An external reference voltage input should not exceed this value or the reference DAC output will become indeterminate.

#### 20.9 Comparator Registers

The comparator module is controlled by the following registers:

- CMPCONx: Comparator Control x Register

- CMPDACx: Comparator DAC x Control Register

| DC CHARA         | CTERISTIC              | S                | (unless ot | Operating Co<br>herwise state<br>temperature | $-40^{\circ}C \le TA \le +3$ | to 3.6V<br>85°C for Industrial<br>125°C for Extended |  |  |

|------------------|------------------------|------------------|------------|----------------------------------------------|------------------------------|------------------------------------------------------|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Мах              | Units      |                                              | Conditions                   |                                                      |  |  |

| Operating C      | Current (IDD)          | ) <sup>(2)</sup> |            |                                              |                              |                                                      |  |  |

| DC20d            | 55                     | 70               | mA         | -40°C                                        |                              |                                                      |  |  |

| DC20a            | 55                     | 70               | mA         | +25°C                                        | 3.3V                         | 10 MIPS                                              |  |  |

| DC20b            | 55                     | 70               | mA         | +85°C                                        | 3.3V                         | See Note 2                                           |  |  |

| DC20c            | 55                     | 70               | mA         | +125°C                                       |                              |                                                      |  |  |

| DC21d            | 68                     | 85               | mA         | -40°C                                        |                              |                                                      |  |  |

| DC21a            | 68                     | 85               | mA         | +25°C                                        | 3.3V                         | 16 MIPS                                              |  |  |

| DC21b            | 68                     | 85               | mA         | +85°C                                        | 3.3V                         | See Note 2 and Note 3                                |  |  |

| DC21c            | 68                     | 85               | mA         | +125°C                                       |                              |                                                      |  |  |

| DC22d            | 78                     | 95               | mA         | -40°C                                        |                              |                                                      |  |  |

| DC22a            | 78                     | 95               | mA         | +25°C                                        | 3.3V                         | 20 MIPS                                              |  |  |

| DC22b            | 78                     | 95               | mA         | +85°C                                        | 3.3V                         | See Note 2 and Note 3                                |  |  |

| DC22c            | 78                     | 95               | mA         | +125°C                                       |                              |                                                      |  |  |

| DC23d            | 88                     | 110              | mA         | -40°C                                        |                              |                                                      |  |  |

| DC23a            | 88                     | 110              | mA         | +25°C                                        | 3.3V                         | 30 MIPS                                              |  |  |

| DC23b            | 88                     | 110              | mA         | +85°C                                        | 3.3V                         | See Note 2 and Note 3                                |  |  |

| DC23c            | 88                     | 110              | mA         | +125°C                                       |                              |                                                      |  |  |

| DC24d            | 98                     | 120              | mA         | -40°C                                        |                              |                                                      |  |  |

| DC24a            | 98                     | 120              | mA         | +25°C                                        | 3.3V                         | 40 MIPS                                              |  |  |

| DC24b            | 98                     | 120              | mA         | +85°C                                        | 5.5 v                        | See Note 2                                           |  |  |

| DC24c            | 98                     | 120              | mA         | +125°C                                       |                              |                                                      |  |  |

| DC25d            | 128                    | 160              | mA         | -40°C                                        |                              | 40 MIPS                                              |  |  |

| DC25a            | 125                    | 150              | mA         | +25°C                                        | 3.3V                         | See Note 2, except PWM is                            |  |  |

| DC25b            | 121                    | 150              | mA         | +85°C                                        | 5.5V                         | operating at maximum speed                           |  |  |

| DC25c            | 119                    | 150              | mA         | +125°C                                       |                              | (PTCON2 = 0x0000)                                    |  |  |

| DC26d            | 115                    | 140              | mA         | -40°C                                        |                              | 40 MIPS                                              |  |  |

| DC26a            | 112                    | 140              | mA         | +25°C                                        | 3.3V                         | See Note 2, except PWM is                            |  |  |

| DC26b            | 110                    | 140              | mA         | +85°C                                        | 5.5V                         | operating at 1/2 speed                               |  |  |