Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-9-                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Details                    |                                                                                  |

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs404t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

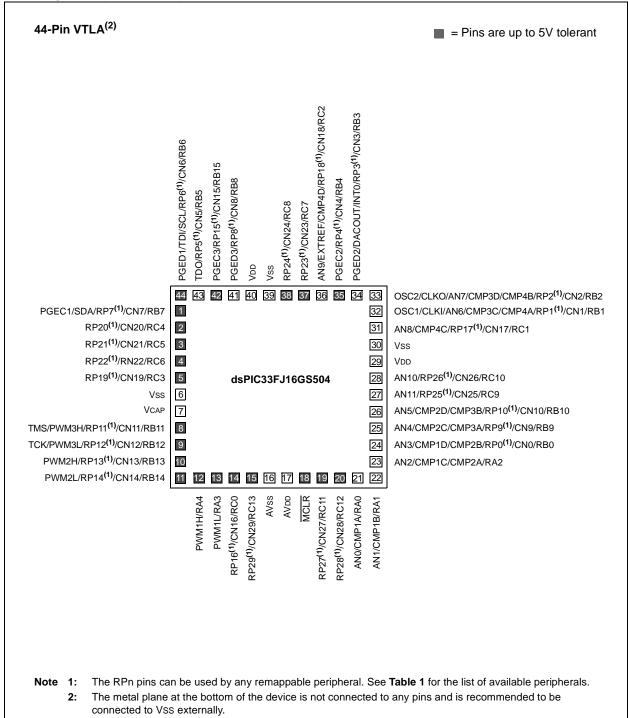

## Pin Diagrams (Continued)

#### 2.5 ICSP™ Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (ViH) and input low (ViL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB® ICD 3 or MPLAB® REAL ICE™.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB® ICD 3" (poster) DS51765

- "MPLAB® ICD 3 Design Advisory" DS51764

- "MPLAB® REAL ICE™ In-Circuit Debugger User's Guide" DS51616

- "Using MPLAB® REAL ICE™" (poster) DS51749

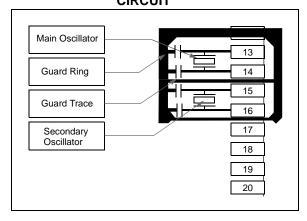

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < FIN < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV, and PLLFBD to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (for example, ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- · Signed or Unsigned DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- Automatic Saturation On/Off for ACCA (SATA)

- · Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

TABLE 3-1: DSP INSTRUCTIONS SUMMARY

| Instruction | Algebraic<br>Operation | ACC<br>Write Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

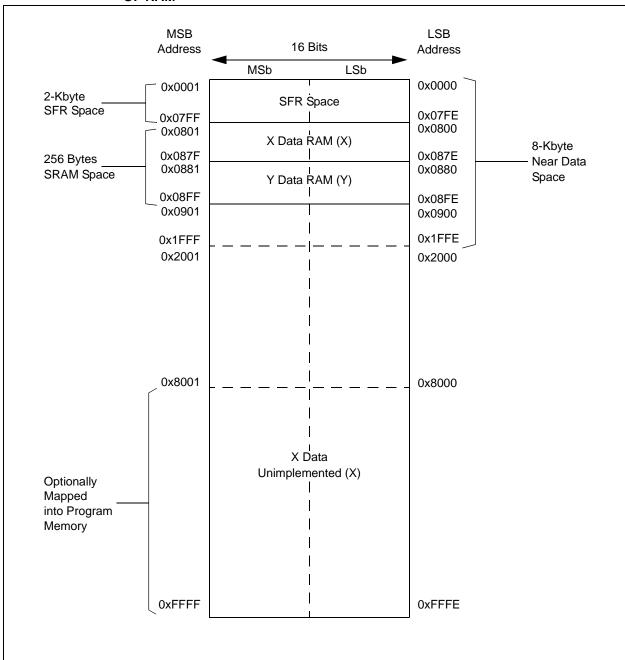

FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJ06GS101/102 DEVICES WITH 256 BYTES OF RAM

| Û           | ٦ |

|-------------|---|

| _           | Į |

| $\subseteq$ | 2 |

| 9           |   |

| 70003       |   |

| >           |   |

| ~           | š |

| _           |   |

| വ           | ٥ |

| 2           | ٥ |

| Ģ           |   |

| 96-5        |   |

| og-ba       | 5 |

| ob-page     | 5 |

|             |   |

| o agad-age  |   |

| oc-page os  |   |

|             |   |

| TΔRI F 4-14· | INPUT CAPTURE REGISTER MAP FOR | dsPIC33FJ16GSX02 AND dsPIC33FJ16GSX04            |

|--------------|--------------------------------|--------------------------------------------------|

| IADLL 4-14.  | INFUT CAFTURE REGISTER WAFT OR | . USF 10331 3 10037AUZ MIND USF 10331 3 10037AU4 |

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| IC1BUF       | 0140        |        | Input Capture 1 Register |        |        |        |        |       |       |       |       |       |       |       |       |       | xxxx  |               |

| IC1CON       | 0142        | _      | _                        | ICSIDL | -      | 1      | _      | _     | _     | ICTMR | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC2BUF       | 0144        |        | Input Capture 2 Register |        |        |        |        |       |       |       |       |       |       |       | xxxx  |       |       |               |

| IC2CON       | 0146        | _      | _                        | ICSIDL | -      |        | _      | _     | -     | ICTMR | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-15: OUTPUT COMPARE REGISTER MAP FOR dsPIC33FJ06GS101 AND dsPIC33FJ06GSX02

| File<br>Name | SFR<br>Addr | Bit 15                              | Bit 14                    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|-------------------------------------|---------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|-------|-------|---------------|

| OC1RS        | 0180        | Output Compare 1 Secondary Register |                           |        |        |        |        |       |       |       |       |       |       |        |       | xxxx  |       |               |

| OC1R         | 0182        |                                     | Output Compare 1 Register |        |        |        |        |       |       |       |       |       |       |        | xxxx  |       |       |               |

| OC1CON       | 0184        | _                                   | _                         | OCSIDL | _      | _      | _      | _     | _     | _     | _     | _     | OCFLT | OCTSEL | OCM2  | OCM1  | ОСМ0  | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### TABLE 4-16: OUTPUT COMPARE REGISTER MAP FOR dsPIC33FJ16GSX02 AND dsPIC33FJ06GSX04

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8      | Bit 7      | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|---------------------------|--------|--------|--------|--------|-----------|------------|------------|--------|-------|-------|--------|-------|-------|-------|---------------|

| OC1RS        | 0180        |        |                           |        |        |        |        | Output Co | mpare 1 Se | condary Re | gister |       |       |        |       |       |       | xxxx          |

| OC1R         | 0182        |        | Output Compare 1 Register |        |        |        |        |           |            |            |        |       |       |        |       |       | xxxx  |               |

| OC1CON       | 0184        |        |                           | OCSIDL |        | -      | _      | _         | _          |            | _      |       | OCFLT | OCTSEL | OCM2  | OCM1  | ОСМ0  | 0000          |

| OC2RS        | 0186        |        |                           |        |        |        |        | Output Co | mpare 2 Se | condary Re | gister |       |       |        |       |       |       | xxxx          |

| OC2R         | 0188        |        | Output Compare 2 Register |        |        |        |        |           |            |            |        |       |       |        |       |       | xxxxx |               |

| OC2CON       | 018A        | _      | _                         | OCSIDL | _      | _      | _      | _         | _          | _          | _      | _     | OCFLT | OCTSEL | OCM2  | OCM1  | ОСМ0  | 0000          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-17: HIGH-SPEED PWM REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7    | Bit 6 | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------|---------------|--------|--------|--------|--------|---------|---------|----------|-------|----------|----------|---------|----------|----------|----------|---------------|

| PTCON        | 0400        | PTEN   | _             | PTSIDL | SESTAT | SEIEN  | EIPU   | SYNCPOL | SYNCOEN | SYNCEN   | I     | SYNCSRC1 | SYNCSRC0 | SEVTPS3 | SEVTPS2  | SEVTPS1  | SEVTPS0  | 0000          |

| PTCON2       | 0402        | _      | _             | _      | _      | _      | _      | _       | _       | _        | _     | _        | _        | _       | PCLKDIV2 | PCLKDIV1 | PCLKDIV0 | 0000          |

| PTPER        | 0404        |        |               |        |        |        |        |         |         | PTPER<15 | :0>   |          |          |         |          |          |          | FFF8          |

| SEVTCMP      | 0406        |        | SEVTCMP<15:3> |        |        |        |        |         |         |          |       |          | _        | 0000    |          |          |          |               |

| MDC          | 040A        |        | SEVTCMP<15:3> |        |        |        |        |         |         |          |       |          |          |         | 0000     |          |          |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-45: PMD REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | AII<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | _      |        | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | -     | ADCMD | 0000          |

| PMD2        | 0772        |        | _      | -      | _      | _      | _      | _      | IC1MD  | _      | _     | _     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD3        | 0774        |        | _      | -      | _      | _      | CMPMD  | _      | _      | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4        | 0776        |        | _      | -      | _      | _      | _      | _      | _      | _      | _     | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        |        | _      | -      | _      | _      | _      | PWM2MD | PWM1MD | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD7        | 077C        |        | _      | -      | _      | _      | _      | CMP2MD | CMP1MD | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-46: PMD REGISTER MAP FOR dsPIC33FJ16GS402 AND dsPIC33FJ16GS404 DEVICES ONLY

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | _      | T3MD   | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | _      | _      | -      | _      | ı      | _      | IC2MD  | IC1MD  | _      | _     | _     | _     | _      | _     | OC2MD | OC1MD | 0000          |

| PMD3        | 0774        | _      | _      | I      | _      | I      | _      | I      | I      | _      | 1     | _     | _     | _      | _     | _     | -     | 0000          |

| PMD4        | 0776        | _      | _      | I      | _      | I      | _      | I      | I      | _      | 1     | _     | _     | REFOMD | _     | _     | -     | 0000          |

| PMD6        | 077A        | _      | _      | -      | _      | ı      | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD7        | 077C        | _      | _      | _      | _      | ı      | _      | 1      | _      | _      | 1     | _     | _     | _      | _     | _     | 1     | 0000          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-47: PMD REGISTER MAP FOR dsPIC33FJ16GS502 AND dsPIC33FJ16GS504 DEVICES ONLY

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | _      | T3MD   | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        |        | -      | -      | _      | -      | _      | IC2MD  | IC1MD  | _      | _     | _     | _     | _      | _     | OC2MD | OC1MD | 0000          |

| PMD3        | 0774        |        | -      | -      | _      | -      | CMPMD  | _      | _      | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4        | 0776        |        | -      | -      | _      | -      | _      | _      | _      | _      | _     | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        | _      | _      | _      | _      | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD7        | 077C        | _      | _      |        | _      | CMP4MD | CMP3MD | CMP2MD | CMP1MD | _      | I     | _     | _     | _      | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

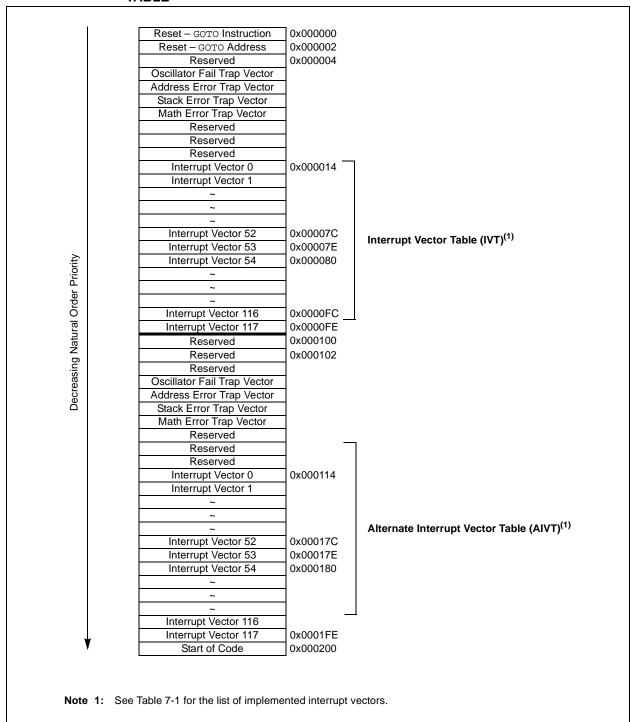

FIGURE 7-1: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 INTERRUPT VECTOR TABLE

## REGISTER 7-32: IPC27: INTERRUPT PRIORITY CONTROL REGISTER 27

| U-0    | R/W-1    | R/W-0    | R/W-0    | U-0 | R/W-1    | R/W-0    | R/W-0    |

|--------|----------|----------|----------|-----|----------|----------|----------|

| _      | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | _   | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 |

| bit 15 |          |          |          |     |          |          | bit 8    |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 ADCP1IP<2:0>: ADC Pair 1 Conversion Done Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 ADCP0IP<2:0>: ADC Pair 0 Conversion Done Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

\_

\_

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7-0 **Unimplemented:** Read as '0'

#### REGISTER 9-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|-----|--------|--------|--------|--------|

| _      | _   | _   | _   | PWM4MD | PWM3MD | PWM2MD | PWM1MD |

| bit 15 |     |     |     |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 Unimplemented: Read as '0'

bit 11 **PWM4MD**: PWM Generator 4 Module Disable bit

1 = PWM Generator 4 module is disabled 0 = PWM Generator 4 module is enabled

bit 10 **PWM3MD**: PWM Generator 3 Module Disable bit

1 = PWM Generator 3 module is disabled 0 = PWM Generator 3 module is enabled

bit 9 **PWM2MD**: PWM Generator 2 Module Disable bit

1 = PWM Generator 2 module is disabled 0 = PWM Generator 2 module is enabled

bit 8 **PWM1MD**: PWM Generator 1 Module Disable bit

1 = PWM Generator 1 module is disabled 0 = PWM Generator 1 module is enabled

bit 7-0 **Unimplemented:** Read as '0'

#### REGISTER 10-9: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | FLT1R5 | FLT1R4 | FLT1R3 | FLT1R2 | FLT1R1 | FLT1R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | -   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 FLT1R<5:0>: Assign PWM Fault Input 1 (FLT1) to the Corresponding RPn Pin bits

111111 = Input tied to Vss

100011 = Input tied to RP35

100010 = Input tied to RP34

100001 = Input tied to RP33

100000 = Input tied to RP32

•

•

•

00000 = Input tied to RP0

bit 7-0 **Unimplemented:** Read as '0'

## REGISTER 10-24: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP19R5 | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP18R5 | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP19R<5:0>: Peripheral Output Function is Assigned to RP19 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP18R<5:0>: Peripheral Output Function is Assigned to RP18 Output Pin bits

(see Table 10-2 for peripheral function numbers)

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

## REGISTER 10-25: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP21R5 | RP21R4 | RP21R3 | RP21R2 | RP21R1 | RP21R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP21R<5:0>: Peripheral Output Function is Assigned to RP21 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP20R<5:0>: Peripheral Output Function is Assigned to RP20 Output Pin bits

(see Table 10-2 for peripheral function numbers)

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

## REGISTER 15-1: PTCON: PWM TIME BASE CONTROL REGISTER (CONTINUED)

bit 3-0 SEVTPS<3:0>: PWM Special Event Trigger Output Postscaler Select bits<sup>(1)</sup>

1111 = 1:16 Postscaler generates a Special Event Trigger trigger on every sixteenth compare match event

•

•

0001 = 1:2 Postscaler generates a Special Event Trigger on every second compare match event

0000 = 1:1 Postscaler generates a Special Event Trigger on every compare match event

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|-------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|

| SSEN <sup>(3)</sup> | CKP   | MSTEN | SPRE2 <sup>(2)</sup> | SPRE1 <sup>(2)</sup> | SPRE0 <sup>(2)</sup> | PPRE1 <sup>(2)</sup> | PPRE0 <sup>(2)</sup> |

| bit 7               |       |       |                      |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12 **DISSCK:** Disable SCKx Pin bit (SPI Master modes only)

1 = Internal SPI clock is disabled; pin functions as I/O

0 = Internal SPI clock is enabled

bit 11 DISSDO: Disable SDOx Pin bit

1 = SDOx pin is not used by module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (see bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)<sup>(3)</sup>

$1 = \overline{SSx}$  pin is used for Slave mode

0 = SSx pin is not used by module; pin controlled by port function

bit 6 CKP: Clock Polarity Select bit

1 = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

**Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

2: Do not set both primary and secondary prescalers to a value of 1:1.

3: This bit must be cleared when FRMEN = 1.

## REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- **Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- **2:** Do not set both primary and secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

## 19.0 HIGH-SPEED 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed 10-Bit Analog-to-Digital Converter (ADC)" (DS70000321) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices provide high-speed, successive approximation Analog-to-Digital conversions to support applications, such as AC/DC and DC/DC power converters.

#### 19.1 Features Overview

The ADC module comprises the following features:

- 10-bit resolution

- · Unipolar inputs

- Up to two Successive Approximation Registers (SARs)

- Up to 12 external input channels

- · Up to two internal analog inputs

- · Dedicated result register for each analog input

- ±1 LSB accuracy at 3.3V

- · Single supply operation

- 4 Msps conversion rate at 3.3V (devices with two SARs)

- 2 Msps conversion rate at 3.3V (devices with one SAR)

- Low-power CMOS technology

#### 19.2 Module Description

This ADC module is designed for applications that require low latency between the request for conversion and the resultant output data. Typical applications include:

- · AC/DC power supplies

- DC/DC Converters

- Power Factor Correction (PFC)

This ADC works with the high-speed PWM module in power control applications that require high-frequency control loops. This module can sample and convert two analog inputs in a 0.5 microsecond when two SARs are used. This small conversion delay reduces the "phase lag" between measurement and control system response.

Up to five inputs may be sampled at a time (four inputs from the dedicated Sample-and-Hold circuits and one from the shared Sample-and-Hold circuit). If multiple inputs request conversion, the ADC will convert them in a sequential manner, starting with the lowest order input.

This ADC design provides each pair of analog inputs (AN1, AN0), (AN3, AN2),..., the ability to specify its own trigger source out of a maximum of sixteen different trigger sources. This capability allows this ADC to sample and convert analog inputs that are associated with PWM generators operating on Independent Time Bases (ITBs).

The user application typically requires synchronization between analog data sampling and PWM output to the application circuit. The very high-speed operation of this ADC module allows "data on demand".

In addition, several hardware features have been added to the peripheral interface to improve real-time performance in a typical DSP-based application.

- · Result alignment options

- · Automated sampling

- External conversion start control

- Two internal inputs to monitor the INTREF internal reference and the EXTREF input signal

#### 19.3 Module Functionality

The high-speed, 10-bit ADC module is designed to support power conversion applications when used with the high-speed PWM module. The ADC may have one or two SAR modules, depending on the device variant. If two SARs are present on a device, two conversions can be processed at a time, yielding 4 Msps conversion rate. If only one SAR is present on a device, only one conversion can be processed at a time, yielding 2 Msps conversion rate. The high-speed 10-bit ADC produces two 10-bit conversion results in a 0.5 microsecond.

The ADC module supports up to 12 external analog inputs and two internal analog inputs. To monitor reference voltage, two internal inputs, AN12 and AN13, are connected to the EXTREF and INTREF voltages, respectively.

The analog reference voltage is defined as the device supply voltage (AVDD/AVSS).

Block diagrams of the ADC module are shown in Figure 19-1 through Figure 19-6.

TABLE 24-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARACT       | ERISTICS               |            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                  |       |                        |  |  |

|------------------|------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------------|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Max        | Units                                                                                                                                                                                                                                            | Jnits Conditions |       |                        |  |  |

| Idle Current (II | DLE): Core Of          | f Clock On | Base Current <sup>(</sup>                                                                                                                                                                                                                        | 2)               |       |                        |  |  |

| DC40d            | 48                     | _          | mA                                                                                                                                                                                                                                               | -40°C            |       |                        |  |  |

| DC40a            | 48                     | _          | mA                                                                                                                                                                                                                                               | +25°C            | 3.3V  | 10 MIPS                |  |  |

| DC40b            | 48                     | _          | mA                                                                                                                                                                                                                                               | +85°C            | 3.3 V | TO WIFS                |  |  |

| DC40c            | 48                     | _          | mA                                                                                                                                                                                                                                               | +125°C           |       |                        |  |  |

| DC41d            | 60                     | _          | mA                                                                                                                                                                                                                                               | -40°C            |       |                        |  |  |

| DC41a            | 60                     | _          | mA                                                                                                                                                                                                                                               | +25°C            | 3.3V  | 16 MIPS <sup>(3)</sup> |  |  |

| DC41b            | 60                     | _          | mA                                                                                                                                                                                                                                               | +85°C            | 3.34  | TO MIPS                |  |  |

| DC41c            | 60                     | _          | mA                                                                                                                                                                                                                                               | +125°C           |       |                        |  |  |

| DC42d            | 68                     | _          | mA                                                                                                                                                                                                                                               | -40°C            |       |                        |  |  |

| DC42a            | 68                     | _          | mA                                                                                                                                                                                                                                               | +25°C            | 3.3V  | 20 MIPS <sup>(3)</sup> |  |  |

| DC42b            | 68                     | _          | mA                                                                                                                                                                                                                                               | +85°C            | 3.34  | 20 MIP3. 7             |  |  |

| DC42c            | 68                     | _          | mA                                                                                                                                                                                                                                               | +125°C           |       |                        |  |  |

| DC43d            | 77                     | _          | mA                                                                                                                                                                                                                                               | -40°C            |       |                        |  |  |

| DC43a            | 77                     | _          | mA                                                                                                                                                                                                                                               | +25°C            | 3.3V  | 30 MIPS <sup>(3)</sup> |  |  |

| DC43b            | 77                     | _          | mA                                                                                                                                                                                                                                               | +85°C            | 3.34  | 30 MIF3(*)             |  |  |

| DC43c            | 77                     | _          | mA                                                                                                                                                                                                                                               | +125°C           | 7     |                        |  |  |

| DC44d            | 86                     | _          | mA                                                                                                                                                                                                                                               | -40°C            |       |                        |  |  |

| DC44a            | 86                     | _          | mA                                                                                                                                                                                                                                               | +25°C            | 2.21/ | 40 MIDS                |  |  |

| DC44b            | 86                     | _          | mA                                                                                                                                                                                                                                               | +85°C            | 3.3V  | 40 MIPS                |  |  |

| DC44c            | 86                     | _          | mA                                                                                                                                                                                                                                               | +125°C           |       |                        |  |  |

- Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 2: Base Idle current (IIDLE) is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- · JTAG is disabled

- **3:** These parameters are characterized but not tested in manufacturing.

TABLE 24-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTERISTICS |                        |     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |       |            |      |         |

|--------------------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|---------|

| Parameter No.      | Typical <sup>(1)</sup> | Max | Doze<br>Ratio                                                                                                                                                                                                                                    | Units | Conditions |      |         |

| Doze Current (IDO  | ZE) <sup>(2)</sup>     |     |                                                                                                                                                                                                                                                  |       |            |      |         |

| DC73a              | 75                     | 105 | 1:2                                                                                                                                                                                                                                              | mA    |            |      |         |

| DC73f              | 60                     | 105 | 1:64                                                                                                                                                                                                                                             | mA    | -40°C      | 3.3V | 40 MIPS |

| DC73g              | 60                     | 105 | 1:128                                                                                                                                                                                                                                            | mA    |            |      |         |

| DC70a              | 75                     | 105 | 1:2                                                                                                                                                                                                                                              | mA    |            |      |         |

| DC70f              | 60                     | 105 | 1:64                                                                                                                                                                                                                                             | mA    | +25°C      | 3.3V | 40 MIPS |

| DC70g              | 60                     | 105 | 1:128                                                                                                                                                                                                                                            | mA    |            |      |         |

| DC71a              | 75                     | 105 | 1:2                                                                                                                                                                                                                                              | mA    |            |      |         |

| DC71f              | 60                     | 105 | 1:64                                                                                                                                                                                                                                             | mA    | +85°C      | 3.3V | 40 MIPS |

| DC71g              | 60                     | 105 | 1:128                                                                                                                                                                                                                                            | mA    |            |      |         |

| DC72a              | 75                     | 105 | 1:2                                                                                                                                                                                                                                              | mA    |            |      |         |

| DC72f              | 60                     | 105 | 1:64                                                                                                                                                                                                                                             | mA    | +125°C     | 3.3V | 40 MIPS |

| DC72g              | 60                     | 105 | 1:128                                                                                                                                                                                                                                            | mA    |            |      |         |

- **Note 1:** Data in the Typical column is at 3.3V, +25°C unless otherwise stated.

- 2: IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU executing while(1) statement

- JTAG disabled

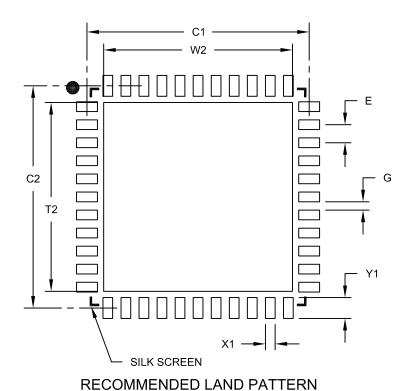

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Units MILLIMETERS Dimension Limits MIN MAX NOM 0.65 BSC Contact Pitch Ε Optional Center Pad Width W2 6.60 Optional Center Pad Length T2 6.60 8.00 Contact Pad Spacing C1 Contact Pad Spacing C2 8.00 Contact Pad Width (X44) X1 0.35 Contact Pad Length (X44) <u>Y1</u> 0.85 Distance Between Pads G 0.25

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

| Timing Diagrams                                  |     |

|--------------------------------------------------|-----|

| Analog-to-Digital Conversion per Input           | 329 |

| Brown-out Situations                             | 94  |

| External Clock                                   | 301 |

| High-Speed PWMx                                  | 311 |

| High-Speed PWMx Fault                            |     |

| I/O                                              |     |

| I2Cx Bus Data (Master Mode)                      |     |

| I2Cx Bus Data (Slave Mode)                       |     |

| I2Cx Bus Start/Stop Bits (Master Mode)           |     |

| I2Cx Bus Start/Stop Bits Slave Mode)             |     |

| Input Capture x (ICx)                            |     |

| OCx/PWMx                                         |     |

| Output Compare x (OCx)                           |     |

| Reset, Watchdog Timer, Oscillator Start-up Timer | 309 |

|                                                  | 205 |

| and Power-up Timer                               | 305 |

| SPIx Master Mode (Full-Duplex, CKE = 0,          |     |

| CKP = x, SMP = 1)                                | 315 |

| SPIx Master Mode (Full-Duplex, CKE = 1,          |     |

| CKP = x, CMP = 1)                                | 314 |

| SPIx Master Mode (Half-Duplex,                   |     |

| Transmit Only, CKE = 0)                          | 312 |

| SPIx Master Mode (Half-Duplex,                   |     |

| Transmit Only, CKE = 1)                          | 312 |

| SPIx Slave Mode (Full-Duplex, CKE = 0,           |     |

| CKP = 0, SMP = 0)                                | 322 |

| SPIx Slave Mode (Full-Duplex, CKE = 0,           |     |

| CKP = 1, SMP = 0)                                | 320 |

| SPIx Slave Mode (Full-Duplex, CKE = 1,           | 0_0 |

| CKP = 0, SMP = 0)                                | 316 |

| SPIx Slave Mode (Full-Duplex, CKE = 1,           | 310 |

| CKP = 1, SMP = 0)                                | 210 |

|                                                  |     |

| System Reset                                     | 93  |

| Timer1, 2, 3 External Clock                      | 307 |

| Timing Requirements                              |     |

| 10-Bit, High-Speed ADC Requirements              |     |

| External Clock301,                               |     |

| I/O                                              | 304 |

| Input Capture x                                  | 309 |

| Simple OCx/PWMx Mode                             | 345 |

| SPIx Master Mode (CKE = 0)                       | 339 |

| SPIx Master Mode (Full-Duplex, CKE = 0,          |     |

| CKP = x, SMP = 1)                                | 315 |

| SPIx Master Mode (Full-Duplex, CKE = 1,          |     |

| CKP = x, SMP = 1)                                | 314 |

| SPIx Master Mode (Half-Duplex,                   | 517 |

| Transmit Only)                                   | 212 |

| SPIx Module Master Mode (CKE = 1)                |     |

|                                                  |     |

| SPIx Module Slave Mode (CKE = 0)                 |     |

| SPIx Module Slave Mode (CKE = 1)                 | 340 |

| SPIx Slave Mode (Full-Duplex, CKE = 0,           |     |

| CKP = 0, SMP = 0)                                | 323 |

| SPIx Slave Mode (Full-Duplex, CKE = 0,           |     |

| CKP = 1, SMP = 0)                                | 321 |

| SPIx Slave Mode (Full-Duplex, CKE = 1,           |     |

| CKP = 0, SMP = 0)                                | 317 |

| SPIx Slave Mode (Full-Duplex, CKE = 1,           |     |

| CKP = 1, SMP = 0)                                | 319 |

| Timing Specifications                             |     |

|---------------------------------------------------|-----|

| 10-Bit High-Speed ADC Module                      | 328 |

| Auxiliary PLL Clock                               | 302 |

| Comparator Module                                 |     |

| DAC Module                                        | 330 |

| DAC Output Buffer DC                              | 33′ |

| High-Speed PWMx Requirements                      | 311 |

| I2Cx Bus Data Requirements (Master Mode)          | 325 |

| I2Cx Bus Data Requirements (Slave Mode)           | 327 |

| Output Compare x Requirements                     | 309 |

| PLL Clock 302,                                    |     |

| Reset, Watchdog Timer, Oscillator Start-up Timer, |     |

| Power-up Timer and Brown-out Reset                |     |

| Requirements                                      | 306 |

| Simple OCx/PWMx Mode Requirements                 | 310 |

| Timer1 External Clock Requirements                | 307 |

| Timer2 External Clock Requirements                | 308 |

| Timer3 External Clock Requirements                | 308 |

| U                                                 |     |

| Universal Asynchronous Receiver                   |     |

| Transmitter (UART)                                | 233 |

| Using the RCON Status Bits                        |     |

| v                                                 |     |

| Voltage Regulator (On-Chip)                       | 270 |

| W                                                 |     |

| Watchdog Timer (WDT)267,                          | 271 |

| Programming Considerations                        | 271 |

| Watchdog Timer Time-out Reset (WDTO)              |     |

| WWW Address                                       |     |

| WWW, On-Line Support                              |     |

| • •                                               |     |