Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502-e-so |

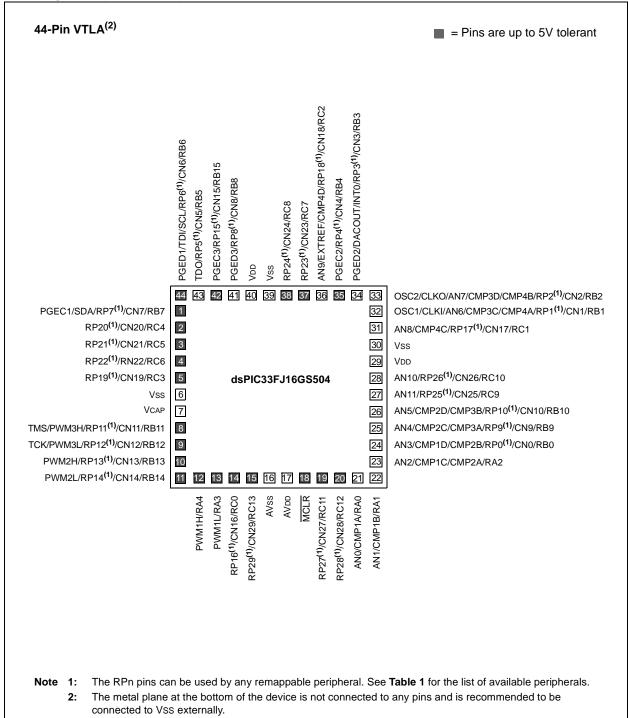

#### Pin Diagrams (Continued)

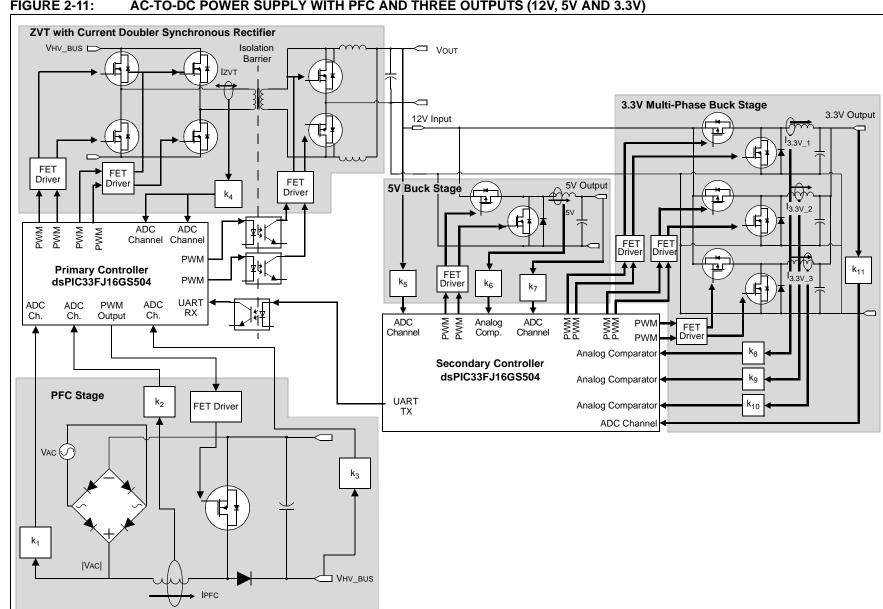

AC-TO-DC POWER SUPPLY WITH PFC AND THREE OUTPUTS (12V, 5V AND 3.3V) **FIGURE 2-11:**

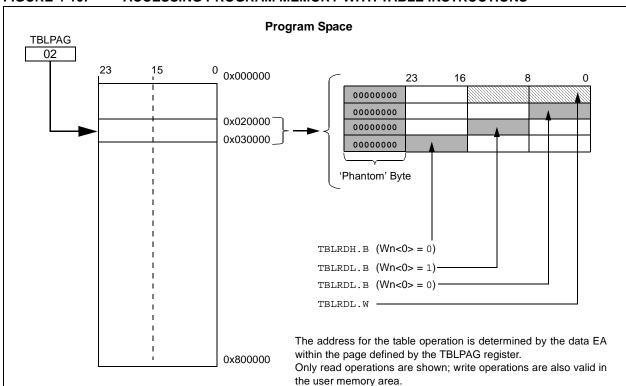

# 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte

of the lower program word is mapped to the

lower byte of a data address. The upper byte

is selected when byte select is '1'; the lower

byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction.

The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

## 7.3 Interrupt Control and Status Registers

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices implement 27 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFSx

- IECx

- IPCx

- INTTREG

#### 7.3.1 INTCON1 AND INTCON2

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

#### 7.3.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.3.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.3.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit is found in IEC0<0> and the INT0IP bits are found in the first position of IPC0 (IPC0<2:0>).

#### 7.3.6 STATUS/CONTROL REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality.

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user can change the current CPU priority level by writing to the IPL bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software

All Interrupt registers are described in Register 7-1 through Register 7-35 in the following pages.

#### REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| R-0    | R-0 | R/C-0 | R/C-0 | R-0 | R/C-0 | R -0 | R/W-0 |

|--------|-----|-------|-------|-----|-------|------|-------|

| OA     | ОВ  | SA    | SB    | OAB | SAB   | DA   | DC    |

| bit 15 |     |       |       |     |       |      | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | N     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

**Legend:** C = Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

110 = CPU Interrupt Priority Level is 6 (14)

101 = CPU Interrupt Priority Level is 5 (13)

100 = CPU Interrupt Priority Level is 4 (12)

011 = CPU Interrupt Priority Level is 3 (11)

010 = CPU Interrupt Priority Level is 2 (10)

001 = CPU Interrupt Priority Level is 1 (9)

000 = CPU Interrupt Priority Level is 0 (8)

Note 1: For complete register details, see Register 3-1.

2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0   |

|--------|-----|-----|-------|-------|-----|-----|-------|

| _      | _   | _   | US    | EDT   | DL2 | DL1 | DL0   |

| bit 15 |     |     |       |       |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-------|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND   | IF    |

| bit 7 |       |       |        |                     |       |       | bit 0 |

**Legend:** C = Clearable bit

R = Readable bit W = Writable bit -n = Value at POR '1' = Bit is set

0' = Bit is cleared x = Bit is unknown y = Unimplemented bit, read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 10-22: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP15R5 | RP15R4 | RP15R3 | RP15R2 | RP15R1 | RP15R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP15R<5:0>: Peripheral Output Function is Assigned to RP15 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP14R<5:0>: Peripheral Output Function is Assigned to RP14 Output Pin bits

(see Table 10-2 for peripheral function numbers)

Note 1: This register is not implemented in the dsPIC33FJ06GS101 device.

#### REGISTER 10-23: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP17R5 | RP17R4 | RP17R3 | RP17R2 | RP17R1 | RP17R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP17R<5:0>: Peripheral Output Function is Assigned to RP17 Output Pin bits

(see Table 10-2 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP16R<5:0>: Peripheral Output Function is Assigned to RP16 Output Pin bits

(see Table 10-2 for peripheral function numbers)

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

#### REGISTER 15-6: **PWMCONX: PWMx CONTROL REGISTER**

| HS/HC-0                | HS/HC-0               | HS/HC-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0              | R/W-0               |

|------------------------|-----------------------|---------|--------|-------|--------|--------------------|---------------------|

| FLTSTAT <sup>(1)</sup> | CLSTAT <sup>(1)</sup> | TRGSTAT | FLTIEN | CLIEN | TRGIEN | ITB <sup>(3)</sup> | MDCS <sup>(3)</sup> |

| bit 15                 |                       |         |        |       |        |                    | bit 8               |

| R/W-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0                | R/W-0                | R/W-0 |

|-------|-------|-----|-----|-----|----------------------|----------------------|-------|

| DTC1  | DTC0  | _   | _   | _   | CAM <sup>(2,3)</sup> | XPRES <sup>(4)</sup> | IUE   |

| bit 7 |       |     |     |     |                      |                      | bit 0 |

| <b>Legend:</b> HC = Hardware Clearable bit |                  | HS = Hardware Settable bit |                    |  |  |

|--------------------------------------------|------------------|----------------------------|--------------------|--|--|

| R = Readable bit                           | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |  |  |

| -n = Value at POR                          | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |  |  |

FLTSTAT: Fault Interrupt Status bit(1) bit 15 1 = Fault interrupt is pending 0 = No Fault interrupt is pending; this bit is cleared by setting FLTIEN = 0 bit 14 **CLSTAT:** Current-Limit Interrupt Status bit<sup>(1)</sup> 1 = Current-limit interrupt is pending 0 = No current-limit interrupt is pending; this bit is cleared by setting CLIEN = 0 bit 13 TRGSTAT: Trigger Interrupt Status bit 1 = Trigger interrupt is pending 0 = No trigger interrupt is pending; this bit is cleared by setting TRGIEN = 0 bit 12 FLTIEN: Fault Interrupt Enable bit 1 = Fault interrupt is enabled 0 = Fault interrupt is disabled and the FLTSTAT bit is cleared bit 11 **CLIEN:** Current-Limit Interrupt Enable bit 1 = Current-limit interrupt is enabled 0 = Current-limit interrupt is disabled and the CLSTAT bit is cleared bit 10 **TRGIEN:** Trigger Interrupt Enable bit 1 = A trigger event generates an interrupt request 0 = Trigger event interrupts are disabled and the TRGSTAT bit is cleared ITB: Independent Time Base Mode bit(3) bit 9 1 = PHASEx/SPHASEx register provides time base period for this PWM generator 0 = PTPER register provides timing for this PWM generator MDCS: Master Duty Cycle Register Select bit (3) bit 8 1 = MDC register provides duty cycle information for this PWM generator 0 = PDCx/SDCx register provides duty cycle information for this PWM generator bit 7-6 DTC<1:0>: Dead-Time Control bits

11 = Reserved

10 = Dead-time function is disabled

01 = Negative dead time is actively applied for all output modes 00 = Positive dead time is actively applied for all output modes

bit 5-3 Unimplemented: Read as '0'

Note 1: Software must clear the interrupt status here and the corresponding IFSx bit in the interrupt controller.

- The Independent Time Base mode (ITB = 1) must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- 3: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- To operate in External Period Reset mode, configure FCLCONx<CLMOD> = 0 and PWMCONx<ITB> = 1.

#### REGISTER 15-7: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER<sup>(1,2)</sup>

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------|-------|-------|-------|-------|-------|-------|-------|

| PDCx<15:8> |       |       |       |       |       |       |       |

| bit 15 bit |       |       |       |       |       |       | bit 8 |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| PDCx<7:0> |       |       |       |       |       |       |       |

| bit 7 bi  |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 PDCx<15:0>: PWM Generator # Duty Cycle Value bits

- **Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL. The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period-0x0008.

- 2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

#### REGISTER 15-8: SDCx: PWMx SECONDARY DUTY CYCLE REGISTER<sup>(1,2)</sup>

| R/W-0        | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------------|------------|-------|-------|-------|-------|-------|-------|

|              | SDCx<15:8> |       |       |       |       |       |       |

| bit 15 bit 8 |            |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | SDCx  | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 SDCx<15:0>: Secondary Duty Cycle for PWMxL Output Pin bits

- Note 1: The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle. The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period-0x0008.

- 2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

#### REGISTER 15-19: PWMCAPx: PRIMARY PWMx TIME BASE CAPTURE REGISTER

| R-0               | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

|-------------------|-----|-----|-----|-----|-----|-----|-----|

| PWMCAP<15:8>(1,2) |     |     |     |     |     |     |     |

| bit 15 b          |     |     |     |     |     |     |     |

| R-0   | R-0 | R-0                      | R-0 | R-0 | U-0 | U-0   | U-0 |

|-------|-----|--------------------------|-----|-----|-----|-------|-----|

|       | PW  | MCAP<7:3> <sup>(1,</sup> | _   | _   | _   |       |     |

| bit 7 |     |                          |     |     |     | bit 0 |     |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **PWMCAP<15:3>:** Captured PWM Time Base Value bits<sup>(1,2)</sup>

The value in this register represents the captured PWM time base value when a leading edge is

detected on the current-limit input.

bit 2-0 **Unimplemented:** Read as '0'

Note 1: The capture feature is only available on the primary output (PWMxH).

2: This feature is active only after LEB processing on the current-limit input signal is complete.

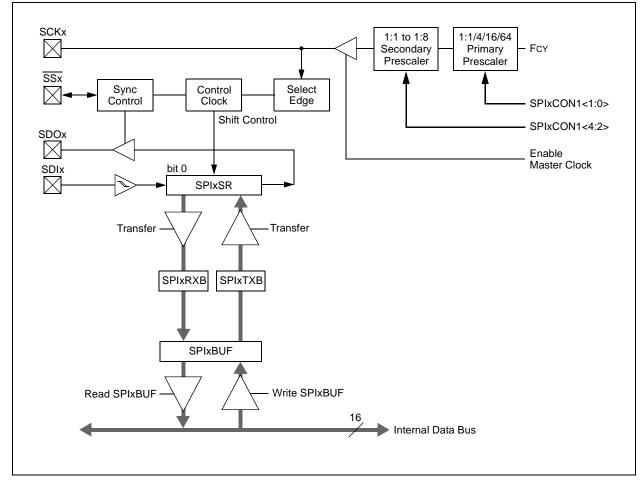

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70206) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters and so on. The SPI module is compatible with SPI and SIOP from Motorola®.

The SPI module consists of a 16-bit shift register, SPIxSR (where x = 1), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of the following four pins:

- SDIx (Serial Data Input)

- SDOx (Serial Data Output)

- SCKx (Shift Clock Input Or Output)

- SSx (Active-Low Slave Select).

In Master mode operation, SCK is a clock output; in Slave mode, it is a clock input.

FIGURE 16-1: SPIX MODULE BLOCK DIAGRAM

#### **ADCPC2: ANALOG-TO-DIGITAL CONVERT PAIR** REGISTER 19-7: CONTROL REGISTER 2<sup>(1)</sup> (CONTINUED)

bit 12-8 TRGSRC5<4:0>: Trigger 5 Source Selection bits Selects trigger source for conversion of Analog Channels AN11 and AN10. 11111 = Timer2 period match 11011 = Reserved 11010 = PWM Generator 4 current-limit ADC trigger 11001 = PWM Generator 3 current-limit ADC trigger 11000 = PWM Generator 2 current-limit ADC trigger 10111 = PWM Generator 1 current-limit ADC trigger 10110 = Reserved 10010 = Reserved 10001 = PWM Generator 4 secondary trigger is selected 10000 = PWM Generator 3 secondary trigger is selected 01111 = PWM Generator 2 secondary trigger is selected 01110 = PWM Generator 1 secondary trigger is selected 01101 = Reserved 01100 = Timer1 period match 01000 = Reserved 00111 = PWM Generator 4 primary trigger is selected 00110 = PWM Generator 3 primary trigger is selected 00101 = PWM Generator 2 primary trigger is selected 00100 = PWM Generator 1 primary trigger is selected 00011 = PWM Special Event Trigger is selected 00010 = Global software trigger is selected 00001 = Individual software trigger is selected 00000 = No conversion is enabled bit 7 IRQEN4: Interrupt Request Enable 4 bit 1 = Enables IRQ generation when requested conversion of Channels AN9 and AN8 is completed 0 = IRQ is not generated bit 6 PEND4: Pending Conversion Status 4 bit 1 = Conversion of Channels AN9 and AN8 is pending; set when selected trigger is asserted 0 = Conversion is complete bit 5 SWTRG4: Software Trigger 4 bit 1 = Starts conversion of AN9 and AN8 (if selected by the TRGSRCx bits)(2)

- This bit is automatically cleared by hardware when the PEND4 bit is set.

- 0 = Conversion has not started

- **Note 1:** This register is only implemented in the dsPIC33FJ16GS504 devices.

- The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

#### TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                                                               | Assembly Syntax  | Description                                    | # of<br>Words | # of<br>Cycles          | Status Flags<br>Affected |

|--------------------|----------------------|-------------------------------------------------------------------------------|------------------|------------------------------------------------|---------------|-------------------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,Ad                                                               | cc,Wx,Wxd,Wy,Wyd | Multiply Wm by Wn to Accumulator               | 1             | 1                       | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY<br>Wm*Wm,Ad                                                               | cc,Wx,Wxd,Wy,Wyd | Square Wm to Accumulator                       | 1             | 1                       | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,Acc,Wx,Wxd,Wy,Wyd                                              |                  | -(Multiply Wm by Wn) to Accumulator            | 1             | 1                       | None                     |

| 50                 | MSC                  | MSC Wm*Wm, Acc, Wx, Wxd, Wy, Wyd Multiply and Subtract from Accumulator , AWB |                  | 1                                              | 1             | OA,OB,OAB,<br>SA,SB,SAB |                          |

| 51                 | MUL                  | MUL.SS                                                                        | Wb, Ws, Wnd      | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)       | 1             | 1                       | None                     |

|                    |                      | MUL.SU                                                                        | Wb, Ws, Wnd      | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)     | 1             | 1                       | None                     |

|                    |                      | MUL.US                                                                        | Wb, Ws, Wnd      | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)     | 1             | 1                       | None                     |

|                    |                      | MUL.UU                                                                        | Wb,Ws,Wnd        | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(Ws)   | 1             | 1                       | None                     |

|                    |                      | MUL.SU                                                                        | Wb,#lit5,Wnd     | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)   | 1             | 1                       | None                     |

|                    |                      | MUL.UU                                                                        | Wb,#lit5,Wnd     | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5) | 1             | 1                       | None                     |

|                    |                      | MUL                                                                           | f                | W3:W2 = f * WREG                               | 1             | 1                       | None                     |

| 52                 | NEG                  | NEG                                                                           | Acc              | Negate Accumulator                             | 1             | 1                       | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG                                                                           | f                | $f = \overline{f} + 1$                         | 1             | 1                       | C,DC,N,OV,Z              |

|                    |                      | NEG                                                                           | f,WREG           | WREG = <del>f</del> + 1                        | 1             | 1                       | C,DC,N,OV,Z              |

|                    |                      | NEG                                                                           | Ws,Wd            | $Wd = \overline{Ws} + 1$                       | 1             | 1                       | C,DC,N,OV,Z              |

| 53                 | NOP                  | NOP                                                                           |                  | No Operation                                   | 1             | 1                       | None                     |

|                    |                      | NOPR                                                                          |                  | No Operation                                   | 1             | 1                       | None                     |

| 54                 | POP                  | POP                                                                           | f                | Pop f from Top-of-Stack (TOS)                  | 1             | 1                       | None                     |

|                    |                      | POP                                                                           | Wdo              | Pop from Top-of-Stack (TOS) to Wdo             | 1             | 1                       | None                     |

|                    |                      | POP.D                                                                         | Wnd              | Pop from Top-of-Stack (TOS) to W(nd):W(nd + 1) | 1             | 2                       | None                     |

|                    |                      | POP.S                                                                         |                  | Pop Shadow Registers                           | 1             | 1                       | All                      |

| 55                 | PUSH                 | PUSH                                                                          | f                | Push f to Top-of-Stack (TOS)                   | 1             | 1                       | None                     |

|                    |                      | PUSH                                                                          | Wso              | Push Wso to Top-of-Stack (TOS)                 | 1             | 1                       | None                     |

|                    |                      | PUSH.D                                                                        | Wns              | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)     | 1             | 2                       | None                     |

|                    |                      | PUSH.S                                                                        |                  | Push Shadow Registers                          | 1             | 1                       | None                     |

| 56                 | PWRSAV               | PWRSAV                                                                        | #lit1            | Go into Sleep or Idle mode                     | 1             | 1                       | WDTO,Sleep               |

| 57                 | RCALL                | RCALL                                                                         | Expr             | Relative Call                                  | 1             | 2                       | None                     |

|                    |                      | RCALL                                                                         | Wn               | Computed Call                                  | 1             | 2                       | None                     |

| 58                 | REPEAT               | REPEAT                                                                        | #lit14           | Repeat Next Instruction lit14 + 1 times        | 1             | 1                       | None                     |

|                    |                      | REPEAT                                                                        | Wn               | Repeat Next Instruction (Wn) + 1 times         | 1             | 1                       | None                     |

| 59                 | RESET                | RESET                                                                         |                  | Software Device Reset                          | 1             | 1                       | None                     |

| 60                 | RETFIE               | RETFIE                                                                        |                  | Return from interrupt                          | 1             | 3 (2)                   | None                     |

| 61                 | RETLW                | RETLW                                                                         | #lit10,Wn        | Return with Literal in Wn                      | 1             | 3 (2)                   | None                     |

| 62                 | RETURN               | RETURN                                                                        |                  | Return from Subroutine                         | 1             | 3 (2)                   | None                     |

| 63                 | RLC                  | RLC                                                                           | f                | f = Rotate Left through Carry f                | 1             | 1                       | C,N,Z                    |

|                    |                      | RLC                                                                           | f,WREG           | WREG = Rotate Left through Carry f             | 1             | 1                       | C,N,Z                    |

| 0.4                |                      | RLC                                                                           | Ws,Wd            | Wd = Rotate Left through Carry Ws              | 1             | 1                       | C,N,Z                    |

| 64                 | RLNC                 | RLNC                                                                          | f supra          | f = Rotate Left (No Carry) f                   | 1             | 1                       | N,Z                      |

|                    |                      | RLNC                                                                          | f,WREG           | WREG = Rotate Left (No Carry) f                | 1             | 1                       | N,Z                      |

| CF.                | DDG.                 | RLNC                                                                          | Ws,Wd            | Wd = Rotate Left (No Carry) Ws                 | 1             | 1                       | N,Z                      |

| 65                 | RRC                  | RRC                                                                           | f ward           | f = Rotate Right through Carry f               | 1             | 1                       | C,N,Z                    |

|                    | ĺ                    | RRC                                                                           | f,WREG           | WREG = Rotate Right through Carry f            | 1             | 1                       | C,N,Z                    |

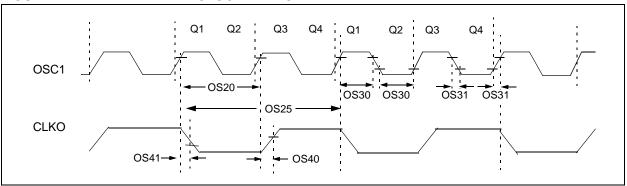

FIGURE 24-2: EXTERNAL CLOCK TIMING

**TABLE 24-16: EXTERNAL CLOCK TIMING REQUIREMENTS**

| AC CHA       | AC CHARACTERISTICS |                                                                                    |              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |              |            |                           |  |  |

|--------------|--------------------|------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|---------------------------|--|--|

| Param<br>No. | Symb               | Characteristic                                                                     | Min          | Typ <sup>(1)</sup>                                                                                                                                                                                                                                  | Max          | Units      | Conditions                |  |  |

| OS10         | FIN                | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC           | _                                                                                                                                                                                                                                                   | 40           | MHz        | EC                        |  |  |

|              |                    | Oscillator Crystal Frequency                                                       | 3.5<br>10    | _                                                                                                                                                                                                                                                   | 10<br>40     | MHz<br>MHz | XT<br>HS                  |  |  |

| OS20         | Tosc               | Tosc = 1/Fosc                                                                      | 12.5         | _                                                                                                                                                                                                                                                   | DC           | ns         |                           |  |  |

| OS25         | TCY                | Instruction Cycle Time <sup>(2)</sup>                                              | 25           | _                                                                                                                                                                                                                                                   | DC           | ns         |                           |  |  |

| OS30         | TosL,<br>TosH      | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc | _                                                                                                                                                                                                                                                   | 0.625 x Tosc | ns         | EC                        |  |  |

| OS31         | TosR,<br>TosF      | External Clock in (OSC1)<br>Rise or Fall Time                                      | _            | _                                                                                                                                                                                                                                                   | 20           | ns         | EC                        |  |  |

| OS40         | TckR               | CLKO Rise Time <sup>(3)</sup>                                                      | _            | 5.2                                                                                                                                                                                                                                                 | _            | ns         |                           |  |  |

| OS41         | TckF               | CLKO Fall Time <sup>(3)</sup>                                                      | _            | 5.2                                                                                                                                                                                                                                                 | _            | ns         |                           |  |  |

| OS42         | Gм                 | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14           | 16                                                                                                                                                                                                                                                  | 18           | mA/V       | VDD = 3.3V,<br>TA = +25°C |  |  |

- **Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 2: Instruction cycle period (TcY) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: Data for this parameter is Preliminary. This parameter is characterized, but not tested in manufacturing.

TABLE 24-22: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

| AC CH        | ARACTER | RISTICS                                                  | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                                      |     |       |                                                                                          |

|--------------|---------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|-------|------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic <sup>(1)</sup>                            | Min                                                                                                                                                                                                                                              | Typ <sup>(2)</sup>                   | Max | Units | Conditions                                                                               |

| SY10         | ТмсL    | MCLR Pulse Width (low)                                   | 2                                                                                                                                                                                                                                                | _                                    | _   | μS    | -40°C to +85°C                                                                           |

| SY11         | TPWRT   | Power-up Timer Period                                    |                                                                                                                                                                                                                                                  | 2<br>4<br>8<br>16<br>32<br>64<br>128 | 1   | ms    | -40°C to +85°C,<br>User programmable                                                     |

| SY12         | TPOR    | Power-on Reset Delay                                     | 3                                                                                                                                                                                                                                                | 10                                   | 30  | μS    | -40°C to +85°C                                                                           |

| SY13         | Tioz    | I/O High-Impedance from MCLR Low or Watchdog Timer Reset | 0.68                                                                                                                                                                                                                                             | 0.72                                 | 1.2 | μS    |                                                                                          |

| SY20         | TWDT1   | Watchdog Timer Time-out Period                           | _                                                                                                                                                                                                                                                | _                                    | _   | ms    | See Section 21.4 "Watch-<br>dog Timer (WDT)" and<br>LPRC Parameter F21a<br>(Table 24-20) |

| SY30         | Tost    | Oscillator Start-up Time                                 | _                                                                                                                                                                                                                                                | 1024 Tosc                            | _   |       | Tosc = OSC1 period                                                                       |

**Note 1:** These parameters are characterized but not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

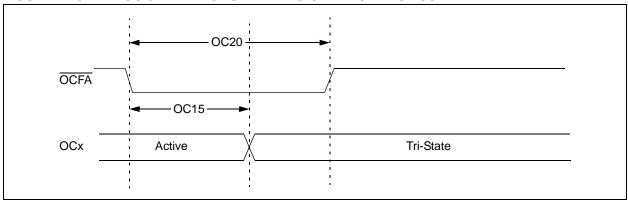

FIGURE 24-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

TABLE 24-28: SIMPLE OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHAI      | AC CHARACTERISTICS |                                |          | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |          |       |            |  |  |

|--------------|--------------------|--------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|------------|--|--|

| Param<br>No. | Symbol             | Characteristic <sup>(1)</sup>  | Min      | Тур                                                                                                                                                                                                                                              | Max      | Units | Conditions |  |  |

| OC15         | TFD                | Fault Input to PWMx I/O Change | _        | _                                                                                                                                                                                                                                                | Tcy + 20 | ns    |            |  |  |

| OC20         | TFLT               | Fault Input Pulse Width        | Tcy + 20 | _                                                                                                                                                                                                                                                | _        | ns    |            |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

# DS70000318G-page 347

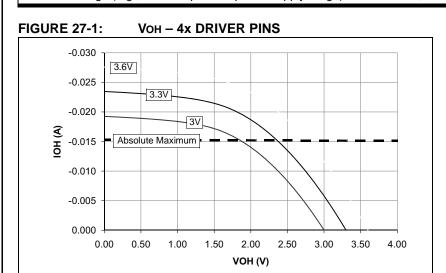

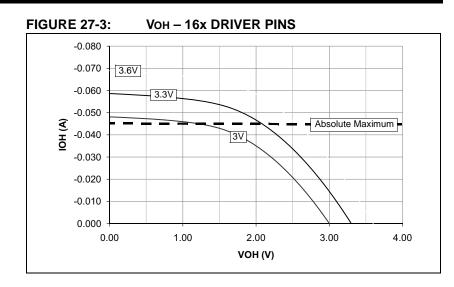

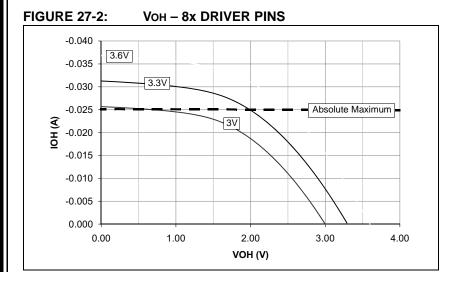

#### DC AND AC DEVICE CHARACTERISTICS GRAPHS 27.0

The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes Note: only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

dsPlC33FJ06GS101/X02 and dsPlC33FJ16GSX02/X04

#### 28.1 Package Marking Information (Continued)

28-Lead UQFN

#### Example

44-Lead QFN

Example

44-Lead TQFP

Example

44-Lead VTLA (TLA)

Example

#### Revision C and D (March 2009)

This revision includes minor typographical and formatting changes throughout the data sheet text.

Global changes include:

- Changed all instances of OSCI to OSC1 and OSCO to OSC2

- Changed all instances of PGCx/EMUCx and PGDx/EMUDx (where x = 1, 2, or 3) to PGECx and PGEDx

- Changed all instances of VDDCORE and VDDCORE/ VCAP to VCAP/VDDCORE

Other major changes are referenced by their respective section in the following table.

TABLE A-2: MAJOR SECTION UPDATES

| Section Name                                                                              | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit Digital<br>Signal Controllers"                                  | Added "Application Examples" to list of features  Updated all pin diagrams to denote the pin voltage tolerance (see "Pin Diagrams").  Added Note 2 to the 28-Pin QFN-S and 44-Pin QFN pin diagrams, which references pin connections to Vss.                                                                                                                                                                                                                |

| Section 1.0 "Device Overview"                                                             | Added ACMP1-ACMP4 pin names and Peripheral Pin Select capability column to Pinout I/O Descriptions (see Table 1-1).                                                                                                                                                                                                                                                                                                                                         |

| Section 2.0 "Guidelines for Getting<br>Started with 16-bit Digital Signal<br>Controllers" | Added new section to the data sheet that provides guidelines on getting started with 16-bit Digital Signal Controllers.                                                                                                                                                                                                                                                                                                                                     |

| Section 3.0 "CPU"                                                                         | Updated CPU Core Block Diagram with a connection from the DSP Engine to the Y Data Bus (see Figure 3-1).  Vertically extended the X and Y Data Bus lines in the DSP Engine Block Diagram (see Figure 3-3).                                                                                                                                                                                                                                                  |

| Section 4.0 "Memory Organization"                                                         | Updated Reset value for ADCON in Table 4-25.  Removed reference to dsPIC33FJ06GS102 devices in the PMD Register Map and updated bit definitions for PMD1 and PMD6, and removed PMD7 (see Table 4-43).  Added a new PMD Register Map, which references dsPIC33FJ06GS102 devices (see Table 4-44).  Updated RAM stack address and SPLIM values in the third paragraph of Section 4.2.6 "Software Stack"  Removed Section 4.2.7 "Data Ram Protection Feature". |

| Section 5.0 "Flash Program<br>Memory"                                                     | Updated <b>Section 5.3 "Programming Operations"</b> with programming time formula.                                                                                                                                                                                                                                                                                                                                                                          |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2008-2014, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-63276-216-0

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.