#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| dsPIC | C33FJ06GS101/X02 AND dsPIC33FJ16GSX02/X04 Product Families            | 2     |

|-------|-----------------------------------------------------------------------|-------|

| 1.0   | Device Overview                                                       | 17    |

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers | 21    |

| 3.0   | CPU                                                                   |       |

| 4.0   | Memory Organization                                                   | 43    |

| 5.0   | Flash Program Memory                                                  | 83    |

| 6.0   | Resets                                                                | 89    |

| 7.0   | Interrupt Controller                                                  | 97    |

| 8.0   | Oscillator Configuration                                              | . 135 |

| 9.0   | Power-Saving Features                                                 | . 147 |

| 10.0  | I/O Ports                                                             | . 155 |

| 11.0  | Timer1                                                                | . 183 |

| 12.0  | Timer2/3 Features                                                     | . 185 |

| 13.0  | Input Capture                                                         | . 191 |

| 14.0  | Output Compare                                                        | . 193 |

| 15.0  | High-Speed PWM                                                        |       |

| 16.0  |                                                                       |       |

| 17.0  | Inter-Integrated Circuit (I <sup>2</sup> C <sup>™</sup> )             |       |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)                    | . 233 |

| 19.0  | High-Speed 10-bit Analog-to-Digital Converter (ADC)                   | . 239 |

| 20.0  | High-Speed Analog Comparator                                          |       |

| 21.0  | Special Features                                                      | . 267 |

| 22.0  | Instruction Set Summary                                               | . 275 |

| 23.0  | Development Support                                                   |       |

| 24.0  | Electrical Characteristics                                            |       |

| 25.0  | High-Temperature Electrical Characteristics                           |       |

| 26.0  | 50 MIPS Electrical Characteristics                                    |       |

|       | DC and AC Device Characteristics Graphs                               |       |

| 28.0  | Packaging Information                                                 | . 351 |

|       | /icrochip Web Site                                                    |       |

| Custo | omer Change Notification Service                                      | . 393 |

| Custo | omer Support                                                          | . 393 |

| Produ | uct Identification System                                             | . 395 |

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0          | All<br>Resets |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|----------------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | —        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | —              | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     | _        | _        | _       | _        | _        | —        | _        | _        | —        | _        | —       | INT2EP   | INT1EP   | INT0EP         | 0000          |

| IFS0         | 0084        | _       | _        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | _        | T1IF    | OC1IF    | IC1IF    | INTOIF         | 0000          |

| IFS1         | 0086        | _       | _        | INT2IF   | _        | _       | _        | _        | —        | _        | _        | _        | INT1IF   | CNIF    | AC1IF    | MI2C1IF  | SI2C1IF        | 0000          |

| IFS3         | 008A        | _       | _        | _        | _        | _       | _        | PSEMIF   | —        | _        | _        | —        | _        | —       | _        | _        | _              | 0000          |

| IFS4         | 008C        |         | _        | —        | _        | _       |          |          |          |          |          | _        | _        | _       | _        | U1EIF    | _              | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF   | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       |          | _        | _              | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | _        | -       | _        | AC4IF    | AC3IF    | AC2IF    | _        | —        | —        | _       | _        | PWM4IF   | PWM3IF         | 0000          |

| IFS7         | 0092        | _       | -        | _        | _        | -       | _        | —        | —        | _        | _        | —        | ADCP6IF  | ADCP5IF | ADCP4IF  | ADCP3IF  | ADCP2IF        | 0000          |

| IEC0         | 0094        | _       | -        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | —        | T1IE    | OC1IE    | IC1IE    | INT0IE         | 0000          |

| IEC1         | 0096        | _       | -        | INT2IE   | _        | -       | _        | —        | —        | _        | _        | —        | INT1IE   | CNIE    | AC1IE    | MI2C1IE  | SI2C1IE        | 0000          |

| IEC3         | 009A        | _       | -        | —        | _        | -       | _        | PSEMIE   | _        | _        | _        | —        | —        | _       | _        |          | -              | 0000          |

| IEC4         | 009C        | _       | -        | _        | _        | -       | _        | —        | —        | _        | _        | —        | —        | _       | _        | U1EIE    | -              | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE   | —        | _        | _       | _        | —        | —        | —        | _        | —        | —        | _       | _        | -        | _              | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  | _        | _        | _       | _        | AC4IE    | AC3IE    | AC2IE    | _        | _        | _        | _       | _        | PWM4IE   | <b>PWM3IE</b>  | 0000          |

| IEC7         | 00A2        | _       | _        | _        | _        | _       | _        | _        | _        | _        | _        | _        | ADCP6IE  | ADCP5IE | ADCP4IE  | ADCP3IE  | ADCP2IE        | 0000          |

| IPC0         | 00A4        | _       | T1IP2    | T1IP1    | T1IP0    | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0   | _       | INT0IP2  | INT0IP1  | INT0IP2        | 4444          |

| IPC1         | 00A6        | _       | T2IP2    | T2IP1    | T2IP0    | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0   | _       | _        | _        | _              | 4440          |

| IPC2         | 00A8        | _       | U1RXIP2  | U1RXIP1  | U1RXIP0  | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 | _       | T3IP2    | T3IP1    | T3IP0          | 4444          |

| IPC3         | 00AA        | _       | _        | —        | _        | -       | _        | —        | —        |          | ADIP2    | ADIP1    | ADIP0    | _       | U1TXIP2  | U1TXIP1  | U1TXIP0        | 0044          |

| IPC4         | 00AC        | _       | CNIP2    | CNIP1    | CNIP0    | -       | AC1IP2   | AC1IP1   | AC1IP0   | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0       | 4444          |

| IPC5         | 00AE        | _       | _        | —        | _        | -       | _        | —        | —        | _        | _        | —        | —        | _       | INT1IP2  | INT1IP1  | INT1IP0        | 0004          |

| IPC7         | 00B2        | _       | -        | _        | _        | -       | _        | —        | _        | _        | INT2IP2  | INT2IP1  | INT2IP0  | _       | _        |          | -              | 0040          |

| IPC14        | 00C0        | _       | -        | _        | _        | -       | _        | —        | _        | _        | PSEMIP2  | PSEMIP1  | PSEMIP0  | _       | _        |          | -              | 0040          |

| IPC16        | 00C4        | _       | -        | _        | _        | -       | _        | —        | _        | _        | U1EIP2   | U1EIP1   | U1EIP0   | _       | _        |          | -              | 0040          |

| IPC23        | 00D2        | _       | PWM2IP2  | PWM2IP1  | PWM2IP0  | _       | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | _        | _        | _        | _       | _        | _        | _              | 4400          |

| IPC24        | 00D4        | _       | —        | —        | —        | —       | —        | _        | _        | _        | PWM4IP2  | PWM4IP1  | PWM4IP0  | _       | PWM3IP2  | PWM3IP1  | PWM3IP0        | 0044          |

| IPC25        | 00D6        | _       | AC2IP2   | AC2IP1   | AC2IP0   | _       | _        | _        | _        | _        | _        | _        | _        | _       | _        | —        | —              | 4000          |

| IPC26        | 00D8        | _       | _        | —        | _        | _       | _        | _        | _        | _        | AC4IP2   | AC4IP1   | AC4IP0   | _       | AC3IP2   | AC3IP1   | AC3IP0         | 0440          |

| IPC27        | 00DA        | _       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | _       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _        | _        | _        | _        | _       | _        | _        | _              | 4400          |

| IPC28        | 00DC        | _       | ADCP5IP2 | ADCP5IP1 | ADCP5IP0 | _       | ADCP4IP2 | ADCP4IP1 | ADCP4IP0 | _        | ADCP3IP2 | ADCP3IP1 | ADCP3IP0 | _       | ADCP2IP2 | ADCP2IP1 | ADCP2IP0       | 4444          |

| IPC29        | 00DE        | _       | _        | _        | _        | _       |          | _        | _        | _        | _        | _        | —        | _       | ADCP6IP2 | ADCP6IP1 | ADCP6IP0       | 0004          |

| INTTREG      |             | _       | _        | _        | _        | ILR3    | ILR2     | ILR1     | ILR0     | _        | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | <b>VECNUM0</b> |               |

# TABLE 4-10: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ16GS504 DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

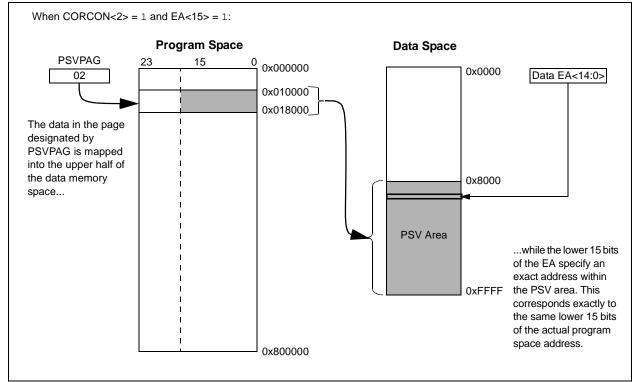

## 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and Program Space Visibility (PSV) is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 8000h and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during Table Reads/Writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

# FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

# 6.1 System Reset

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 families of devices have two types of Reset:

- Cold Reset

- Warm Reset

A Cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a Cold Reset, the FNOSCx Configuration bits in the FOSC Configuration register select the device clock source. A Warm Reset is the result of all the other Reset sources, including the RESET instruction. On Warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection (COSC<2:0>) bits in the Oscillator Control (OSCCON<14:12>) register.

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is detailed in Figure 6-2.

| Oscillator Mode           | Oscillator<br>Startup Delay | Oscillator<br>Startup Timer | PLL Lock Time        | Total Delay                             |

|---------------------------|-----------------------------|-----------------------------|----------------------|-----------------------------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd <sup>(1)</sup>        | _                           | _                    | Toscd <sup>(1)</sup>                    |

| FRCPLL                    | Toscd <sup>(1)</sup>        | _                           | ТLОСК <sup>(3)</sup> | Toscd + Tlock <sup>(1,3)</sup>          |

| XT                        | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| HS                        | Toscd(1)                    | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| EC                        | —                           | —                           | —                    | —                                       |

| XTPLL                     | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | ТLОСК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| HSPLL                     | Toscd(1)                    | Tost <sup>(2)</sup>         | ТLOCК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| ECPLL                     | —                           | —                           | ТLОСК <sup>(3)</sup> | TLOCK <sup>(3)</sup>                    |

| LPRC                      | Toscd <sup>(1)</sup>        | _                           | —                    | Toscd <sup>(1)</sup>                    |

# TABLE 6-1:OSCILLATOR DELAY

**Note 1:** TOSCD = Oscillator start-up delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal) if PLL is enabled.

| REGISTER 7-26: IPC14: INTERRUPT PRIORITY CONTROL REGISTER | 14 |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | PSEMIP2 | PSEMIP1 | PSEMIP0 | —   | —   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

|            | l   | - |  |

|------------|-----|---|--|

| <b>e</b> 0 | ena |   |  |

|            |     |   |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-7<br>bit 6-4 | Unimplemented: Read as '0'<br>PSEMIP<2:0>: PWM Special Event Match Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | •<br>001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                                                 |

Unimplemented: Read as '0' bit 3-0

# REGISTER 7-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0              | U-0    | U-0              | U-0    | U-0              | U-0              | U-0                | U-0   |  |

|------------------|--------|------------------|--------|------------------|------------------|--------------------|-------|--|

| —                | —      | —                | _      | —                | —                | —                  | —     |  |

| bit 15           |        |                  |        |                  | •                |                    | bit 8 |  |

|                  |        |                  |        |                  |                  |                    |       |  |

| U-0              | R/W-1  | R/W-0            | R/W-0  | U-0              | U-0              | U-0                | U-0   |  |

| —                | U1EIP2 | U1EIP1           | U1EIP0 | —                | —                | —                  | —     |  |

| bit 7            |        |                  |        |                  |                  |                    | bit 0 |  |

|                  |        |                  |        |                  |                  |                    |       |  |

| Legend:          |        |                  |        |                  |                  |                    |       |  |

| R = Readable bit |        | W = Writable     | bit    | U = Unimpler     | mented bit, read | l as '0'           |       |  |

| -n = Value at F  | POR    | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

| bit 15-7 | Unimplemented: Read as '0' |  |

|----------|----------------------------|--|

| bit 6-4 | <b>U1EIP&lt;2:0&gt;:</b> UART1 Error Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |

|---------|----------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                          |

|         | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                        |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                 |

|                             | • = • • • • • • • • • • • • • • • • • •                                                                                                 |                                                                  |                                                                                  |                   |                 |                 |       |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------|-----------------|-----------------|-------|

| U-0                         | U-0                                                                                                                                     | U-0                                                              | U-0                                                                              | U-0               | U-0             | R/W-0           | R/W-0 |

| —                           | —                                                                                                                                       | —                                                                | —                                                                                | —                 | _               | IC2MD           | IC1MD |

| it 15                       |                                                                                                                                         |                                                                  |                                                                                  |                   |                 |                 | bit 8 |

| U-0                         | U-0                                                                                                                                     | U-0                                                              | U-0                                                                              | U-0               | U-0             | R/W-0           | R/W-0 |

| _                           | —                                                                                                                                       | —                                                                |                                                                                  | _                 |                 | OC2MD           | OC1MD |

| oit 7                       | ·                                                                                                                                       |                                                                  |                                                                                  |                   |                 |                 | bit C |

| _egend:                     |                                                                                                                                         |                                                                  |                                                                                  |                   |                 |                 |       |

| R = Readabl                 | e bit                                                                                                                                   | W = Writable                                                     | bit                                                                              | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at               | POR                                                                                                                                     | '1' = Bit is set                                                 |                                                                                  | '0' = Bit is clea | ared            | x = Bit is unkn | iown  |

| bit 15-10<br>bit 9<br>bit 8 | <b>IC2MD</b> : Input<br>1 = Input Cap<br>0 = Input Cap<br><b>IC1MD</b> : Input<br>1 = Input Cap                                         | ture 2 module<br>ture 2 module<br>Capture 1 Moo<br>ture 1 module | dule Disable bit<br>is disabled<br>is enabled<br>dule Disable bit<br>is disabled |                   |                 |                 |       |

| bit 7-2                     | 0 = Input Capture 1 module is enabled<br>Unimplemented: Read as '0'                                                                     |                                                                  |                                                                                  |                   |                 |                 |       |

| bit 1                       | <b>OC2MD</b> : Output Compare 2 Module Disable bit<br>1 = Output Compare 2 module is disabled<br>0 = Output Compare 2 module is enabled |                                                                  |                                                                                  |                   |                 |                 |       |

| bit 0                       | 1 = Output Co                                                                                                                           | out Compare 1<br>ompare 1 modu<br>ompare 1 modu                  |                                                                                  | e bit             |                 |                 |       |

# REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

# 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70193) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

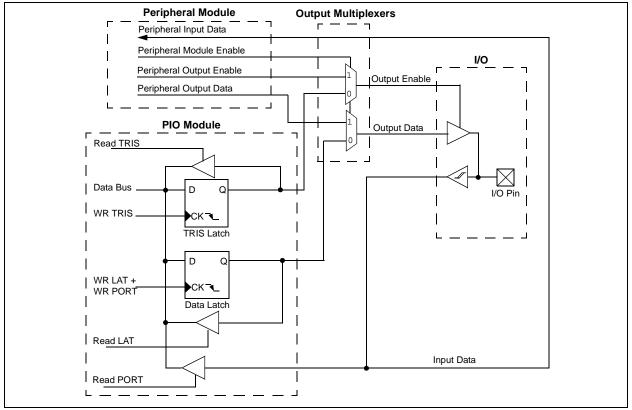

# 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

# FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

© 2008-2014 Microchip Technology Inc.

| U-0          | U-0                                                          | R/W-1                                                                                        | R/W-1       | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

|--------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------|------------------|------------------|-----------------|--------|

| _            | _                                                            | FLT5R5                                                                                       | FLT5R4      | FLT5R3           | FLT5R2           | FLT5R1          | FLT5R0 |

| bit 15       |                                                              |                                                                                              |             |                  |                  |                 | bit    |

|              |                                                              |                                                                                              |             |                  |                  |                 |        |

| U-0          | U-0                                                          | R/W-1                                                                                        | R/W-1       | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

| —            | —                                                            | FLT4R5                                                                                       | FLT4R4      | FLT4R3           | FLT4R2           | FLT4R1          | FLT4R0 |

| bit 7        |                                                              |                                                                                              |             |                  |                  |                 | bit    |

| Legend:      |                                                              |                                                                                              |             |                  |                  |                 |        |

| R = Readab   | le bit                                                       | W = Writable                                                                                 | bit         | U = Unimpler     | nented bit, read | l as '0'        |        |

| -n = Value a | t POR                                                        | '1' = Bit is set                                                                             |             | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15-14    | Unimplemen                                                   | ted: Read as '                                                                               | כ'          |                  |                  |                 |        |

|              | 100010 = Inp<br>100001 = Inp                                 | t tied to RP35<br>but tied to RP34<br>but tied to RP33<br>but tied to RP32<br>t tied to RP32 | 3           |                  |                  |                 |        |

| bit 7-6      | Unimplemen                                                   | ted: Read as '                                                                               | י'          |                  |                  |                 |        |

| bit 5-0      | 111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100001 = Inp | •                                                                                            | ;<br>;<br>; | FLT4) to the Co  | orresponding R   | Pn Pin bits     |        |

# REGISTER 10-11: RPINR31: PERIPHERAL PIN SELECT INPUT REGISTER 31

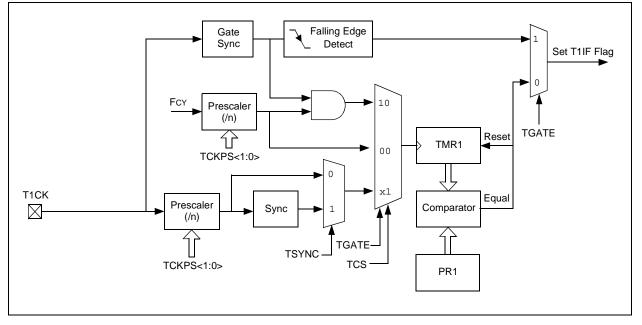

# 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as a time counter for the Real-Time Clock (RTC), or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low-power 32 kHz crystal oscillator available on the device

- Can be operated in Asynchronous Counter mode from an external clock source

- Optionally, the external clock input (T1CK) can be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 11-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

The timer control bit settings for different operating modes are given in the Table 11-1.

| TABLE 11-1: TIN | ER MODE SETTINGS |

|-----------------|------------------|

|-----------------|------------------|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | x     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

## FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| R/W-0         | U-0                                                                                                 | R/W-0                                                                                                            | U-0           | U-0               | U-0            | U-0              | U-0 |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------|-------------------|----------------|------------------|-----|--|--|--|--|

| TON           | _                                                                                                   | TSIDL                                                                                                            | _             | —                 | _              | —                | _   |  |  |  |  |

| bit 15        |                                                                                                     |                                                                                                                  |               |                   |                |                  | bit |  |  |  |  |

|               |                                                                                                     |                                                                                                                  |               | <b>D</b> 0.44 a   |                |                  |     |  |  |  |  |

| U-0           | R/W-0                                                                                               | R/W-0                                                                                                            | R/W-0         | R/W-0             | U-0            | R/W-0            | U-0 |  |  |  |  |

| —<br>L:1 7    | TGATE                                                                                               | TCKPS1                                                                                                           | TCKPS0        | T32               | _              | TCS              |     |  |  |  |  |

| bit 7         |                                                                                                     |                                                                                                                  |               |                   |                |                  | bit |  |  |  |  |

| Legend:       |                                                                                                     |                                                                                                                  |               |                   |                |                  |     |  |  |  |  |

| R = Readable  | e bit                                                                                               | W = Writable                                                                                                     | bit           | U = Unimplem      | ented bit, rea | d as '0'         |     |  |  |  |  |

| -n = Value at | POR                                                                                                 | '1' = Bit is set                                                                                                 |               | '0' = Bit is clea | ared           | x = Bit is unkne | own |  |  |  |  |

|               |                                                                                                     |                                                                                                                  |               |                   |                |                  |     |  |  |  |  |

| bit 15        | TON: Timerx                                                                                         |                                                                                                                  |               |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     | 1 (in 32-Bit Tim<br>bit TMRx:TMR                                                                                 |               |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     | bit TMRx:TMR                                                                                                     | • •           |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     | 0 (in 16-Bit Tim                                                                                                 |               |                   |                |                  |     |  |  |  |  |

|               | 1 = Starts 16-                                                                                      |                                                                                                                  |               |                   |                |                  |     |  |  |  |  |

|               | 0 = Stops 16-                                                                                       |                                                                                                                  |               |                   |                |                  |     |  |  |  |  |

| bit 14        | -                                                                                                   | ted: Read as '                                                                                                   |               |                   |                |                  |     |  |  |  |  |

| bit 13        |                                                                                                     | <b>TSIDL:</b> Timerx Stop in Idle Mode bit<br>1 = Discontinues timer operation when device enters Idle mode      |               |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     | ues timer operations timer operations timer operations to the second second second second second second second s |               |                   | mode           |                  |     |  |  |  |  |

| bit 12-7      | Unimplemen                                                                                          | ted: Read as '                                                                                                   | 0'            |                   |                |                  |     |  |  |  |  |

| bit 6         | TGATE: Time                                                                                         | erx Gated Time                                                                                                   | Accumulation  | Enable bit        |                |                  |     |  |  |  |  |

|               |                                                                                                     | $\frac{\text{When TCS} = 1}{\text{This bit is ignored.}}$                                                        |               |                   |                |                  |     |  |  |  |  |

|               | When TCS = 0:                                                                                       |                                                                                                                  |               |                   |                |                  |     |  |  |  |  |

|               | <ol> <li>Gated time accumulation is enabled</li> <li>Gated time accumulation is disabled</li> </ol> |                                                                                                                  |               |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     |                                                                                                                  |               | 0.1               |                |                  |     |  |  |  |  |

| bit 5-4       |                                                                                                     | : Timerx Input                                                                                                   | Clock Prescal | e Select bits     |                |                  |     |  |  |  |  |

|               | 11 = 1:256 pr<br>10 = 1:64 pre                                                                      |                                                                                                                  |               |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     | 10 = 1:64 prescale value<br>01 = 1:8 prescale value                                                              |               |                   |                |                  |     |  |  |  |  |

|               | 00 = 1:1 pres                                                                                       | cale value                                                                                                       |               |                   |                |                  |     |  |  |  |  |

| bit 3         | T32: 32-Bit T                                                                                       | imerx Mode Se                                                                                                    | elect bit     |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     | d TMRy form a<br>d TMRy form a                                                                                   |               | oit timer         |                |                  |     |  |  |  |  |

| bit 2         | Unimplemen                                                                                          | ted: Read as '                                                                                                   | 0'            |                   |                |                  |     |  |  |  |  |

| bit 1         | TCS: Timerx                                                                                         | Clock Source S                                                                                                   | Select bit    |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     | clock from TxC<br>lock (Fosc/2)                                                                                  | K pin         |                   |                |                  |     |  |  |  |  |

|               |                                                                                                     | 1001 (1 000/2)                                                                                                   |               |                   |                |                  |     |  |  |  |  |

# **REGISTER 12-1:** TxCON: TIMERx CONTROL REGISTER (x = 2)

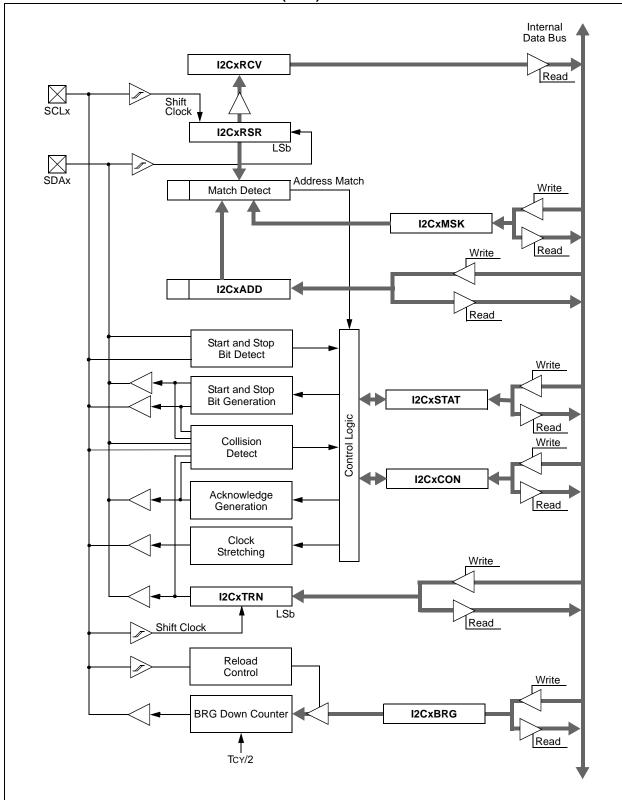

FIGURE 17-1: I2Cx BLOCK DIAGRAM (x = 1)

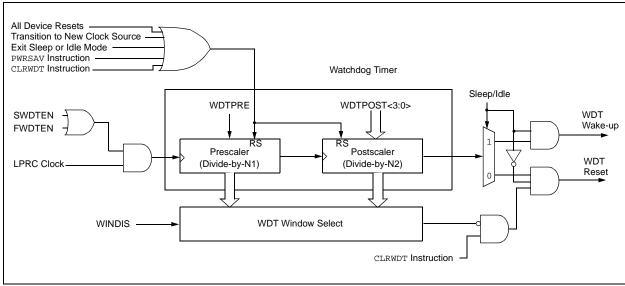

# 21.4 Watchdog Timer (WDT)

For the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

# 21.4.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC<2:0> bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

## FIGURE 21-2: WDT BLOCK DIAGRAM

## 21.4.2 SLEEP AND IDLE MODES

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP bit (RCON<3>) or IDLE bit (RCON<2>) will need to be cleared in software after the device wakes up.

## 21.4.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

# 21.8 Code Protection and CodeGuard<sup>™</sup> Security

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices offer the intermediate implementation of CodeGuard<sup>™</sup> Security. CodeGuard Security enables multiple parties to securely share resources (memory, interrupts and peripherals) on a single chip. This feature helps protect individual Intellectual Property (IP) in collaborative system designs.

When coupled with software encryption libraries, Code-Guard<sup>™</sup> Security can be used to securely update Flash even when multiple IPs reside on a single chip.

# TABLE 21-3:CODE FLASH SECURITY<br/>SEGMENT SIZES FOR<br/>6-Kbyte DEVICES

| Configuration Bits     |              |                                                                           |

|------------------------|--------------|---------------------------------------------------------------------------|

|                        | VS = 256 IW  | 000000h<br>0001FEh                                                        |

| BSS<2:0> = x11<br>0K   | GS = 1792 IW | 000200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h<br>000FFEh<br>000FFEh |

|                        |              | 002BFEh                                                                   |

|                        | VS = 256 IW  | 000000h<br>0001FEh                                                        |

|                        | BS = 256 IW  | 000200h<br>0003FEh                                                        |

| BSS<2:0> = x10<br>256  | GS = 1536 IW | 000400h<br>0007FEh<br>000800h<br>000FFEh<br>001000h                       |

|                        |              | 002BFEh                                                                   |

|                        | VS = 256 IW  | 000000h<br>00015Eh                                                        |

| BSS<2:0> = x01         | BS = 768 IW  | 000200h<br>0003FEh<br>000400h<br>0007FEh                                  |

| 768                    | GS = 1024 IW | 000800h<br>000FFEh<br>001000h                                             |

|                        |              | 002BFEh                                                                   |

|                        | VS = 256 IW  | 000000h<br>0001FEh                                                        |

| BSS<2:0> = x00<br>1792 | BS = 1792 IW | 000200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h<br>000FFEh<br>001000h |

|                        |              | 002BFEh                                                                   |

The code protection features are controlled by the Configuration registers: FBS and FGS.

Secure segment and RAM protection is not implemented in dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices.

| Note: | Refer                                   | to     | "Co | odeGuar | Secur | ity"   |    |

|-------|-----------------------------------------|--------|-----|---------|-------|--------|----|

|       | (DS701                                  | 199)   | for | further | infor | mation | on |

|       | CodeGuard Security usage, configuration |        |     |         |       |        |    |

|       | and op                                  | eratio | on. |         |       |        |    |

## TABLE 21-4: CODE FLASH SECURITY SEGMENT SIZES FOR 16-Kbyte DEVICES

| Configuration Bits          |              |                                                                                        |

|-----------------------------|--------------|----------------------------------------------------------------------------------------|

|                             | VS = 256 IW  | 000000h<br>0001FEh                                                                     |

| BSS<2:0> = x11<br>0K        | GS = 5376 IW | 0002200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h<br>000FFEh<br>0006FFEh<br>001000h |

|                             |              | 002BFEh                                                                                |

|                             | VS = 256 IW  | 000000h<br>0001FEh<br>000200h                                                          |

| BSS<2:0> = x10              | BS = 256 IW  | 0003FEh<br>000400h                                                                     |

| 256                         |              | 0007FEh<br>000800h<br>000FFEh<br>001000h                                               |

|                             | GS = 5120 IW | 002BFEh                                                                                |

|                             | VS = 256 IW  | 000000h<br>0001FEh                                                                     |

| <b>BSS&lt;2:0&gt; =</b> x01 | BS = 768 IW  | 000200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h                                    |

| 768                         |              | 000800h<br>000FFEh<br>001000h                                                          |

|                             | GS = 4608 IW | 002BFEh                                                                                |

|                             | VS = 256 IW  | 000000h<br>0001FEh                                                                     |

| BSS<2:0> = x00              | BS = 1792 IW | 000200h<br>0003FEh<br>000400h<br>0007FEh<br>000800h                                    |

|                             | GS = 3584 IW | 000FFEh<br>001000h<br>002BFEh                                                          |

# 23.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 23.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 23.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 23.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 23.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# 24.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                  | 40°C to +125°C       |

|---------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                             | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                              | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>  | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss, when VDD $\geq 3.0 V^{(3)}$ | -0.3V to +5.6V       |

| Voltage on any 5V tolerant pin with respect to Vss, when VDD < $3.0V^{(3)}$     | 0.3V to (VDD + 0.3V) |

| Maximum current out of Vss pin                                                  |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                     |                      |

| Maximum current sourced/sunk by any 4x I/O pin                                  |                      |

| Maximum current sourced/sunk by any 8x I/O pin                                  |                      |

| Maximum current sourced/sunk by any 16x I/O pin                                 |                      |

| Maximum current sunk by all ports                                               |                      |

| Maximum current sourced by all ports <sup>(2)</sup>                             | 200mA                |

**Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 24-2).

- 3: See the "Pin Diagrams" section for 5V tolerant pins.

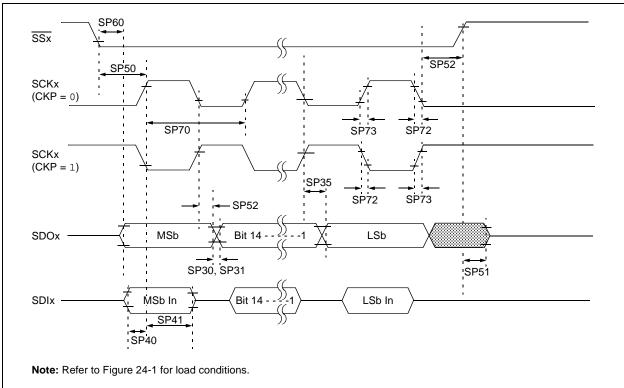

# TABLE 24-34:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       |                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$        |              |                    |     |       |                                      |

|--------------|-----------------------|--------------------------------------------------------------|--------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min          | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70         | TscP                  | Maximum SCKx Input<br>Frequency                              | —            | —                  | 15  | MHz   | See Note 3                           |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —            |                    |     | ns    | See Parameter DO32 and Note 4        |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —            | —                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | —            | _                  | —   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —            | _                  | —   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —            | 6                  | 20  | ns    |                                      |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30           | —                  | _   | ns    |                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30           | —                  | _   | ns    |                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30           | —                  | _   | ns    |                                      |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120          | _                  | _   | ns    |                                      |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>        | 10           | —                  | 50  | ns    |                                      |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40 | —                  | —   | ns    | See Note 4                           |

| SP60         | TssL2doV              | SDOx Data Output Valid after                                 | —            | —                  | 50  | ns    |                                      |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

# FIGURE 24-16: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| AC CHAR      | AC CHARACTERISTICSStandard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                                            |    |       |            | -  |            |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----|-------|------------|----|------------|

| Param<br>No. | Symbol                                                                                                                                                                        | Characteristic <sup>(1)</sup> Min Typ Max  |    | Units | Conditions |    |            |

| HSP35        | TscH2doV,<br>TscL2doV                                                                                                                                                         | SDOx Data Output Valid after<br>SCKx Edge  | -  | —     | 35         | ns |            |

| HSP40        | TdiV2scH,<br>TdiV2scL                                                                                                                                                         | Setup Time of SDIx Data Input to SCKx Edge | 25 | —     | —          | ns |            |

| HSP41        | TscH2diL,<br>TscL2diL                                                                                                                                                         | Hold Time of SDIx Data Input to SCKx Edge  | 25 | —     | —          | ns |            |

| HSP51        | TssH2doZ                                                                                                                                                                      | SSx ↑ to SDOx Output<br>High-Impedance     | 15 | —     | 55         | ns | See Note 2 |

# TABLE 25-11: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Assumes 50 pF load on all SPIx pins.

## TABLE 25-12: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |

| HSP35              | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               |     |     | 35  | ns    |            |  |

| HSP40              | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 25  |     |     | ns    |            |  |

| HSP41              | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 25  |     |     | ns    |            |  |

| HSP51              | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                  | 15  | —   | 55  | ns    | See Note 2 |  |

| HSP60              | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                                                                                                |     |     | 55  | ns    |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Assumes 50 pF load on all SPIx pins.

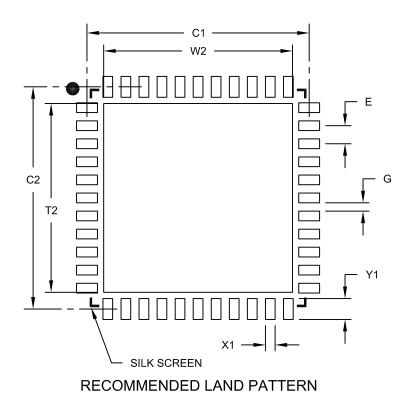

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension                  | MIN         | NOM      | MAX  |      |

| Contact Pitch              | E           | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 6.60 |

| Optional Center Pad Length | T2          |          |      | 6.60 |

| Contact Pad Spacing        | C1          |          | 8.00 |      |

| Contact Pad Spacing        | C2          |          | 8.00 |      |

| Contact Pad Width (X44)    | X1          |          |      | 0.35 |

| Contact Pad Length (X44)   | Y1          |          |      | 0.85 |

| Distance Between Pads      | G           | 0.25     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

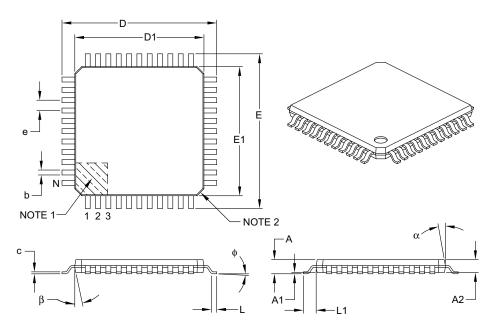

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |      |      |  |

|--------------------------|------------------|-------------|------|------|--|

|                          | Dimension Limits | MIN         | NOM  | MAX  |  |

| Number of Leads          | N                | 44          |      |      |  |

| Lead Pitch               | е                | 0.80 BSC    |      |      |  |

| Overall Height           | А                | _           | —    | 1.20 |  |

| Molded Package Thickness | A2               | 0.95        | 1.00 | 1.05 |  |

| Standoff                 | A1               | 0.05        | -    | 0.15 |  |

| Foot Length              | L                | 0.45        | 0.60 | 0.75 |  |

| Footprint                | L1               | 1.00 REF    |      |      |  |

| Foot Angle               | ¢                | 0°          | 3.5° | 7°   |  |

| Overall Width            | E                | 12.00 BSC   |      |      |  |

| Overall Length           | D                | 12.00 BSC   |      |      |  |

| Molded Package Width     | E1               | 10.00 BSC   |      |      |  |

| Molded Package Length    | D1               | 10.00 BSC   |      |      |  |

| Lead Thickness           | С                | 0.09        | -    | 0.20 |  |

| Lead Width               | b                | 0.30        | 0.37 | 0.45 |  |

| Mold Draft Angle Top     | α                | 11°         | 12°  | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°  | 13°  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.