Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502-h-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value that is sign-extended to 40 bits. Integer data is inherently represented as a signed 2's complement value, where the Most Significant bit (MSb) is defined as a sign bit. The range of an N-bit 2's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ .

- For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0.

- For a 32-bit integer, the data range is

-2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a 2's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit 2's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product that has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiply operations.

The MUL instruction can be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

## 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled using the barrel shifter prior to accumulation.

## 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side, and either true or complement data into the other input.

- In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented).

- In the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented.

The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS Register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits, 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block that controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described previously and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS Register bits support saturation and overflow:

- OA: ACCA overflowed into guard bits

- · OB: ACCB overflowed into guard bits

- SA: ACCA saturated (bit 31 overflow and saturation) or

~

or

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation)

• SB: ACCB saturated (bit 31 overflow and saturation)

ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- OAB: Logical OR of OA and OB

- SAB: Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register are set (refer to **Section 7.0 "Interrupt Controller"**). This allows the user application to take immediate action, for example, to correct system gain.

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

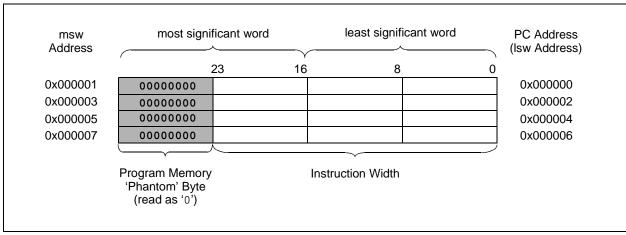

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate consider each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (see Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during the code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

#### TABLE 4-27: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15       | Bit 14 | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6          | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------------|--------|--------|----------|----------|----------|----------|----------|-------------|----------------|---------|-----------|----------|----------|----------|----------|---------------|

| ADCON        | 0300        | ADON         | —      | ADSIDL | SLOWCLK  | —        | GSWTRG   | —        | FORM     | EIE         | ORDER          | SEQSAMP | ASYNCSAMP | —        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _            | -      | —      | _        | _        |          | _        | —        | _           | _              | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _            | -      | —      | _        | _        |          | _        | —        | _           | P6RDY          | _       | _         | _        | P2RDY    | P1RDY    | PORDY    | 0000          |

| ADBASE       | 0308        | ADBASE<15:1> |        |        |          |          |          |          |          |             | —              | 0000    |           |          |          |          |          |               |

| ADCPC0       | 030A        | IRQEN1       | PEND1  | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0          | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | _            | -      | —      | _        | _        |          | _        | —        | IRQEN2      | PEND2          | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCPC3       | 0310        | _            |        | —      | _        | —        | _        | —        | —        | IRQEN6      | PEND6          | SWTRG6  | TRGSRC64  | TRGSRC63 | TRGSRC62 | TRGSRC61 | TRGSRC60 | 0000          |

| ADCBUF0      | 0320        |              |        |        |          |          |          |          | ADC E    | Data Buffer | 0              |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |              |        |        |          |          |          |          | ADC E    | Data Buffer | <sup>.</sup> 1 |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |              |        |        |          |          |          |          | ADC E    | Data Buffer | 2              |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |              |        |        |          |          |          |          | ADC E    | Data Buffer | 3              |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |              |        |        |          |          |          |          | ADC E    | Data Buffer | 4              |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |              |        |        |          |          |          |          | ADC E    | Data Buffer | 5              |         |           |          |          |          |          | xxxx          |

| ADCBUF12     | 0338        |              |        |        |          |          |          |          | ADC D    | ata Buffer  | 12             |         |           |          |          |          |          | xxxx          |

| ADCBUF13     | 033A        |              |        |        |          |          |          |          | ADC D    | Data Buffer | 13             |         |           |          |          |          |          | xxxx          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### TABLE 4-28: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ16GS402/404 DEVICES ONLY

|              | -           |              |                       |            | -           |                 |               |               |              |            |       | -       |           |          |          |          |          |               |

|--------------|-------------|--------------|-----------------------|------------|-------------|-----------------|---------------|---------------|--------------|------------|-------|---------|-----------|----------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15       | Bit 14                | Bit 13     | Bit 12      | Bit 11          | Bit 10        | Bit 9         | Bit 8        | Bit 7      | Bit 6 | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADCON        | 0300        | ADON         | —                     | ADSIDL     | SLOWCLK     | _               | GSWTRG        | _             | FORM         | EIE        | ORDER | SEQSAMP | ASYNCSAMP | -        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _            | _                     | _          | _           | —               | _             | _             | _            | PCFG7      | PCFG6 | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _            | _                     | _          | _           | —               | _             | _             | _            | _          | _     | _       | _         | P3RDY    | P2RDY    | P1RDY    | P0RDY    | 0000          |

| ADBASE       | 0308        | ADBASE<15:1> |                       |            |             |                 |               |               |              |            |       | —       | 0000      |          |          |          |          |               |

| ADCPC0       | 030A        | IRQEN1       | PEND1                 | SWTRG1     | TRGSRC14    | TRGSRC13        | TRGSRC12      | TRGSRC11      | TRGSRC10     | IRQEN0     | PEND0 | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | IRQEN3       | PEND3                 | SWTRG3     | TRGSRC34    | TRGSRC33        | TRGSRC32      | TRGSRC31      | TRGSRC30     | IRQEN2     | PEND2 | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCBUF0      | 0320        |              |                       |            |             |                 |               |               | ADC D        | ata Buffer | 0     |         |           |          |          |          |          | xxxx          |

| ADCBUF1      | 0322        |              |                       |            |             |                 |               |               | ADC D        | ata Buffer | 1     |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |              |                       |            |             |                 |               |               | ADC D        | ata Buffer | 2     |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |              |                       |            |             |                 |               |               | ADC D        | ata Buffer | 3     |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |              |                       |            |             |                 |               |               | ADC D        | ata Buffer | 4     |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |              |                       |            |             |                 |               |               | ADC D        | ata Buffer | 5     |         |           |          |          |          |          | xxxx          |

| ADCBUF6      | 032C        |              |                       |            |             |                 |               |               | ADC D        | ata Buffer | 6     |         |           |          |          |          |          | xxxx          |

| ADCBUF7      | 032E        |              | ADC Data Buffer 7 xxx |            |             |                 |               |               |              |            |       |         | xxxx      |          |          |          |          |               |

| Legend:      | x =         | unknown      | value on              | Reset, — = | unimplement | ed, read as '0' | . Reset value | s are shown i | n hexadecima | al.        |       |         |           |          |          |          |          |               |

#### 7.4 Interrupt Setup Procedures

#### 7.4.1 INITIALIZATION

Complete the following steps to configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |          |          |           |  |  |  |  |  |  |  |

|-------|-------------------------------------------|----------|----------|-----------|--|--|--|--|--|--|--|

|       | initialized s                             | uch that | all user | interrupt |  |  |  |  |  |  |  |

|       | sources are assigned to Priority Level 4. |          |          |           |  |  |  |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

#### 7.4.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development toolsuite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, program will re-enter the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

The following steps outline the procedure to disable all user interrupts:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value 0xE0 with SRL.

To enable user interrupts, the POP instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of 7 |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|--|--|--|

|       | or lower can be disabled. Trap sources          |  |  |  |  |  |  |  |  |

|       | (level 8-level 15) cannot be disabled.          |  |  |  |  |  |  |  |  |

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

### dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| REGISTER 8      | -2: CLKDI                                                    | V: CLOCK D               | IVISOR REC                           | SISTER <sup>(1)</sup>                 |                  |                    |              |

|-----------------|--------------------------------------------------------------|--------------------------|--------------------------------------|---------------------------------------|------------------|--------------------|--------------|

| R/W-0           | R/W-0                                                        | R/W-1                    | R/W-1                                | R/W-0                                 | R/W-0            | R/W-0              | R/W-0        |

| ROI             | DOZE2                                                        | DOZE1                    | DOZE0                                | DOZEN <sup>(2)</sup>                  | FRCDIV2          | FRCDIV1            | FRCDIVC      |

| bit 15          |                                                              |                          |                                      |                                       |                  |                    | bit          |

| R/W-0           | R/W-1                                                        | U-0                      | R/W-0                                | R/W-0                                 | R/W-0            | R/W-0              | R/W-0        |

| PLLPOST1        | PLLPOST0                                                     | _                        | PLLPRE4                              | PLLPRE3                               | PLLPRE2          | PLLPRE1            | PLLPRE       |

| bit 7           |                                                              |                          |                                      |                                       |                  |                    | bit          |

| Legend:         |                                                              |                          |                                      |                                       |                  |                    |              |

| R = Readable    | hit                                                          | W = Writable             | hit                                  |                                       | antad hit raa    |                    |              |

|                 |                                                              |                          |                                      | -                                     | nented bit, read |                    |              |

| -n = Value at F | <u>'OR</u>                                                   | '1' = Bit is se          | [                                    | '0' = Bit is clea                     | ared             | x = Bit is unkr    | IOWN         |

| bit 15          | ROI: Recover                                                 | on Interrupt b           | it                                   |                                       |                  |                    |              |

|                 |                                                              | -                        |                                      | d the processo                        | r clock/periphe  | ral clock ratio is | s set to 1:1 |

|                 |                                                              |                          | t on the DOZE                        |                                       |                  |                    |              |

| bit 14-12       | DOZE<2:0>:                                                   | Processor Clo            | ck Reduction S                       | Select bits                           |                  |                    |              |

|                 | 111 = Fcy/12                                                 | 8                        |                                      |                                       |                  |                    |              |

|                 | 110 = FCY/64                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 101 = FCY/32                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 100 = FCY/16                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 011 = FCY/8 (<br>010 = FCY/4                                 | delault)                 |                                      |                                       |                  |                    |              |

|                 | 001 = FCY/2                                                  |                          |                                      |                                       |                  |                    |              |

|                 | 000 = Fcy/1                                                  |                          |                                      |                                       |                  |                    |              |

| bit 11          | DOZEN: Doze                                                  | e Mode Enable            | e bit <sup>(2)</sup>                 |                                       |                  |                    |              |

|                 |                                                              |                          | ies the ratio be<br>eral clock ratio |                                       | pheral clocks a  | and the process    | or clocks    |

| bit 10-8        | FRCDIV<2:0>                                                  | : Internal Fas           | t RC Oscillator                      | Postscaler bits                       | 6                |                    |              |

|                 | 111 = FRC di<br>110 = FRC di<br>101 = FRC di<br>100 = FRC di | vide-by-64<br>vide-by-32 |                                      |                                       |                  |                    |              |

|                 | 011 = FRC di                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 010 = FRC di                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 001 = FRC di                                                 | •                        |                                      |                                       |                  |                    |              |

| h.H. 7. C       | 000 = FRC di                                                 | <b>,</b> (               | ,                                    | Calaat hita (al                       |                  |                    | eeler)       |

| bit 7-6         |                                                              |                          | Output Divider                       | Select bits (all                      | so denoted as    | 'N2', PLL posts    | caler)       |

|                 | 11 = Output/8<br>10 = Reserve                                |                          |                                      |                                       |                  |                    |              |

|                 | 01 = Output/4                                                |                          |                                      |                                       |                  |                    |              |

|                 | 00 = Output/2                                                | •                        |                                      |                                       |                  |                    |              |

| bit 5           | Unimplement                                                  | t <b>ed:</b> Read as     | 0'                                   |                                       |                  |                    |              |

| bit 4-0         | PLLPRE<4:0                                                   | >: PLL Phase             | Detector Input                       | Divider bits (a                       | so denoted as    | 'N1', PLL prese    | caler)       |

|                 | 11111 <b>= I</b> npu                                         |                          |                                      | , , , , , , , , , , , , , , , , , , , |                  | · •                | ,            |

|                 | •                                                            |                          |                                      |                                       |                  |                    |              |

|                 | •                                                            |                          |                                      |                                       |                  |                    |              |

|                 | •                                                            | 10                       |                                      |                                       |                  |                    |              |

|                 | 00001 = Inpu                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 00000 = Inpu                                                 | t/2 (default)            |                                      |                                       |                  |                    |              |

#### CIGTED 0 2

Note 1: This register is reset only on a Power-on Reset (POR).

2: This bit is cleared when the ROI bit is set and an interrupt occurs.

## dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| U-0          | U-0           | U-0                              | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0    |

|--------------|---------------|----------------------------------|-----------------|-------------------|-----------------|-----------------|----------|

|              | —             | —                                |                 | CMP4MD            | CMP3MD          | CMP2MD          | CMP1MD   |

| bit 15       |               |                                  |                 |                   |                 |                 | bit      |

| U-0          | U-0           | U-0                              | U-0             | U-0               | U-0             | U-0             | U-0      |

| _            |               | <u> </u>                         | <u> </u>        | <u> </u>          | _               | <u> </u>        | <u> </u> |

| bit 7        |               |                                  |                 |                   |                 |                 | bit (    |

|              |               |                                  |                 |                   |                 |                 |          |

| Legend:      |               |                                  |                 |                   |                 |                 |          |

| R = Readab   | le bit        | W = Writable I                   | oit             | U = Unimplem      | ented bit, read | l as '0'        |          |

| -n = Value a | t POR         | '1' = Bit is set                 |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown     |

|              |               |                                  |                 |                   |                 |                 |          |

| bit 15-12    | Unimplemen    | ted: Read as '0                  | )'              |                   |                 |                 |          |

| bit 11       | CMP4MD: An    | alog Comparat                    | or 4 Module D   | isable bit        |                 |                 |          |

|              | 0             | omparator 4 mo                   |                 |                   |                 |                 |          |

|              | •             | omparator 4 mo                   |                 |                   |                 |                 |          |

| bit 10       |               | alog Comparat                    |                 |                   |                 |                 |          |

|              | Ų             | omparator 3 mo<br>omparator 3 mo |                 |                   |                 |                 |          |

| bit 9        | •             | alog Comparat                    |                 |                   |                 |                 |          |

|              | 1 = Analog Co | omparator 2 mo                   | dule is disable | ed                |                 |                 |          |

|              | 0 = Analog Co | omparator 2 mo                   | dule is enable  | ed                |                 |                 |          |

| bit 8        | CMP1MD: An    | alog Comparat                    | or 1 Module D   | isable bit        |                 |                 |          |

|              | •             | omparator 1 mo                   |                 |                   |                 |                 |          |

|              | C C           | omparator 1 mo                   |                 | ed                |                 |                 |          |

| bit 7-0      | Unimplemen    |                                  |                 |                   |                 |                 |          |

#### REGISTER 9-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

| U-0          | U-0          | U-0              | U-0           | U-0              | U-0              | U-0             | U-0   |

|--------------|--------------|------------------|---------------|------------------|------------------|-----------------|-------|

| —            | —            | _                | —             |                  | —                | —               | —     |

| bit 15       |              |                  |               |                  |                  |                 | bit 8 |

|              |              |                  |               |                  |                  |                 |       |

| U-0          | U-0          | R/W-1            | R/W-1         | R/W-1            | R/W-1            | R/W-1           | R/W-1 |

| _            | _            | SS1R5            | SS1R4         | SS1R3            | SS1R2            | SS1R1           | SS1R0 |

| bit 7        |              |                  |               |                  |                  |                 | bit 0 |

|              |              |                  |               |                  |                  |                 |       |

| Legend:      |              |                  |               |                  |                  |                 |       |

| R = Readat   | ole bit      | W = Writable     | bit           | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |              |                  |               |                  |                  |                 |       |

| bit 15-6     | Unimplemen   | ted: Read as '   | 0'            |                  |                  |                 |       |

| bit 5-0      | SS1R<5:0>:   | Assign SPI1 SI   | ave Select In | put (SS1IN) to   | the Correspond   | ing RPn Pin bit | S     |

|              | 111111 = Inp | out tied to Vss  |               |                  |                  |                 |       |

|              | 100011 = Inp | out tied to RP35 | 5             |                  |                  |                 |       |

|              | 100010 = Inp | out tied to RP34 | 1             |                  |                  |                 |       |

|              | 100001 = Inp | out tied to RP33 | 3             |                  |                  |                 |       |

|              | 100000 = Inp | out tied to RP32 | 2             |                  |                  |                 |       |

|              | •            |                  |               |                  |                  |                 |       |

|              | •            |                  |               |                  |                  |                 |       |

|              | •            |                  |               |                  |                  |                 |       |

|              |              |                  |               |                  |                  |                 |       |

#### REGISTER 10-8: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

00000 = Input tied to RP0

### 12.0 TIMER2/3 FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

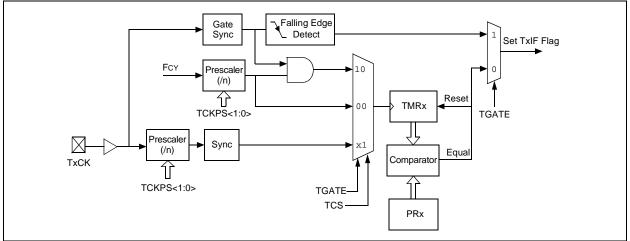

Timer2 is a Type B timer that offers the following major features:

- A Type B timer can be concatenated with a Type C timer to form a 32-bit timer

- External clock input (TxCK) is always synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

Figure 12-1 shows a block diagram of the Type B timer.

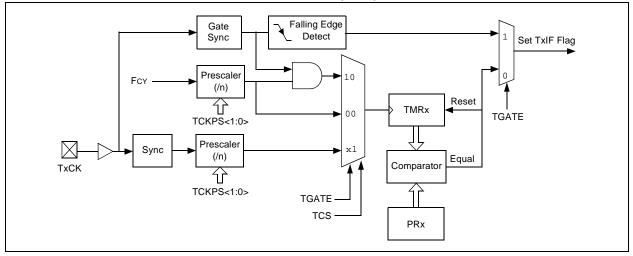

Timer3 is a Type C timer that offers the following major features:

- A Type C timer can be concatenated with a Type B timer to form a 32-bit timer

- The external clock input (TxCK) is always synchronized to the internal device clock and the clock synchronization is performed before the prescaler

A block diagram of the Type C timer is shown in Figure 12-2.

**Note:** Timer3 is not available on all devices.

### FIGURE 12-1: TYPE B TIMER BLOCK DIAGRAM (x = 2)

#### FIGURE 12-2: TYPE C TIMER BLOCK DIAGRAM (x = 3)

#### REGISTER 15-14: IOCONx: PWMx I/O CONTROL REGISTER (CONTINUED)

| bit 3-2 | CLDAT<1:0>: State for PWMxH and PWMxL Pins if CLMODE is Enabled bits <sup>(2)</sup>                          |

|---------|--------------------------------------------------------------------------------------------------------------|

|         | FCLCONx <ifltmod> = 0: Normal Fault mode:</ifltmod>                                                          |

|         | If current-limit is active, then CLDAT<1> provides the state for PWMxH                                       |

|         | If current-limit is active, then CLDAT<0> provides the state for PWMxL                                       |

|         | FCLCONx <ifltmod> = 1: Independent Fault mode:</ifltmod>                                                     |

|         | CLDAT<1:0> bits are ignored.                                                                                 |

| bit 1   | SWAP<1:0>: Swap PWMxH and PWMxL pins                                                                         |

|         | 1 = PWMxH output signal is connected to the PWMxL pin and the PWMxL signal is connected to the<br>PWMxH pins |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                 |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                   |

|         | 1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWM time base                          |

|         | 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary                           |

| Note 1: | These bits should be changed only when PTEN = 0. Changing the clock selection during operation will          |

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 2: The state represents the active/inactive state of the PWM module depending on the POLH and POLL bit settings.

#### REGISTER 19-1: ADCON: ANALOG-TO-DIGITAL CONTROL REGISTER (CONTINUED)

#### bit 4 ASYNCSAMP: Asynchronous Dedicated S&H Sampling Enable bit<sup>(1)</sup>

- 1 = The dedicated S&H is constantly sampling and then terminates sampling as soon as the trigger pulse is detected

- 0 = The dedicated S&H starts sampling when the trigger event is detected and completes the sampling process in two ADC clock cycles

- bit 3 Unimplemented: Read as '0'

- bit 2-0 ADCS<2:0>: Analog-to-Digital Conversion Clock Divider Select bits<sup>(1)</sup>

- 111 = FADC/8

- 110 = FADC/7

- 101 = FADC/6

- 100 = FADC/5

- 011 = FADC/4 (default)

- 010 = FADC/3

- 001 = FADC/2

- 000 = FADC/1

- Note 1: These control bits can only be changed while ADC is disabled (ADON = 0).

- 2: These bits are only available on devices with one SAR.

#### REGISTER 19-5: ADCPC0: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 0 (CONTINUED)

```

bit 4-0

TRGSRC0<4:0>: Trigger 0 Source Selection bits

Selects trigger source for conversion of Analog Channels AN1 and AN0.

11111 = Timer2 period match

11011 = Reserved

11010 = PWM Generator 4 current-limit ADC trigger

11001 = PWM Generator 3 current-limit ADC trigger

11000 = PWM Generator 2 current-limit ADC trigger

10111 = PWM Generator 1 current-limit ADC trigger

10110 = \text{Reserved}

10010 = Reserved

10001 = PWM Generator 4 secondary trigger is selected

10000 = PWM Generator 3 secondary trigger is selected

01111 = PWM Generator 2 secondary trigger is selected

01110 = PWM Generator 1 secondary trigger is selected

01101 = Reserved

01100 = Timer1 period match

01000 = Reserved

00111 = PWM Generator 4 primary trigger is selected

00110 = PWM Generator 3 primary trigger is selected

00101 = PWM Generator 2 primary trigger is selected

00100 = PWM Generator 1 primary trigger is selected

00011 = PWM Special Event Trigger is selected

00010 = Global software trigger is selected

00001 = Individual software trigger is selected

00000 = No conversion is enabled

```

**Note 1:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

#### 23.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 23.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 23.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 23.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 23.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 23.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

#### 24.1 DC Characteristics

|                | Voo Bongo               | Tomp Bongo            | Max MIPS                                         |  |  |  |  |

|----------------|-------------------------|-----------------------|--------------------------------------------------|--|--|--|--|

| Characteristic | VDD Range<br>(in Volts) | Temp Range<br>(in °C) | dsPIC33FJ06GS101/X02 and<br>dsPIC33FJ16GSX02/X04 |  |  |  |  |

| _              | 3.0-3.6∨ <sup>(1)</sup> | -40°C to +85°C        | 40                                               |  |  |  |  |

|                | 3.0-3.6∨ <sup>(1)</sup> | -40°C to +125°C       | 40                                               |  |  |  |  |

#### TABLE 24-1: OPERATING MIPS VS. VOLTAGE

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 24-11 for BOR values.

#### TABLE 24-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min         | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +85  | °C   |

| Extended Temperature Devices                                                                |        |             |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40         | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40         | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | Pint + Pi/o |             |      | W    |

| I/O Pin Power Dissipation:<br>I/O = $\Sigma$ ({VDD - VOH} x IOH) + $\Sigma$ (VOL x IOL)     |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (           | TJ — TA)/θJ | IA   | W    |

#### TABLE 24-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур | Max | Unit | Notes |

|------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 44-Pin QFN   | θJA    | 28  | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TFQP  | θJA    | 39  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP | θJA    | 42  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θJA    | 47  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S | θJA    | 34  | —   | °C/W | 1     |

| Package Thermal Resistance, 18-Pin SOIC  | θJA    | 57  | —   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin VTLA  | θJA    | 25  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| AC CHARACTERISTICS |        |                                                            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                    |     |       |                                          |  |

|--------------------|--------|------------------------------------------------------------|------------------------------------------------------|-----|--------------------|-----|-------|------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                             |                                                      | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                               |  |

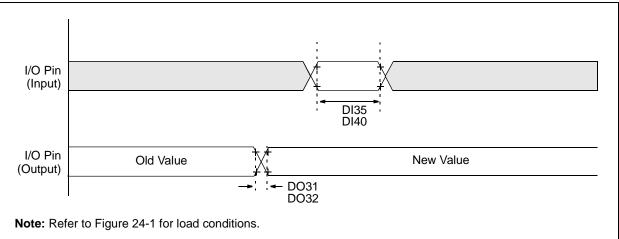

| DO31 TIOR          |        | Port Output Rise Time:                                     |                                                      |     |                    |     |       |                                          |  |

|                    |        | 4x Source Driver Pin<br>RB0-RB2, RB5-RB1<br>RC2, RC9, RC10 | ,                                                    | —   | 10                 | 25  | ns    | Refer to Figure 24-1 for test conditions |  |

|                    |        | 8x Source Driver Pir<br>RC3-RC8, RC11-RC                   | •                                                    | _   | 8                  | 20  | ns    |                                          |  |

|                    |        | 16x Source Driver P<br>RA4, RB3, RB4, RB                   | ,                                                    |     | 6                  | 15  | ns    |                                          |  |

| DO32               | TIOF   | Port Output Fall Time:                                     |                                                      |     |                    |     |       |                                          |  |

|                    |        | 4x Source Driver Pin<br>RB0-RB2, RB5-RB1<br>RC2, RC9, RC10 | ,                                                    | _   | 10                 | 25  | ns    | Refer to Figure 24-1 for test conditions |  |

|                    |        | 8x Source Driver Pir<br>RC3-RC8, RC11-RC                   |                                                      |     | 8                  | 20  | ns    |                                          |  |

|                    |        | 16x Source Driver P<br>RA4, RB3, RB4, RB                   |                                                      | _   | 6                  | 15  | ns    |                                          |  |

| DI35               | TINP   | INTx Pin High or Lov                                       | v Time (input)                                       | 20  | —                  | —   | ns    |                                          |  |

| DI40               | Trbp   | CNx High or Low Tin                                        | ne (input)                                           | 2   | _                  |     | Тсү   |                                          |  |

#### TABLE 24-21: I/O TIMING REQUIREMENTS

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

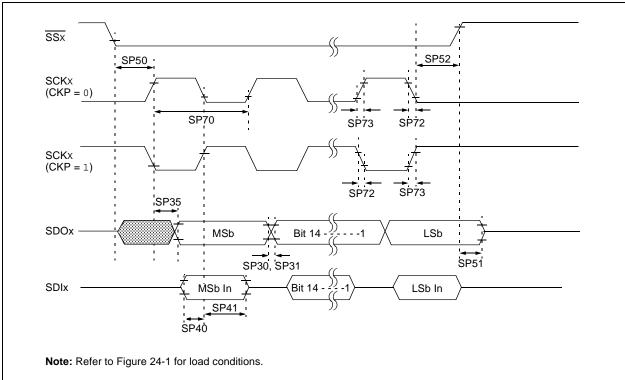

# FIGURE 24-18: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS |        |                                                                                                                                                     | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |      |      |                                                    |                                                                                                                                                         |  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    |        |                                                                                                                                                     | Operating temperature                                                    |      |      | -40°C $\leq$ TA $\leq$ +150°C for High Temperature |                                                                                                                                                         |  |

| Param.             | Symbol | Characteristic                                                                                                                                      | Min.                                                                     | Тур. | Max. | Units                                              | Conditions                                                                                                                                              |  |

|                    |        | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins –<br>RA0-RA2, RB0-RB2, RB5-<br>RB10, RB15, RC1, RC2, RC9,<br>RC10                            | _                                                                        | _    | 0.4  | V                                                  | Io∟ ≤ 3.6 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                           |  |

| DO10 Vol           | Vol    | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins – RC0,<br>RC3-RC8, RC11-RC13                                                                 | _                                                                        | _    | 0.4  | V                                                  | $\begin{array}{l} \text{IOL} \leq 6 \text{ mA, VDD} = 3.3 \text{V} \\ \text{See } \textbf{Note 1} \end{array}$                                          |  |

|                    |        | Output Low Voltage<br>I/O Pins:<br>16x Sink Driver Pins – RA3,<br>RA4, RB3, RB4, RB11-RB14                                                          | _                                                                        | _    | 0.4  | V                                                  | $\label{eq:IDL} \begin{array}{l} \text{IOL} \leq 12 \text{ mA}, \text{ VDD} = 3.3\text{V} \\ \text{See } \textbf{Note 1} \end{array}$                   |  |

| DO20 Voh           |        | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins –<br>RA0-RA2, RB0-RB2, RB5-<br>RB10, RB15, RC1, RC2, RC9,<br>RC10                         | 2.4                                                                      | _    | _    | ~                                                  | IoL ≥ -4 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                            |  |

|                    | Vон    | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins – RC0,<br>RC3-RC8, RC11-RC13                                                              | 2.4                                                                      | _    | _    | V                                                  | IOL ≥ -8 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                            |  |

|                    |        | Output High Voltage<br>I/O Pins:<br>16x Source Driver Pins – RA3,<br>RA4, RB3, RB4, RB11-RB14                                                       | 2.4                                                                      | _    | _    | V                                                  | Io∟≥ -16 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                            |  |

|                    |        | Output High Voltage<br>I/O Pins:                                                                                                                    | 1.5                                                                      | _    | —    |                                                    | $\label{eq:IOH} \begin{array}{l} \text{IOH} \geq \textbf{-3.9 mA}, \ \text{VDD} = \textbf{3.3V} \\ \text{See} \ \textbf{Note} \ \textbf{1} \end{array}$ |  |

|                    |        | 4x Source Driver Pins –<br>RA0-RA2, RB0-RB2, RB5-                                                                                                   | 2.0                                                                      | _    | _    | V                                                  | IOH ≥ -3.7 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                          |  |

|                    |        | RB10, RB15, RC1, RC2, RC9<br>RC10                                                                                                                   | 3.0                                                                      | —    | —    |                                                    | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                            |  |

|                    |        | Output High Voltage<br>I/O Pins:                                                                                                                    | 1.5                                                                      | _    | _    |                                                    | $\begin{array}{l} \text{IOH} \geq \text{-7.5 mA, VDD} = 3.3\text{V} \\ \text{See Note 1} \end{array}$                                                   |  |

| DO20A V            | Voh1   | 8x Source Driver Pins – RC0,<br>RC3-RC8, RC11-RC13<br>Output High Voltage<br>I/O Pins:<br>16x Source Driver Pins – RA3,<br>RA4, RB3, RB4, RB11-RB14 | 2.0                                                                      | _    | _    | v<br>v                                             | IOH ≥ -6.8 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                          |  |

|                    |        |                                                                                                                                                     | 3.0                                                                      | _    | _    |                                                    | IOH ≥ -3 mA, VDD = 3.3V<br>See <b>Note</b> 1                                                                                                            |  |

|                    |        |                                                                                                                                                     | 1.5                                                                      | _    | _    |                                                    | IOH ≥ -15 mA, VDD = 3.3V<br>See <b>Note</b> 1                                                                                                           |  |

|                    |        |                                                                                                                                                     | 2.0                                                                      | _    | _    |                                                    | IOH ≥ -14 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                           |  |

|                    |        |                                                                                                                                                     | 3.0                                                                      | _    | _    |                                                    | IOH ≥ -7 mA, VDD = 3.3V<br>See <b>Note 1</b>                                                                                                            |  |

#### TABLE 25-5: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

| AC CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |

| HSP35              | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               | —   | 10  | 25  | ns    |            |  |

| HSP40              | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 28  | _   |     | ns    |            |  |

| HSP41              | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 35  | —   |     | ns    |            |  |

#### TABLE 25-9: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

#### TABLE 25-10: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|--------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                           | Min | Тур | Max | Units | Conditions |  |

| HSP35              | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                               |     | 10  | 25  | ns    |            |  |

| HSP36              | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                            | 35  | _   | _   | ns    |            |  |

| HSP40              | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                              | 28  | _   | _   | ns    |            |  |

| HSP41              | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                               | 35  |     |     | ns    |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

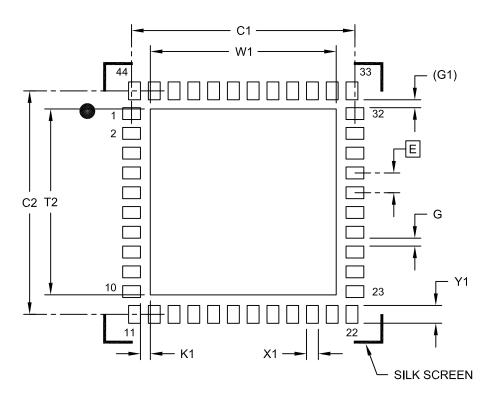

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### **RECOMMENDED LAND PATTERN**

|                            | MILLIMETERS |          |           |      |  |  |

|----------------------------|-------------|----------|-----------|------|--|--|

| Dimension                  | MIN         | NOM      | MAX       |      |  |  |

| Terminal Pitch             |             | 0.50 BSC |           |      |  |  |

| Optional Center Pad Width  | W2          |          |           | 4.70 |  |  |

| Optional Center Pad Length | T2          |          |           | 4.70 |  |  |

| Terminal Pad Spacing       | C1          |          | 5.65      |      |  |  |

| Terminal Pad Spacing       | C2          |          | 5.65      |      |  |  |

| Terminal Pad Width (X44)   | X1          |          |           | 0.30 |  |  |

| Terminal Pad Length (X44)  | Y1          |          |           | 0.45 |  |  |

| Distance Between Pads      | (G1)        |          | 0.20 REF. |      |  |  |

| Distance Between Pads      | G           | 0.20     |           |      |  |  |

| Distance Between Pads      | K1          | 0.267    |           |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2157A

| TABLE A-1: | MAJOR SECTION UPDATES (CONTINUED) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Section Name             | Update Description                                                                                                                                                                                                                            |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 23.0 "Electrical | Updated Typ values for Thermal Packaging Characteristics (Table 23-3).                                                                                                                                                                        |

| Characteristics"         | Removed Typ value for DC Temperature and Voltage Specifications Parameter DC12 (Table 23-4).                                                                                                                                                  |

|                          | Updated all Typ values and conditions for DC Characteristics: Operating Current (IDD), updated last sentence in Note 2 (Table 23-5).                                                                                                          |

|                          | Updated all Typ values for DC Characteristics: Idle Current (IIDLE) (see Table 23-6).                                                                                                                                                         |

|                          | Updated all Typ values for DC Characteristics: Power Down Current (IPD) (see Table 23-7).                                                                                                                                                     |

|                          | Updated all Typ values for DC Characteristics: Doze Current (IDOZE) (see Table 23-8).                                                                                                                                                         |

|                          | Added Note 4 (reference to new table containing digital-only and analog pin information, as well as Current Sink/Source capabilities) in the I/O Pin Input Specifications (Table 23-9).                                                       |

|                          | Updated Max value for BOR electrical characteristics Parameter BO10 (see Table 23-11).                                                                                                                                                        |

|                          | Swapped Min and Typ values for Program Memory Parameters D136 and D137 (Table 23-12).                                                                                                                                                         |

|                          | Updated Typ values for Internal RC Accuracy Parameter F20 and added Extended temperature range to table heading (see Table 23-19).                                                                                                            |

|                          | Removed all values for Reset, Watchdog Timer, Oscillator Start-up Timer, and Power-up Timer Parameter SY20 and updated conditions, which now refers to <b>Section 20.4 "Watchdog Timer (WDT)</b> " and LPRC Parameter F21a (see Table 23-22). |

|                          | Added specifications to High-Speed PWM Module Timing Requirements for Tap Delay (Table 23-29).                                                                                                                                                |

|                          | Updated Min and Max values for 10-bit High-Speed Analog-to-Digital Module Parameters AD01 and AD11 (see Table 23-36).                                                                                                                         |

|                          | Updated Max value and unit of measure for DAC AC Specification (see Table 23-40).                                                                                                                                                             |