#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502-h-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

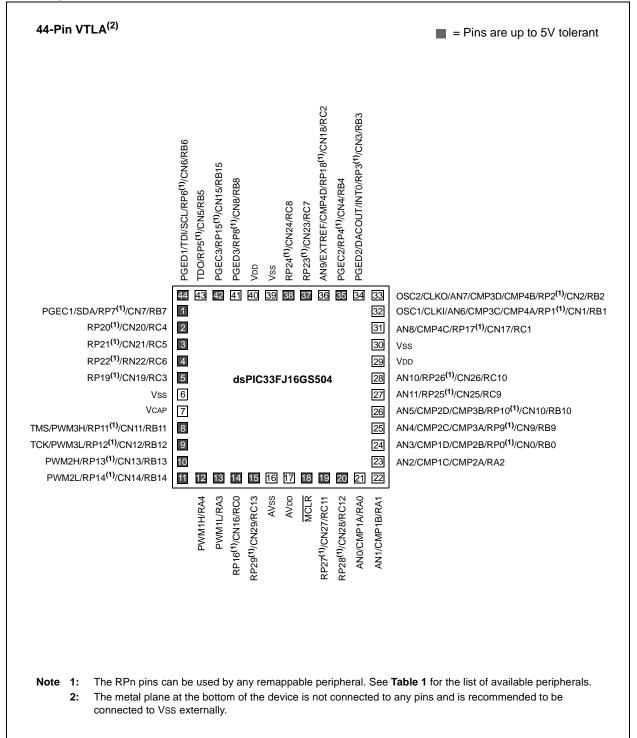

### **Pin Diagrams (Continued)**

| FABLE 1-1: I   Pin Name | Pin        | I/O DESC<br>Buffer | PPS     | Description                                                           |

|-------------------------|------------|--------------------|---------|-----------------------------------------------------------------------|

|                         | Туре       | Туре               | Capable |                                                                       |

| CMP1A                   | I          | Analog             | No      | Comparator 1 Channel A.                                               |

| CMP1B                   | 1          | Analog             | No      | Comparator 1 Channel B.                                               |

| CMP1C                   | 1          | Analog             | No      | Comparator 1 Channel C.                                               |

| CMP1D                   | 1          | Analog             | No      | Comparator 1 Channel D.                                               |

| CMP2A                   | 1          | Analog             | No      | Comparator 2 Channel A.                                               |

| CMP2B                   | 1          | Analog             | No      | Comparator 2 Channel B.                                               |

| CMP2C                   | 1          | Analog             | No      | Comparator 2 Channel C.                                               |

| CMP2D                   | 1          | Analog             | No      | Comparator 2 Channel D.                                               |

| CMP3A                   | i          | Analog             | No      | Comparator 3 Channel A.                                               |

| CMP3B                   | 1          | Analog             | No      | Comparator 3 Channel B.                                               |

| CMP3C                   | 1          | Analog             | No      | Comparator 3 Channel C.                                               |

| CMP3D                   | i          | Analog             | No      | Comparator 3 Channel D.                                               |

| CMP4A                   | i          | Analog             | No      | Comparator 4 Channel A.                                               |

| CMP4B                   | i          | Analog             | No      | Comparator 4 Channel B.                                               |

| CMP4C                   | i          | Analog             | No      | Comparator 4 Channel C.                                               |

| CMP4D                   | l i        | Analog             | No      | Comparator 4 Channel D.                                               |

| DACOUT                  | 0          | 7 (10)             | No      | DAC output voltage.                                                   |

| ACMP1-ACMP4             | 0          |                    | Yes     | DAC trigger to PWM module.                                            |

| EXTREF                  | 1          |                    | No      | External voltage reference input for the reference DACs.              |

| REFCLKO                 | 0          | Analog             |         |                                                                       |

| REFULKO                 | 0          |                    | Yes     | REFCLKO output signal is a postscaled derivative of the system clock. |

| FLT1-FLT8               | I          | ST                 | Yes     | Fault Inputs to PWM module.                                           |

| SYNCI1-SYNCI2           | I          | ST                 | Yes     | External synchronization signal to PWM master time base.              |

| SYNCO1                  | 0          |                    | Yes     | PWM master time base for external device synchronization.             |

| PWM1L                   | 0          |                    | No      | PWM1 low output.                                                      |

| PWM1H                   | 0          |                    | No      | PWM1 high output.                                                     |

| PWM2L                   | 0          |                    | No      | PWM2 low output.                                                      |

| PWM2H                   | Ō          |                    | No      | PWM2 high output.                                                     |

| PWM3L                   | 0          |                    | No      | PWM3 low output.                                                      |

| PWM3H                   | 0          |                    | No      | PWM3 high output.                                                     |

| PWM4L                   | 0          |                    | Yes     | PWM4 low output.                                                      |

| PWM4H                   | 0          | _                  | Yes     | PWM4 high output.                                                     |

| PGED1                   | I/O        | ST                 | No      | Data I/O pin for programming/debugging Communication Channel 1.       |

| PGEC1                   | 1          | ST                 | No      | Clock input pin for programming/debugging Communication               |

|                         |            | _                  | -       | Channel 1.                                                            |

| PGED2                   | I/O        | ST                 | No      | Data I/O pin for programming/debugging Communication Channel 2.       |

| PGEC2                   | ., C       | ST                 | No      | Clock input pin for programming/debugging Communication               |

| . 0101                  |            | 01                 |         | Channel 2.                                                            |

| PGED3                   | I/O        | ST                 | No      | Data I/O pin for programming/debugging Communication Channel 3        |

| PGEC3                   | 1/0        | ST                 | No      | Clock input pin for programming/debugging Communication Channel 3.    |

| TOLOG                   | · ·        | 01                 | NO      | Channel 3.                                                            |

| MCLR                    | I/P        | ST                 | No      | Master Clear (Reset) input. This pin is an active-low Reset to the    |

|                         | UL.        | 51                 | NU      | device.                                                               |

| AVDD                    | Р          | Р                  | No      | Positive supply for analog modules. This pin must be connected at     |

| ////DD                  |            | I                  |         | all times. AVDD is connected to VDD.                                  |

| AVss                    | Р          | Р                  | No      | Ground reference for analog modules. AVss is connected to Vss.        |

| VDD                     | P          |                    | No      | Positive supply for peripheral logic and I/O pins.                    |

| VCAP                    | P          |                    | No      | CPU logic filter capacitor connection.                                |

| Vss                     | P          |                    | No      | Ground reference for logic and I/O pins.                              |

|                         | -          | <br>compatible     |         |                                                                       |

|                         |            | gger input v       |         |                                                                       |

|                         | Fransistor |                    |         |                                                                       |

#### . . . . .

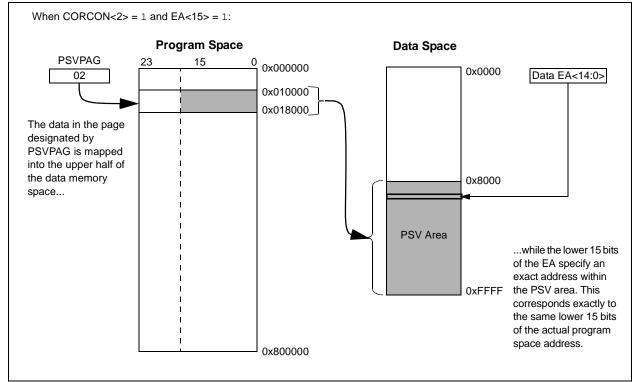

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and Program Space Visibility (PSV) is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address 8000h and higher maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during Table Reads/Writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

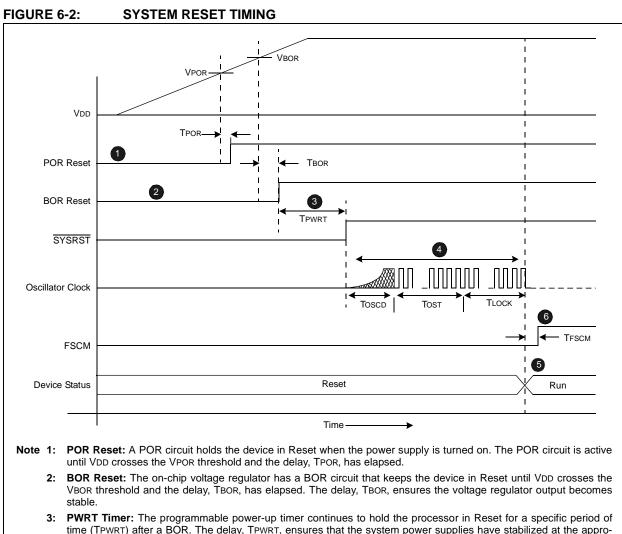

- time (TPWRT) after a BOR. The delay, TPWRT, ensures that the system power supplies have stabilized at the appropriate level for full-speed operation. After the delay, TPWRT has elapsed and the SYSRST becomes inactive, which in turn, enables the selected oscillator to start generating clock cycles.

- 4: Oscillator Delay: The total delay for the clock to be ready for various clock source selections is given in Table 6-1. Refer to Section 8.0 "Oscillator Configuration" for more information.

- 5: When the oscillator clock is ready, the processor begins execution from location, 0x000000. The user application programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

- 6: If the Fail-Safe Clock Monitor (FSCM) is enabled, it begins to monitor the system clock when the system clock is ready and the delay, TFSCM, has elapsed.

| Symbol | Parameter                           | Value            |

|--------|-------------------------------------|------------------|

| VPOR   | POR Threshold                       | 1.8V nominal     |

| TPOR   | POR Extension Time                  | 30 µs maximum    |

| VBOR   | BOR Threshold                       | 2.5V nominal     |

| TBOR   | BOR Extension Time                  | 100 μs maximum   |

| TPWRT  | Programmable<br>Power-up Time Delay | 0-128 ms nominal |

| TFSCM  | Fail-Safe Clock Monitor<br>Delay    | 900 μs maximum   |

### TABLE 6-2: OSCILLATOR DELAY

| Note: | When the device exits the Reset<br>condition (begins normal operation), the<br>device operating parameters (voltage,<br>frequency, temperature, etc.) must be                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | within their operating ranges; otherwise,<br>the device may not function correctly.<br>The user application must ensure that<br>the delay between the time power is first<br>applied, and the time SYSRST becomes |

|       | inactive, is long enough to get all operating parameters within specification.                                                                                                                                    |

| R/W-0            | R/W-0                                                                | U-0                                              | U-0                                     | U-0              | U-0             | R/W-0           | R/W-0  |

|------------------|----------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------|------------------|-----------------|-----------------|--------|

| ADCP1IF          | ADCP0IF                                                              | _                                                | _                                       | _                | _               | AC4IF           | AC3IF  |

| bit 15           |                                                                      |                                                  |                                         |                  |                 |                 | bit    |

| R/W-0            | U-0                                                                  | U-0                                              | U-0                                     | U-0              | U-0             | R/W-0           | R/W-0  |

| AC2IF            | _                                                                    | _                                                | _                                       | _                | _               | PWM4IF          | PWM3IF |

| bit 7            |                                                                      |                                                  |                                         |                  |                 |                 | bit    |

| Legend:          |                                                                      |                                                  |                                         |                  |                 |                 |        |

| R = Readable     | bit                                                                  | W = Writable                                     | bit                                     | U = Unimplen     | nented bit, rea | ıd as '0'       |        |

| -n = Value at F  | POR                                                                  | '1' = Bit is set                                 |                                         | '0' = Bit is cle | ared            | x = Bit is unkn | nown   |

| bit 15<br>bit 14 | 1 = Interrupt r<br>0 = Interrupt r<br>ADCP0IF: AD<br>1 = Interrupt r | equest has oc<br>equest has no                   | t occurred<br>rersion Done Ir<br>curred |                  |                 |                 |        |

| bit 13-10        | •                                                                    | ted: Read as '                                   |                                         |                  |                 |                 |        |

| bit 9            | 1 = Interrupt r                                                      | g Comparator<br>equest has oc<br>equest has no   |                                         | g Status bit     |                 |                 |        |

| bit 8            | AC3IF: Analo                                                         | •                                                | 3 Interrupt Fla<br>curred               | g Status bit     |                 |                 |        |

| bit 7            | 1 = Interrupt r                                                      | g Comparator<br>equest has oc<br>equest has no   |                                         | g Status bit     |                 |                 |        |

| bit 6-2          | •                                                                    | ted: Read as '                                   |                                         |                  |                 |                 |        |

| bit 1            | <b>PWM4IF:</b> PW<br>1 = Interrupt r                                 | M4 Interrupt F<br>equest has oc<br>equest has no | lag Status bit<br>curred                |                  |                 |                 |        |

| bit 0            |                                                                      | M3 Interrupt F<br>equest has oc<br>equest has no | curred                                  |                  |                 |                 |        |

### REGISTER 7-10: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| R/W-0           | R/W-0         | U-0               | U-0       | U-0                                     | U-0 | U-0 | U-0   |  |

|-----------------|---------------|-------------------|-----------|-----------------------------------------|-----|-----|-------|--|

| PWM2IE          | PWM1IE        | —                 | _         | —                                       | —   | —   | _     |  |

| bit 15          |               |                   |           |                                         |     |     | bit 8 |  |

|                 |               |                   |           |                                         |     |     |       |  |

| U-0             | U-0           | U-0               | U-0       | U-0                                     | U-0 | U-0 | U-0   |  |

| _               | —             | —                 |           | _                                       | —   | —   | —     |  |

| bit 7           |               |                   |           |                                         |     |     | bit 0 |  |

|                 |               |                   |           |                                         |     |     |       |  |

| Legend:         |               |                   |           |                                         |     |     |       |  |

| R = Readable    | bit           | W = Writable b    | oit       | U = Unimplemented bit, read as '0'      |     |     |       |  |

| -n = Value at F | POR           | '1' = Bit is set  |           | '0' = Bit is cleared x = Bit is unknown |     |     | own   |  |

|                 |               |                   |           |                                         |     |     |       |  |

| bit 15          | PWM2IE: PV    | /M2 Interrupt Er  | nable bit |                                         |     |     |       |  |

|                 |               | request is enabl  |           |                                         |     |     |       |  |

|                 | 0 = Interrupt | request is not ei | nabled    |                                         |     |     |       |  |

| bit 14          | PWM1IE: PV    | /M1 Interrupt Er  | nable bit |                                         |     |     |       |  |

|                 | •             | request is enabl  |           |                                         |     |     |       |  |

|                 | 0 = Interrupt | request is not ei | nabled    |                                         |     |     |       |  |

| bit 13-0        | Unimplemen    | ted: Read as '0   | )'        |                                         |     |     |       |  |

|                 |               |                   |           |                                         |     |     |       |  |

### REGISTER 7-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| R/W-0         | U-0                                           | R/W-0                                  | R/W-0           | R/W-0                  | R/W-0                  | R/W-0                 | R/W-0                 |  |  |  |

|---------------|-----------------------------------------------|----------------------------------------|-----------------|------------------------|------------------------|-----------------------|-----------------------|--|--|--|

| ROON          | _                                             | ROSSLP                                 | ROSEL           | RODIV3 <sup>(1)</sup>  | RODIV2 <sup>(1)</sup>  | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                               |                                        |                 |                        |                        |                       | bit 8                 |  |  |  |

|               |                                               |                                        |                 |                        |                        |                       |                       |  |  |  |

| U-0           | U-0                                           | U-0                                    | U-0             | U-0                    | U-0                    | U-0                   | U-0                   |  |  |  |

|               | _                                             | —                                      |                 | —                      | —                      | —                     | —                     |  |  |  |

| bit 7         |                                               |                                        |                 |                        |                        |                       | bit 0                 |  |  |  |

| Legend:       |                                               |                                        |                 |                        |                        |                       |                       |  |  |  |

| R = Readabl   | e bit                                         | W = Writable                           | bit             | U = Unimplen           | nented bit, read       | l as '0'              |                       |  |  |  |

| -n = Value at | POR                                           | '1' = Bit is set                       |                 | '0' = Bit is cle       |                        | x = Bit is unkr       | iown                  |  |  |  |

|               |                                               |                                        |                 |                        |                        |                       |                       |  |  |  |

| bit 15        | ROON: Refer                                   | ence Oscillator                        | r Output Enab   | ole bit                |                        |                       |                       |  |  |  |

|               |                                               |                                        |                 | on the REFCL           | .K0 pin <sup>(2)</sup> |                       |                       |  |  |  |

|               |                                               | e oscillator outp                      |                 | ł                      |                        |                       |                       |  |  |  |

| bit 14        | Unimplemen                                    | ted: Read as '                         | 0'              |                        |                        |                       |                       |  |  |  |

| bit 13        | ROSSLP: Reference Oscillator Run in Sleep bit |                                        |                 |                        |                        |                       |                       |  |  |  |

|               |                                               | e oscillator outp<br>e oscillator outp |                 |                        |                        |                       |                       |  |  |  |

| bit 12        |                                               | erence Oscillato                       |                 |                        |                        |                       |                       |  |  |  |

|               | 1 = Oscillator                                | crystal is used                        | as the refere   | nce clock              |                        |                       |                       |  |  |  |

|               | •                                             | lock is used as                        |                 |                        |                        |                       |                       |  |  |  |

| bit 11-8      | RODIV<3:0>:                                   | Reference Os                           | cillator Divide | er bits <sup>(1)</sup> |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        | •               |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        | •               | 4                      |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi<br>ence clock divi     |                 |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        | -               |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        | •               |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        |                 |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        | -               |                        |                        |                       |                       |  |  |  |

|               | 0111 = Refer                                  | ence clock divi                        | ded by 128      |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        | -               |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        |                 |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        |                 |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi                        | -               |                        |                        |                       |                       |  |  |  |

|               |                                               | ence clock divi<br>ence clock divi     | -               |                        |                        |                       |                       |  |  |  |

|               | 000T = Velet                                  |                                        |                 |                        |                        |                       |                       |  |  |  |

|               | 0000 = Refer                                  |                                        |                 |                        |                        |                       |                       |  |  |  |

### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

Note 1: The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

2: This pin is remappable. Refer to Section 10.6 "Peripheral Pin Select" for more information.

### 10.2 Open-Drain Configuration

In addition to the PORTx, LATx and TRISx registers for data control, some digital-only port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (for example, 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to **"Pin Diagrams"** for the available pins and their functionality.

### 10.3 Configuring Analog Port Pins

The ADPCFG and TRISx registers control the operation of the Analog-to-Digital (A/D) port pins. The port pins that are to function as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The ADPCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORTx register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

### 10.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP. An example is shown in Example 10-1.

### 10.5 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 30 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a Change-of-State.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when the push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on Change Notification pins should always be disabled when the port pin is configured as a digital output.

#### EQUATION 10-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| BTSS | PORTB, #13 | ; | Next Instruction                |

|      |            |   |                                 |

#### REGISTER 10-5: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0    | U-0    | U-0    | U-0    | U-0    | U-0    |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | _   |        | —      | _      | —      | —      | —      |

| bit 15 |     |        |        |        |        | •      | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

| —      | —   | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7  | •   |        |        |        |        | •      | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0

OCFAR<5:0>: Assign Output Capture A (OCFA) to the Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35 100010 = Input tied to RP34 100001 = Input tied to RP33 100000 = Input tied to RP32

•

00000 = Input tied to RP0

| REGISTER     | 10-7: RPINI                                                                                                                                                                                                                                                                         | R20: PERIPHI                                                                                                      | ERAL PIN S                    |                   | I REGISTER       | 20              |        |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|------------------|-----------------|--------|

| U-0          | U-0                                                                                                                                                                                                                                                                                 | R/W-1                                                                                                             | R/W-1                         | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|              |                                                                                                                                                                                                                                                                                     | SCK1R5                                                                                                            | SCK1R4                        | SCK1R3            | SCK1R2           | SCK1R1          | SCK1R0 |

| bit 15       | -     -     SCK1R5     SCK1R4     SCK1R3     SCK1R2     SCK1R1       J-0     U-0     R/W-1     R/W-1     R/W-1     R/W-1     R/W-1       -     -     SDI1R5     SDI1R4     SDI1R3     SDI1R2     SDI1R1       nd:     -     W = Writable bit     U = Unimplemented bit, read as '0' | bit                                                                                                               |                               |                   |                  |                 |        |

| U-0          | U-0                                                                                                                                                                                                                                                                                 | R/W-1                                                                                                             | R/W-1                         | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

| _            |                                                                                                                                                                                                                                                                                     |                                                                                                                   | r                             | I I               |                  | 1               | SDI1R0 |

| bit 7        |                                                                                                                                                                                                                                                                                     |                                                                                                                   |                               |                   |                  |                 | bit    |

| Legend:      |                                                                                                                                                                                                                                                                                     |                                                                                                                   |                               |                   |                  |                 |        |

| R = Readab   | le bit                                                                                                                                                                                                                                                                              | W = Writable                                                                                                      | bit                           | U = Unimplen      | nented bit, read | d as '0'        |        |

| -n = Value a | t POR                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                  |                               | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| bit 7-6      | 100010 = In<br>100001 = In<br>100000 = In<br>•<br>•<br>•<br>00000 = Inp                                                                                                                                                                                                             | put tied to RP34<br>put tied to RP33<br>put tied to RP32                                                          | 4<br>3<br>2                   |                   |                  |                 |        |

| bit 5-0      | SDI1R<5:0><br>111111 = In<br>100011 = In<br>100010 = In<br>100001 = In                                                                                                                                                                                                              | Assign SPI1 E<br>pout tied to Vss<br>pout tied to RP3<br>pout tied to RP3<br>pout tied to RP3<br>pout tied to RP3 | Pata Input (SD<br>5<br>4<br>3 | I1) to the Corre  | esponding RPn    | Pin bits        |        |

### REGISTER 10-7: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0                | U-0                                                                                                                                         | R/W-1                                                                                                                                                                                       | R/W-1                                               | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------|------------------|-----------------|--------|

| —                  |                                                                                                                                             | FLT3R5                                                                                                                                                                                      | FLT3R4                                              | FLT3R3            | FLT3R2           | FLT3R1          | FLT3R0 |

| bit 15             |                                                                                                                                             |                                                                                                                                                                                             |                                                     |                   |                  |                 | bit 8  |

| 11.0               | U-0                                                                                                                                         | R/W-1                                                                                                                                                                                       | R/W-1                                               | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

| U-0<br>—<br>bit 7  | 0-0                                                                                                                                         | FLT2R5                                                                                                                                                                                      | FLT2R4                                              | FLT2R3            | FLT2R2           | FLT2R1          | FLT2R0 |

| bit 7              |                                                                                                                                             | T LIZI(                                                                                                                                                                                     | 1 21214                                             | T ETZI(0          | TLIZI            | I LIZI(I        | bit (  |

|                    |                                                                                                                                             |                                                                                                                                                                                             |                                                     |                   |                  |                 |        |

| Legend:            |                                                                                                                                             | \A/ \A/ \                                                                                                                                                                                   | 1.14                                                |                   |                  |                 |        |

| R = Readab         |                                                                                                                                             | W = Writable                                                                                                                                                                                |                                                     |                   | nented bit, read |                 |        |

| -n = Value a       | t POR                                                                                                                                       | '1' = Bit is set                                                                                                                                                                            |                                                     | '0' = Bit is clea | ared             | x = Bit is unkr | IOWN   |

| bit 15-14          | Unimplomon                                                                                                                                  | ted: Read as '                                                                                                                                                                              | 0'                                                  |                   |                  |                 |        |

|                    | -                                                                                                                                           |                                                                                                                                                                                             |                                                     |                   |                  |                 |        |

| bit 13-8           |                                                                                                                                             | •                                                                                                                                                                                           | Fault Input 3 (                                     | FLI3) to the Co   | orresponding R   | Pn Pin bits     |        |

|                    | 111111 = Inp                                                                                                                                | ut tied to Vss                                                                                                                                                                              |                                                     |                   |                  |                 |        |

|                    |                                                                                                                                             |                                                                                                                                                                                             | _                                                   |                   |                  |                 |        |

|                    |                                                                                                                                             | ut tied to RP3                                                                                                                                                                              |                                                     |                   |                  |                 |        |

|                    | 100010 <b>= Inp</b>                                                                                                                         | ut tied to RP34                                                                                                                                                                             | 1                                                   |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp                                                                                                                | ut tied to RP34<br>ut tied to RP33                                                                                                                                                          | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp                                                                                                                | ut tied to RP34                                                                                                                                                                             | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp                                                                                                                | ut tied to RP34<br>ut tied to RP33                                                                                                                                                          | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp                                                                                                                | ut tied to RP34<br>ut tied to RP33                                                                                                                                                          | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                                       | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>00000 = Inpu                                                                 | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0                                                                                                                      | 4<br>3<br>2                                         |                   |                  |                 |        |

| bit 7-6            | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>00000 = Inpu<br>Unimplement                                             | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '                                                                                             | 4<br>3<br>2<br>0'                                   |                   |                  |                 |        |

| bit 7-6<br>bit 5-0 | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM                                                                               | 4<br>3<br>2<br>0'                                   | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss                                                           | 4<br>3<br>2<br>0'<br>Fault Input 2 (                | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP35                                        | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5           | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34                     | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4      | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34<br>ut tied to RP34  | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | orresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34                     | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34<br>ut tied to RP34  | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34<br>ut tied to RP34  | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>ut tied to RP32 | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

### REGISTER 10-10: RPINR30: PERIPHERAL PIN SELECT INPUT REGISTER 30

| R/W-0                 | U-0                     | R/W-0                                                 | HS/HC-0                 | R/W-0                      | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------------------------------------|-------------------------|----------------------------|------------------------|------------------------|------------------------|

| PTEN                  | —                       | PTSIDL                                                | SESTAT                  | SEIEN                      | EIPU <sup>(1)</sup>    | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15                |                         |                                                       |                         |                            |                        |                        | bit 8                  |

|                       |                         |                                                       |                         |                            |                        |                        |                        |

| R/W-0                 | U-0                     | R/W-0                                                 | R/W-0                   | R/W-0                      | R/W-0                  | R/W-0                  | R/W-0                  |

| SYNCEN <sup>(1)</sup> | —                       | SYNCSRC1 <sup>(1)</sup>                               | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup>     | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 |                         |                                                       |                         |                            |                        |                        | bit 0                  |

| r                     |                         |                                                       |                         |                            |                        |                        |                        |

| Legend:               |                         | HC = Hardware                                         |                         |                            | re Settable bit        |                        |                        |

| R = Readable          |                         | W = Writable bi                                       | t                       |                            | nented bit, rea        |                        |                        |

| -n = Value at         | POR                     | '1' = Bit is set                                      |                         | '0' = Bit is cle           | ared                   | x = Bit is unkr        | nown                   |

| bit 15                |                         | M Module Enabl<br>nodule is enable                    |                         |                            |                        |                        |                        |

|                       |                         | nodule is disable                                     |                         |                            |                        |                        |                        |

| bit 14                |                         | ented: Read as                                        |                         |                            |                        |                        |                        |

| bit 13                | -                       | WM Time Base S                                        |                         | e bit                      |                        |                        |                        |

|                       |                         | me base halts in<br>me base runs in                   |                         |                            |                        |                        |                        |

| bit 12                | SESTAT: S               | pecial Event Inte                                     | errupt Status bit       |                            |                        |                        |                        |

|                       | •                       | event interrupt i<br>event interrupt i                |                         |                            |                        |                        |                        |

| bit 11                | SEIEN: Spe              | ecial Event Interr                                    | upt Enable bit          |                            |                        |                        |                        |

|                       |                         | event interrupt i<br>event interrupt i                |                         |                            |                        |                        |                        |

| bit 10                |                         | ole Immediate Pe                                      | •                       |                            |                        |                        |                        |

|                       |                         | Period register is<br>Period register u               |                         |                            | oundaries              |                        |                        |

| bit 9                 | 1 = SYNCI               | : Synchronization<br>x and SYNCO po<br>x and SYNCO ar | plarity is inverted     | •                          |                        |                        |                        |

| bit 8                 | SYNCOEN                 | : Primary Time E                                      | Base Sync Enab          | le bit <sup>(1)</sup>      |                        |                        |                        |

|                       |                         | D output is enabl<br>D output is disabl               |                         |                            |                        |                        |                        |

| bit 7                 | SYNCEN:                 | External Time Ba                                      | ase Synchroniza         | tion Enable bit            | t(1)                   |                        |                        |

|                       |                         | al synchronization<br>al synchronization              |                         |                            |                        |                        |                        |

| bit 6                 | Unimplem                | ented: Read as                                        | ʻ0'                     |                            |                        |                        |                        |

| bit 5-4               | SYNCSRC                 | <1:0>: Synchror                                       | ous Source Sel          | ection bits <sup>(1)</sup> |                        |                        |                        |

|                       | 11 = Reser              |                                                       |                         |                            |                        |                        |                        |

|                       | 10 = Reser<br>01 = SYNC |                                                       |                         |                            |                        |                        |                        |

|                       | 01 = STNC<br>00 = SYNC  |                                                       |                         |                            |                        |                        |                        |

|                       |                         | uld be changed o<br>st program the P                  |                         |                            |                        |                        |                        |

### REGISTER 15-1: PTCON: PWM TIME BASE CONTROL REGISTER

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | TRGCI | MP<15:8>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | U-0              | U-0             | U-0   |

|                 |       | TRGCMP<7:3>      |       |                   | _                | _               | _     |

| bit 7           |       |                  |       |                   |                  |                 | bit C |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

When primary PWM functions in the local time base, this register contains the compare values that can trigger the ADC module.

bit 2-0

Unimplemented: Read as '0'

### REGISTER 15-17: STRIGX: PWMx SECONDARY TRIGGER COMPARE VALUE REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|-----------|-------|-------|-------|

|        |       |       | STRGCM | /IP<15:8> |       |       |       |

| bit 15 |       |       |        |           |       |       | bit 8 |

|        |       |       |        |           |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0     | U-0   | U-0   | U-0   |

| 10/00-0 | 10/00-0 | 10/00-0     | 11/00-0 | 10/00-0 | 0-0 | 0-0 | 0-0   |

|---------|---------|-------------|---------|---------|-----|-----|-------|

|         | ST      | FRGCMP<7:3> | _       |         | —   |     |       |

| bit 7   |         |             |         |         |     |     | bit 0 |

|         |         |             |         |         |     |     |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-3 STRGCMP<15:3>: Secondary Trigger Control Value bits When secondary PWM functions in the local time base, this register contains the compare values that can trigger the ADC module.

bit 2-0 Unimplemented: Read as '0'

| REGISTER 1            | 8-1: UxMO                                                       | DE: UARTx N                                       |                     | STER                 |                  |                   |               |  |

|-----------------------|-----------------------------------------------------------------|---------------------------------------------------|---------------------|----------------------|------------------|-------------------|---------------|--|

| R/W-0                 | U-0                                                             | R/W-0                                             | R/W-0               | R/W-0                | U-0              | R/W-0             | R/W-0         |  |

| UARTEN <sup>(1)</sup> |                                                                 | USIDL                                             | IREN <sup>(2)</sup> | RTSMD                | —                | UEN1              | UEN0          |  |

| bit 15                | ·                                                               |                                                   |                     |                      |                  |                   | bit           |  |

| R/W-0, HC             | R/W-0                                                           | R/W-0, HC                                         | R/W-0               | R/W-0                | R/W-0            | R/W-0             | R/W-0         |  |

| WAKE                  | LPBACK                                                          | ABAUD                                             | URXINV              | BRGH                 | PDSEL1           | PDSEL0            | STSEL         |  |

| bit 7                 | EI BROR                                                         | //B/(OD                                           | OTOXINV             | BROM                 | TDOLLI           | 1 DOLLO           | bit           |  |

|                       |                                                                 |                                                   | 0                   | •.                   |                  |                   |               |  |

| Legend:               | 1.12                                                            | HC = Hardwa                                       |                     |                      |                  |                   |               |  |

| R = Readable          |                                                                 | W = Writable                                      |                     | -                    | nented bit, read |                   |               |  |

| -n = Value at F       | POR                                                             | '1' = Bit is set                                  |                     | '0' = Bit is cle     | ared             | x = Bit is unkn   | own           |  |

| bit 15                | UARTEN: UA                                                      | ARTx Enable bi                                    | <sub>t</sub> (1)    |                      |                  |                   |               |  |

|                       | 1 = UARTx is                                                    | s enabled; all U                                  | ARTx pins are       | e controlled by      | UARTx as defi    | ned by UEN<1:     | 0>            |  |

|                       |                                                                 |                                                   | UARTx pins a        | are controlled I     | by port latches  | , UARTx power     | consumptio    |  |

| bit 14                | is minima                                                       | ai<br>i <b>ted:</b> Read as 'i                    | ר'                  |                      |                  |                   |               |  |

| bit 13                | -                                                               | Tx Stop in Idle I                                 |                     |                      |                  |                   |               |  |

| bit 13                |                                                                 | ues module op                                     |                     | device enters        | Idle mode        |                   |               |  |

|                       |                                                                 | s module operation                                |                     |                      |                  |                   |               |  |

| bit 12                | IREN: IrDA <sup>®</sup>                                         | Encoder and D                                     | ecoder Enable       | e bit <sup>(2)</sup> |                  |                   |               |  |

|                       | 1 = IrDA enc                                                    | oder and deco                                     | der are enable      | ed                   |                  |                   |               |  |

|                       | 0 = IrDA encoder and decoder are disabled                       |                                                   |                     |                      |                  |                   |               |  |

| bit 11                |                                                                 | le Selection for                                  |                     | it                   |                  |                   |               |  |

|                       |                                                                 | in is in Simple»<br>in is in Flow Co              |                     |                      |                  |                   |               |  |

| bit 10                | Unimplemen                                                      | ted: Read as '                                    | כ'                  |                      |                  |                   |               |  |

| bit 9-8               |                                                                 | IARTx Enable b                                    |                     |                      |                  |                   |               |  |