Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70204) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies from device to device. A singlecycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can serve as a data, address or address offset register. The sixteenth Working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

There are two classes of instruction in the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 is capable of executing a data (or program data) memory read, a Working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model is shown in Figure 3-2.

# 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data space mapping feature allows any instruction access program space as if it were data space.

# 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits, right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal realtime performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain Working registers to each address space.

# TABLE 4-27: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS202 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15       | Bit 14                | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6          | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|--------------|-----------------------|--------|----------|----------|----------|----------|----------|-------------|----------------|---------|-----------|----------|----------|----------|----------|---------------|

| ADCON        | 0300        | ADON         | —                     | ADSIDL | SLOWCLK  | —        | GSWTRG   | —        | FORM     | EIE         | ORDER          | SEQSAMP | ASYNCSAMP | —        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _            | -                     | —      | _        | _        |          | _        | —        | _           | _              | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _            | -                     | —      | _        | _        |          | _        | —        | _           | P6RDY          | _       | _         | _        | P2RDY    | P1RDY    | PORDY    | 0000          |

| ADBASE       | 0308        | ADBASE<15:1> |                       |        |          |          |          |          |          |             |                | —       | 0000      |          |          |          |          |               |

| ADCPC0       | 030A        | IRQEN1       | PEND1                 | SWTRG1 | TRGSRC14 | TRGSRC13 | TRGSRC12 | TRGSRC11 | TRGSRC10 | IRQEN0      | PEND0          | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | _            | -                     | —      | _        | _        |          | _        | —        | IRQEN2      | PEND2          | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCPC3       | 0310        | _            |                       | —      | _        | _        | _        | —        | —        | IRQEN6      | PEND6          | SWTRG6  | TRGSRC64  | TRGSRC63 | TRGSRC62 | TRGSRC61 | TRGSRC60 | 0000          |

| ADCBUF0      | 0320        |              | ADC Data Buffer 0     |        |          |          |          |          |          |             |                |         |           | xxxx     |          |          |          |               |

| ADCBUF1      | 0322        |              |                       |        |          |          |          |          | ADC E    | Data Buffer | <sup>.</sup> 1 |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |              |                       |        |          |          |          |          | ADC E    | Data Buffer | 2              |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |              |                       |        |          |          |          |          | ADC E    | Data Buffer | 3              |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |              |                       |        |          |          |          |          | ADC E    | Data Buffer | 4              |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |              | ADC Data Buffer 5     |        |          |          |          |          |          |             |                | xxxx    |           |          |          |          |          |               |

| ADCBUF12     | 0338        |              | ADC Data Buffer 12 xx |        |          |          |          |          |          |             |                | xxxx    |           |          |          |          |          |               |

| ADCBUF13     | 033A        |              |                       |        |          |          |          |          | ADC D    | Data Buffer | 13             |         |           |          |          |          |          | xxxx          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

# TABLE 4-28: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ16GS402/404 DEVICES ONLY

|              | -           |                       |                       |            | -           |                 |               |               |              |            |       | -       |           |          |          |          |          |               |

|--------------|-------------|-----------------------|-----------------------|------------|-------------|-----------------|---------------|---------------|--------------|------------|-------|---------|-----------|----------|----------|----------|----------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15                | Bit 14                | Bit 13     | Bit 12      | Bit 11          | Bit 10        | Bit 9         | Bit 8        | Bit 7      | Bit 6 | Bit 5   | Bit 4     | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADCON        | 0300        | ADON                  | —                     | ADSIDL     | SLOWCLK     | _               | GSWTRG        | _             | FORM         | EIE        | ORDER | SEQSAMP | ASYNCSAMP | -        | ADCS2    | ADCS1    | ADCS0    | 0003          |

| ADPCFG       | 0302        | _                     | _                     | _          | _           | —               | _             | _             | _            | PCFG7      | PCFG6 | PCFG5   | PCFG4     | PCFG3    | PCFG2    | PCFG1    | PCFG0    | 0000          |

| ADSTAT       | 0306        | _                     | _                     | _          | _           | —               | _             | _             | _            | _          | _     | _       | _         | P3RDY    | P2RDY    | P1RDY    | P0RDY    | 0000          |

| ADBASE       | 0308        | ADBASE<15:1> — (      |                       |            |             |                 |               |               |              |            |       |         | 0000      |          |          |          |          |               |

| ADCPC0       | 030A        | IRQEN1                | PEND1                 | SWTRG1     | TRGSRC14    | TRGSRC13        | TRGSRC12      | TRGSRC11      | TRGSRC10     | IRQEN0     | PEND0 | SWTRG0  | TRGSRC04  | TRGSRC03 | TRGSRC02 | TRGSRC01 | TRGSRC00 | 0000          |

| ADCPC1       | 030C        | IRQEN3                | PEND3                 | SWTRG3     | TRGSRC34    | TRGSRC33        | TRGSRC32      | TRGSRC31      | TRGSRC30     | IRQEN2     | PEND2 | SWTRG2  | TRGSRC24  | TRGSRC23 | TRGSRC22 | TRGSRC21 | TRGSRC20 | 0000          |

| ADCBUF0      | 0320        | ADC Data Buffer 0     |                       |            |             |                 |               |               |              |            |       |         | xxxx      |          |          |          |          |               |

| ADCBUF1      | 0322        |                       |                       |            |             |                 |               |               | ADC D        | ata Buffer | 1     |         |           |          |          |          |          | xxxx          |

| ADCBUF2      | 0324        |                       |                       |            |             |                 |               |               | ADC D        | ata Buffer | 2     |         |           |          |          |          |          | xxxx          |

| ADCBUF3      | 0326        |                       |                       |            |             |                 |               |               | ADC D        | ata Buffer | 3     |         |           |          |          |          |          | xxxx          |

| ADCBUF4      | 0328        |                       |                       |            |             |                 |               |               | ADC D        | ata Buffer | 4     |         |           |          |          |          |          | xxxx          |

| ADCBUF5      | 032A        |                       | ADC Data Buffer 5     |            |             |                 |               |               |              |            |       |         | xxxx      |          |          |          |          |               |

| ADCBUF6      | 032C        |                       | ADC Data Buffer 6 xxx |            |             |                 |               |               |              |            |       |         | xxxx      |          |          |          |          |               |

| ADCBUF7      | 032E        | ADC Data Buffer 7 xxx |                       |            |             |                 |               |               |              |            |       | xxxx    |           |          |          |          |          |               |

| Legend:      | x =         | unknown               | value on              | Reset, — = | unimplement | ed, read as '0' | . Reset value | s are shown i | n hexadecima | al.        |       |         |           |          |          |          |          |               |

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

### TABLE 4-48: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions to provide a greater addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing mode specified in the instruction can differ |

|-------|---------------------------------------------------------------------------------------|

|       | for the source and destination EA. How-                                               |

|       | ever, the 4-bit Wb (register offset) field is                                         |

|       | shared by both source and destination                                                 |

|       | (but typically only used by one).                                                     |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the MAC class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.3.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| <br> | -             |                            |                                         | _ |

|------|---------------|----------------------------|-----------------------------------------|---|

| ;    | Set up NVMCO  | N for row programming open | rations                                 |   |

|      | MOV           | #0x4001, W0                | ;                                       |   |

|      | MOV           | W0, NVMCON                 | ; Initialize NVMCON                     |   |

| ;    | Set up a poir | nter to the first program  | memory location to be written           |   |

| ;    | program memo: | ry selected, and writes en | nabled                                  |   |

|      | MOV           | #0x0000, W0                | ;                                       |   |

|      | MOV           | W0, TBLPAG                 | ; Initialize PM Page Boundary SFR       |   |

|      | MOV           | #0x6000, W0                | ; An example program memory address     |   |

| ;    | Perform the   | TBLWT instructions to writ | te the latches                          |   |

| ;    | 0th_program_v | word                       |                                         |   |

|      | MOV           | #LOW_WORD_0, W2            | i                                       |   |

|      | MOV           | #HIGH_BYTE_0, W3           | ;                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

| ;    | lst_program_  | word                       |                                         |   |

|      | MOV           | #LOW_WORD_1, W2            | ;                                       |   |

|      | MOV           | #HIGH_BYTE_1, W3           | i                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

| ;    | 2nd_program   | _word                      |                                         |   |

|      | MOV           | #LOW_WORD_2, W2            | i                                       |   |

|      | MOV           | #HIGH_BYTE_2, W3           | i                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

|      | •             |                            |                                         |   |

|      | •             |                            |                                         |   |

|      | •             |                            |                                         |   |

| ;    | 63rd_program  |                            |                                         |   |

|      |               | #LOW_WORD_31, W2           | ;                                       |   |

|      |               | #HIGH_BYTE_31, W3          | ;                                       |   |

|      |               | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

|      |               |                            |                                         |   |

EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | <pre>; Block all interrupts with priority &lt;7 ; for next 5 instructions</pre> |

|------|-------------|---------------------------------------------------------------------------------|

| MOV  | #0x55, W0   |                                                                                 |

| MOV  | W0, NVMKEY  | ; Write the 55 key                                                              |

| MOV  | #0xAA, W1   | ;                                                                               |

| MOV  | W1, NVMKEY  | ; Write the AA key                                                              |

| BSET | NVMCON, #WR | ; Start the erase sequence                                                      |

| NOP  |             | ; Insert two NOPs after the                                                     |

| NOP  |             | ; erase command is asserted                                                     |

|      |             |                                                                                 |

# 7.3 Interrupt Control and Status Registers

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices implement 27 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFSx

- IECx

- IPCx

- INTTREG

### 7.3.1 INTCON1 AND INTCON2

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

### 7.3.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

### 7.3.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

# 7.3.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

# 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit is found in IEC0<0> and the INT0IP bits are found in the first position of IPC0 (IPC0<2:0>).

# 7.3.6 STATUS/CONTROL REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality.

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user can change the current CPU priority level by writing to the IPL bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-35 in the following pages.

| R/W-0                               | R/W-0                            | U-0               | U-0       | U-0                                | U-0  | U-0                | U-0   |  |  |  |

|-------------------------------------|----------------------------------|-------------------|-----------|------------------------------------|------|--------------------|-------|--|--|--|

| PWM2IE                              | PWM1IE                           | —                 | —         | —                                  | —    | —                  | _     |  |  |  |

| bit 15                              |                                  |                   |           |                                    |      |                    | bit 8 |  |  |  |

|                                     |                                  |                   |           |                                    |      |                    |       |  |  |  |

| U-0                                 | U-0                              | U-0               | U-0       | U-0                                | U-0  | U-0                | U-0   |  |  |  |

| _                                   | —                                | —                 |           | —                                  | —    | —                  | —     |  |  |  |

| bit 7                               |                                  |                   |           |                                    |      |                    | bit 0 |  |  |  |

|                                     |                                  |                   |           |                                    |      |                    |       |  |  |  |

| Legend:                             |                                  |                   |           |                                    |      |                    |       |  |  |  |

| R = Readable                        | bit                              | W = Writable b    | oit       | U = Unimplemented bit, read as '0' |      |                    |       |  |  |  |

| -n = Value at F                     | POR                              | '1' = Bit is set  |           | '0' = Bit is cle                   | ared | x = Bit is unknown |       |  |  |  |

|                                     |                                  |                   |           |                                    |      |                    |       |  |  |  |

| bit 15                              | PWM2IE: PV                       | /M2 Interrupt Er  | nable bit |                                    |      |                    |       |  |  |  |

|                                     |                                  | request is enabl  |           |                                    |      |                    |       |  |  |  |

|                                     | 0 = Interrupt                    | request is not ei | nabled    |                                    |      |                    |       |  |  |  |

| bit 14                              | PWM1IE: PV                       | /M1 Interrupt Er  | nable bit |                                    |      |                    |       |  |  |  |

|                                     | 1 = Interrupt request is enabled |                   |           |                                    |      |                    |       |  |  |  |

|                                     | 0 = Interrupt                    | request is not ei | nabled    |                                    |      |                    |       |  |  |  |

| bit 13-0 Unimplemented: Read as '0' |                                  |                   |           |                                    |      |                    |       |  |  |  |

|                                     |                                  |                   |           |                                    |      |                    |       |  |  |  |

# REGISTER 7-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| U-0          | R/W-1                              | R/W-0                                                        | R/W-0           | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|--------------|------------------------------------|--------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

| 0-0          | T1IP2                              | T1IP1                                                        | T1IP0           | 0-0               | OC1IP2           | OC1IP1          | OC1IP0  |  |  |  |  |  |

| <br>Dit 15   | 11112                              | 1 111 1                                                      | THE             |                   | 001112           | 00111           | bit     |  |  |  |  |  |

|              |                                    |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

| U-0          | R/W-1                              | R/W-0                                                        | R/W-0           | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|              | IC1IP2                             | IC1IP1                                                       | IC1IP0          |                   | INT0IP2          | INT0IP1         | INT0IP0 |  |  |  |  |  |

| bit 7        |                                    |                                                              |                 |                   |                  |                 | bit     |  |  |  |  |  |

| Legend:      |                                    |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

| R = Readab   | le bit                             | W = Writable                                                 | bit             | U = Unimple       | mented bit, read | l as '0'        |         |  |  |  |  |  |

| -n = Value a | t POR                              | '1' = Bit is set                                             | :               | '0' = Bit is cl   | eared            | x = Bit is unkr | nown    |  |  |  |  |  |

| bit 15       | Unimplome                          | ented: Read as '                                             | 0'              |                   |                  |                 |         |  |  |  |  |  |

| bit 14-12    | -                                  | Timer1 Interrupt                                             |                 |                   |                  |                 |         |  |  |  |  |  |

| 011 14-12    |                                    | upt is Priority 7                                            | •               | ity interrunt)    |                  |                 |         |  |  |  |  |  |

|              | •                                  |                                                              | (ingricer prior | ity interrupty    |                  |                 |         |  |  |  |  |  |

|              | •                                  |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | •<br>001 – Intorr                  | upt is Priority 1                                            |                 |                   |                  |                 |         |  |  |  |  |  |

|              |                                    | upt source is dis                                            | abled           |                   |                  |                 |         |  |  |  |  |  |

| bit 11       |                                    | nted: Read as '                                              |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 10-8     | -                                  | OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits |                 |                   |                  |                 |         |  |  |  |  |  |

|              |                                    | upt is Priority 7                                            |                 |                   | <b>,</b>         |                 |         |  |  |  |  |  |

|              | •                                  |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | •                                  |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1 |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | 000 = Interrupt source is disabled |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 7        | Unimpleme                          | ented: Read as '                                             | 0'              |                   |                  |                 |         |  |  |  |  |  |

| bit 6-4      | IC1IP<2:0>                         | : Input Capture (                                            | Channel 1 Int   | errupt Priority I | oits             |                 |         |  |  |  |  |  |

|              | 111 = Interr                       | upt is Priority 7                                            | (highest prior  | ity interrupt)    |                  |                 |         |  |  |  |  |  |

|              | •                                  |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | •                                  |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interr                       | upt is Priority 1                                            |                 |                   |                  |                 |         |  |  |  |  |  |

|              |                                    | upt source is dis                                            | abled           |                   |                  |                 |         |  |  |  |  |  |

| bit 3        | Unimpleme                          | ented: Read as '                                             | 0'              |                   |                  |                 |         |  |  |  |  |  |

| bit 2-0      | INT0IP<2:0                         | >: External Inter                                            | rupt 0 Priority | bits              |                  |                 |         |  |  |  |  |  |

|              | 111 = Interr                       | upt is Priority 7                                            | (highest prior  | ity interrupt)    |                  |                 |         |  |  |  |  |  |

|              | •                                  |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | •                                  |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | 0.01                               |                                                              |                 |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = interr                       | upt is Priority 1                                            |                 |                   |                  |                 |         |  |  |  |  |  |

#### IDCA. INTERRURT PRIORITY CONTROL REGISTER A

# **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,2)</sup> (CONTINUED)

- bit 3 **CF:** Clock Fail Detect bit (read/clear by application)

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.

- 2: This register is reset only on a Power-on Reset (POR).

- 3: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

# 9.2.2 IDLE MODE

The following occur in Idle mode:

- The CPU stops executing instructions

- The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active

The device will wake-up from Idle mode on any of these events:

- Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

# 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

# 9.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

# 9.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

| REGISTER 1      | 1-1: T1CO                                                                                           | N: TIMER1 C                     | ONTROL RE       | GISTER           |                  |                  |       |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------|---------------------------------|-----------------|------------------|------------------|------------------|-------|--|--|--|--|

| R/W-0           | U-0                                                                                                 | R/W-0                           | U-0             | U-0              | U-0              | U-0              | U-0   |  |  |  |  |

| TON             | —                                                                                                   | TSIDL                           | —               | —                | —                | —                |       |  |  |  |  |

| bit 15          |                                                                                                     |                                 |                 |                  |                  |                  | bit 8 |  |  |  |  |

|                 | <b>D</b> 4 4 4                                                                                      |                                 |                 |                  | 5444.6           | <b>D b b c c</b> |       |  |  |  |  |

| U-0             | R/W-0                                                                                               | R/W-0                           | R/W-0           | U-0              | R/W-0            | R/W-0            | U-0   |  |  |  |  |

|                 | TGATE                                                                                               | TCKPS1                          | TCKPS0          | _                | TSYNC            | TCS              | —     |  |  |  |  |

| bit 7           |                                                                                                     |                                 |                 |                  |                  |                  | bit ( |  |  |  |  |

| Legend:         |                                                                                                     |                                 |                 |                  |                  |                  |       |  |  |  |  |

| R = Readable    | bit                                                                                                 | W = Writable                    | bit             | U = Unimpler     | mented bit, read | l as '0'         |       |  |  |  |  |

| -n = Value at I | POR                                                                                                 | '1' = Bit is set                |                 | '0' = Bit is cle |                  | x = Bit is unkno | own   |  |  |  |  |

|                 |                                                                                                     |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 15          | TON: Timer1                                                                                         | On bit                          |                 |                  |                  |                  |       |  |  |  |  |

|                 | 1 = Starts 16-                                                                                      | bit Timer1                      |                 |                  |                  |                  |       |  |  |  |  |

|                 | 0 = Stops 16-                                                                                       | bit Timer1                      |                 |                  |                  |                  |       |  |  |  |  |

| bit 14          | Unimplemented: Read as '0'                                                                          |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 13          | t 13 TSIDL: Timer1 Stop in Idle Mode bit                                                            |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                                     | ues module op<br>s module opera |                 |                  | dle mode         |                  |       |  |  |  |  |

| bit 12-7        | <ul> <li>0 = Continues module operation in Idle mode</li> <li>Unimplemented: Read as '0'</li> </ul> |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 6           | -                                                                                                   |                                 |                 | n Enable bit     |                  |                  |       |  |  |  |  |

| bit 0           | <b>TGATE:</b> Timer1 Gated Time Accumulation Enable bit<br>When TCS = 1:                            |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | This bit is igno                                                                                    |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | When TCS =                                                                                          | 0:                              |                 |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                                     | e accumulation                  |                 |                  |                  |                  |       |  |  |  |  |

| bit E 1         |                                                                                                     | e accumulation                  |                 | - Coloct hito    |                  |                  |       |  |  |  |  |

| bit 5-4         | 11 = 1:256                                                                                          | Timer1 Input (                  | JUCK Prescale   | e Select bits    |                  |                  |       |  |  |  |  |

|                 | 11 = 1.250<br>10 = 1.64                                                                             |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | 01 = 1:8                                                                                            |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | 00 = 1:1                                                                                            |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 3           | Unimplemen                                                                                          | ted: Read as '                  | 0'              |                  |                  |                  |       |  |  |  |  |

| bit 2           | TSYNC: Time                                                                                         | er1 External Clo                | ock Input Synd  | chronization Se  | elect bit        |                  |       |  |  |  |  |

|                 | When TCS =                                                                                          |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                                     | izes external c                 |                 | aput             |                  |                  |       |  |  |  |  |

|                 | When TCS =                                                                                          | synchronize e>                  | Riemai Ciuck II | iput             |                  |                  |       |  |  |  |  |

|                 | This bit is igno                                                                                    |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 1           | •                                                                                                   | Clock Source S                  | Select bit      |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                                     | clock from T1C                  |                 | rising edge)     |                  |                  |       |  |  |  |  |

|                 | 0 = Internal cl                                                                                     |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                                     |                                 |                 |                  |                  |                  |       |  |  |  |  |

# REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

# 13.1 Input Capture Register

# **REGISTER 13-1:** ICxCON: INPUT CAPTURE x CONTROL REGISTER (x = 1, 2)

| U-0    | U-0   | R/W-0  | U-0     | U-0     | U-0   | U-0   | U-0   |

|--------|-------|--------|---------|---------|-------|-------|-------|

| —      | —     | ICSIDL | —       | —       | —     | _     | —     |

| bit 15 |       |        |         |         |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0  | R-0, HC | R-0, HC | R/W-0 | R/W-0 | R/W-0 |

| ICTMR  | ICI1  | ICI0   | ICOV    | ICBNE   | ICM2  | ICM1  | ICM0  |

| bit 7  | •     | •      |         |         |       |       | bit   |

| Legend:           | HC = Hardware Clearable bit |                           |                    |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                                            |

|           | 1 = Input capture module halts in CPU Idle mode                                                                                                                                  |

|           | 0 = Input capture module continues to operate in CPU Idle mode                                                                                                                   |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 7     | ICTMR: Input Capture Timer Select bits                                                                                                                                           |

|           | <ul> <li>1 = TMR2 contents are captured on a capture event</li> <li>0 = TMR3 contents are captured on a capture event</li> </ul>                                                 |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                           |

|           | 11 = Interrupt on every fourth capture event                                                                                                                                     |

|           | 10 = Interrupt on every third capture event                                                                                                                                      |

|           | 01 = Interrupt on every second capture event                                                                                                                                     |

| L:1. 4    | 00 = Interrupt on every capture event                                                                                                                                            |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                         |

|           | 1 = Input capture overflow occurred                                                                                                                                              |

| 1.11.0    | 0 = No input capture overflow occurred                                                                                                                                           |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                                         |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                                         |

|           | 111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode; rising edge detect only, all other control bits are not applicable                     |

|           | 110 = Unused (module disabled)                                                                                                                                                   |

|           | 101 = Capture mode, every 16th rising edge                                                                                                                                       |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                                        |

|           | 011 = Capture mode, every rising edge                                                                                                                                            |

|           | <ul> <li>010 = Capture mode, every falling edge</li> <li>001 = Capture mode, every edge (rising and falling); ICI&lt;1:0&gt; bits do not control interrupt generation</li> </ul> |

|           | for this mode                                                                                                                                                                    |

|           | 000 = Input capture module turned off                                                                                                                                            |

# 15.3 Control Registers

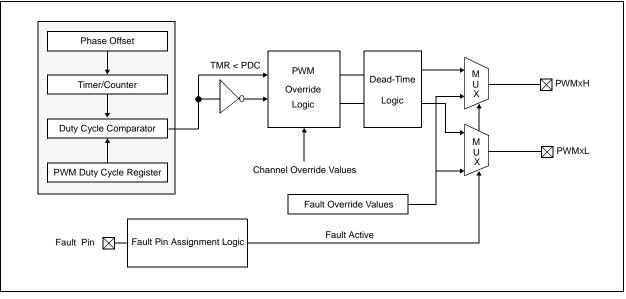

The following registers control the operation of the high-speed PWM module.

- PTCON: PWM Time Base Control Register

- PTCON2: PWM Clock Divider Select Register

- PTPER: PWM Master Time Base Register(1)

- SEVTCMP: PWM Special Event Compare Register

- MDC: PWM Master Duty Cycle Register(1,2)

- PWMCONx: PWMx Control Register

- PDCx: PWMx Generator Duty Cycle Register(1,2)

- PHASEx: PWMx Primary Phase-Shift Register(1,2) (provides the local time base period for PWMxH)

- DTRx: PWMx Dead-Time Register

- ALTDTRx: PWMx Alternate Dead-Time Register

- SDCx: PWMx Secondary Duty Cycle Register(1,2)

- SPHASEx: PWMx Secondary Phase-Shift Register(1,2) (provides the local time base period for PWMxL)

- TRGCONx: PWMx Trigger Control Register

- IOCONx: PWMx I/O Control Register

- FCLCONx: PWMx Fault Current-Limit Control Register

- TRIGx: PWMx Primary Trigger Compare Value Register

- STRIGx: PWMx Secondary Trigger Compare Value Register

- LEBCONx: Leading-Edge Blanking Control Register(1)

- PWMCAPx: Primary PWMx Time Base Capture Register

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

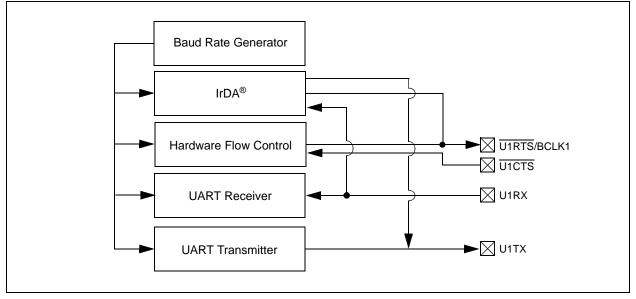

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70188) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 device families. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 12.5 Mbps to 38 bps at 50 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- Transmit and Receive Interrupts

- A Separate Interrupt for all UART Error Conditions

- Loopback mode for Diagnostic Support

- Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

A simplified block diagram of the UART module is shown in Figure 1. The UART module consists of these key hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

# FIGURE 1: UART1 SIMPLIFIED BLOCK DIAGRAM

# 20.3 Module Applications

This module provides a means for the SMPS dsPIC<sup>®</sup> DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator and an associated 10-bit DAC that provides a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- Generate an Interrupt

- Trigger an ADC Sample and Convert Process

- Truncate the PWM Signal (current limit)

- Truncate the PWM Period (current minimum)

- Disable the PWM Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWM output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

# 20.4 DAC

The range of the DAC is controlled through an analog multiplexer that selects either AVDD/2, an internal reference source, INTREF, or an external reference source, EXTREF. The full range of the DAC (AVDD/2) will typically be used when the chosen input source pin is shared with the ADC. The reduced range option (INTREF) will likely be used when monitoring current levels using a current sense resistor. Usually, the measured voltages in such applications are small (<1.25V); therefore the option of using a reduced reference range for the comparator extends the available DAC resolution in these applications. The use of an external reference enables the user to connect to a reference that better suits their application.

DACOUT, shown in Figure 20-1, can only be associated with a single comparator at a given time.

Note: It should be ensured in software that multiple DACOE bits are not set. The output on the DACOUT pin will be indeterminate if multiple comparators enable the DAC output.

### 20.5 Interaction with I/O Buffers

If the comparator module is enabled and a pin has been selected as the source for the comparator, then the chosen I/O pad must disable the digital input buffer associated with the pad to prevent excessive currents in the digital buffer due to analog input voltages.

# 20.6 Digital Logic

The CMPCONx register (see Register 20-1) provides the control logic that configures the comparator module. The digital logic provides a glitch filter for the comparator output to mask transient signals in less than two instruction cycles. In Sleep or Idle mode, the glitch filter is bypassed to enable an asynchronous path from the comparator to the interrupt controller. This asynchronous path can be used to wake-up the processor from Sleep or Idle mode.

The comparator can be disabled while in Idle mode if the CMPSIDL bit is set. If a device has multiple comparators, if any CMPSIDL bit is set, then the entire group of comparators will be disabled while in Idle mode. This behavior reduces complexity in the design of the clock control logic for this module.

The digital logic also provides a one TCY width pulse generator for triggering the ADC and generating interrupt requests.

The CMPDACx (see Register 20-2) register provides the digital input value to the reference DAC.

If the module is disabled, the DAC and comparator are disabled to reduce power consumption.

# 20.7 Comparator Input Range

The comparator has a limitation for the input Common-Mode Range (CMR) of (AVDD - 1.5V), typical. This means that both inputs should not exceed this range. As long as one of the inputs is within the Common-Mode Range, the comparator output will be correct. However, any input exceeding the CMR limitation will cause the comparator input to be saturated.

If both inputs exceed the CMR, the comparator output will be indeterminate.

# 20.8 DAC Output Range

The DAC has a limitation for the maximum reference voltage input of (AVDD - 1.6) volts. An external reference voltage input should not exceed this value or the reference DAC output will become indeterminate.

# 20.9 Comparator Registers

The comparator module is controlled by the following registers:

- CMPCONx: Comparator Control x Register

- CMPDACx: Comparator DAC x Control Register

#### TABLE 24-19: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

| АС СНА                                                          | RACTERISTICS   |     | d Operating temper |     | -40°0 | <b>3.0V to 3.6V (unless ot</b> $C \le TA \le +85^{\circ}C$ for indus $C \le TA \le +125^{\circ}C$ for Exte | trial          |

|-----------------------------------------------------------------|----------------|-----|--------------------|-----|-------|------------------------------------------------------------------------------------------------------------|----------------|

| Param<br>No.                                                    | Characteristic | Min | Тур                | Max | Units | Conditions                                                                                                 |                |

| Internal FRC Accuracy @ FRC Frequency = 7.37 MHz <sup>(1)</sup> |                |     |                    |     |       |                                                                                                            |                |

| F20a                                                            | FRC            | -2  | _                  | +2  | %     | $\text{-40°C} \leq \text{TA} \leq \text{+85°C}$                                                            | VDD = 3.0-3.6V |

| F20b                                                            | FRC            | -5  | _                  | +5  | %     | $-40^{\circ}C \leq TA \leq +125^{\circ}C$                                                                  | VDD = 3.0-3.6V |

Note 1: Frequency calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

### TABLE 24-20: AC CHARACTERISTICS: INTERNAL LPRC ACCURACY

| AC CH                            | ARACTERISTICS  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                                                       |                |

|----------------------------------|----------------|------------------------------------------------------|-----|-----|-------|-------------------------------------------------------|----------------|

| Param<br>No.                     | Characteristic | Min                                                  | Тур | Max | Units | Conditions                                            |                |

| LPRC @ 32.768 kHz <sup>(1)</sup> |                |                                                      |     |     |       |                                                       |                |

| F21a                             | LPRC           | -20                                                  | ±6  | +20 | %     | $\textbf{-40°C} \leq \textbf{TA} \leq \textbf{+85°C}$ | VDD = 3.0-3.6V |

| F21b                             | LPRC           | -70                                                  |     | +70 | %     | $-40^{\circ}C \leq TA \leq +125^{\circ}C$             | VDD = 3.0-3.6V |

Note 1: Change of LPRC frequency as VDD changes.

| AC CHARACTERISTICS   |                                          |                                             | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)               | CKE | СКР | SMP |  |

| 15 MHz               | Table 24-31                              | —                                           | —                                                        | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | —                                        | Table 24-32                                 | —                                                        | 1   | 0,1 | 1   |  |

| 9 MHz                | —                                        | Table 24-33                                 | —                                                        | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 24-34                                              | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 24-35                                              | 1   | 1   | 0   |  |

| 15 MHz               | —                                        | —                                           | Table 24-36                                              | 0   | 1   | 0   |  |

| 11 MHz               |                                          | —                                           | Table 24-37                                              | 0   | 0   | 0   |  |

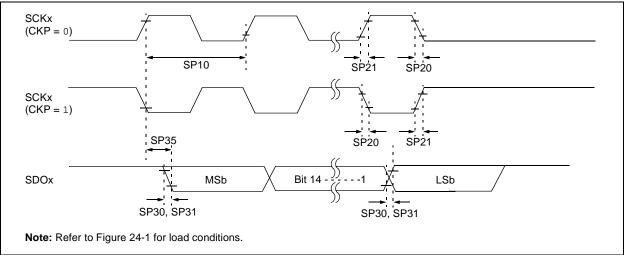

#### FIGURE 24-11: SPIx MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING **CHARACTERISTICS**

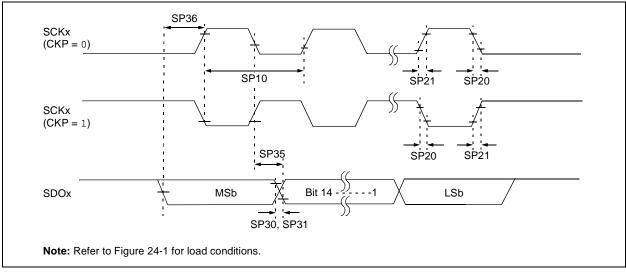

#### SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING FIGURE 24-12: **CHARACTERISTICS**

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

NOTES:

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

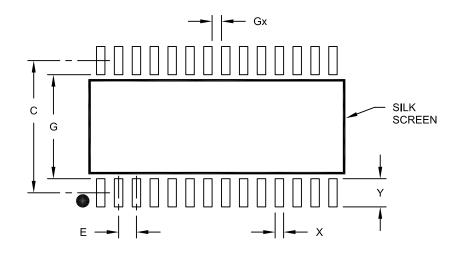

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | N                |      | s        |      |

|--------------------------|------------------|------|----------|------|

| Dimension                | Dimension Limits |      | NOM      | MAX  |

| Contact Pitch            | E                |      | 1.27 BSC |      |

| Contact Pad Spacing      | С                |      | 9.40     |      |

| Contact Pad Width (X28)  | X                |      |          | 0.60 |

| Contact Pad Length (X28) | Y                |      |          | 2.00 |

| Distance Between Pads    | Gx               | 0.67 |          |      |