Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

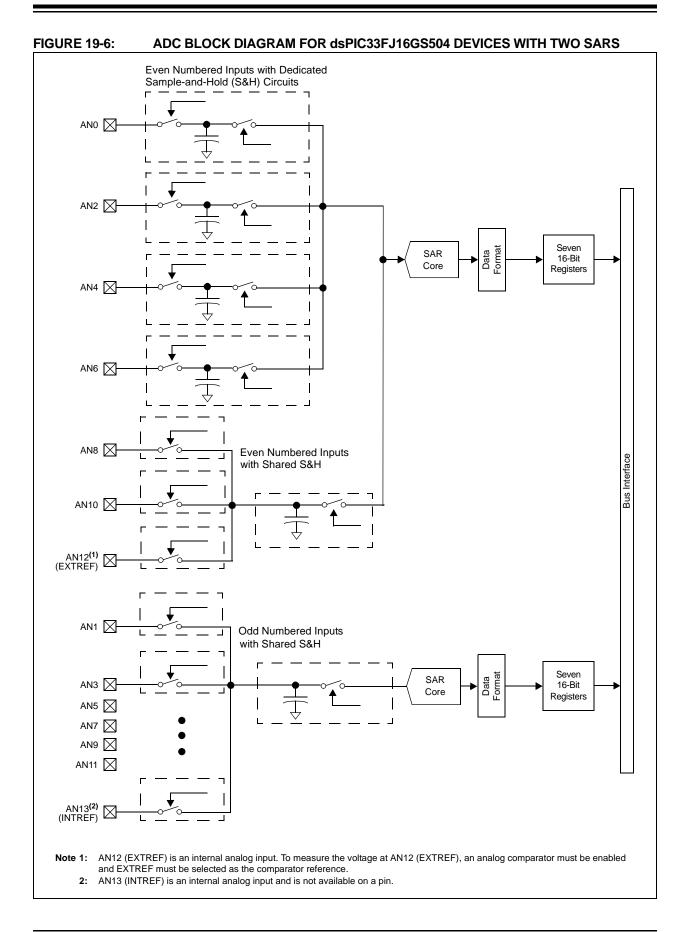

| Data Converters            | A/D 16x10b; D/A 4x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5 ICSP<sup>™</sup> Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

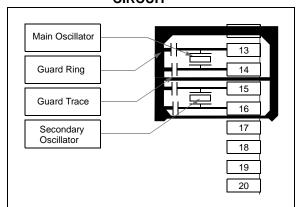

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < FIN < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV, and PLLFBD to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

#### 3.4 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| БA                 | ΒΛ                                          | R/C-0                                                           | R/C-0                      | D A               | R/C-0                | D 0                | R/W-0         |  |  |  |  |

|--------------------|---------------------------------------------|-----------------------------------------------------------------|----------------------------|-------------------|----------------------|--------------------|---------------|--|--|--|--|

| R-0                | R-0                                         | R/C-0<br>SA <sup>(1)</sup>                                      | R/C-0<br>SB <sup>(1)</sup> | R-0               | SAB <sup>(1,4)</sup> | R-0                |               |  |  |  |  |

| OA                 | OB                                          | SAW                                                             | SB(1)                      | OAB               | SAB                  | DA                 | DC            |  |  |  |  |

| bit 15             |                                             |                                                                 |                            |                   |                      |                    | bit 8         |  |  |  |  |

| R/W-0 <sup>(</sup> | 3) <sub>R/W-0</sub> (3)                     | R/W-0 <sup>(3)</sup>                                            | <b>D</b> 0                 | <b>D</b> 444 o    | <b>D</b> 444 0       | <b>D</b> 444 0     | DAVA          |  |  |  |  |

| IPL2 <sup>(2</sup> |                                             |                                                                 | R-0                        | R/W-0             | R/W-0                | R/W-0              | R/W-0         |  |  |  |  |

|                    | ) IPL1 <sup>(2)</sup>                       | IPL0 <sup>(2)</sup>                                             | RA                         | N                 | OV                   | Z                  | C             |  |  |  |  |

| bit 7              |                                             |                                                                 |                            |                   |                      |                    | bit 0         |  |  |  |  |

| Legend:            |                                             | C = Clearable                                                   | bit                        |                   |                      |                    |               |  |  |  |  |

| R = Reada          | able bit                                    | W = Writable                                                    | bit                        | -n = Value at     | POR                  | '1' = Bit is set   |               |  |  |  |  |

| 0' = Bit is        | cleared                                     | 'x = Bit is unk                                                 | nown                       | U = Unimplei      | mented bit, read     | l as '0'           |               |  |  |  |  |

|                    |                                             |                                                                 |                            | -                 |                      |                    |               |  |  |  |  |

| bit 15             | OA: Accumul                                 | lator A Overflov                                                | v Status bit               |                   |                      |                    |               |  |  |  |  |

|                    | 1 = Accumula                                | ator A has over                                                 | flowed                     |                   |                      |                    |               |  |  |  |  |

|                    | 0 = Accumula                                | ator A has not c                                                | verflowed                  |                   |                      |                    |               |  |  |  |  |

| bit 14             |                                             | lator B Overflov                                                |                            |                   |                      |                    |               |  |  |  |  |

|                    |                                             | ator B has over                                                 |                            |                   |                      |                    |               |  |  |  |  |

| L:40               |                                             | ator B has not c                                                |                            | н                 |                      |                    |               |  |  |  |  |

| bit 13             |                                             | ator A Saturation                                               | -                          |                   | acmo timo            |                    |               |  |  |  |  |

|                    |                                             | ator A is not sat                                               |                            | en saluraleu al   | some ume             |                    |               |  |  |  |  |

| bit 12             | SB: Accumul                                 | SB: Accumulator B Saturation 'Sticky' Status bit <sup>(1)</sup> |                            |                   |                      |                    |               |  |  |  |  |

|                    |                                             | ator B is saturat                                               |                            |                   | some time            |                    |               |  |  |  |  |

|                    | 0 = Accumula                                | ator B is not sat                                               | urated                     |                   |                      |                    |               |  |  |  |  |

| bit 11             | <b>OAB:</b> OA    C                         | OB Combined A                                                   | ccumulator O               | verflow Status    | bit                  |                    |               |  |  |  |  |

|                    |                                             | ator A or B has<br>accumulator A o                              |                            | owed              |                      |                    |               |  |  |  |  |

| bit 10             | <b>SAB:</b> SA    S                         | B Combined Ad                                                   | cumulator 'Si              | ticky' Status bit | (1,4)                |                    |               |  |  |  |  |

|                    |                                             | ator A or B is sa<br>accumulator A o                            |                            |                   | ed at some time      | in the past        |               |  |  |  |  |

| bit 9              | DA: DO Loop                                 | Active bit                                                      |                            |                   |                      |                    |               |  |  |  |  |

|                    | 1 = DO  loop in                             |                                                                 |                            |                   |                      |                    |               |  |  |  |  |

|                    |                                             | ot in progress                                                  |                            |                   |                      |                    |               |  |  |  |  |

| bit 8              |                                             | U Half Carry/Bo                                                 |                            |                   |                      |                    |               |  |  |  |  |

|                    | •                                           | out from the 4th sult occurred                                  | low-order bit (            | for byte-sized of | data) or 8th low-    | order bit (for wor | d-sized data) |  |  |  |  |

|                    | 0 = No carry                                |                                                                 |                            | oit (for byte-siz | ed data) or 8th      | low-order bit (fo  | or word-sized |  |  |  |  |

| Note 1:            | This bit can be rea                         | ad or cleared (n                                                | ot set).                   |                   |                      |                    |               |  |  |  |  |

| 2:                 | The IPL<2:0> bits<br>Level (IPL). The value | are concatenat                                                  | ed with the IF             |                   |                      |                    |               |  |  |  |  |

- IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

- 4: Clearing this bit will clear SA and SB.

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3          | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------|----------|----------|----------------|----------|----------|----------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | —        | MATHERR  | ADDRERR        | STKERR   | OSCFAIL  | _        | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     |          |          | _       |          | _        | _        | _        | _        | _        | _        | _              | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084        | _       | —        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | —        | T1IF           | OC1IF    | IC1IF    | INTOIF   | 0000          |

| IFS1         | 0086        | _       | _        | INT2IF   | _        | —       | _        | _        | _        | _        | _        | _        | INT1IF   | CNIF           | _        | MI2C1IF  | SI2C1IF  | 0000          |

| IFS3         | 008A        |         |          | _        | _        | _       | _        | PSEMIF   | _        | _        | _        | _        | _        | _              | _        | _        | _        | 0000          |

| IFS4         | 008C        |         |          | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _              | _        | U1EIF    | _        | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF   | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _              | _        | _        | _        | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _              | _        | _        | PWM3IF   | 0000          |

| IFS7         | 0092        | _       | _        | —        | _        | —       | _        | —        |          | —        | _        | —        | —        |                |          | ADCP3IF  | ADCP2IF  | 0000          |

| IEC0         | 0094        | -       | _        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | —        | T1IE           | OC1IE    | IC1IE    | INTOIE   | 0000          |

| IEC1         | 0096        | -       | _        | INT2IE   | —        | _       |          | —        |          | -        |          | —        | INT1IE   | CNIE           |          | MI2C1IE  | SI2C1IE  | 0000          |

| IEC3         | 009A        | -       | _        | —        | —        | _       |          | PSEMIE   |          | -        |          | —        | _        |                |          |          | _        | 0000          |

| IEC4         | 009C        | -       | _        | —        | —        | _       |          | —        |          | -        |          | —        | _        |                |          | U1EIE    | _        | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE   | —        | —        | _       |          | —        |          | -        |          | —        | _        |                |          |          | _        | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  | —        | —        | _       |          | —        |          | -        |          | —        | _        |                |          |          | PWM3IE   | 0000          |

| IEC7         | 00A2        | -       | _        | —        | —        | _       |          | —        |          | -        |          | —        | _        |                |          | ADCP3IE  | ADCP2IE  | 0000          |

| IPC0         | 00A4        | -       | T1IP2    | T1IP1    | T1IP0    | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0   |                | INT0IP2  | INT0IP1  | INT0IP2  | 4444          |

| IPC1         | 00A6        | -       | T2IP2    | T2IP1    | T2IP0    | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0   |                |          |          | _        | 4440          |

| IPC2         | 00A8        | -       | U1RXIP2  | U1RXIP1  | U1RXIP0  | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 |                | T3IP2    | T3IP1    | T3IP0    | 4444          |

| IPC3         | 00AA        | _       | _        | —        | —        | _       | _        | -        |          | -        | ADIP2    | ADIP1    | ADIP0    |                | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC        | —       | CNIP2    | CNIP1    | CNIP0    | —       | _        | —        | _        | —        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | -              | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4044          |

| IPC5         | 00AE        | _       | _        | —        | —        | _       | _        | -        |          | -        |          | -        | -        |                | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC7         | 00B2        | —       | —        | —        | —        | —       | _        | —        | _        | —        | INT2IP2  | INT2IP1  | INT2IP0  | -              | -        | -        | —        | 0040          |

| IPC14        | 00C0        | —       | —        | —        | —        | —       | _        | —        | _        | —        | PSEMIP2  | PSEMIP1  | PSEMIP0  | -              | -        | -        | —        | 0040          |

| IPC16        | 00C4        | -       | _        | —        | —        | _       |          | —        |          | -        | U1EIP2   | U1EIP1   | U1EIP0   |                |          |          | _        | 0040          |

| IPC23        | 00D2        | _       | PWM2IP2  | PWM2IP1  | PWM2IP0  | —       | PWM1IP2  | PWM1IP1  | PWM1IP0  |          |          | —        |          | _              | _        |          | _        | 4400          |

| IPC24        | 00D4        | _       | —        | _        | —        | —       | _        | —        | —        | —        | _        | —        | —        | _              | PWM3IP2  | PWM3IP1  | PWM3IP0  | 0004          |

| IPC27        | 00DA        | _       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | —       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 |          |          | _        |          |                |          | -        | _        | 4400          |

| IPC28        | 00DC        | _       |          | _        | _        | —       |          | _        | _        | —        | ADCP3IP2 | ADCP3IP1 | ADCP3IP0 | _              | ADCP2IP2 | ADCP2IP1 | ADCP2IP0 | 0044          |

| INTTREG      | 00E0        | _       | _        | _        | _        | ILR3    | ILR2     | ILR1     | ILR0     | _        | VECNUM6  | VECNUM5  | VECNUM4  | <b>VECNUM3</b> | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

#### TABLE 4-8. INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33E.116GS402/404 DEVICES ONLY

Legend: x = unknown value on Reset, ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit |

|-------|----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                       |

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                                                                                            | U-0                                              | U-0                       | U-0              | U-0             | R/W-0           | R/W-0  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------|------------------|-----------------|-----------------|--------|--|--|

| ADCP1IF          | ADCP0IF                                                                                                                                                                                                                                                                                                                                          | _                                                | _                         | _                | _               | AC4IF           | AC3IF  |  |  |

| bit 15           |                                                                                                                                                                                                                                                                                                                                                  |                                                  |                           |                  |                 |                 | bit    |  |  |

| R/W-0            | U-0                                                                                                                                                                                                                                                                                                                                              | U-0                                              | U-0                       | U-0              | U-0             | R/W-0           | R/W-0  |  |  |

| AC2IF            | _                                                                                                                                                                                                                                                                                                                                                | _                                                | _                         | _                | _               | PWM4IF          | PWM3IF |  |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                  |                                                  |                           |                  |                 |                 | bit    |  |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                  |                                                  |                           |                  |                 |                 |        |  |  |

| R = Readable     | bit                                                                                                                                                                                                                                                                                                                                              | W = Writable                                     | bit                       | U = Unimplen     | nented bit, rea | ıd as '0'       |        |  |  |

| -n = Value at F  | POR                                                                                                                                                                                                                                                                                                                                              | '1' = Bit is set                                 |                           | '0' = Bit is cle | ared            | x = Bit is unkn | nown   |  |  |

| bit 15<br>bit 14 | <ul> <li>ADCP1IF: ADC Pair 1 Conversion Done Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>ADCP0IF: ADC Pair 0 Conversion Done Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                                  |                           |                  |                 |                 |        |  |  |

| bit 13-10        | •                                                                                                                                                                                                                                                                                                                                                | ted: Read as '                                   |                           |                  |                 |                 |        |  |  |

| bit 9            | 1 = Interrupt r                                                                                                                                                                                                                                                                                                                                  | g Comparator<br>equest has oc<br>equest has no   |                           | g Status bit     |                 |                 |        |  |  |

| bit 8            | AC3IF: Analo                                                                                                                                                                                                                                                                                                                                     | •                                                | 3 Interrupt Fla<br>curred | g Status bit     |                 |                 |        |  |  |

| bit 7            | 1 = Interrupt r                                                                                                                                                                                                                                                                                                                                  | g Comparator<br>equest has oc<br>equest has no   |                           | g Status bit     |                 |                 |        |  |  |

| bit 6-2          | •                                                                                                                                                                                                                                                                                                                                                | ted: Read as '                                   |                           |                  |                 |                 |        |  |  |

| bit 1            | <b>PWM4IF:</b> PW<br>1 = Interrupt r                                                                                                                                                                                                                                                                                                             | M4 Interrupt F<br>equest has oc<br>equest has no | lag Status bit<br>curred  |                  |                 |                 |        |  |  |

| bit 0            |                                                                                                                                                                                                                                                                                                                                                  | M3 Interrupt F<br>equest has oc<br>equest has no | curred                    |                  |                 |                 |        |  |  |

#### REGISTER 7-10: IFS6: INTERRUPT FLAG STATUS REGISTER 6

#### 8.1 CPU Clocking System

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices provide six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Low-Power RC (LPRC) Oscillator

- FRC Oscillator with Postscaler

#### 8.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

The LPRC internal oscIllator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of

output frequencies for device operation. PLL configuration is described in **Section 8.1.3 "PLL Configuration"**.

The FRC frequency depends on the FRC accuracy (see Table 24-20) and the value of the FRC Oscillator Tuning register (see Register 8-4).

#### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 21.1 "Configuration Bits"** for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected), FOSC, is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device and speeds up to 40 MHz are supported by the dsPIC33FJ06GS101/ X02 and dsPIC33FJ16GSX02/X04 architecture.

Instruction execution speed or device operating frequency, Fcy, is given by Equation 8-1.

#### EQUATION 8-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

#### TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                 | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Notes |

|-------------------------------------------------|-------------------|-------------|------------|-----------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal          | xx          | 111        | 1, 2      |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal          | xx          | 110        | 1         |

| Low-Power RC Oscillator (LPRC)                  | Internal          | xx          | 101        | 1         |

| Reserved                                        | Reserved          | xx          | 100        | —         |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary           | 10          | 011        | _         |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary           | 01          | 011        | —         |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary           | 00          | 011        | 1         |

| Primary Oscillator (HS)                         | Primary           | 10          | 010        | —         |

| Primary Oscillator (XT)                         | Primary           | 01          | 010        | —         |

| Primary Oscillator (EC)                         | Primary           | 00          | 010        | 1         |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal          | xx          | 001        | 1         |

| Fast RC Oscillator (FRC)                        | Internal          | xx          | 000        | 1         |

**Note 1:** OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

|               |             |                  | -              |                  | -                |                |           |

|---------------|-------------|------------------|----------------|------------------|------------------|----------------|-----------|

| U-0           | U-0         | U-0              | U-0            | U-0              | U-0              | U-0            | R/W-0     |

|               |             | —                |                | —                | —                | —              | PLLDIV<8> |

| bit 15        |             |                  |                |                  |                  |                | bit 8     |

| R/W-0         | R/W-0       | R/W-1            | R/W-1          | R/W-0            | R/W-0            | R/W-0          | R/W-0     |

| 10000         | 10,00 0     |                  |                | IV<7:0>          | 1000 0           | 10000          | 1010 0    |

| bit 7         |             |                  |                |                  |                  |                | bit 0     |

| Legend:       |             |                  |                |                  |                  |                |           |

| R = Readabl   | le bit      | W = Writable     | bit            | U = Unimpler     | mented bit, read | l as '0'       |           |

| -n = Value at |             | '1' = Bit is set |                | '0' = Bit is cle |                  | x = Bit is unl | nown      |

|               |             |                  |                |                  |                  |                |           |

| bit 15-9      | Unimplemen  | ted: Read as '   | י'             |                  |                  |                |           |

| bit 8-0       | PLLDIV<8:0> | >: PLL Feedbac   | k Divisor bits | (also denoted    | as 'M', PLL mu   | ltiplier)      |           |

|               | 111111111 = | = 513            |                |                  |                  |                |           |

|               | •           |                  |                |                  |                  |                |           |

|               | •           |                  |                |                  |                  |                |           |

|               | •           |                  |                |                  |                  |                |           |

|               | 000110000=  | = 50 (default)   |                |                  |                  |                |           |

|               | •           |                  |                |                  |                  |                |           |

|               | •           |                  |                |                  |                  |                |           |

|               | •           |                  |                |                  |                  |                |           |

|               | 000000010=  | = 4              |                |                  |                  |                |           |

|               | 000000001 = |                  |                |                  |                  |                |           |

|               | 000000000 = | = 2              |                |                  |                  |                |           |

|               |             |                  |                |                  |                  |                |           |

## REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

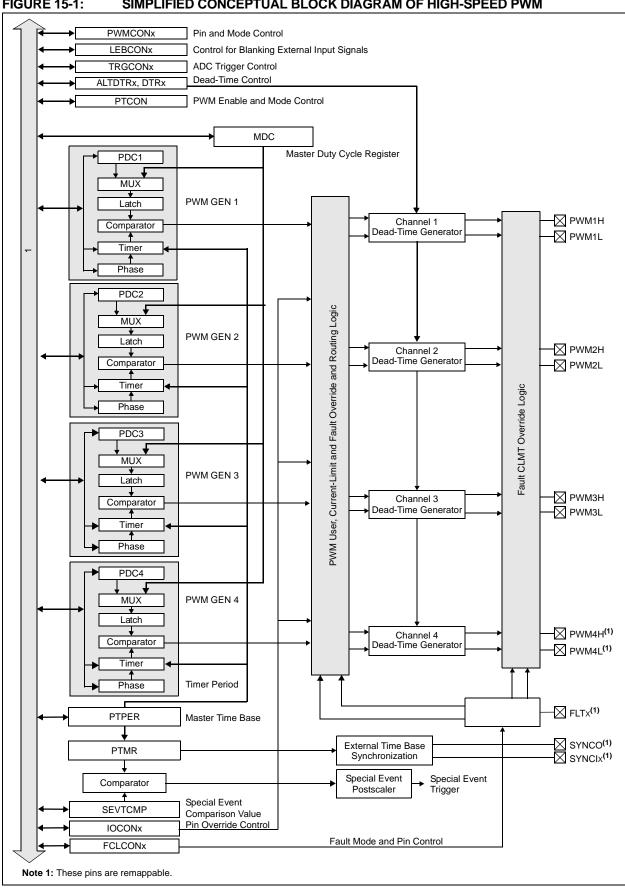

**FIGURE 15-1:** SIMPLIFIED CONCEPTUAL BLOCK DIAGRAM OF HIGH-SPEED PWM

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0   | U-0          | U-0   |

|--------|-----|-----|-----|-----|-------|--------------|-------|

| —      | —   | —   | —   | —   | —     | —            | —     |

| bit 15 | -   |     |     |     |       | •            | bit 8 |

|        |     |     |     |     |       |              |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0        | R/W-0 |

| _      | —   | —   | _   | _   | P     | CLKDIV<2:0>( | 1)    |

| bit 7  |     |     | •   |     |       |              | bit 0 |

|        |     |     |     |     |       |              |       |

#### REGISTER 15-2: PTCON2: PWM CLOCK DIVIDER SELECT REGISTER

## Γ.

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

- bit 2-0 PCLKDIV<2:0>: PWM Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64, maximum PWM timing resolution

- 101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

- Note 1: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will vield unpredictable results.

#### REGISTER 15-3: PTPER: PWM MASTER TIME BASE REGISTER<sup>(1)</sup>

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | PTPE  | R <15:8>                                |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | PTPE  | R <7:0>                                 |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

#### bit 15-0 PTPER<15:0>: PWM Master Time Base (PMTMR) Period Value bits

Note 1: The minimum value that can be loaded into the PTPER register is 0x0010 and the maximum value is 0xFFF8.

| R/W-0                                 | U-0                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                           | U-0                                                                      | U-0                    | U-0             | U-0                              | U-0          |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------|-----------------|----------------------------------|--------------|--|--|

| SPIEN                                 | _                                                                                                                                                                                                                                                                                                                                                           | SPISIDL                                                                                                         | —                                                                        | —                      |                 | —                                | —            |  |  |

| bit 15                                |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |                                                                          |                        |                 |                                  | bit 8        |  |  |

| U-0                                   | R/C-0                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                                                             | U-0                                                                      | U-0                    | U-0             | R-0                              | R-0          |  |  |

|                                       | SPIROV                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                               | —                                                                        | _                      |                 | SPITBF                           | SPIRBF       |  |  |

| bit 7                                 |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |                                                                          |                        |                 |                                  | bit 0        |  |  |

| Legend:                               |                                                                                                                                                                                                                                                                                                                                                             | C = Clearable                                                                                                   | bit                                                                      |                        |                 |                                  |              |  |  |

| R = Readab                            | ole bit                                                                                                                                                                                                                                                                                                                                                     | W = Writable I                                                                                                  | oit                                                                      | U = Unimpler           | nented bit, rea | d as '0'                         |              |  |  |

| -n = Value a                          | at POR                                                                                                                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                                                |                                                                          | '0' = Bit is cle       | ared            | x = Bit is unkr                  | nown         |  |  |

| bit 14<br>bit 13<br>bit 12-7<br>bit 6 | 0 = Disables<br>Unimplemen<br>SPISIDL: SPI<br>1 = Discontin<br>0 = Continues<br>Unimplemen<br>SPIROV: SPI                                                                                                                                                                                                                                                   | ted: Read as '(<br>Ix Stop in Idle M<br>ues module opera<br>s module opera<br>ted: Read as '(<br>x Receive Over | )'<br>lode bit<br>eration when<br>tion in Idle mo<br>)'<br>flow Flag bit | device enters I<br>ode | dle mode        |                                  |              |  |  |

|                                       | previous<br>0 = No overfl                                                                                                                                                                                                                                                                                                                                   | data in the SPI<br>low has occurre                                                                              | xBUF registe                                                             |                        | arded. The use  | er software has                  | not read the |  |  |

| bit 5-2                               | •                                                                                                                                                                                                                                                                                                                                                           | ted: Read as '0                                                                                                 |                                                                          |                        |                 |                                  |              |  |  |

| bit 1                                 | <ul> <li>SPITBF: SPIx Transmit Buffer Full Status bit</li> <li>1 = Transmit not yet started, SPIxTXB is full</li> <li>0 = Transmit started, SPIxTXB is empty. Automatically set in hardware when CPU writes the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.</li> </ul> |                                                                                                                 |                                                                          |                        |                 |                                  |              |  |  |

| bit 0                                 | 1 = Receive<br>0 = Receive<br>data from                                                                                                                                                                                                                                                                                                                     |                                                                                                                 | RXB is full<br>, SPIxRXB is<br>IxRXB. Auton                              | empty. Autom           |                 | hardware when<br>when core reads |              |  |  |

#### REGISTER 16-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

| U-0                 | U-0                              | U-0                                | R/W-0                               | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |  |

|---------------------|----------------------------------|------------------------------------|-------------------------------------|----------------------------------------|----------------------|----------------------|----------------------|--|--|--|--|--|

| _                   | _                                | _                                  | DISSCK                              | DISSDO                                 | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |  |  |

| pit 15              |                                  |                                    |                                     |                                        |                      |                      | bit                  |  |  |  |  |  |

| R/W-0               | R/W-0                            | R/W-0                              | R/W-0                               | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |  |

| SSEN <sup>(3)</sup> | CKP                              | MSTEN                              | SPRE2 <sup>(2)</sup>                | SPRE1 <sup>(2)</sup>                   | SPRE0 <sup>(2)</sup> | PPRE1 <sup>(2)</sup> | PPRE0 <sup>(2)</sup> |  |  |  |  |  |

| bit 7               | CI                               | MOTEN                              | SI KLZ.                             | SFILL IV                               | SINLO                |                      | bit                  |  |  |  |  |  |

| 51(7)               |                                  |                                    |                                     |                                        |                      |                      |                      |  |  |  |  |  |

| Legend:             |                                  |                                    |                                     |                                        |                      |                      |                      |  |  |  |  |  |

| R = Readab          | le bit                           | W = Writable                       | bit                                 | U = Unimpler                           | mented bit, read     | d as '0'             |                      |  |  |  |  |  |

| n = Value a         | t POR                            | '1' = Bit is se                    | t                                   | '0' = Bit is cle                       | ared                 | x = Bit is unkr      | nown                 |  |  |  |  |  |

| bit 15-13           | Unimplemen                       | ted: Read as                       | ʻ0'                                 |                                        |                      |                      |                      |  |  |  |  |  |

| bit 12              | -                                |                                    |                                     | er modes only)                         |                      |                      |                      |  |  |  |  |  |

|                     |                                  | PI clock is dis<br>PI clock is ena | abled; pin func<br>abled            | tions as I/O                           |                      |                      |                      |  |  |  |  |  |

| bit 11              | DISSDO: Dis                      | DISSDO: Disable SDOx Pin bit       |                                     |                                        |                      |                      |                      |  |  |  |  |  |

|                     |                                  | is not used by is controlled by    |                                     | unctions as I/C                        | )                    |                      |                      |  |  |  |  |  |

| oit 10              | MODE16: Wo                       | ord/Byte Comn                      | nunication Sele                     | ect bit                                |                      |                      |                      |  |  |  |  |  |

|                     |                                  |                                    | -wide (16 bits)                     |                                        |                      |                      |                      |  |  |  |  |  |

|                     |                                  | cation is byte-                    |                                     |                                        |                      |                      |                      |  |  |  |  |  |

| oit 9               |                                  | ata Input Sam                      | ple Phase bit                       |                                        |                      |                      |                      |  |  |  |  |  |

|                     |                                  | a sampled at e                     | nd of data outp<br>hiddle of data o |                                        |                      |                      |                      |  |  |  |  |  |

|                     | Slave mode:                      | ·                                  |                                     | n Slave mode.                          |                      |                      |                      |  |  |  |  |  |

| bit 8               | CKE: SPIx CI                     | ock Edge Sele                      | ect bit <sup>(1)</sup>              |                                        |                      |                      |                      |  |  |  |  |  |

|                     |                                  |                                    |                                     |                                        |                      | lle clock state (    |                      |  |  |  |  |  |

| ait 7               |                                  |                                    | bit (Slave mo                       |                                        | OCK STATE TO ACTI    | ve clock state (     | see bit 6)           |  |  |  |  |  |

| bit 7               |                                  | select Enable<br>s used for Slav   |                                     |                                        |                      |                      |                      |  |  |  |  |  |

|                     |                                  |                                    |                                     | ntrolled by port                       | function             |                      |                      |  |  |  |  |  |

| bit 6               | CKP: Clock F                     | Polarity Select                    | bit                                 |                                        |                      |                      |                      |  |  |  |  |  |

|                     |                                  |                                    |                                     | ve state is a lov<br>e state is a higl |                      |                      |                      |  |  |  |  |  |

| oit 5               | MSTEN: Mas                       | ter Mode Enat                      | ole bit                             |                                        |                      |                      |                      |  |  |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo     |                                    |                                     |                                        |                      |                      |                      |  |  |  |  |  |

|                     | he CKE bit is not<br>FRMEN = 1). | used in the Fr                     | amed SPI mod                        | des. Program t                         | his bit to '0' for   | the Framed SF        | Pl modes             |  |  |  |  |  |

| -                   | o not set both pri               | mary and seco                      | ondary prescal                      | ers to a value                         | of 1:1.              |                      |                      |  |  |  |  |  |

|                     | bio bit must be al               | -                                  |                                     |                                        | -                    |                      |                      |  |  |  |  |  |

#### REGISTER 16-2: SPIxCON1: SPIx CONTROL REGISTER 1

- **3:** This bit must be cleared when FRMEN = 1.

#### © 2008-2014 Microchip Technology Inc.

|  | REGISTER 19-2: | ADSTAT: ANALOG-TO-DIGITAL STATUS REGISTER |

|--|----------------|-------------------------------------------|

|--|----------------|-------------------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | _   |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/C-0, HS |

|-------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| —     | P6RDY     | P5RDY     | P4RDY     | P3RDY     | P2RDY     | P1RDY     | P0RDY     |

| bit 7 |           |           |           |           |           |           | bit 0     |

| Legend:           | C = Clearable bit | HS = Hardware Settabl | le bit             |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                          |

|----------|-------------------------------------------------------------------------------------|

| bit 6    | P6RDY: Conversion Data for Pair 6 Ready bit                                         |

|          | Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. |

| bit 5    | P5RDY: Conversion Data for Pair 5 Ready bit                                         |

|          | Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. |

| bit 4    | P4RDY: Conversion Data for Pair 4 Ready bit                                         |

|          | Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. |

| bit 3    | P3RDY: Conversion Data for Pair 3 Ready bit                                         |

|          | Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. |

| bit 2    | P2RDY: Conversion Data for Pair 2 Ready bit                                         |

|          | Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. |

| bit 1    | P1RDY: Conversion Data for Pair 1 Ready bit                                         |

|          | Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. |

| bit 0    | PORDY: Conversion Data for Pair 0 Ready bit                                         |

|          | Bit is set when data is ready in buffer, cleared when a '0' is written to this bit. |

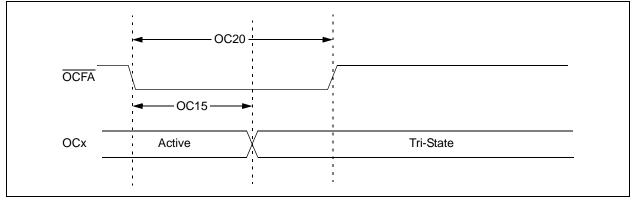

#### FIGURE 24-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 24-28: SIMPLE OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |          |     |          | 35°C for Industrial |            |

|--------------------|--------|-------------------------------------------------------|----------|-----|----------|---------------------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                         | Min      | Тур | Max      | Units               | Conditions |

| OC15               | Tfd    | Fault Input to PWMx I/O<br>Change                     | _        | _   | Tcy + 20 | ns                  |            |

| OC20               | TFLT   | Fault Input Pulse Width                               | Tcy + 20 | _   | —        | ns                  |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

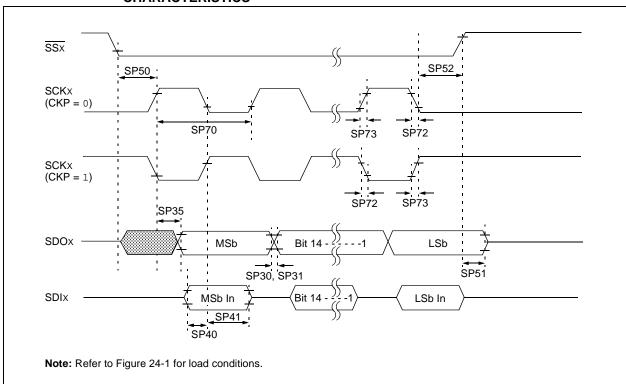

#### FIGURE 24-17: SPIX SLAVE MODE (FULL-DUPLEX CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

## 26.0 50 MIPS ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 electrical characteristics for devices operating at 50 MIPS.

The specifications for 50 MIPS are identical to those shown in **Section 24.0 "Electrical Characteristics"**, with the exception of the parameters listed in this section.

Parameters in this section begin with the letter "M", which denotes 50 MIPS operation. For example, Parameter DC29a in **Section 24.0** "Electrical Characteristics", is the up to 40 MIPS operation equivalent of MDC29a.

Absolute maximum ratings for the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 50 MIPS devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

#### Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                 | 40°C to +85°C  |

|--------------------------------------------------------------------------------|----------------|

| Storage temperature                                                            | 65°C to +150°C |

| Voltage on VDD with respect to Vss                                             | 0.3V to +4.0V  |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup> |                |

| Voltage on any 5V tolerant pin with respect to Vss, when Vdd $\geq 3.0V^{(3)}$ | 0.3V to +5.6V  |

| Voltage on any 5V tolerant pin with respect to Vss, when $VDD < 3.0V^{(3)}$    |                |

| Maximum current out of Vss pin                                                 |                |

| Maximum current into Vod pin <sup>(2)</sup>                                    | 250 mA         |

| Maximum current sourced/sunk by any 4x I/O pin                                 |                |

| Maximum current sourced/sunk by any 8x I/O pin                                 | 25 mA          |

| Maximum current sourced/sunk by any 16x I/O pin                                | 45 mA          |

| Maximum current sunk by all ports                                              | 200 mA         |

| Maximum current sourced by all ports <sup>(2)</sup>                            | 200mA          |

|                                                                                |                |

# **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

2: Maximum allowable current is a function of device maximum power dissipation (see Table 24-2).

**3:** See the **"Pin Diagrams"** section for 5V tolerant pins.

| TABLE A-1: | MAJOR SECTION UPDATES (CONTINUED) |

|------------|-----------------------------------|

|------------|-----------------------------------|

| Section Name             | Update Description                                                                                                                                                                                                                            |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 23.0 "Electrical | Updated Typ values for Thermal Packaging Characteristics (Table 23-3).                                                                                                                                                                        |

| Characteristics"         | Removed Typ value for DC Temperature and Voltage Specifications Parameter DC12 (Table 23-4).                                                                                                                                                  |

|                          | Updated all Typ values and conditions for DC Characteristics: Operating Current (IDD), updated last sentence in Note 2 (Table 23-5).                                                                                                          |

|                          | Updated all Typ values for DC Characteristics: Idle Current (IIDLE) (see Table 23-6).                                                                                                                                                         |

|                          | Updated all Typ values for DC Characteristics: Power Down Current (IPD) (see Table 23-7).                                                                                                                                                     |

|                          | Updated all Typ values for DC Characteristics: Doze Current (IDOZE) (see Table 23-8).                                                                                                                                                         |

|                          | Added Note 4 (reference to new table containing digital-only and analog pin information, as well as Current Sink/Source capabilities) in the I/O Pin Input Specifications (Table 23-9).                                                       |

|                          | Updated Max value for BOR electrical characteristics Parameter BO10 (see Table 23-11).                                                                                                                                                        |

|                          | Swapped Min and Typ values for Program Memory Parameters D136 and D137 (Table 23-12).                                                                                                                                                         |

|                          | Updated Typ values for Internal RC Accuracy Parameter F20 and added Extended temperature range to table heading (see Table 23-19).                                                                                                            |

|                          | Removed all values for Reset, Watchdog Timer, Oscillator Start-up Timer, and Power-up Timer Parameter SY20 and updated conditions, which now refers to <b>Section 20.4 "Watchdog Timer (WDT)</b> " and LPRC Parameter F21a (see Table 23-22). |

|                          | Added specifications to High-Speed PWM Module Timing Requirements for Tap Delay (Table 23-29).                                                                                                                                                |

|                          | Updated Min and Max values for 10-bit High-Speed Analog-to-Digital Module Parameters AD01 and AD11 (see Table 23-36).                                                                                                                         |

|                          | Updated Max value and unit of measure for DAC AC Specification (see Table 23-40).                                                                                                                                                             |

NOTES: