Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

XFI

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 21                                                                                 |

| Program Memory Size        | 16KB (16K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                              |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 28-VQFN Exposed Pad                                                                |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502t-50i-mm |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

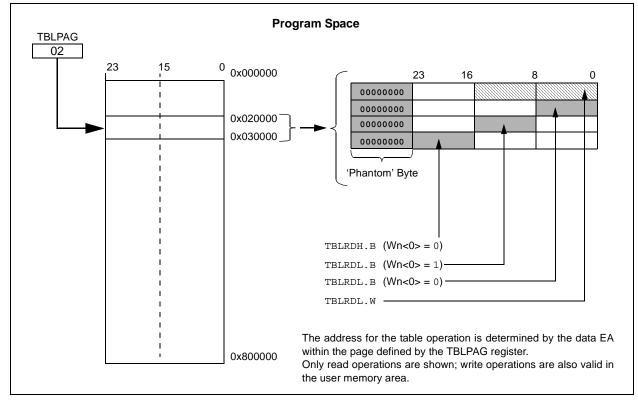

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

### FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| R/W-0         | R/W-0                               | U-0                                  | U-0           | U-0                   | U-0              | R/W-0             | R/W-0        |

|---------------|-------------------------------------|--------------------------------------|---------------|-----------------------|------------------|-------------------|--------------|

| TRAPR         | IOPUWR                              |                                      |               |                       |                  | СМ                | VREGS        |

| bit 15        |                                     |                                      |               |                       |                  |                   | bit 8        |

| DAMO          | DAM 0                               | DANO                                 | DAMO          | DAMO                  | D/M/ O           |                   |              |

| R/W-0         | R/W-0                               | R/W-0<br>SWDTEN <sup>(2)</sup>       | R/W-0         | R/W-0                 | R/W-0            | R/W-1             | R/W-1        |

| EXTR<br>bit 7 | SWR                                 | SWDIEN                               | WDTO          | SLEEP                 | IDLE             | BOR               | POR<br>bit ( |

|               |                                     |                                      |               |                       |                  |                   |              |

| Legend:       |                                     |                                      |               |                       |                  |                   |              |

| R = Readable  | e bit                               | W = Writable b                       | bit           | U = Unimpler          | nented bit, rea  | d as '0'          |              |

| -n = Value at | POR                                 | '1' = Bit is set                     |               | '0' = Bit is cle      | ared             | x = Bit is unk    | nown         |

| bit 15        | TRAPR: Trap                         | Reset Flag bit                       |               |                       |                  |                   |              |

|               | •                                   | onflict Reset has                    | s occurred    |                       |                  |                   |              |

|               | 0 = A Trap Co                       | onflict Reset has                    | s not occurre | d                     |                  |                   |              |

| bit 14        |                                     | gal Opcode or                        |               |                       | -                |                   |              |

|               | •                                   | l opcode detec                       |               | gal address mo        | ode or Uninitia  | lized W registe   | er used as a |

|               |                                     | Pointer caused<br>I opcode or Unit   |               | egister Reset h       | as not occurre   | d                 |              |

| bit 13-10     |                                     | ted: Read as '0                      |               | og.oto: 11000111      |                  | -                 |              |

| bit 9         | -                                   | ation Mismatch                       |               |                       |                  |                   |              |

|               | -                                   | uration Mismatc                      | -             | occurred              |                  |                   |              |

|               | 0 = A Configu                       | uration Mismatc                      | h Reset has   | NOT occurred          |                  |                   |              |

| bit 8         | VREGS: Volta                        | age Regulator S                      | Standby Durir | ng Sleep bit          |                  |                   |              |

|               |                                     | egulator is activ                    |               |                       |                  |                   |              |

| h:+ 7         | -                                   | egulator goes in                     | -             | node during Sie       | ер               |                   |              |

| bit 7         |                                     | nal Reset Pin (M<br>Clear (pin) Res  | ,             | rod                   |                  |                   |              |

|               |                                     | Clear (pin) Res                      |               |                       |                  |                   |              |

| bit 6         |                                     | re Reset Flag (                      |               |                       |                  |                   |              |

|               |                                     | instruction has                      |               |                       |                  |                   |              |

|               | 0 = A reset                         | instruction has                      | not been exe  | ecuted                |                  |                   |              |

| bit 5         | SWDTEN: So                          | oftware Enable/I                     | Disable of W  | DT bit <sup>(2)</sup> |                  |                   |              |

|               | 1 = WDT is e<br>0 = WDT is di       |                                      |               |                       |                  |                   |              |

| bit 4         |                                     | hdog Timer Tim                       | e-out Flag bi | it                    |                  |                   |              |

|               | 1 = WDT time                        | e-out has occuri<br>e-out has not oc | ed            |                       |                  |                   |              |

| bit 3         | SLEEP: Wak                          | e-up from Sleep                      | Flag bit      |                       |                  |                   |              |

|               |                                     | as been in Sleep                     | -             |                       |                  |                   |              |

|               | 0 = Device ha                       | as not been in S                     | leep mode     |                       |                  |                   |              |

| bit 2         |                                     | up from Idle Fla                     | g bit         |                       |                  |                   |              |

|               |                                     | as in Idle mode<br>as not in Idle m  | ode           |                       |                  |                   |              |

|               | of the Reset sta<br>use a device Re | atus bits can be                     |               | d in software. S      | etting one of th | nese bits in soft | ware does no |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-0        | R-0          | U-0                                       | U-0        | U-0              | U-0             | U-0             | U-0    |  |  |  |

|--------------|--------------|-------------------------------------------|------------|------------------|-----------------|-----------------|--------|--|--|--|

| ALTIVT       | DISI         | —                                         |            | _                | —               |                 |        |  |  |  |

| oit 15       |              |                                           |            |                  |                 |                 | bit 8  |  |  |  |

|              |              |                                           |            |                  |                 |                 |        |  |  |  |

| U-0          | U-0          | U-0                                       | U-0        | U-0              | R/W-0           | R/W-0           | R/W-0  |  |  |  |

| —            |              |                                           |            | —                | INT2EP          | INT1EP          | INT0EP |  |  |  |

| bit 7        |              |                                           |            |                  |                 |                 | bit C  |  |  |  |

|              |              |                                           |            |                  |                 |                 |        |  |  |  |

| Legend:      |              |                                           |            |                  |                 |                 |        |  |  |  |

| R = Readab   |              | W = Writable I                            | oit        | •                | mented bit, rea |                 |        |  |  |  |

| -n = Value a | POR          | '1' = Bit is set                          |            | '0' = Bit is cle | eared           | x = Bit is unkr | nown   |  |  |  |

|              |              |                                           |            |                  |                 |                 |        |  |  |  |

| bit 15       |              | able Alternate Int                        | •          | r Table bit      |                 |                 |        |  |  |  |

|              |              | ernate vector table<br>ndard (default) ve | -          |                  |                 |                 |        |  |  |  |

| bit 14       |              | Instruction Status                        |            |                  |                 |                 |        |  |  |  |

| DIT 14       |              | instruction Status                        |            |                  |                 |                 |        |  |  |  |

|              |              | struction is active                       |            |                  |                 |                 |        |  |  |  |

| bit 13-3     |              | ented: Read as '0                         |            |                  |                 |                 |        |  |  |  |

| bit 2        | -            | ternal Interrupt 2                        |            | t Polaritv Selec | t bit           |                 |        |  |  |  |

|              |              | t on negative edg                         | •          | ,,               |                 |                 |        |  |  |  |

|              |              | t on positive edge                        |            |                  |                 |                 |        |  |  |  |

| bit 1        | INT1EP: Ex   | ternal Interrupt 1                        | Edge Detec | t Polarity Selec | t bit           |                 |        |  |  |  |

|              |              | 1 = Interrupt on negative edge            |            |                  |                 |                 |        |  |  |  |

|              | 0 = Interrup | t on positive edge                        | Э          |                  |                 |                 |        |  |  |  |

| bit 0        |              | ternal Interrupt 0                        | •          | t Polarity Selec | t bit           |                 |        |  |  |  |

|              | •            | t on negative edg                         |            |                  |                 |                 |        |  |  |  |

|              | 0 – Interrun | t on positive edge                        | <b>`</b>   |                  |                 |                 |        |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0           | R/W-0                             | U-0               | U-0       | U-0                                      | U-0              | U-0      | U-0   |

|-----------------|-----------------------------------|-------------------|-----------|------------------------------------------|------------------|----------|-------|

| PWM2IE          | PWM1IE                            | —                 | _         | —                                        | —                | —        | _     |

| bit 15          |                                   |                   |           |                                          |                  |          | bit 8 |

|                 |                                   |                   |           |                                          |                  |          |       |

| U-0             | U-0                               | U-0               | U-0       | U-0                                      | U-0              | U-0      | U-0   |

| _               | —                                 | —                 |           | —                                        | —                | —        | —     |

| bit 7           |                                   |                   |           |                                          |                  |          | bit 0 |

|                 |                                   |                   |           |                                          |                  |          |       |

| Legend:         |                                   |                   |           |                                          |                  |          |       |

| R = Readable    | bit                               | W = Writable b    | oit       | U = Unimpler                             | mented bit, read | l as '0' |       |

| -n = Value at F | POR                               | '1' = Bit is set  |           | 0' = Bit is cleared $x = Bit is unknown$ |                  |          | own   |

|                 |                                   |                   |           |                                          |                  |          |       |

| bit 15          | PWM2IE: PV                        | /M2 Interrupt Er  | nable bit |                                          |                  |          |       |

|                 |                                   | request is enabl  |           |                                          |                  |          |       |

|                 | 0 = Interrupt                     | request is not ei | nabled    |                                          |                  |          |       |

| bit 14          | PWM1IE: PWM1 Interrupt Enable bit |                   |           |                                          |                  |          |       |

|                 | •                                 | request is enabl  |           |                                          |                  |          |       |

|                 | 0 = Interrupt                     | request is not ei | nabled    |                                          |                  |          |       |

| bit 13-0        | Unimplemen                        | ted: Read as '0   | )'        |                                          |                  |          |       |

|                 |                                   |                   |           |                                          |                  |          |       |

### REGISTER 7-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0              | R/W-1                                                                                  | R/W-0                                                                          | R/W-0                                                      | U-0               | R/W-1            | R/W-0           | R/W-0  |

|------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------|-------------------|------------------|-----------------|--------|

| _                | T2IP2                                                                                  | T2IP1                                                                          | T2IP0                                                      |                   | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15           | ·                                                                                      |                                                                                |                                                            |                   | •                | ·               | bit 8  |

|                  |                                                                                        | R/W-0                                                                          | R/W-0                                                      |                   |                  |                 |        |

| U-0              | R/W-1                                                                                  | 1                                                                              | 1                                                          | U-0               | U-0              | U-0             | U-0    |

| <br>bit 7        | IC2IP2                                                                                 | IC2IP1                                                                         | IC2IP0                                                     | —                 | —                | _               | bit    |

|                  |                                                                                        |                                                                                |                                                            |                   |                  |                 |        |

| Legend:          |                                                                                        |                                                                                |                                                            |                   |                  |                 |        |

| R = Readab       | le bit                                                                                 | W = Writable                                                                   | bit                                                        | U = Unimpler      | mented bit, read | d as '0'        |        |

| -n = Value a     | t POR                                                                                  | '1' = Bit is set                                                               |                                                            | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                  |                                                                                        |                                                                                |                                                            |                   |                  |                 |        |

| bit 15           | Unimplemer                                                                             | nted: Read as '                                                                | 0'                                                         |                   |                  |                 |        |

| bit 14-12        |                                                                                        | Timer2 Interrupt                                                               | •                                                          |                   |                  |                 |        |

|                  | 111 = Interru                                                                          | pt is Priority 7 (                                                             | highest priori                                             | ty interrupt)     |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                            |                   |                  |                 |        |

|                  | •                                                                                      |                                                                                |                                                            |                   |                  |                 |        |

|                  | 001 = Interru                                                                          | pt is Priority 1                                                               |                                                            |                   |                  |                 |        |

|                  | 000 = Interru                                                                          | pt source is dis                                                               | abled                                                      |                   |                  |                 |        |

| bit 11           | Unimplemer                                                                             | nted: Read as '                                                                | 0'                                                         |                   |                  |                 |        |

| bit 10-8         | OC2IP<2:0>                                                                             | : Output Compa                                                                 | are Channel 2                                              | 2 Interrupt Prior | ity bits         |                 |        |

|                  | 111 = Interru                                                                          | pt is Priority 7 (                                                             | highest priori                                             | ty interrunt)     |                  |                 |        |

|                  |                                                                                        |                                                                                | ingiloot phon                                              | ty interrupt)     |                  |                 |        |

|                  | •                                                                                      |                                                                                | ingridet priori                                            | ty interrupty     |                  |                 |        |

|                  | •<br>•                                                                                 |                                                                                | ingricet priori                                            | ty interrupty     |                  |                 |        |

|                  | •<br>•<br>001 = Interru                                                                | ipt is Priority 1                                                              | ingreet profi                                              | ty monopty        |                  |                 |        |

|                  |                                                                                        | ipt is Priority 1<br>ipt source is dis                                         |                                                            |                   |                  |                 |        |

| bit 7            | 000 = Interru                                                                          |                                                                                | abled                                                      |                   |                  |                 |        |

|                  | 000 = Interru<br>Unimplemer                                                            | pt source is dis                                                               | abled<br>0'                                                |                   | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br>nted: Read as '                                           | abled<br>0'<br>Channel 2 Inte                              | errupt Priority b | its              |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br><b>ted:</b> Read as '<br>Input Capture (                  | abled<br>0'<br>Channel 2 Inte                              | errupt Priority b | its              |                 |        |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                                             | ipt source is dis<br><b>ted:</b> Read as '<br>Input Capture (                  | abled<br>0'<br>Channel 2 Inte                              | errupt Priority b | its              |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•                  | ipt source is dis<br><b>ted:</b> Read as '<br>Input Capture (                  | abled<br>0'<br>Channel 2 Inte                              | errupt Priority b | its              |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru | ipt source is dis<br>nted: Read as '<br>Input Capture (<br>ipt is Priority 7 ( | abled<br><sup>0'</sup><br>Channel 2 Inte<br>highest priori | errupt Priority b | its              |                 |        |

## REGISTER 7-20: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| REGISTER 7-34: | IPC29: INTERRUPT PRIORITY CONTROL REGISTER 29 |

|----------------|-----------------------------------------------|

|----------------|-----------------------------------------------|

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0      | U-0      | U-0      |

|--------|-----|-----|-----|-----|----------|----------|----------|

| —      | —   | —   | —   | _   | —        | —        | —        |

| bit 15 |     |     |     |     |          |          | bit 8    |

|        |     |     |     |     |          |          |          |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1    | R/W-0    | R/W-0    |

| —      | —   | —   | —   | —   | ADCP6IP2 | ADCP6IP1 | ADCP6IP0 |

| bit 7  | •   |     |     |     |          |          | bit 0    |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

## bit 15-3 Unimplemented: Read as '0'

bit 2-0 ADCP6IP<2:0>: ADC Pair 6 Conversion Done Interrupt 1 Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| U-0          | U-0           | U-0                              | U-0             | R/W-0                                   | R/W-0           | R/W-0    | R/W-0    |  |  |

|--------------|---------------|----------------------------------|-----------------|-----------------------------------------|-----------------|----------|----------|--|--|

|              | —             | —                                |                 | CMP4MD                                  | CMP3MD          | CMP2MD   | CMP1MD   |  |  |

| bit 15       |               |                                  |                 |                                         |                 |          | bit      |  |  |

| U-0          | U-0           | U-0                              | U-0             | U-0                                     | U-0             | U-0      | U-0      |  |  |

| _            |               | <u> </u>                         |                 |                                         | _               | <u> </u> | <u> </u> |  |  |

| bit 7        |               |                                  |                 |                                         |                 |          | bit (    |  |  |

|              |               |                                  |                 |                                         |                 |          |          |  |  |

| Legend:      |               |                                  |                 |                                         |                 |          |          |  |  |

| R = Readab   | le bit        | W = Writable I                   | oit             | U = Unimplem                            | ented bit, read | l as '0' |          |  |  |

| -n = Value a | t POR         | '1' = Bit is set                 |                 | '0' = Bit is cleared x = Bit is unknown |                 |          |          |  |  |

|              |               |                                  |                 |                                         |                 |          |          |  |  |

| bit 15-12    | Unimplemen    | ted: Read as '0                  | )'              |                                         |                 |          |          |  |  |

| bit 11       | CMP4MD: An    | alog Comparat                    | or 4 Module D   |                                         |                 |          |          |  |  |

|              | 0             | omparator 4 mo                   |                 |                                         |                 |          |          |  |  |

|              | •             | omparator 4 mo                   |                 |                                         |                 |          |          |  |  |

| bit 10       |               | alog Comparat                    |                 |                                         |                 |          |          |  |  |

|              | Ų             | omparator 3 mo<br>omparator 3 mo |                 |                                         |                 |          |          |  |  |

| bit 9        | •             | alog Comparat                    |                 |                                         |                 |          |          |  |  |

|              | 1 = Analog Co | omparator 2 mo                   | dule is disable | ed                                      |                 |          |          |  |  |

|              | 0 = Analog Co | omparator 2 mo                   | dule is enable  | ed                                      |                 |          |          |  |  |

| bit 8        | CMP1MD: An    | alog Comparat                    | or 1 Module D   | isable bit                              |                 |          |          |  |  |

|              | •             | omparator 1 mo                   |                 |                                         |                 |          |          |  |  |

|              | C C           | omparator 1 mo                   |                 | ed                                      |                 |          |          |  |  |

| bit 7-0      | Unimplemen    |                                  |                 |                                         |                 |          |          |  |  |

#### REGISTER 9-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

| U-0                         | U-0          | U-0              | U-0           | U-0                                | U-0            | U-0                | U-0   |  |  |

|-----------------------------|--------------|------------------|---------------|------------------------------------|----------------|--------------------|-------|--|--|

| —                           | —            | _                | —             |                                    | —              | —                  | —     |  |  |

| bit 15                      |              |                  |               |                                    |                |                    | bit 8 |  |  |

|                             |              |                  |               |                                    |                |                    |       |  |  |

| U-0                         | U-0          | R/W-1            | R/W-1         | R/W-1                              | R/W-1          | R/W-1              | R/W-1 |  |  |

| _                           | _            | SS1R5            | SS1R4         | SS1R3                              | SS1R2          | SS1R1              | SS1R0 |  |  |

| bit 7                       |              |                  |               |                                    |                |                    | bit 0 |  |  |

|                             |              |                  |               |                                    |                |                    |       |  |  |

| Legend:                     |              |                  |               |                                    |                |                    |       |  |  |

| R = Readat                  | ole bit      | W = Writable     | bit           | U = Unimplemented bit, read as '0' |                |                    |       |  |  |

| -n = Value a                | at POR       | '1' = Bit is set |               | '0' = Bit is cleared               |                | x = Bit is unknown |       |  |  |

|                             |              |                  |               |                                    |                |                    |       |  |  |

| bit 15-6                    | Unimplemen   | ted: Read as '   | 0'            |                                    |                |                    |       |  |  |

| bit 5-0                     | SS1R<5:0>:   | Assign SPI1 SI   | ave Select In | put (SS1IN) to                     | the Correspond | ing RPn Pin bit    | S     |  |  |

|                             | 111111 = Inp | out tied to Vss  |               |                                    |                |                    |       |  |  |

|                             | 100011 = Inp | out tied to RP35 | 5             |                                    |                |                    |       |  |  |

|                             | 100010 = Inp | out tied to RP34 | 1             |                                    |                |                    |       |  |  |

|                             | 100001 = Inp | out tied to RP33 | 3             |                                    |                |                    |       |  |  |

| 100000 = Input tied to RP32 |              |                  | 2             |                                    |                |                    |       |  |  |

|                             | •            |                  |               |                                    |                |                    |       |  |  |

|                             | •            |                  |               |                                    |                |                    |       |  |  |

|                             | •            |                  |               |                                    |                |                    |       |  |  |

|                             |              |                  |               |                                    |                |                    |       |  |  |

## REGISTER 10-8: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

00000 = Input tied to RP0

| R = Readable bit W = Writable bit |     |        | bit    | U = Unimpler | nented bit, read | as '0' |        |

|-----------------------------------|-----|--------|--------|--------------|------------------|--------|--------|

| Legend:                           |     |        |        |              |                  |        |        |

|                                   |     |        |        |              |                  |        |        |

| bit 7                             | 1   |        |        |              |                  | •      | bit 0  |

|                                   | —   | RP22R5 | RP22R4 | RP22R3       | RP22R2           | RP22R1 | RP22R0 |

| U-0                               | U-0 | R/W-0  | R/W-0  | R/W-0        | R/W-0            | R/W-0  | R/W-0  |

|                                   |     |        |        |              |                  |        | 5110   |

| bit 15                            | •   |        | •      | •            |                  |        | bit 8  |

| _                                 | _   | RP23R5 | RP23R4 | RP23R3       | RP23R2           | RP23R1 | RP23R0 |

| U-0                               | U-0 | R/W-0  | R/W-0  | R/W-0        | R/W-0            | R/W-0  | R/W-0  |

# REGISTER 10-26: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11<sup>(1)</sup>

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP23R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP23 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP22R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP22 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

| U-0                                                                                                                                               | U-0   | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|--------|------------------------------------|--------|--------------------|--------|--|

| _                                                                                                                                                 | —     | RP25R5           | RP25R4 | RP25R3                             | RP25R2 | RP25R1             | RP25R0 |  |

| bit 15                                                                                                                                            |       |                  |        |                                    |        | •                  | bit 8  |  |

|                                                                                                                                                   |       |                  |        |                                    |        |                    |        |  |

| U-0                                                                                                                                               | U-0   | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |

| _                                                                                                                                                 | —     | RP24R5           | RP24R4 | RP24R3                             | RP24R2 | RP24R1             | RP24R0 |  |

| bit 7                                                                                                                                             |       | •                |        |                                    | •      | •                  | bit 0  |  |

|                                                                                                                                                   |       |                  |        |                                    |        |                    |        |  |

| Legend:                                                                                                                                           |       |                  |        |                                    |        |                    |        |  |

| R = Readabl                                                                                                                                       | e bit | W = Writable     | bit    | U = Unimplemented bit, read as '0' |        |                    |        |  |

| -n = Value at                                                                                                                                     | POR   | '1' = Bit is set |        | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |

|                                                                                                                                                   |       |                  |        |                                    |        |                    |        |  |

| bit 15-14 Unimplemented: Read as '0'                                                                                                              |       |                  |        |                                    |        |                    |        |  |

| bit 13-8 <b>RP25R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP25 Output Pin bits (see Table 10-2 for peripheral function numbers) |       |                  |        |                                    |        |                    |        |  |

| bit 7-6 Unimplemented: Read as '0'                                                                                                                |       |                  |        |                                    |        |                    |        |  |

| bit 5-0 <b>RP24R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP24 Output Pin bits (see Table 10-2 for peripheral function numbers)  |       |                  |        |                                    |        |                    |        |  |

|                                                                                                                                                   |       |                  |        |                                    |        |                    |        |  |

# **REGISTER 10-27:** RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12<sup>(1)</sup>

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

NOTES:

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

## 20.3 Module Applications

This module provides a means for the SMPS dsPIC<sup>®</sup> DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator and an associated 10-bit DAC that provides a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- Generate an Interrupt

- Trigger an ADC Sample and Convert Process

- Truncate the PWM Signal (current limit)

- Truncate the PWM Period (current minimum)

- Disable the PWM Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWM output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

## 20.4 DAC

The range of the DAC is controlled through an analog multiplexer that selects either AVDD/2, an internal reference source, INTREF, or an external reference source, EXTREF. The full range of the DAC (AVDD/2) will typically be used when the chosen input source pin is shared with the ADC. The reduced range option (INTREF) will likely be used when monitoring current levels using a current sense resistor. Usually, the measured voltages in such applications are small (<1.25V); therefore the option of using a reduced reference range for the comparator extends the available DAC resolution in these applications. The use of an external reference enables the user to connect to a reference that better suits their application.

DACOUT, shown in Figure 20-1, can only be associated with a single comparator at a given time.

Note: It should be ensured in software that multiple DACOE bits are not set. The output on the DACOUT pin will be indeterminate if multiple comparators enable the DAC output.

#### 20.5 Interaction with I/O Buffers

If the comparator module is enabled and a pin has been selected as the source for the comparator, then the chosen I/O pad must disable the digital input buffer associated with the pad to prevent excessive currents in the digital buffer due to analog input voltages.

## 20.6 Digital Logic

The CMPCONx register (see Register 20-1) provides the control logic that configures the comparator module. The digital logic provides a glitch filter for the comparator output to mask transient signals in less than two instruction cycles. In Sleep or Idle mode, the glitch filter is bypassed to enable an asynchronous path from the comparator to the interrupt controller. This asynchronous path can be used to wake-up the processor from Sleep or Idle mode.

The comparator can be disabled while in Idle mode if the CMPSIDL bit is set. If a device has multiple comparators, if any CMPSIDL bit is set, then the entire group of comparators will be disabled while in Idle mode. This behavior reduces complexity in the design of the clock control logic for this module.

The digital logic also provides a one TCY width pulse generator for triggering the ADC and generating interrupt requests.

The CMPDACx (see Register 20-2) register provides the digital input value to the reference DAC.

If the module is disabled, the DAC and comparator are disabled to reduce power consumption.

### 20.7 Comparator Input Range

The comparator has a limitation for the input Common-Mode Range (CMR) of (AVDD - 1.5V), typical. This means that both inputs should not exceed this range. As long as one of the inputs is within the Common-Mode Range, the comparator output will be correct. However, any input exceeding the CMR limitation will cause the comparator input to be saturated.

If both inputs exceed the CMR, the comparator output will be indeterminate.

### 20.8 DAC Output Range

The DAC has a limitation for the maximum reference voltage input of (AVDD - 1.6) volts. An external reference voltage input should not exceed this value or the reference DAC output will become indeterminate.

### 20.9 Comparator Registers

The comparator module is controlled by the following registers:

- CMPCONx: Comparator Control x Register

- CMPDACx: Comparator DAC x Control Register

|                                                              |              |                  |              |                                    |                   | <b>D</b> 444 a     | 5444.0         |  |

|--------------------------------------------------------------|--------------|------------------|--------------|------------------------------------|-------------------|--------------------|----------------|--|

| r-0                                                          | r-0          | r-0              | r-0          | r-0                                | r-0               | R/W-0              | R/W-0          |  |

| r                                                            | r            | r                | r            | r                                  | r                 | CMRE               | F<9:8>         |  |

| bit 15                                                       |              |                  |              |                                    |                   |                    | bit 8          |  |

| DAMO                                                         | DAA4 0       | DAALO            | <b>D M A</b> | <b>D</b> 444 0                     | DANIO             | DANA               | <b>D</b> 444 o |  |

| R/W-0                                                        | R/W-0        | R/W-0            | R/W-0        | R/W-0                              | R/W-0             | R/W-0              | R/W-0          |  |

|                                                              |              |                  | CMRE         | EF<7:0>                            |                   |                    |                |  |

| bit 7                                                        |              |                  |              |                                    |                   |                    | bit C          |  |

|                                                              |              |                  |              |                                    |                   |                    |                |  |

| Legend:                                                      |              | r = Reserved     | bit          |                                    |                   |                    |                |  |

| R = Readab                                                   | le bit       | W = Writable     | bit          | U = Unimplemented bit, read as '0' |                   |                    |                |  |

| -n = Value a                                                 | t POR        | '1' = Bit is set |              | '0' = Bit is cleared               |                   | x = Bit is unknown |                |  |

|                                                              |              |                  |              |                                    |                   |                    |                |  |

| bit 15-10                                                    | Reserved: Re | ead as '0'       |              |                                    |                   |                    |                |  |

| bit 9-0                                                      | CMREF<9:0>   | Comparator       | Reference Vo | Itage Select bit                   | s                 |                    |                |  |

|                                                              |              | •                |              | •                                  |                   | רייע (21/201) אר   | lts depending  |  |

| 1111111111 = (CMREF<9:0> * INTREF<br>on the RANGE bit or (CM |              |                  | , ,          | •                                  | , ,               |                    |                |  |

|                                                              | •            |                  |              |                                    | XIIXEI / 1024) II |                    | L              |  |

|                                                              | •            |                  |              |                                    |                   |                    |                |  |

|                                                              | •            |                  |              |                                    |                   |                    |                |  |

|                                                              | 0000000000   | = 0.0 volts      |              |                                    |                   |                    |                |  |

|                                                              |              |                  |              |                                    |                   |                    |                |  |

|                                                              |              |                  |              |                                    |                   |                    |                |  |

## REGISTER 20-2: CMPDACx: COMPARATOR DAC x CONTROL REGISTER

# 22.0 INSTRUCTION SET SUMMARY

**Note:** This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest sections in the "dsPIC33F/PIC24H Family Reference Manual", which are available on the Microchip web site (www.microchip.com).

The dsPIC33F instruction set is identical to that of the dsPIC30F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 22-1 shows the general symbols used in describing the instructions.

The dsPIC33F instruction set summary in Table 22-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value, 'f'

- The destination, which could be either the file register, 'f', or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register, 'Wn', or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

| AC CHARACTERISTICS |        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                |           |     |                    |     |       |                                |

|--------------------|--------|---------------------------------------------------------------------|-----------|-----|--------------------|-----|-------|--------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                      |           | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                     |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |           | 0.8 | _                  | 8   | MHz   | ECPLL, XTPLL modes             |

| OS51               | Fsys   | On-Chip VCO System<br>Frequency                                     |           | 100 | —                  | 200 | MHz   |                                |

| OS52               | TLOCK  | PLL Start-up Time (L                                                | ock Time) | 0.9 | 1.5                | 3.1 | mS    |                                |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                              |           | -3  | 0.5                | 3   | %     | Measured over 100 ms<br>period |

#### TABLE 24-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested in manufacturing.

2: These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

$$Peripheral Clock Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$

For example: FOSC = 32 MHz, DCLK = 3%, SPI bit rate clock (i.e., SCKx) is 2 MHz.

SPI SCK Jitter =

$$\left\lfloor \frac{D_{CLK}}{\sqrt{\left(\frac{32 \ MHz}{2 \ MHz}\right)}} \right\rfloor = \left\lfloor \frac{3\%}{\sqrt{16}} \right\rfloor = \left\lfloor \frac{3\%}{4} \right\rfloor = 0.75\%$$

#### TABLE 24-18: AUXILIARY PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| AC CHARACTERISTICS |        |                                                   | Standard (<br>Operating |     | ure -40°           | $C \le TA \le -$ | -85°C fo | u <b>nless otherwise stated)</b><br>r Industrial<br>or Extended |

|--------------------|--------|---------------------------------------------------|-------------------------|-----|--------------------|------------------|----------|-----------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                    |                         | Min | Typ <sup>(1)</sup> | Max              | Units    | Conditions                                                      |

| OS56               | Fhpout | On-Chip 16x PLL CCO<br>Frequency                  |                         | 112 | 118                | 120              | MHz      |                                                                 |

| OS57               | Fhpin  | On-Chip 16x PLL Phase<br>Detector Input Frequency |                         | 7.0 | 7.37               | 7.5              | MHz      |                                                                 |

| OS58               | Tsu    | Frequency Generator Lock<br>Time                  |                         |     | _                  | 10               | μs       |                                                                 |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested in manufacturing.

## 26.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 AC characteristics and timing parameters for 50 MIPS devices.

| AC CHARACTERISTICS |      |                                                                                    | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |     |       |            |  |

|--------------------|------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|

| Param<br>No.       | Symb | Characteristic                                                                     | Min                                                                                                                                             | Typ <sup>(1)</sup> | Мах | Units | Conditions |  |

| MOS10              | FIN  | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                              | _                  | 50  | MHz   | EC         |  |

|                    |      | Oscillator Crystal Frequency                                                       | 3.5                                                                                                                                             | —                  | 10  | MHz   | XT         |  |

|                    |      |                                                                                    | 10                                                                                                                                              | —                  | 50  | MHz   | HS         |  |

| MOS20              | Tosc | Tosc = 1/Fosc                                                                      | 10                                                                                                                                              | _                  | DC  | ns    |            |  |

| MOS25              | TCY  | Instruction Cycle Time <sup>(2)</sup>                                              | 20                                                                                                                                              | —                  | DC  | ns    |            |  |

## TABLE 26-5: EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: Instruction cycle period (Tcr) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

### TABLE 26-6: SIMPLE OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |          |       |            |

|--------------------|--------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min                                                                                                                                                     | Тур | Мах      | Units | Conditions |

| MOC15              | Tfd    | Fault Input to PWMx I/O<br>Change | _                                                                                                                                                       |     | Tcy + 10 | ns    |            |

| MOC20              | TFLT   | Fault Input Pulse Width           | Tcy + 10                                                                                                                                                | _   | —        | ns    |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

# TABLE A-4: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                              | Update Description                                                                                                                                            |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 26.0 "50 MIPS Electrical<br>Characteristics"      | Added new chapter in support of 50 MIPS devices.                                                                                                              |

| Section 27.0 "DC and AC Device<br>Characteristics Graphs" | Added new chapter.                                                                                                                                            |

| Section 28.0 "Packaging<br>Information"                   | Added 44-pin VTLA package marking information and diagrams (see Section 28.1 "Package Marking Information" and Section 28.2 "Package Details", respectively). |

| "Product Identification System"                           | Added the TL package definition.                                                                                                                              |

| IFS5 (Interrupt Flag Status 5)109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| IFS6 (Interrupt Flag Status 6)11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |