Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 21                                                                                 |

| Program Memory Size        | 16KB (16K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                              |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                     |

| Supplier Device Package    | 28-SOIC                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502t-50i-so |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

### © 2008-2014 Microchip Technology Inc.

#### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/ 16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (for example, ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- Signed or Unsigned DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation | ACC<br>Write Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

| TABLE 4-7: | INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06G202 DEVICES ONLY |

|------------|--------------------------------------------------------------------|

|------------|--------------------------------------------------------------------|

|              | 4-1.        |         |          |          |          |         |          |          | usric.   |          |                |          |          |         |          |          |               |               |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------------|----------|----------|---------|----------|----------|---------------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6          | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0         | All<br>Resets |

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | <b>DIV0ERR</b> | —        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | _             | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     | _        | _        | _       | _        | —        | _        | _        | _              | _        | _        | _       | INT2EP   | INT1EP   | INT0EP        | 0000          |

| IFS0         | 0084        | _       | _        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | -        | T2IF     | _              |          |          | T1IF    | OC1IF    | IC1IF    | <b>INTOIF</b> | 0000          |

| IFS1         | 0086        | _       | _        | INT2IF   | _        | _       | _        | _        | _        | _        | _              |          | INT1IF   | CNIF    | AC1IF    | MI2C1IF  | SI2C1IF       | 0000          |

| IFS3         | 008A        | _       | _        | _        | _        | -       | -        | PSEMIF   | _        | _        | _              |          |          | -       | _        | _        |               | 0000          |

| IFS4         | 008C        | _       | _        | _        | —        | _       | _        | _        | _        | —        | —              | _        | _        | _       | —        | U1EIF    | _             | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF   | _        | —        | _       | _        | _        | _        | —        | —              | _        | _        | _       | —        | _        | _             | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | —        | _       | _        | _        | _        | AC2IF    | _              | _        | _        | _       | _        | _        | _             | 0000          |

| IFS7         | 0092        | _       | _        | _        | _        | _       | _        | _        | _        | —        | _              | _        | ADCP6IF  | _       | _        | _        | ADCP2IF       | 0000          |

| IEC0         | 0094        | _       | _        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  |          | T2IE     | _              |          |          | T1IE    | OC1IE    | IC1IE    | INT0IE        | 0000          |

| IEC1         | 0096        | _       | _        | INT2IE   | —        | _       |          | —        |          | —        | _              |          | INT1IE   | CNIE    | AC1IE    | MI2C1IE  | SI2C1IE       | 0000          |

| IEC3         | 009A        | _       | _        |          | _        | _       |          | PSEMIE   |          | —        | _              |          |          |         | —        | _        | _             | 0000          |

| IEC4         | 009C        | _       | _        |          | _        | _       |          | —        |          | —        | _              |          |          |         | —        | U1EIE    | _             | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE   |          | _        | _       |          | —        |          | —        | _              |          |          |         | —        | _        | _             | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  |          | _        |         |          | _        |          | AC2IE    | _              |          |          |         | —        | _        |               | 0000          |

| IEC7         | 00A2        | _       |          |          | _        |         |          | _        |          | _        | _              |          | ADCP6IE  |         | —        | _        | ADCP2IE       | 0000          |

| IPC0         | 00A4        | _       | T1IP2    | T1IP1    | T1IP0    |         | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2         | IC1IP1   | IC1IP0   |         | INT0IP2  | INT0IP1  | INT0IP0       | 4444          |

| IPC1         | 00A6        | _       | T2IP2    | T2IP1    | T2IP0    |         |          | _        |          | _        | _              |          |          |         | —        | _        |               | 4000          |

| IPC2         | 00A8        | _       | U1RXIP2  | U1RXIP1  | U1RXIP0  |         | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2       | SPI1EIP1 | SPI1EIP0 |         | —        | _        |               | 4440          |

| IPC3         | 00AA        | _       |          |          | _        |         |          | _        |          | _        | ADIP2          | ADIP1    | ADIP0    |         | U1TXIP2  | U1TXIP1  | U1TXIP0       | 0044          |

| IPC4         | 00AC        | _       | CNIP2    | CNIP1    | CNIP0    |         | AC1IP2   | AC1IP1   | AC1IP0   | _        | MI2C1IP2       | MI2C1IP1 | MI2C1IP0 |         | SI2C1IP2 | SI2C1IP1 | SI2C1IP0      | 4444          |

| IPC5         | 00AE        | _       |          |          | _        |         |          | _        |          | _        | _              |          |          |         | INT1IP2  | INT1IP1  | INT1IP0       | 0004          |

| IPC7         | 00B2        | _       |          |          | _        |         |          | _        |          | _        | INT2IP2        | INT2IP1  | INT2IP0  |         | —        | _        |               | 0040          |

| IPC14        | 00C0        | _       |          |          | _        |         |          | _        |          | _        | PSEMIP2        | PSEMIP1  | PSEMIP0  |         | —        | _        |               | 0040          |

| IPC16        | 00C4        | _       |          |          | _        |         |          | _        |          | _        | U1EIP2         | U1EIP1   | U1EIP0   |         | —        | _        |               | 0040          |

| IPC23        | 00D2        | _       | PWM2IP2  | PWM2IP1  | PWM2IP0  |         | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | _              |          |          |         | —        | _        |               | 4400          |

| IPC25        | 00D6        | _       | AC2IP2   | AC2IP1   | AC2IP0   |         |          | _        |          | _        | _              |          |          |         | —        | _        |               | 4000          |

| IPC27        | 00DA        | —       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | —       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | —        | —              | —        | _        | _       | —        | —        | _             | 4400          |

| IPC28        | 00DC        | _       | _        |          | —        | -       |          | -        |          | —        | _              |          |          |         | ADCP2IP2 | ADCP2IP1 | ADCP2IP0      | 0004          |

| IPC29        | 00DE        |         | _        | _        | —        | _       | -        | _        | _        | _        | _              | —        | _        | _       | ADCP6IP2 | ADCP6IP1 | ADCP6IP0      | 0004          |

| INTTREG      | 00E0        | —       | _        | _        | —        | ILR3    | ILR2     | ILR1     | ILR0     | —        | VECNUM6        | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0       | 0000          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| dsPIC33FJ06GS101/X02  |

|-----------------------|

| 01/X02 and dsPIC33FJ1 |

| PIC33FJ16GS           |

| 116GSX02/X04          |

#### TABLE 4-18: HIGH-SPEED PWM GENERATOR 1 REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14             | Bit 13  | Bit 12  | Bit 11   | Bit 10  | Bit 9   | Bit 8  | Bit 7      | Bit 6      | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|--------------------|---------|---------|----------|---------|---------|--------|------------|------------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON1      | 0420        | FLTSTAT | CLSTAT             | TRGSTAT | FLTIEN  | CLIEN    | TRGIEN  | ITB     | MDCS   | DTC1       | DTC0       | —        | —        | —        | CAM      | XPRES    | IUE      | 0000          |

| IOCON1       | 0422        | PENH    | PENL               | POLH    | POLL    | PMOD1    | PMOD0   | OVRENH  | OVRENL | OVRDAT1    | OVRDAT0    | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON1      | 0424        | IFLTMOD | CLSRC4             | CLSRC3  | CLSRC2  | CLSRC1   | CLSRC0  | CLPOL   | CLMOD  | FLTSRC4    | FLTSRC3    | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC1         | 0426        |         |                    |         |         |          |         |         |        | PDC1<15:0: | >          |          |          |          |          |          |          | 0000          |

| PHASE1       | 0428        |         |                    |         |         |          |         |         | P      | HASE1<15:  | 0>         |          |          |          |          |          |          | 0000          |

| DTR1         | 042A        |         | _                  |         |         |          |         |         |        | Γ          | DTR1<13:0> |          |          |          |          |          |          | 0000          |

| ALTDTR1      | 042C        |         | ALTDTR1<13:0> 0000 |         |         |          |         |         |        |            | 0000       |          |          |          |          |          |          |               |

| SDC1         | 042E        |         |                    |         |         |          |         |         | ;      | SDC1<15:0: | >          |          |          |          |          |          |          | 0000          |

| SPHASE1      | 0430        |         |                    |         |         |          |         |         | SF     | PHASE1<15  | :0>        |          |          |          |          |          |          | 0000          |

| TRIG1        | 0432        |         |                    |         |         |          | ٦       | rrgcmp< | 15:3>  |            |            |          |          |          | —        | _        | _        | 0000          |

| TRGCON1      | 0434        | TRGDIV3 | TRGDIV2            | TRGDIV1 | TRGDIV0 | _        | —       | _       | _      | DTM        | _          | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG1       | 0436        |         |                    |         |         |          | S       | TRGCMP< | <15:3> |            |            |          |          |          | -        | _        |          | 0000          |

| PWMCAP1      | 0438        |         |                    |         |         |          | Р       | WMCAP1< | <15:3> |            |            |          |          |          | _        | _        |          | 0000          |

| LEBCON1      | 043A        | PHR     | PHF                | PLR     | PLF     | FLTLEBEN | CLLEBEN | LEB6    | LEB5   | LEB4       | LEB3       | LEB2     | LEB1     | LEB0     |          |          |          | 0000          |

| Legend:      |             |         |                    |         |         |          |         |         |        |            |            |          |          |          |          |          |          |               |

#### TABLE 4-19: HIGH-SPEED PWM GENERATOR 2 REGISTER MAP FOR dsPIC33FJ06GS102/202 AND dsPIC33FJ16GSX02/X04 DEVICES ONLY

|         | SFR<br>Addr | Bit 15  | Bit 14           | Bit 13            | Bit 12  | Bit 11   | Bit 10  | Bit 9   | Bit 8  | Bit 7     | Bit 6       | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|---------|-------------|---------|------------------|-------------------|---------|----------|---------|---------|--------|-----------|-------------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2 | 0440        | FLTSTAT | CLSTAT           | TRGSTAT           | FLTIEN  | CLIEN    | TRGIEN  | ITB     | MDCS   | DTC1      | DTC0        |          | _        | _        | CAM      | XPRES    | IUE      | 0000          |

| IOCON2  | 0442        | PENH    | PENL             | POLH              | POLL    | PMOD1    | PMOD0   | OVRENH  | OVRENL | OVRDAT1   | OVRDAT0     | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON2 | 0444        | IFLTMOD | CLSRC4           | CLSRC3            | CLSRC2  | CLSRC1   | CLSRC0  | CLPOL   | CLMOD  | FLTSRC4   | FLTSRC3     | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC2    | 0446        |         |                  |                   |         |          |         |         |        | PDC2<15:0 | >           |          |          |          |          |          |          | 0000          |

| PHASE2  | 0448        |         | PHASE2<15:0> 000 |                   |         |          |         |         |        |           | 0000        |          |          |          |          |          |          |               |

| DTR2    | 044A        | _       | _                | - DTR2<13:0> 0000 |         |          |         |         |        |           | 0000        |          |          |          |          |          |          |               |

| ALTDTR2 | 044C        | _       | _                |                   |         |          |         |         |        | AL        | .TDTR2<13:( | )>       |          |          |          |          |          | 0000          |

| SDC2    | 044E        |         |                  |                   |         |          |         |         |        | SDC2<15:0 | >           |          |          |          |          |          |          | 0000          |

| SPHASE2 | 0450        |         |                  |                   |         |          |         |         | SI     | PHASE2<15 | :0>         |          |          |          |          |          |          | 0000          |

| TRIG2   | 0452        |         |                  |                   |         |          |         | TRGCMP< | :15:3> |           |             |          |          |          | _        | _        | —        | 0000          |

| TRGCON2 | 0454        | TRGDIV3 | TRGDIV2          | TRGDIV1           | TRGDIV0 | _        | —       | _       | _      | DTM       | _           | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| STRIG2  | 0456        |         |                  |                   |         |          | 5       | STRGCMP | <15:3> |           |             |          |          |          | _        | —        | _        | 0000          |

| PWMCAP2 | 0458        |         |                  |                   |         |          | F       | WMCAP2  | <15:3> |           |             |          |          |          |          | _        | _        | 0000          |

| LEBCON2 | 045A        | PHR     | PHF              | PLR               | PLF     | FLTLEBEN | CLLEBEN | LEB6    | LEB5   | LEB4      | LEB3        | LEB2     | LEB1     | LEB0     | -        | _        | _        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

# FIGURE 7-1: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 INTERRUPT VECTOR TABLE

|                                   |                             | -         |                                                        |

|-----------------------------------|-----------------------------|-----------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction    | 0x000000  |                                                        |

|                                   | Reset – GOTO Address        | 0x000002  |                                                        |

|                                   | Reserved                    | 0x000004  |                                                        |

|                                   | Oscillator Fail Trap Vector |           |                                                        |

|                                   | Address Error Trap Vector   |           |                                                        |

|                                   | Stack Error Trap Vector     |           |                                                        |

|                                   | Math Error Trap Vector      |           |                                                        |

|                                   | Reserved                    |           |                                                        |

|                                   | Reserved                    |           |                                                        |

|                                   | Reserved                    |           |                                                        |

|                                   | Interrupt Vector 0          | 0x000014  |                                                        |

|                                   | Interrupt Vector 1          |           |                                                        |

|                                   | ~                           |           |                                                        |

|                                   | ~                           |           |                                                        |

|                                   | ~                           |           |                                                        |

|                                   | Interrupt Vector 52         | 0x00007C  | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

|                                   | Interrupt Vector 53         | 0x00007E  |                                                        |

| rity                              | Interrupt Vector 54         | 0x000080  |                                                        |

| Jric                              | ~                           |           |                                                        |

| ж<br>Н                            | ~                           |           |                                                        |

| rde                               | ~                           |           |                                                        |

| 0                                 | Interrupt Vector 116        | 0x0000FC  |                                                        |

| nra                               | Interrupt Vector 117        | 0x0000FE  |                                                        |

| Decreasing Natural Order Priority | Reserved                    | 0x000100  |                                                        |

| l b                               | Reserved                    | 0x000102  |                                                        |

| asir                              | Reserved                    | _         |                                                        |

| rea                               | Oscillator Fail Trap Vector | _         |                                                        |

| Dec                               | Address Error Trap Vector   | _         |                                                        |

|                                   | Stack Error Trap Vector     | _         |                                                        |

|                                   | Math Error Trap Vector      | -         |                                                        |

|                                   | Reserved                    |           | 1                                                      |

|                                   | Reserved                    | _         |                                                        |

|                                   | Reserved                    | 00001111  |                                                        |

|                                   | Interrupt Vector 0          | 0x000114  |                                                        |

|                                   | Interrupt Vector 1          | -         |                                                        |

|                                   | ~                           | -         |                                                        |

|                                   | ~                           | -         | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   |                             | 0x00017C  |                                                        |

|                                   | Interrupt Vector 53         | 0x00017E  |                                                        |

|                                   | Interrupt Vector 54         | 0x00017L  |                                                        |

|                                   |                             | 0,000,100 |                                                        |

|                                   | ~                           | -         |                                                        |

|                                   |                             | -         |                                                        |

|                                   | Interrupt Vector 116        |           | 1                                                      |

|                                   | Interrupt Vector 117        | 0x0001FE  |                                                        |

| *                                 | Start of Code               | 0x000200  |                                                        |

|                                   |                             |           |                                                        |

|                                   |                             |           |                                                        |

|                                   |                             |           |                                                        |

|                                   |                             |           |                                                        |

## 8.4 Oscillator Control Registers

## **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,2)</sup>

| U-0     | R-0    | R-0   | R-0   | U-0   | R/W-y                | R/W-y                | R/W-y                |

|---------|--------|-------|-------|-------|----------------------|----------------------|----------------------|

| —       | COSC2  | COSC1 | COSC0 | —     | NOSC2 <sup>(3)</sup> | NOSC1 <sup>(3)</sup> | NOSC0 <sup>(3)</sup> |

| bit 15  |        |       |       |       |                      |                      | bit 8                |

|         |        |       |       |       |                      |                      |                      |

| R/W-0   | R/W-0  | R-0   | U-0   | R/C-0 | U-0                  | U-0                  | R/W-0                |

| CLKLOCK | IOLOCK | LOCK  | —     | CF    | _                    | —                    | OSWEN                |

| bit 7   |        |       |       |       |                      |                      | bit 0                |

| Legend:           | y = Value set from Configuration bits on POR |                       |                    |  |  |  |  |  |

|-------------------|----------------------------------------------|-----------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit | t, read as '0'     |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits (read-only)                                                                                                                                                                                                                                                                    |

|           | <pre>111 = Fast RC oscillator (FRC) with divide-by-n 110 = Fast RC oscillator (FRC) with divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Reserved 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL 000 = Fast RC oscillator (FRC)</pre> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(3)</sup>                                                                                                                                                                                                                                                                     |

|           | <pre>111 = Fast RC oscillator (FRC) with divide-by-n 110 = Fast RC oscillator (FRC) with divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Reserved 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL</pre>                                |

|           | 000 = Fast RC oscillator (FRC)                                                                                                                                                                                                                                                                                              |

| bit 7     | CLKLOCK: Clock Lock Enable bit                                                                                                                                                                                                                                                                                              |

|           | <pre>If Clock Switching is Enabled and FSCM is Disabled, (FOSC<fcksm> = 0b01): 1 = Clock switching is disabled, system clock source is locked 0 = Clock switching is enabled, system clock source can be modified by clock switching</fcksm></pre>                                                                          |

| bit 6     | IOLOCK: Peripheral Pin Select Lock bit                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Peripheral Pin Select is locked, write to Peripheral Pin Select registers not allowed</li> <li>0 = Peripheral Pin Select is not locked, write to Peripheral Pin Select registers allowed</li> </ul>                                                                                                            |

| bit 5     | LOCK: PLL Lock Status bit (read-only)                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Indicates that PLL is in lock, or PLL start-up timer is satisfied</li> <li>0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled</li> </ul>                                                                                                                                  |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

| Note 1:   | Writes to this register require an unlock sequence. Refer to " <b>Oscillator (Part IV)</b> " (DS70307) in the<br>"dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.                                                                                                             |

| 2:        | This register is reset only on a Power-on Reset (POR).                                                                                                                                                                                                                                                                      |

| 3:        | Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.<br>This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.                                            |

mode as a transition clock source between the two PLL modes.

| R/W-0           | R-0                                                                                                                                                                                 | R/W-1                                                                 | U-0          | U-0             | R/W-1                                                          | R/W-1           | R/W-1    |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|-----------------|----------------------------------------------------------------|-----------------|----------|

| ENAPLL          | APLLCK                                                                                                                                                                              | SELACLK                                                               | _            | —               | APSTSCLR2                                                      | APSTSCLR1       | APSTSCLR |

| bit 15          | •                                                                                                                                                                                   |                                                                       |              |                 |                                                                | •               | bit 0    |

| R/W-0           | R/W-0                                                                                                                                                                               | U-0                                                                   | U-0          | U-0             | U-0                                                            | U-0             | U-0      |

| ASRCSEL         | FRCSEL                                                                                                                                                                              | _                                                                     | _            |                 | _                                                              | _               | _        |

| bit 7           |                                                                                                                                                                                     |                                                                       |              |                 |                                                                |                 |          |

| Legend:         |                                                                                                                                                                                     |                                                                       |              |                 |                                                                |                 |          |

| R = Readable    | bit                                                                                                                                                                                 | W = Writable b                                                        | oit          | U = Unimple     | emented bit, read                                              | d as '0'        |          |

| -n = Value at P | OR                                                                                                                                                                                  | '1' = Bit is set                                                      |              | ʻ0' = Bit is c  | leared                                                         | x = Bit is unkn | own      |

| bit 15          | ENAPLL: Au<br>1 = APLL is e<br>0 = APLL is d                                                                                                                                        |                                                                       | ole bit      |                 |                                                                |                 |          |

| bit 14          | 1 = Indicates                                                                                                                                                                       | PLL Locked Statu<br>that auxiliary PL<br>that auxiliary PL            | L is in lock |                 |                                                                |                 |          |

| bit 13          | 1 = Auxiliary                                                                                                                                                                       | oscillators provi                                                     | des the sou  | rce clock for a | Clock Divider bi<br>auxiliary clock div<br>auxiliary clock dir | rider           |          |

| bit 12-11       | •                                                                                                                                                                                   | ited: Read as '0                                                      |              |                 |                                                                | Vider           |          |

| bit 10-8        | -                                                                                                                                                                                   | :2:0>: Auxiliary (                                                    |              | ıt Dividar hits |                                                                |                 |          |

|                 | 111 = Divideo<br>110 = Divideo<br>101 = Divideo<br>100 = Divideo<br>011 = Divideo<br>010 = Divideo<br>001 = Divideo<br>001 = Divideo                                                | d by 1<br>d by 2<br>d by 4<br>d by 8<br>d by 16<br>d by 32<br>d by 64 |              |                 |                                                                |                 |          |

| bit 7           | ASRCSEL: Select Reference Clock Source for Auxiliary Clock bit<br>1 = Primary oscillator is the clock source<br>0 = No clock input is selected                                      |                                                                       |              |                 |                                                                |                 |          |

| bit 6           | FRCSEL: Select Reference Clock Source for Auxiliary PLL bit <ol> <li>Select FRC clock for auxiliary PLL</li> <li>Input clock source is determined by ASRCSEL bit setting</li> </ol> |                                                                       |              |                 |                                                                |                 |          |

|                 | 0 = Input cloc                                                                                                                                                                      |                                                                       |              | ASRCSEL bit     | setting                                                        |                 |          |

## REGISTER 8-5: ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER<sup>(1)</sup>

**Note 1:** This register is reset only on a Power-on Reset (POR).

### 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70193) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

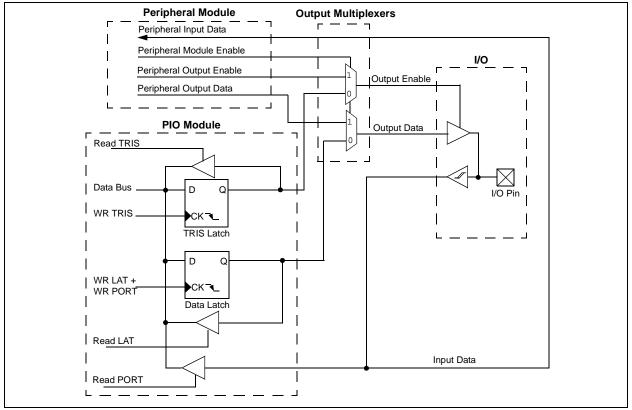

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

#### FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

© 2008-2014 Microchip Technology Inc.

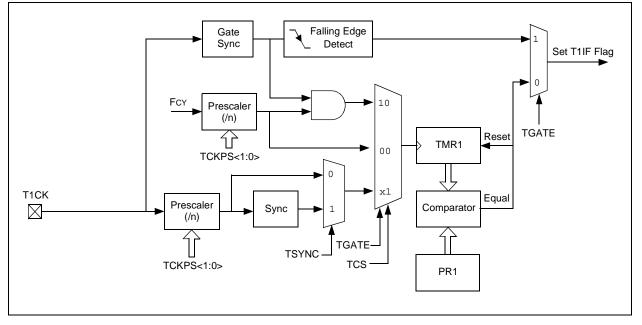

### 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as a time counter for the Real-Time Clock (RTC), or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low-power 32 kHz crystal oscillator available on the device

- Can be operated in Asynchronous Counter mode from an external clock source

- Optionally, the external clock input (T1CK) can be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 11-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

The timer control bit settings for different operating modes are given in the Table 11-1.

| TABLE 11-1: TIN | ER MODE SETTINGS |

|-----------------|------------------|

|-----------------|------------------|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | x     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

### 15.2 Feature Description

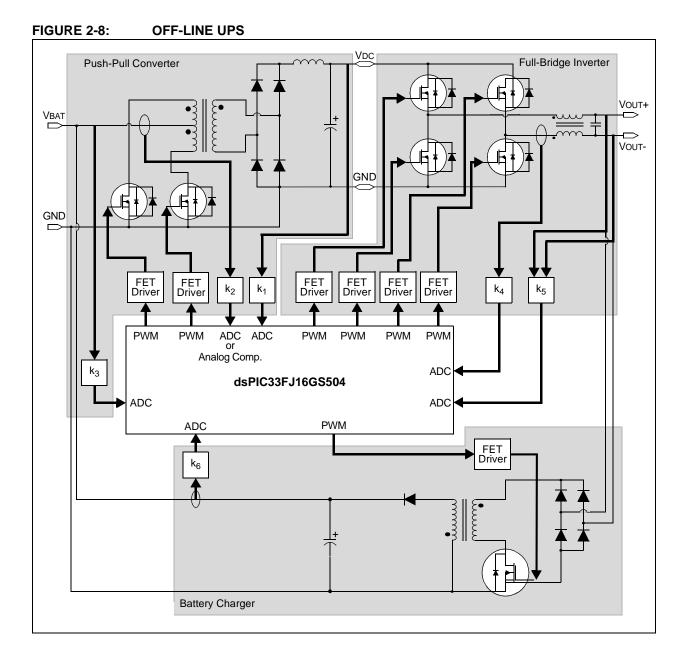

The PWM module is designed for applications that require:

- High-resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode, and Push-Pull mode outputs

- The ability to create multiphase PWM outputs

For Center-Aligned mode, the duty cycle, period phase and dead-time resolutions will be 8.32 ns.

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

Phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable. Multiphase PWM is often used to improve DC/DC Converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC Converters are often operated in parallel, but phase-shifted in time. A single PWM output operating at 250 kHz has a period of 4  $\mu$ s, but an array of four PWM channels, staggered by 1  $\mu$ s each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

Variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50%, and the power flow is controlled by varying the relative phase shift between the two PWM generators.

| R/W-0                             | R/W-0            | R/W-0       | R/W-0                                 | R/W-0                                                                                                 | R/W-0                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|------------------|-------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |                  | SPHAS       | SEx<15:8>                             |                                                                                                       |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                   |                  |             |                                       |                                                                                                       |                                                                                                                                    | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>D</b> 444 0                    | DAMA             | DAM 0       | DAMA                                  | DAVA                                                                                                  | DAMA                                                                                                                               | DAMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| R/W-0                             | R/W-0            | R/W-0       | R/W-0                                 | R/W-0                                                                                                 | R/W-0                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                   |                  | SPHA        | SEx<7:0>                              |                                                                                                       |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                   |                  |             |                                       |                                                                                                       |                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                   |                  |             |                                       |                                                                                                       |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R = Readable bit W = Writable bit |                  |             | U = Unimplemented bit, read as '0'    |                                                                                                       |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |