Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-UQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502t-e-mx |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

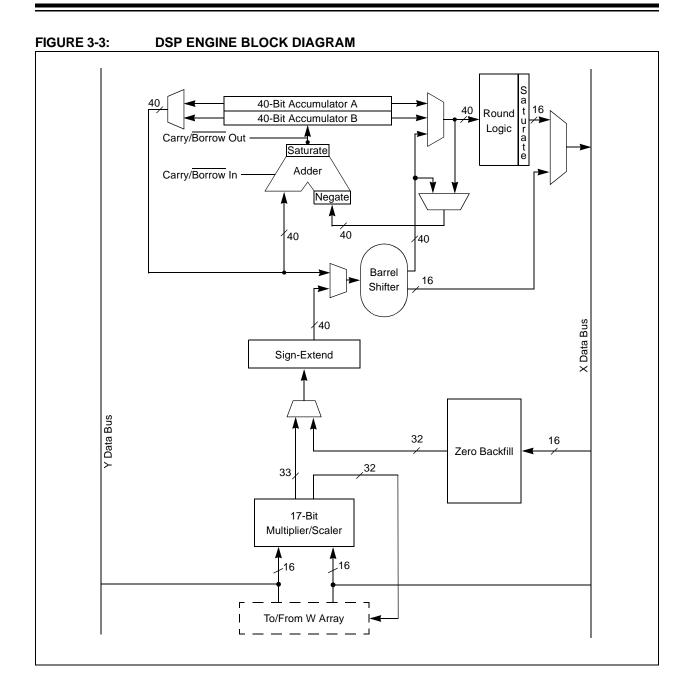

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user application. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and thus, indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). Programmers can check one bit in the STATUS Register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This is useful for complex number arithmetic, which typically uses both accumulators.

The device supports three Saturation and Overflow modes:

- Bit 39 Overflow and Saturation: When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive

9.31 (0x7FFFFFFFF) or maximally negative

9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. This condition is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (such as gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFFF) or maximally negative 1.31 value (0x008000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

- Bit 39 Catastrophic Overflow: The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set

- until cleared by the user application. No saturation operation is performed, and the accumulator is allowed to overflow, destroying its sign. If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

## 3.6.3 ACCUMULATOR 'WRITE BACK'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13] + = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

## 3.6.3.1 Round Logic

The round logic is a combinational block that performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value that is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word is simply discarded.

Conventional rounding zero-extends bit 15 of the accumulator and adds it to the ACCxH word (bits 16 through 31 of the accumulator).

- If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented.

- If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged.

A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is examined:

- If it is '1', ACCxH is incremented.

- If it is '0', ACCxH is not modified.

Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0         | All<br>Reset |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|---------------|--------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | -        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  |               | 0000         |

| INTCON2      | 0082        | ALTIVT  | DISI     |          |          | _       | _        | _        | _        | _        | _        | _        | _        | _       | INT2EP   | INT1EP   | INT0EP        | 0000         |

| IFS0         | 0084        | _       | _        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | _        | T2IF     | _        | _        | _        | T1IF    | OC1IF    | _        | <b>INT0IF</b> | 0000         |

| IFS1         | 0086        |         | _        | INT2IF   | _        | -       | _        | _        | _        | _        | _        | _        | INT1IF   | CNIF    | _        | MI2C1IF  | SI2C1IF       | 0000         |

| IFS3         | 008A        |         | _        | _        | _        | -       | _        | PSEMIF   | _        | _        | _        | _        | _        | _       | _        | _        | _             | 0000         |

| IFS4         | 008C        | _       | _        | —        | _        | _       |          | —        |          | —        |          |          |          | —       | _        | U1EIF    | _             | 0000         |

| IFS5         | 008E        | PWM2IF  | PWM1IF   | —        | _        | _       |          | —        |          | —        |          |          |          | —       | _        |          | _             | 0000         |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | —        | _        | _       |          | _        |          | —        |          |          |          | _       |          |          |               | 0000         |

| IFS7         | 0092        |         |          | —        | _        | _       |          | _        |          | —        |          |          |          | _       |          |          | ADCP2IF       | 0000         |

| IEC0         | 0094        |         |          | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  |          | T2IE     |          |          |          | T1IE    | OC1IE    |          | INT0IE        | 0000         |

| IEC1         | 0096        |         |          | INT2IE   | —        | _       |          | _        |          | —        |          |          | INT1IE   | CNIE    |          | MI2C1IE  | SI2C1IE       | 0000         |

| IEC3         | 009A        |         |          | —        | _        | _       |          | PSEMIE   |          | —        |          |          |          | _       |          |          |               | 0000         |

| IEC4         | 009C        |         |          | —        | _        | _       |          | _        |          | —        |          |          |          | _       |          | U1EIE    |               | 0000         |

| IEC5         | 009E        | PWM2IE  | PWM1IE   | —        | _        | _       |          | _        |          | —        |          |          |          | _       |          |          |               | 0000         |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  | —        | _        | _       |          | _        |          | —        |          |          |          | _       |          |          |               | 0000         |

| IEC7         | 00A2        |         |          | —        | _        | _       |          | _        |          | —        |          |          |          | _       |          |          | ADCP2IE       | 0000         |

| IPC0         | 00A4        | _       | T1IP2    | T1IP1    | T1IP0    | _       | OC1IP2   | OC1IP1   | OC1IP0   | —        |          |          |          | —       | INT0IP2  | INT0IP1  | INT0IP0       | 4404         |

| IPC1         | 00A6        |         | T2IP2    | T2IP1    | T2IP0    | _       |          | _        |          | —        |          |          |          | _       |          |          |               | 4000         |

| IPC2         | 00A8        | _       | U1RXIP2  | U1RXIP2  | U1RXIP0  | —       | SPI1IP2  | SPI1IP1  | SPI1IP0  | —        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 | —       | -        | -        | -             | 4440         |

| IPC3         | 00AA        | _       | _        | —        | —        | —       | -        | —        | _        |          | ADIP2    | ADIP1    | ADIP0    | —       | U1TXIP2  | U1TXIP1  | U1TXIP0       | 0044         |

| IPC4         | 00AC        | _       | CNIP2    | CNIP1    | CNIP0    | —       | -        | —        | _        | —        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | —       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0      | 4044         |

| IPC5         | 00AE        | _       | _        | —        | —        | —       | -        | —        | _        | —        | -        | -        | -        | —       | INT1IP2  | INT1IP1  | INT1IP0       | 0004         |

| IPC7         | 00B2        | _       | _        | —        | —        | —       | -        | —        | _        | —        | INT2IP2  | INT2IP1  | INT2IP0  | —       | -        | -        | -             | 0040         |

| IPC14        | 00C0        | —       | _        | —        | —        | —       | -        | —        | _        | —        | PSEMIP2  | PSEMIP1  | PSEMIP0  | —       | -        | -        | -             | 0040         |

| IPC16        | 00C4        | —       | _        | —        | —        | —       | -        | —        | _        | —        | U1EIP2   | U1EIP1   | U1EIP0   | —       | -        | -        | -             | 0040         |

| IPC23        | 00D2        | -       | PWM2IP2  | PWM2IP1  | PWM2IP0  | _       | PWM1IP2  | PWM1IP1  | PWM1IP0  | —        |          | -        | -        | —       |          | -        |               | 4400         |

| IPC27        | 00DA        | -       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | _       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | —        |          | -        | -        | —       |          | -        |               | 4400         |

| IPC28        | 00DC        | _       | _        | -        | _        | _       | _        | -        | _        | —        |          |          |          | —       | ADCP2IP2 | ADCP2IP1 | ADCP2IP0      | 0004         |

| INTTREG      | 00E0        | _       | _        |          | _        | ILR3    | ILR2     | ILR1     | ILR0     | _        | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0       | 0000         |

### TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06GS102 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0          | All<br>Resets |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|----------------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | —        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | —              | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     | _        | _        | _       | _        | _        | —        | _        | _        | —        | _        | —       | INT2EP   | INT1EP   | INT0EP         | 0000          |

| IFS0         | 0084        | _       | _        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | T3IF     | T2IF     | OC2IF    | IC2IF    | _        | T1IF    | OC1IF    | IC1IF    | INTOIF         | 0000          |

| IFS1         | 0086        | _       | _        | INT2IF   | _        | _       | _        | _        | —        | _        | _        | _        | INT1IF   | CNIF    | AC1IF    | MI2C1IF  | SI2C1IF        | 0000          |

| IFS3         | 008A        | _       | _        | _        | _        | _       | _        | PSEMIF   | —        | _        | _        | —        | _        | —       | _        | _        | _              | 0000          |

| IFS4         | 008C        |         | _        | —        | _        | _       |          |          |          |          |          | _        | _        | _       | _        | U1EIF    | _              | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF   | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       |          | -        | _              | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | _        | -       | _        | AC4IF    | AC3IF    | AC2IF    | _        | —        | —        | _       | _        | PWM4IF   | PWM3IF         | 0000          |

| IFS7         | 0092        | _       | -        | _        | _        | -       | _        | —        | —        | _        | _        | —        | ADCP6IF  | ADCP5IF | ADCP4IF  | ADCP3IF  | ADCP2IF        | 0000          |

| IEC0         | 0094        | _       | -        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  | T3IE     | T2IE     | OC2IE    | IC2IE    | —        | T1IE    | OC1IE    | IC1IE    | INT0IE         | 0000          |

| IEC1         | 0096        | _       | -        | INT2IE   | _        | -       | _        | —        | —        | _        | _        | —        | INT1IE   | CNIE    | AC1IE    | MI2C1IE  | SI2C1IE        | 0000          |

| IEC3         | 009A        | _       | -        | —        | _        | -       | _        | PSEMIE   | —        | _        | _        | —        | —        | _       | _        |          | -              | 0000          |

| IEC4         | 009C        | _       | -        | _        | _        | -       | _        | —        | —        | _        | _        | —        | —        | _       | _        | U1EIE    | -              | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE   | —        | _        | _       | _        | —        | —        | —        | _        | —        | —        | _       | _        | -        | _              | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  | _        | _        | _       | _        | AC4IE    | AC3IE    | AC2IE    | _        | _        | _        | _       | _        | PWM4IE   | <b>PWM3IE</b>  | 0000          |

| IEC7         | 00A2        | _       | _        | _        | _        | _       | _        | _        | _        | _        | _        | _        | ADCP6IE  | ADCP5IE | ADCP4IE  | ADCP3IE  | ADCP2IE        | 0000          |

| IPC0         | 00A4        | _       | T1IP2    | T1IP1    | T1IP0    | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2   | IC1IP1   | IC1IP0   | _       | INT0IP2  | INT0IP1  | INT0IP2        | 4444          |

| IPC1         | 00A6        | _       | T2IP2    | T2IP1    | T2IP0    | _       | OC2IP2   | OC2IP1   | OC2IP0   | _        | IC2IP2   | IC2IP1   | IC2IP0   | _       | _        | _        | _              | 4440          |

| IPC2         | 00A8        | _       | U1RXIP2  | U1RXIP1  | U1RXIP0  | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 | _       | T3IP2    | T3IP1    | T3IP0          | 4444          |

| IPC3         | 00AA        | _       | _        | —        | _        | -       | _        | —        | —        |          | ADIP2    | ADIP1    | ADIP0    | _       | U1TXIP2  | U1TXIP1  | U1TXIP0        | 0044          |

| IPC4         | 00AC        | _       | CNIP2    | CNIP1    | CNIP0    | -       | AC1IP2   | AC1IP1   | AC1IP0   | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0       | 4444          |

| IPC5         | 00AE        | _       | _        | —        | _        | -       | _        | —        | —        | _        | _        | —        | —        | _       | INT1IP2  | INT1IP1  | INT1IP0        | 0004          |

| IPC7         | 00B2        | _       | -        | _        | _        | -       | _        | —        | —        | _        | INT2IP2  | INT2IP1  | INT2IP0  | _       | _        |          | -              | 0040          |

| IPC14        | 00C0        | _       | -        | _        | _        | -       | _        | —        | —        | _        | PSEMIP2  | PSEMIP1  | PSEMIP0  | _       | _        |          | -              | 0040          |

| IPC16        | 00C4        | _       | -        | _        | _        | -       | _        | —        | _        | _        | U1EIP2   | U1EIP1   | U1EIP0   | _       | _        |          | -              | 0040          |

| IPC23        | 00D2        | _       | PWM2IP2  | PWM2IP1  | PWM2IP0  | _       | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | _        | _        | _        | _       | _        | _        | _              | 4400          |

| IPC24        | 00D4        | _       | —        | —        | —        | —       | —        | _        | _        | _        | PWM4IP2  | PWM4IP1  | PWM4IP0  | _       | PWM3IP2  | PWM3IP1  | PWM3IP0        | 0044          |

| IPC25        | 00D6        | _       | AC2IP2   | AC2IP1   | AC2IP0   | _       | _        | _        | _        | _        | _        | _        | _        | _       | _        | —        | —              | 4000          |

| IPC26        | 00D8        | _       | _        | —        | _        | _       | _        | _        | _        | _        | AC4IP2   | AC4IP1   | AC4IP0   | _       | AC3IP2   | AC3IP1   | AC3IP0         | 0440          |

| IPC27        | 00DA        | _       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | _       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _        | _        | _        | _        | _       | _        | _        | _              | 4400          |

| IPC28        | 00DC        | _       | ADCP5IP2 | ADCP5IP1 | ADCP5IP0 | _       | ADCP4IP2 | ADCP4IP1 | ADCP4IP0 | _        | ADCP3IP2 | ADCP3IP1 | ADCP3IP0 | _       | ADCP2IP2 | ADCP2IP1 | ADCP2IP0       | 4444          |

| IPC29        | 00DE        | _       | _        | _        | _        | _       |          | _        | _        | _        | _        | _        | —        | _       | ADCP6IP2 | ADCP6IP1 | ADCP6IP0       | 0004          |

| INTTREG      |             | _       | _        | _        | _        | ILR3    | ILR2     | ILR1     | ILR0     | _        | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | <b>VECNUM0</b> |               |

## TABLE 4-10: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ16GS504 DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 6.1 System Reset

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 families of devices have two types of Reset:

- Cold Reset

- Warm Reset

A Cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a Cold Reset, the FNOSCx Configuration bits in the FOSC Configuration register select the device clock source. A Warm Reset is the result of all the other Reset sources, including the RESET instruction. On Warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection (COSC<2:0>) bits in the Oscillator Control (OSCCON<14:12>) register.

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is detailed in Figure 6-2.

| Oscillator Mode           | Oscillator<br>Startup Delay | Oscillator<br>Startup Timer | PLL Lock Time        | Total Delay                             |

|---------------------------|-----------------------------|-----------------------------|----------------------|-----------------------------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd <sup>(1)</sup>        | _                           | _                    | Toscd <sup>(1)</sup>                    |

| FRCPLL                    | Toscd <sup>(1)</sup>        | _                           | ТLОСК <sup>(3)</sup> | Toscd + Tlock <sup>(1,3)</sup>          |

| XT                        | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| HS                        | Toscd(1)                    | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| EC                        | —                           | —                           | —                    | —                                       |

| XTPLL                     | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | ТLОСК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| HSPLL                     | Toscd(1)                    | Tost <sup>(2)</sup>         | ТLOCК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| ECPLL                     | —                           | —                           | ТLОСК <sup>(3)</sup> | TLOCK <sup>(3)</sup>                    |

| LPRC                      | Toscd <sup>(1)</sup>        | _                           | —                    | Toscd <sup>(1)</sup>                    |

## TABLE 6-1: OSCILLATOR DELAY

**Note 1:** TOSCD = Oscillator start-up delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal) if PLL is enabled.

|                             | • = • • • • • • • • • • • • • • • • • •                                                         |                                                                  |                                                                                  |                   |                 |                 |       |

|-----------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------|-----------------|-----------------|-------|

| U-0                         | U-0                                                                                             | U-0                                                              | U-0                                                                              | U-0               | U-0             | R/W-0           | R/W-0 |

| —                           | —                                                                                               | —                                                                | —                                                                                | —                 | _               | IC2MD           | IC1MD |

| it 15                       |                                                                                                 |                                                                  |                                                                                  |                   |                 |                 | bit 8 |

| U-0                         | U-0                                                                                             | U-0                                                              | U-0                                                                              | U-0               | U-0             | R/W-0           | R/W-0 |

| _                           | —                                                                                               | —                                                                |                                                                                  | _                 |                 | OC2MD           | OC1MD |

| oit 7                       | ·                                                                                               |                                                                  |                                                                                  |                   |                 |                 | bit C |

| _egend:                     |                                                                                                 |                                                                  |                                                                                  |                   |                 |                 |       |

| R = Readabl                 | e bit                                                                                           | W = Writable                                                     | bit                                                                              | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at               | POR                                                                                             | '1' = Bit is set                                                 |                                                                                  | '0' = Bit is clea | ared            | x = Bit is unkn | iown  |

| bit 15-10<br>bit 9<br>bit 8 | <b>IC2MD</b> : Input<br>1 = Input Cap<br>0 = Input Cap<br><b>IC1MD</b> : Input<br>1 = Input Cap | ture 2 module<br>ture 2 module<br>Capture 1 Moo<br>ture 1 module | dule Disable bit<br>is disabled<br>is enabled<br>dule Disable bit<br>is disabled |                   |                 |                 |       |

| bit 7-2                     |                                                                                                 | ture 1 module<br>t <b>ed:</b> Read as 'd                         |                                                                                  |                   |                 |                 |       |

| bit 1                       | 1 = Output Co                                                                                   | out Compare 2<br>ompare 2 modu<br>ompare 2 modu                  |                                                                                  | e bit             |                 |                 |       |

| bit 0                       | 1 = Output Co                                                                                   | out Compare 1<br>ompare 1 modu<br>ompare 1 modu                  |                                                                                  | e bit             |                 |                 |       |

## REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0           | U-0                                                               | R/W-1                                                    | R/W-1          | R/W-1             | R/W-1                   | R/W-1           | R/W-1  |  |  |  |  |

|---------------|-------------------------------------------------------------------|----------------------------------------------------------|----------------|-------------------|-------------------------|-----------------|--------|--|--|--|--|

| _             | —                                                                 | FLT1R5                                                   | FLT1R4         | FLT1R3            | FLT1R2                  | FLT1R1          | FLT1R0 |  |  |  |  |

| bit 15        |                                                                   |                                                          |                |                   |                         |                 | bit    |  |  |  |  |

|               |                                                                   |                                                          |                |                   |                         |                 |        |  |  |  |  |

| U-0           | U-0                                                               | U-0                                                      | U-0            | U-0               | U-0                     | U-0             | U-0    |  |  |  |  |

| _             | <u> </u>                                                          | —                                                        | —              | —                 |                         |                 | _      |  |  |  |  |

| bit 7         |                                                                   |                                                          |                |                   |                         |                 | bit (  |  |  |  |  |

|               |                                                                   |                                                          |                |                   |                         |                 |        |  |  |  |  |

| Legend:       |                                                                   |                                                          |                |                   |                         |                 |        |  |  |  |  |

| R = Readable  | e bit                                                             | W = Writable                                             | bit            | U = Unimplem      | nented bit, read as '0' |                 |        |  |  |  |  |

| -n = Value at | POR                                                               | '1' = Bit is set                                         |                | '0' = Bit is clea | ared                    | x = Bit is unkn | nown   |  |  |  |  |

|               |                                                                   |                                                          |                |                   |                         |                 |        |  |  |  |  |

| bit 15-14     | Unimplemer                                                        | ted: Read as '                                           | כי             |                   |                         |                 |        |  |  |  |  |

| bit 13-8      | FLT1R<5:0>                                                        | : Assign PWM I                                           | ault Input 1 ( | FLT1) to the Co   | orresponding R          | Pn Pin bits     |        |  |  |  |  |

|               | 111111 = Input tied to Vss                                        |                                                          |                |                   |                         |                 |        |  |  |  |  |

|               | TTTTTT - UN                                                       | out fied to VSS                                          |                |                   |                         |                 |        |  |  |  |  |

|               | 100011 <b>= In</b>                                                | out tied to RP35                                         |                |                   |                         |                 |        |  |  |  |  |

|               | 100011 = Ing<br>100010 = Ing                                      | out tied to RP35<br>out tied to RP34                     | ŀ              |                   |                         |                 |        |  |  |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                   |                         |                 |        |  |  |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34                     | <br>}          |                   |                         |                 |        |  |  |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                   |                         |                 |        |  |  |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                   |                         |                 |        |  |  |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                   |                         |                 |        |  |  |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing<br>100000 = Ing<br>• | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                   |                         |                 |        |  |  |  |  |

## REGISTER 10-9: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP19R5 | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

**RP18R3**

**RP18R2**

**RP18R1**

**RP18R0**

bit 0

RP18R4

## REGISTER 10-24: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

**RP18R5**

bit 7

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP19R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP19 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP18R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP18 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

| U-0             | U-0        | R/W-0            | R/W-0  | R/W-0                                    | R/W-0            | R/W-0    | R/W-0  |  |

|-----------------|------------|------------------|--------|------------------------------------------|------------------|----------|--------|--|

| _               |            | RP21R5           | RP21R4 | RP21R3                                   | RP21R2           | RP21R1   | RP21R0 |  |

| bit 15          |            |                  |        |                                          |                  |          | bit 8  |  |

|                 |            |                  |        |                                          |                  |          |        |  |

| U-0             | U-0        | R/W-0            | R/W-0  | R/W-0                                    | R/W-0            | R/W-0    | R/W-0  |  |

| —               | —          | RP20R5           | RP20R4 | RP20R3                                   | RP20R2           | RP20R1   | RP20R0 |  |

| bit 7           |            |                  |        |                                          |                  | •        | bit 0  |  |

|                 |            |                  |        |                                          |                  |          |        |  |

| Legend:         |            |                  |        |                                          |                  |          |        |  |

| R = Readable    | bit        | W = Writable     | bit    | U = Unimpler                             | mented bit, read | l as '0' |        |  |

| -n = Value at F | POR        | '1' = Bit is set |        | 0' = Bit is cleared $x = Bit is unknown$ |                  |          |        |  |

|                 |            |                  |        |                                          |                  |          |        |  |

| bit 15-14       | Unimplemen | ted: Read as '   | כ'     |                                          |                  |          |        |  |

## REGISTER 10-25: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10<sup>(1)</sup>

| bit 13-8 | <b>RP21R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP21 Output Pin bits (see Table 10-2 for peripheral function numbers) |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                               |

|          |                                                                                                                                          |

bit 5-0 **RP20R<5:0>:** Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 10-2 for peripheral function numbers)

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

| R/W-0                 | U-0                                                | R/W-0                                                   | HS/HC-0                 | R/W-0                              | R/W-0               | R/W-0                  | R/W-0                  |  |  |

|-----------------------|----------------------------------------------------|---------------------------------------------------------|-------------------------|------------------------------------|---------------------|------------------------|------------------------|--|--|

| PTEN                  | 0-0                                                | PTSIDL                                                  | SESTAT                  | SEIEN                              | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |  |  |

| bit 15                |                                                    | TIGIDE                                                  | OLUTAI                  | OLILIN                             |                     |                        | bit 8                  |  |  |

|                       |                                                    |                                                         |                         |                                    |                     |                        |                        |  |  |

| R/W-0                 | U-0                                                | R/W-0                                                   | R/W-0                   | R/W-0                              | R/W-0               | R/W-0                  | R/W-0                  |  |  |

| SYNCEN <sup>(1)</sup> |                                                    | SYNCSRC1 <sup>(1)</sup>                                 | SYNCSRC0 <sup>(1)</sup> | SEVTPS3(1)                         | SEVTPS2(1)          | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |  |  |

| bit 7                 |                                                    |                                                         |                         |                                    |                     |                        | bit 0                  |  |  |

|                       |                                                    |                                                         |                         |                                    |                     |                        |                        |  |  |

| Legend:               |                                                    | HC = Hardware                                           | e Clearable bit         | HS = Hardwa                        | re Settable bit     |                        |                        |  |  |

| R = Readable          | e bit                                              | W = Writable b                                          | it                      | U = Unimplemented bit, read as '0' |                     |                        |                        |  |  |

| -n = Value at         | POR                                                | '1' = Bit is set                                        |                         | '0' = Bit is cle                   | ared                | x = Bit is unkr        | nown                   |  |  |

| bit 15                | 1 = PWM m                                          | M Module Enabl<br>nodule is enable<br>nodule is disable | d                       |                                    |                     |                        |                        |  |  |

| bit 14                | Unimplem                                           | ented: Read as                                          | '0'                     |                                    |                     |                        |                        |  |  |

| bit 13                | PTSIDL: P                                          | WM Time Base \$                                         | Stop in Idle Mod        | e bit                              |                     |                        |                        |  |  |

|                       |                                                    | me base halts in<br>me base runs in                     |                         |                                    |                     |                        |                        |  |  |

| bit 12                |                                                    | pecial Event Inte                                       | -                       |                                    |                     |                        |                        |  |  |

|                       | •                                                  | event interrupt i<br>event interrupt i                  |                         |                                    |                     |                        |                        |  |  |

| bit 11                | SEIEN: Spe                                         | ecial Event Inter                                       | rupt Enable bit         |                                    |                     |                        |                        |  |  |

|                       |                                                    | event interrupt i<br>event interrupt i                  |                         |                                    |                     |                        |                        |  |  |

| bit 10                | EIPU: Enat                                         | ole Immediate Po                                        | eriod Updates bi        | t(1)                               |                     |                        |                        |  |  |

|                       |                                                    | Period register is<br>Period register u                 |                         |                                    | oundaries           |                        |                        |  |  |

| bit 9                 | SYNCPOL                                            | : Synchronizatio                                        | n Input/Output P        | olarity bit <sup>(1)</sup>         |                     |                        |                        |  |  |

|                       |                                                    | x and SYNCO po<br>x and SYNCO a                         | •                       | d (active-low)                     |                     |                        |                        |  |  |

| bit 8                 | SYNCOEN                                            | : Primary Time E                                        | Base Sync Enab          | le bit <sup>(1)</sup>              |                     |                        |                        |  |  |

|                       |                                                    | ) output is enabl<br>) output is disab                  |                         |                                    |                     |                        |                        |  |  |

| bit 7                 | SYNCEN:                                            | External Time Ba                                        | ase Synchroniza         | tion Enable bit                    | (1)                 |                        |                        |  |  |

|                       |                                                    | al synchronizatio<br>al synchronizatio                  |                         |                                    |                     |                        |                        |  |  |

| bit 6                 | Unimplem                                           | ented: Read as                                          | '0'                     |                                    |                     |                        |                        |  |  |

| bit 5-4               | SYNCSRC                                            | <1:0>: Synchror                                         | nous Source Sel         | ection bits <sup>(1)</sup>         |                     |                        |                        |  |  |

|                       | 11 = Reser<br>10 = Reser<br>01 = SYNC<br>00 = SYNC | ved<br>ll2                                              |                         |                                    |                     |                        |                        |  |  |

|                       |                                                    | uld be changed o                                        |                         |                                    |                     |                        |                        |  |  |

## REGISTER 15-1: PTCON: PWM TIME BASE CONTROL REGISTER

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0   | U-0          | U-0   |

|--------|-----|-----|-----|-----|-------|--------------|-------|

| —      | —   | —   | —   | —   | —     | —            | —     |

| bit 15 | -   |     |     |     |       | •            | bit 8 |

|        |     |     |     |     |       |              |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0        | R/W-0 |

| _      | —   | —   | _   | _   | P     | CLKDIV<2:0>( | 1)    |

| bit 7  |     |     | •   |     |       |              | bit 0 |

|        |     |     |     |     |       |              |       |

### REGISTER 15-2: PTCON2: PWM CLOCK DIVIDER SELECT REGISTER

## Γ.

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

- bit 2-0 PCLKDIV<2:0>: PWM Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64, maximum PWM timing resolution

- 101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

- Note 1: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will vield unpredictable results.

### REGISTER 15-3: PTPER: PWM MASTER TIME BASE REGISTER<sup>(1)</sup>

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|--------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|              |       |                  | PTPE  | R <15:8>         |                 |                 |       |

| bit 15       |       |                  |       |                  |                 |                 | bit 8 |

| R/W-1        | R/W-1 | R/W-1            | R/W-1 | R/W-1            | R/W-0           | R/W-0           | R/W-0 |

|              |       |                  | PTPE  | R <7:0>          |                 |                 |       |

| bit 7        |       |                  |       |                  |                 |                 | bit 0 |

| Legend:      |       |                  |       |                  |                 |                 |       |

| R = Readable | bit   | W = Writable b   | oit   | U = Unimplen     | nented bit, rea | d as '0'        |       |

|              |       | '1' = Bit is set |       | '0' = Bit is cle |                 | x = Bit is unkr | nown  |

#### bit 15-0 PTPER<15:0>: PWM Master Time Base (PMTMR) Period Value bits

Note 1: The minimum value that can be loaded into the PTPER register is 0x0010 and the maximum value is 0xFFF8.

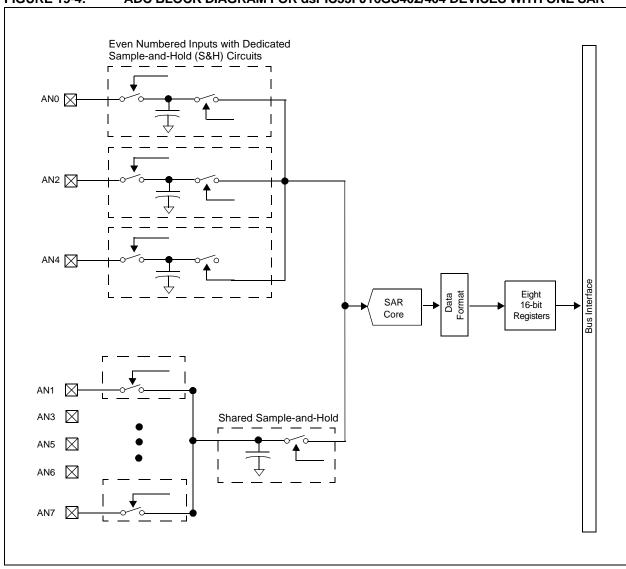

## FIGURE 19-4: ADC BLOCK DIAGRAM FOR dsPIC33FJ16GS402/404 DEVICES WITH ONE SAR

## REGISTER 19-5: ADCPC0: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 0 (CONTINUED)

| bit 12-8 | TRGSRC1<4:0>: Trigger 1 Source Selection bits                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Selects trigger source for conversion of Analog Channels AN3 and AN2.<br>11111 = Timer2 period match                                                                                                                                                                                                                                                                                                                                     |

|          | •                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 11011 = Reserved<br>11010 = PWM Generator 4 current-limit ADC trigger<br>11001 = PWM Generator 3 current-limit ADC trigger<br>1000 = PWM Generator 2 current-limit ADC trigger                                                                                                                                                                                                                                                           |

|          | <pre>10111 = PWM Generator 1 current-limit ADC trigger 10110 = Reserved •</pre>                                                                                                                                                                                                                                                                                                                                                          |

|          | •<br>10010 = Reserved<br>10001 = PWM Generator 4 secondary trigger is selected<br>10000 = PWM Generator 3 secondary trigger is selected<br>01111 = PWM Generator 2 secondary trigger is selected<br>01110 = PWM Generator 1 secondary trigger is selected<br>01101 = Reserved<br>01100 = Timer1 period match<br>•                                                                                                                        |

|          | •<br>01000 = Reserved<br>00111 = PWM Generator 4 primary trigger is selected<br>00100 = PWM Generator 3 primary trigger is selected<br>00101 = PWM Generator 2 primary trigger is selected<br>00100 = PWM Generator 1 primary trigger is selected<br>00011 = PWM Special Event Trigger is selected<br>00010 = Global software trigger is selected<br>00001 = Individual software trigger is selected<br>00000 = No conversion is enabled |

| bit 7    | <b>IRQEN0:</b> Interrupt Request Enable 0 bit<br>1 = Enables IRQ generation when requested conversion of Channels AN1 and AN0 is completed<br>0 = IRQ is not generated                                                                                                                                                                                                                                                                   |

| bit 6    | <b>PEND0:</b> Pending Conversion Status 0 bit<br>1 = Conversion of Channels AN1 and AN0 is pending; set when selected trigger is asserted<br>0 = Conversion is complete                                                                                                                                                                                                                                                                  |

| bit 5    | <ul> <li>SWTRG0: Software Trigger 0 bit</li> <li>1 = Starts conversion of AN1 and AN0 (if selected by the TRGSRCx bits)<sup>(1)</sup><br/>This bit is automatically cleared by hardware when the PEND0 bit is set.</li> <li>0 = Conversion has not started</li> </ul>                                                                                                                                                                    |

**Note 1:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

### REGISTER 19-6: ADCPC1: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 1 (CONTINUED)

TRGSRC2<4:0>: Trigger 2 Source Selection bits<sup>(2)</sup> bit 4-0 Selects trigger source for conversion of Analog Channels AN5 and AN4. 11111 = Timer2 period match 11011 = Reserved 11010 = PWM Generator 4 current-limit ADC trigger 11001 = PWM Generator 3 current-limit ADC trigger 11000 = PWM Generator 2 current-limit ADC trigger 10111 = PWM Generator 1 current-limit ADC trigger 10110 = Reserved 10010 = Reserved 10001 = PWM Generator 4 secondary trigger is selected 10000 = PWM Generator 3 secondary trigger is selected 01111 = PWM Generator 2 secondary trigger is selected 01110 = PWM Generator 1 secondary trigger is selected 01101 = Reserved 01100 = Timer1 period match 01000 = Reserved 00111 = PWM Generator 4 primary trigger is selected 00110 = PWM Generator 3 primary trigger is selected 00101 = PWM Generator 2 primary trigger is selected 00100 = PWM Generator 1 primary trigger is selected 00011 = PWM Special Event Trigger is selected 00010 = Global software trigger is selected 00001 = Individual software trigger is selected 00000 = No conversion is enabled

- Note 1: These bits are available in the dsPIC33FJ16GS402/404, dsPIC33FJ16GS504, dsPIC33FJ16GS502 and dsPIC33FJ06GS101 devices only.

- 2: These bits are available in the dsPIC33FJ16GS502, dsPIC33FJ16GS504, dsPIC33FJ06GS102, dsPIC33FJ06GS202 and dsPIC33FJ16GS402/404 devices only.

- **3:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

## 20.3 Module Applications

This module provides a means for the SMPS dsPIC<sup>®</sup> DSC devices to monitor voltage and currents in a power conversion application. The ability to detect transient conditions and stimulate the dsPIC DSC processor and/or peripherals, without requiring the processor and ADC to constantly monitor voltages or currents, frees the dsPIC DSC to perform other tasks.

The comparator module has a high-speed comparator and an associated 10-bit DAC that provides a programmable reference voltage to the inverting input of the comparator. The polarity of the comparator output is user-programmable. The output of the module can be used in the following modes:

- Generate an Interrupt

- Trigger an ADC Sample and Convert Process

- Truncate the PWM Signal (current limit)

- Truncate the PWM Period (current minimum)

- Disable the PWM Outputs (Fault latch)

The output of the comparator module may be used in multiple modes at the same time, such as: 1) generate an interrupt, 2) have the ADC take a sample and convert it, and 3) truncate the PWM output in response to a voltage being detected beyond its expected value.

The comparator module can also be used to wake-up the system from Sleep or Idle mode when the analog input voltage exceeds the programmed threshold voltage.

## 20.4 DAC

The range of the DAC is controlled through an analog multiplexer that selects either AVDD/2, an internal reference source, INTREF, or an external reference source, EXTREF. The full range of the DAC (AVDD/2) will typically be used when the chosen input source pin is shared with the ADC. The reduced range option (INTREF) will likely be used when monitoring current levels using a current sense resistor. Usually, the measured voltages in such applications are small (<1.25V); therefore the option of using a reduced reference range for the comparator extends the available DAC resolution in these applications. The use of an external reference enables the user to connect to a reference that better suits their application.

DACOUT, shown in Figure 20-1, can only be associated with a single comparator at a given time.

Note: It should be ensured in software that multiple DACOE bits are not set. The output on the DACOUT pin will be indeterminate if multiple comparators enable the DAC output.

## 20.5 Interaction with I/O Buffers

If the comparator module is enabled and a pin has been selected as the source for the comparator, then the chosen I/O pad must disable the digital input buffer associated with the pad to prevent excessive currents in the digital buffer due to analog input voltages.

## 20.6 Digital Logic

The CMPCONx register (see Register 20-1) provides the control logic that configures the comparator module. The digital logic provides a glitch filter for the comparator output to mask transient signals in less than two instruction cycles. In Sleep or Idle mode, the glitch filter is bypassed to enable an asynchronous path from the comparator to the interrupt controller. This asynchronous path can be used to wake-up the processor from Sleep or Idle mode.

The comparator can be disabled while in Idle mode if the CMPSIDL bit is set. If a device has multiple comparators, if any CMPSIDL bit is set, then the entire group of comparators will be disabled while in Idle mode. This behavior reduces complexity in the design of the clock control logic for this module.

The digital logic also provides a one TCY width pulse generator for triggering the ADC and generating interrupt requests.

The CMPDACx (see Register 20-2) register provides the digital input value to the reference DAC.

If the module is disabled, the DAC and comparator are disabled to reduce power consumption.

## 20.7 Comparator Input Range

The comparator has a limitation for the input Common-Mode Range (CMR) of (AVDD - 1.5V), typical. This means that both inputs should not exceed this range. As long as one of the inputs is within the Common-Mode Range, the comparator output will be correct. However, any input exceeding the CMR limitation will cause the comparator input to be saturated.

If both inputs exceed the CMR, the comparator output will be indeterminate.

## 20.8 DAC Output Range

The DAC has a limitation for the maximum reference voltage input of (AVDD - 1.6) volts. An external reference voltage input should not exceed this value or the reference DAC output will become indeterminate.

## 20.9 Comparator Registers

The comparator module is controlled by the following registers:

- CMPCONx: Comparator Control x Register

- CMPDACx: Comparator DAC x Control Register

| Bit Field  | Register | RTSP Effect                | Description                                                                                                                                 |

|------------|----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| BWRP       | FBS      | Immediate                  | Boot Segment Program Flash Write Protection bit                                                                                             |

|            |          |                            | 1 = Boot segment can be written                                                                                                             |

|            |          |                            | 0 = Boot segment is write-protected                                                                                                         |

| BSS<2:0>   | FBS      | Immediate                  | Boot Segment Program Flash Code Protection Size bits                                                                                        |

|            |          |                            | x11 = No boot program Flash segment                                                                                                         |

|            |          |                            | Boot Space is 256 Instruction Words (except interrupt vectors):<br>110 = Standard security; boot program Flash segment ends at<br>0x0003FE  |

|            |          |                            | 010 = High security; boot program Flash segment ends at<br>0x0003FE                                                                         |

|            |          |                            | Boot Space is 768 Instruction Words (except interrupt vectors):                                                                             |

|            |          |                            | 101 = Standard security; boot program Flash segment ends at<br>0x0007FE                                                                     |

|            |          |                            | 001 = High security; boot program Flash segment ends at<br>0x0007FE                                                                         |

|            |          |                            | Boot Space is 1792 Instruction Words (except interrupt vectors):<br>100 = Standard security; boot program Flash segment ends at<br>0x000FFE |

|            |          |                            | 000 = High security; boot program Flash segment ends at<br>0x000FFE                                                                         |

| GSS<1:0>   | FGS      | Immediate                  | General Segment Code-Protect bits                                                                                                           |

|            |          |                            | 11 = User program memory is not code-protected                                                                                              |

|            |          |                            | 10 = Standard security                                                                                                                      |

| 014/00     |          |                            | 0x = High security                                                                                                                          |

| GWRP       | FGS      | Immediate                  | General Segment Write-Protect bit                                                                                                           |

|            |          |                            | <ul> <li>1 = User program memory is not write-protected</li> <li>0 = User program memory is write-protected</li> </ul>                      |

| IESO       | FOSCSEL  | Immediate                  | Two-speed Oscillator Start-up Enable bit                                                                                                    |

|            |          |                            | 1 = Start-up device with FRC, then automatically switch to the                                                                              |

|            |          |                            | user-selected oscillator source when ready                                                                                                  |

|            |          |                            | 0 = Start-up device with user-selected oscillator source                                                                                    |

| FNOSC<2:0> | FOSCSEL  | If clock switch            | Initial Oscillator Source Selection bits                                                                                                    |

|            |          | is enabled,<br>RTSP effect | 111 = Internal Fast RC (FRC) Oscillator with Postscaler                                                                                     |

|            |          | is on any                  | 110 = Internal Fast RC (FRC) Oscillator with Divide-by-16<br>101 = LPRC Oscillator                                                          |

|            |          | device Reset;              | 100 = Reserved                                                                                                                              |

|            |          | otherwise,                 | 011 = Primary (XT, HS, EC) Oscillator with PLL                                                                                              |

|            |          | Immediate                  | 010 = Primary (XT, HS, EC) Oscillator                                                                                                       |

|            |          |                            | 001 = Internal Fast RC (FRC) Oscillator with PLL<br>000 = FRC Oscillator                                                                    |

| FCKSM<1:0> | FOSC     | Immediate                  | Clock Switching Mode bits                                                                                                                   |

|            |          | ininiodiate                | 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled                                                                       |

|            |          |                            | 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled |

| IOL1WAY    | FOSC     | Immediate                  | Peripheral Pin Select Configuration bit                                                                                                     |

|            |          |                            | 1 = Allows only one reconfiguration                                                                                                         |

|            |          |                            | 0 = Allows multiple reconfigurations                                                                                                        |

| OSCIOFNC   | FOSC     | Immediate                  | OSC2 Pin Function bit (except in XT and HS modes)                                                                                           |

|            |          |                            | 1 = OSC2 is the clock output                                                                                                                |

|            |          |                            | 0 = OSC2 is the general purpose digital I/O pin                                                                                             |

## TABLE 21-2: dsPIC33F CONFIGURATION BITS DESCRIPTION

| Bit Field    | Register | RTSP Effect | Description                                                                                                                                                                                                                                                                                                                                |

|--------------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POSCMD<1:0>  | FOSC     | Immediate   | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                          |

| FWDTEN       | FWDT     | Immediate   | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN bit in the RCON register will have no effect)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul> |

| WINDIS       | FWDT     | Immediate   | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                             |

| WDTPRE       | FWDT     | Immediate   | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                                                      |

| WDTPOST<3:0> | FWDT     | Immediate   | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                      |

| FPWRT<2:0>   | FPOR     | Immediate   | Power-on Reset Timer Value Select bits<br>111 = PWRT = 128 ms<br>110 = PWRT = 64 ms<br>101 = PWRT = 32 ms<br>100 = PWRT = 16 ms<br>011 = PWRT = 8 ms<br>010 = PWRT = 4 ms<br>001 = PWRT = 2 ms<br>000 = PWRT = Disabled                                                                                                                    |

| JTAGEN       | FICD     | Immediate   | JTAG Enable bit<br>1 = JTAG is enabled<br>0 = JTAG is disabled                                                                                                                                                                                                                                                                             |

| ICS<1:0>     | FICD     | Immediate   | ICD Communication Channel Select Enable bits<br>11 = Communicates on PGEC1 and PGED1<br>10 = Communicates on PGEC2 and PGED2<br>01 = Communicates on PGEC3 and PGED3<br>00 = Reserved, do not use.                                                                                                                                         |

## TABLE 21-2: dsPIC33F CONFIGURATION BITS DESCRIPTION (CONTINUED)

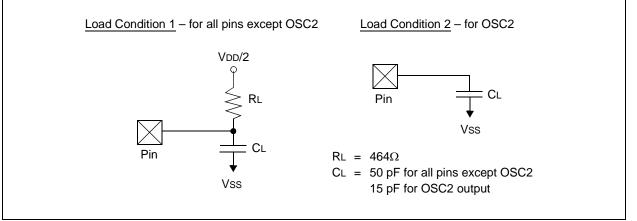

## 24.0 ELECTRICAL CHARACTERISTICS