Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b; D/A 4x10b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs502t-i-so |

**TABLE 4-5**: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06GS101 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|----------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | _        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | _        | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084        | _       | _        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | _        | T2IF     | _        | _        | _        | T1IF    | OC1IF    | _        | INT0IF   | 0000          |

| IFS1         | 0086        | _       | _        | INT2IF   | _        | _       |          | _        | _        | _        | _        | _        | INT1IF   | CNIF    | _        | MI2C1IF  | SI2C1IF  | 0000          |

| IFS3         | 008A        |         | _        | _        | _        | -       | _        | PSEMIF   | _        | _        | _        | _        | _        | _       | -        | _        | _        | 0000          |

| IFS4         | 008C        |         | _        | _        | _        | -       | _        | _        | _        | _        | _        | _        | _        | _       | -        | U1EIF    | _        | 0000          |

| IFS5         | 008E        |         | PWM1IF   | _        | _        | -       | _        | _        | _        | _        | _        | _        | _        | _       | -        | _        | _        | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | _        | -       | _        | _        | _        | _        | _        | _        | _        | -       | -        | PWM4IF   | _        | 0000          |

| IFS7         | 0092        |         | _        | _        | _        | -       | _        | _        | _        | _        | _        | _        | _        | -       | -        | ADCP3IF  | _        | 0000          |

| IEC0         | 0094        |         | _        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  | _        | T2IE     | _        | _        | _        | T1IE    | OC1IE    | _        | INT0IE   | 0000          |

| IEC1         | 0096        |         | _        | INT2IE   | _        | -       | _        | _        | _        | _        | _        | _        | INT1IE   | CNIE    | -        | MI2C1IE  | SI2C1IE  | 0000          |

| IEC2         | 0098        |         | _        | _        | _        | -       | _        | _        | _        | _        | _        | _        | _        | -       | -        | _        | _        | 0000          |

| IEC3         | 009A        |         | _        | _        | _        | -       | _        | PSEMIE   | _        | _        | _        | _        | _        | -       | -        | _        | _        | 0000          |

| IEC4         | 009C        |         | _        | _        | _        | -       | _        | _        | _        | _        | _        | _        | _        | -       | -        | U1EIE    | _        | 0000          |

| IEC5         | 009E        | _       | PWM1IE   |          | _        | _       | 1        | _        | -        | _        |          | _        | _        | -       |          | _        | -        | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  | I        |          | _       | I        | _        | 1        |          | I        | _        | _        | 1       | I        | PWM4IE   | -        | 0000          |

| IEC7         | 00A2        | 1       | 1        | I        |          | _       | I        | _        | 1        |          | I        | _        | _        | 1       | I        | ADCP3IE  | -        | 0000          |

| IPC0         | 00A4        | _       | T1IP2    | T1IP1    | T1IP0    | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        |          | _        | _        | -       | INT0IP2  | INT0IP1  | INT0IP2  | 4404          |

| IPC1         | 00A6        | 1       | T2IP2    | T2IP1    | T2IP0    | _       | I        | _        | 1        |          | I        | _        | _        | 1       | I        |          | -        | 4000          |

| IPC2         | 8A00        | 1       | U1RXIP2  | U1RXIP1  | U1RXIP0  | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  |          | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 | 1       | I        |          | -        | 4440          |

| IPC3         | 00AA        | 1       | 1        | I        |          | _       | I        | _        | 1        |          | ADIP2    | ADIP1    | ADIP0    | 1       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC        | 1       | CNIP2    | CNIP1    | CNIP0    | _       | I        | _        | 1        |          | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | 1       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4044          |

| IPC5         | 00AE        | 1       | 1        | I        |          | _       | I        | _        | 1        |          | I        | _        | _        | 1       | INT1IP2  | INT1IP21 | INT1IP0  | 0004          |

| IPC7         | 00B2        | 1       | 1        | I        |          | _       | I        | _        | 1        |          | INT2IP2  | INT2IP1  | INT2IP0  | 1       | I        |          | 1        | 0040          |

| IPC14        | 00C0        | 1       | 1        | I        |          | _       | I        | _        | 1        |          | PSEMIP2  | PSEMIP1  | PSEMIP0  | 1       | I        |          | 1        | 0040          |

| IPC16        | 00C4        | 1       | 1        | I        |          | _       | I        | _        | 1        |          | U1EIP2   | U1EIP1   | U1EIP0   | 1       | I        |          | 1        | 0400          |

| IPC23        | 00D2        | _       | _        | _        | _        | _       | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | _        | _        | _        | _       | _        | _        | -        | 0040          |

| IPC24        | 00D4        | _       | _        | _        | _        | _       | _        | _        | _        | _        | PWM4IP2  | PWM4IP1  | PWM4IP0  | _       | _        | _        | -        | 4400          |

| IPC27        | 00DA        | _       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | _       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _        |          | _        |          | _       |          | _        | _        | 0040          |

| IPC28        | 00DC        | _       |          |          |          | _       | _        |          |          | _        | ADCP3IP2 | ADCP3IP1 | ADCP3IP0 | _       | _        |          |          | 0000          |

| INTTREG      | 00E0        | _       | _        | _        | _        | ILR3    | ILR2     | ILR1     | ILR0     | _        | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Ō        |

|----------|

| 7        |

| 0        |

| 000      |

| 0        |

| 0        |

| 031      |

|          |

|          |

|          |

|          |

|          |

| 8<br>G-Y |

| 8<br>G-Y |

|          |

| 8<br>G-Y |

| 8G-page  |

| 8<br>G-Y |

| TABLE 4-6: | INTERRUPT CONTROLLER | REGISTER MAP FOR | dsPIC33FJ06GS102 DEVICES ONLY |

|------------|----------------------|------------------|-------------------------------|

|------------|----------------------|------------------|-------------------------------|

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------|----------|----------|---------|----------|----------|----------|---------------|

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | DIV0ERR  | _        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | _        | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0         | 0084        | _       | _        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | _        | T2IF     | _        | _        | _        | T1IF    | OC1IF    | _        | INT0IF   | 0000          |

| IFS1         | 0086        | -       | _        | INT2IF   | _        | _       | _        | _        |          | _        | _        | ı        | INT1IF   | CNIF    | _        | MI2C1IF  | SI2C1IF  | 0000          |

| IFS3         | 008A        | -       | _        | -        | _        | _       | _        | PSEMIF   |          | _        | _        | ı        | _        | _       | _        | _        | -        | 0000          |

| IFS4         | 008C        | 1       | 1        | 1        | _        | _       | 1        | 1        | 1        | -        | _        | I        |          | _       |          | U1EIF    | 1        | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF   | -        | _        | _       | _        | _        | _        | _        | _        | -        | _        | _       | _        | _        | -        | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       | _        | _        | _        | 0000          |

| IFS7         | 0092        | -       | _        | _        | _        | _       | _        | _        | _        | _        | _        |          | _        | _       | _        | _        | ADCP2IF  | 0000          |

| IEC0         | 0094        |         | _        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  | _        | T2IE     | _        |          | _        | T1IE    | OC1IE    | _        | INT0IE   | 0000          |

| IEC1         | 0096        | _       | _        | INT2IE   | _        | _       | _        | _        | _        | _        | _        | _        | INT1IE   | CNIE    | _        | MI2C1IE  | SI2C1IE  | 0000          |

| IEC3         | 009A        | _       | _        | _        | _        | _       | _        | PSEMIE   | _        | _        | _        |          | _        | _       | _        | _        | _        | 0000          |

| IEC4         | 009C        | _       | _        | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       | _        | U1EIE    | _        | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE   | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       | _        | _        | _        | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  | _        | _        | _       | _        | _        | _        | _        | _        |          | _        | _       | _        | _        | _        | 0000          |

| IEC7         | 00A2        |         | _        | _        | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       | _        | _        | ADCP2IE  | 0000          |

| IPC0         | 00A4        |         | T1IP2    | T1IP1    | T1IP0    | _       | OC1IP2   | OC1IP1   | OC1IP0   | _        | _        | _        | _        | _       | INT0IP2  | INT0IP1  | INT0IP0  | 4404          |

| IPC1         | 00A6        |         | T2IP2    | T2IP1    | T2IP0    | _       | _        | _        | _        | _        | _        | _        | _        | _       | _        | _        | _        | 4000          |

| IPC2         | 00A8        |         | U1RXIP2  | U1RXIP2  | U1RXIP0  | _       | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0 | _       | _        | _        | _        | 4440          |

| IPC3         | 00AA        |         | _        | _        | _        | _       | _        | _        | _        | _        | ADIP2    | ADIP1    | ADIP0    | _       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 0044          |

| IPC4         | 00AC        |         | CNIP2    | CNIP1    | CNIP0    | _       | _        | _        | _        | _        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0 | _       | SI2C1IP2 | SI2C1IP1 | SI2C1IP0 | 4044          |

| IPC5         | 00AE        |         | _        | _        | _        | _       | _        | _        | _        | _        | _        |          | _        | _       | INT1IP2  | INT1IP1  | INT1IP0  | 0004          |

| IPC7         | 00B2        | -       | _        | _        | _        | _       | _        | _        | _        | _        | INT2IP2  | INT2IP1  | INT2IP0  | _       | _        | _        |          | 0040          |

| IPC14        | 00C0        |         | _        |          | _        | _       | _        | _        | _        | _        | PSEMIP2  | PSEMIP1  | PSEMIP0  | _       | _        | _        |          | 0040          |

| IPC16        | 00C4        | -       |          | 1        | _        | -       | _        | _        | _        | _        | U1EIP2   | U1EIP1   | U1EIP0   | -       | _        | _        | -        | 0040          |

| IPC23        | 00D2        |         | PWM2IP2  | PWM2IP1  | PWM2IP0  | _       | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | _        | _        | _        | _       | _        | _        | _        | 4400          |

| IPC27        | 00DA        | _       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | _       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | _        | _        | _        | _        | _       | _        | _        | _        | 4400          |

| IPC28        | 00DC        |         | _        |          | _        | _       | _        | _        | _        | _        | _        | _        | _        | _       | ADCP2IP2 | ADCP2IP1 | ADCP2IP0 | 0004          |

| INTTREG      | 00E0        | _       | _        | _        | _        | ILR3    | ILR2     | ILR1     | ILR0     | _        | VECNUM6  | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TA DI E 1-11. | INPUT CAPTURE REGISTER MAP FOR dsPIC | 33E 146G6AU3 VND 99DIC33E 146G6AU4 |

|---------------|--------------------------------------|------------------------------------|

| IABLE 4-14    | INPUT CAPTURE REGISTER MAP FOR OSPIC | .33FJ10G3XUZ AND 0SPIG33FJ10G3XU4  |

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                   | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| IC1BUF       | 0140        |        | Input Capture 1 Register |        |        |        |        |       |       |       |       |       |       |       |       |       |       | xxxx          |

| IC1CON       | 0142        | -      | -                        | ICSIDL | -      | _      | _      | _     | _     | ICTMR | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

| IC2BUF       | 0144        |        | Input Capture 2 Register |        |        |        |        |       |       |       |       |       |       |       |       |       |       | xxxx          |

| IC2CON       | 0146        | _      | _                        | ICSIDL | -      | _      | _      | _     | -     | ICTMR | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: OUTPUT COMPARE REGISTER MAP FOR dsPIC33FJ06GS101 AND dsPIC33FJ06GSX02

| File<br>Name | SFR<br>Addr | Bit 15                              | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|-------------------------------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|-------|-------|---------------|

| OC1RS        | 0180        | Output Compare 1 Secondary Register |        |        |        |        |        |       |       |       |       |       |       |        |       |       |       | xxxx          |

| OC1R         | 0182        | Output Compare 1 Register           |        |        |        |        |        |       |       |       |       |       |       |        |       |       | xxxx  |               |

| OC1CON       | 0184        | _                                   | _      | OCSIDL | _      | _      | _      | _     | _     | _     | _     | _     | OCFLT | OCTSEL | OCM2  | OCM1  | ОСМ0  | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

### TABLE 4-16: OUTPUT COMPARE REGISTER MAP FOR dsPIC33FJ16GSX02 AND dsPIC33FJ06GSX04

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14                                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8      | Bit 7      | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|----------------------------------------|--------|--------|--------|--------|-----------|------------|------------|--------|-------|-------|--------|-------|-------|-------|---------------|

| OC1RS        | 0180        |        | Output Compare 1 Secondary Register xx |        |        |        |        |           |            |            |        |       |       |        |       | xxxx  |       |               |

| OC1R         | 0182        |        | Output Compare 1 Register              |        |        |        |        |           |            |            |        |       |       |        |       |       | xxxx  |               |

| OC1CON       | 0184        | _      | _                                      | OCSIDL | _      | _      | _      | _         | _          | _          | _      | _     | OCFLT | OCTSEL | OCM2  | OCM1  | ОСМ0  | 0000          |

| OC2RS        | 0186        |        |                                        |        |        |        |        | Output Co | mpare 2 Se | condary Re | gister |       |       |        |       |       |       | xxxx          |

| OC2R         | 0188        |        |                                        |        |        |        |        | Outp      | ut Compare | 2 Register | •      |       |       |        |       |       |       | xxxxx         |

| OC2CON       | 018A        | _      | _                                      | OCSIDL | _      | _      | _      | _         | _          | _          | _      | _     | OCFLT | OCTSEL | OCM2  | OCM1  | ОСМ0  | 0000          |

dsPlC33FJ06GS101/X02 and dsPlC33FJ16GSX02/X04

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-17: HIGH-SPEED PWM REGISTER MAP

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7  | Bit 6 | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|--------------|-------------|--------|---------------|--------|--------|--------|--------|---------|---------|--------|-------|----------|----------|----------|----------|---------|---------|---------------|

| PTCON        | 0400        | PTEN   | _             | PTSIDL | SESTAT | SEIEN  | EIPU   | SYNCPOL | SYNCOEN | SYNCEN | -     | SYNCSRC1 | SYNCSRC0 | SEVTPS3  | SEVTPS2  | SEVTPS1 | SEVTPS0 | 0000          |

| PTCON2       | 0402        | _      |               |        |        |        |        |         |         |        |       |          | PCLKDIV2 | PCLKDIV1 | PCLKDIV0 | 0000    |         |               |

| PTPER        | 0404        |        | PTPER<15:0>   |        |        |        |        |         |         |        |       |          |          |          | FFF8     |         |         |               |

| SEVTCMP      | 0406        |        | SEVTCMP<15:3> |        |        |        |        |         |         |        |       |          |          |          | 0000     |         |         |               |

| MDC          | 040A        |        | MDC<15:0>     |        |        |        |        |         |         |        |       |          |          |          |          | 0000    |         |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# DS70000318G-page 71

| TABLE 4-41: | SYSTEM   | CONTROL | REGISTER  | МΔР   |

|-------------|----------|---------|-----------|-------|

| IADLL 4-41. | SISILIVI | CONTROL | ILLGIOILI | IVIAL |

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|--------------|-------------|--------|--------|---------|--------|--------|-----------|-----------|-----------|----------|----------|--------|----------|---------|---------|---------|---------|---------------|

| RCON         | 0740        | TRAPR  | IOPUWR | 1       | _      | _      | _         | CM        | VREGS     | EXTR     | SWR      | SWDTEN | WDTO     | SLEEP   | IDLE    | BOR     | POR     | xxxx(1)       |

| OSCCON       | 0742        | _      | COSC2  | COSC1   | COSC0  | _      | NOSC2     | NOSC1     | NOSC0     | CLKLOCK  | IOLOCK   | LOCK   | _        | CF      | -       | _       | OSWEN   | 0300(2)       |

| CLKDIV       | 0744        | ROI    | DOZE2  | DOZE1   | DOZE0  | DOZEN  | FRCDIV2   | FRCDIV1   | FRCDIV0   | PLLPOST1 | PLLPOST0 | _      | PLLPRE4  | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 3040          |

| PLLFBD       | 0746        | _      |        | -       | _      | _      | -         | I         |           |          |          | PLLI   | OIV<8:0> |         |         |         |         | 0030          |

| REFOCON      | 074E        | ROON   | 1      | ROSSLP  | ROSEL  | RODIV3 | RODIV2    | RODIV1    | RODIV0    | _        | _        | _      | _        | -       | -       | _       | _       | 0000          |

| OSCTUN       | 0748        | -      | _      | _       | _      | _      | _         | _         |           |          |          |        |          | 0000    |         |         |         |               |

| ACLKCON      | 0750        | ENAPLL | APLLCK | SELACLK | _      | _      | APSTSCLR2 | APSTSCLR1 | APSTSCLR0 | ASRCSEL  | FRCSEL   | _      | _        | _       | _       | _       | _       | 2300          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

The RCON register Reset values are dependent on the type of Reset.

The OSCCON register Reset values are dependent on the FOSCx Configuration bits and on type of Reset.

### **TABLE 4-42: NVM REGISTER MAP**

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------|--------|--------|--------|---------------|

| NVMCON       | 0760        | WR     | WREN   | WRERR  | _      | _      | _      | _     | _     | _     | ERASE | _     | _     | NVMOP3  | NVMOP2 | NVMOP1 | NVMOP0 | 0000(1)       |

| NVMKEY       | 0766        | _      | _      | _      | _      | _      | -      | _     | _     |       |       |       | NVMKI | EY<7:0> |        |        |        | 0000          |

dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

1: Reset value shown is for POR only. The value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

### TABLE 4-43: PMD REGISTER MAP FOR dsPIC33FJ06GS101 DEVICES ONLY

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1         | 0770        | _      | _      | _      | T2MD   | T1MD   | -      | PWMMD | _      | I2C1MD | -     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2         | 0772        |        | _      | _      | _      | -      |        | IC2MD | IC1MD  | _      | _     | _     | _     | _      | _     | OC2MD | OC1MD | 0000          |

| PMD3         | 0774        | _      | _      | _      | _      | _      | CMPMD  | _     | _      | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4         | 0776        | _      | _      | _      | _      | _      |        | -     | _      | _      | 1     | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6         | 077A        | _      | _      | _      | _      | PWM4MD |        | -     | PWM1MD | -      |       | _     | _     | _      | -     | _     | -     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### PMD REGISTER MAP FOR dsPIC33FJ06GS102 DEVICES ONLY **TABLE 4-44:**

| File<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1         | 0770        | _      | _      | _      | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2         | 0772        | _      | _      | _      | -      | -      | -      | IC2MD  | IC1MD  | _      | 1     | _     | _     | _      | _     | OC2MD | OC1MD | 0000          |

| PMD3         | 0774        | -      | _      | _      | ı      | I      | CMPMD  | ı      | _      |        | ı     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4         | 0776        |        | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6         | 077A        | _      | _      | _      | _      | _      | _      | PWM2MD | PWM1MD | _      | -     | _     | _     | _      | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 5.2 RTSP Operation

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 24-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the Table Write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

The programming time depends on the FRC accuracy (see Table 24-20) and the value of the FRC Oscillator Tuning register (see Register 8-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time, and Word Write Cycle Time parameters (see Table 24-12).

# **EQUATION 5-1: PROGRAMMING TIME**

$$\frac{T}{7.37 \ MHz \times (FRC \ Accuracy)\% \times (FRC \ Tuning)\%}$$

For example, if the device is operating at +125°C, the FRC accuracy will be ±5%. If the TUN<5:0> bits (see Register 8-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

# 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3** "**Programming Operations**" for further details.

### REGISTER 7-12: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

| U-0    | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0 |

|--------|-----|-------|--------|--------|--------|---------|-------|

| _      | _   | ADIE  | U1TXIE | U1RXIE | SPI1IE | SPI1EIE | T3IE  |

| bit 15 |     |       |        |        |        |         | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  |

|-------|-------|-------|-----|-------|-------|-------|--------|

| T2IE  | OC2IE | IC2IE | _   | T1IE  | OC1IE | IC1IE | INT0IE |

| bit 7 |       |       |     |       |       |       | bit 0  |

Legend:

bit 8

bit 4

bit 3

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 ADIE: ADC1 Conversion Complete Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 12 **U1TXIE:** UART1 Transmitter Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 11 U1RXIE: UART1 Receiver Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 10 SPI1IE: SPI1 Event Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 9 SPI1EIE: SPI1 Event Interrupt Enable bit

1 = Interrupt request enabled

0 = Interrupt request not enabled

T3IE: Timer3 Interrupt Enable bit

1 = Interrupt request enabled

0 = Interrupt request not enabled

bit 7 **T2IE:** Timer2 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 6 OC2IE: Output Compare Channel 2 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 5 IC2IE: Input Capture Channel 2 Interrupt Enable bit

1 = Interrupt request enabled

0 = Interrupt request not enabled

Unimplemented: Read as '0'

T1IE: Timer1 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 2 OC1IE: Output Compare Channel 1 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

# REGISTER 7-18: IEC7: INTERRUPT ENABLE CONTROL REGISTER 7

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| _     | _   | _   | ADCP6IE | ADCP5IE | ADCP4IE | ADCP3IE | ADCP2IE |

| bit 7 |     |     |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4 ADCP6IE: ADC Pair 6 Conversion Done Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 3 ADCP5IE: ADC Pair 5 Conversion Done Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 2 ADCP4IE: ADC Pair 4 Conversion Done Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 1 ADCP3IE: ADC Pair 3 Conversion Done Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 0 ADCP2IE: ADC Pair 2 Conversion Done Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

# 8.2 Auxiliary Clock Generation

The auxiliary clock generation is used for a peripherals that need to operate at a frequency unrelated to the system clock such as a PWM or ADC.

The primary oscillator and internal FRC oscillator sources can be used with an auxiliary PLL to obtain the auxiliary clock. The auxiliary PLL has a fixed 16x multiplication factor.

The auxiliary clock has the following configuration restrictions:

- For proper PWM operation, auxiliary clock generation must be configured for 120 MHz (see

Parameter OS56 in Table 24-18 in Section 24.0

"Electrical Characteristics"). If a slower frequency is desired, the PWM Input Clock Prescaler (Divider) Select bits (PCLKDIV<2:0>) should be used.

- To achieve 1.04 ns PWM resolution, the auxiliary clock must use the 16x auxiliary PLL (APLL). All other clock sources will have a minimum PWM resolution of 8 ns.

- If the primary PLL is used as a source for the auxiliary clock, the primary PLL should be configured up to a maximum operation of 30 MIPS or less

### 8.3 Reference Clock Generation

The reference clock output logic provides the user with the ability to output a clock signal based on the system clock or the crystal oscillator on a device pin. The user application can specify a wide range of clock scaling prior to outputting the reference clock.

# REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,2)</sup> (CONTINUED)

bit 3 **CF:** Clock Fail Detect bit (read/clear by application)

1 = FSCM has detected clock failure0 = FSCM has not detected clock failure

bit 2-1 Unimplemented: Read as '0'

bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Request oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Writes to this register require an unlock sequence. Refer to "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.

- 2: This register is reset only on a Power-on Reset (POR).

- 3: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

# REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| _      | _   | _   | _   | _   | _   | IC2MD | IC1MD |

| bit 15 |     |     |     |     |     |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | _   | _   | _   | OC2MD | OC1MD |

| bit 7 |     |     |     |     |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9 IC2MD: Input Capture 2 Module Disable bit

1 = Input Capture 2 module is disabled0 = Input Capture 2 module is enabled

bit 8 IC1MD: Input Capture 1 Module Disable bit

1 = Input Capture 1 module is disabled0 = Input Capture 1 module is enabled

bit 7-2 **Unimplemented:** Read as '0'

bit 1 OC2MD: Output Compare 2 Module Disable bit

1 = Output Compare 2 module is disabled0 = Output Compare 2 module is enabled

bit 0 OC1MD: Output Compare 1 Module Disable bit

1 = Output Compare 1 module is disabled0 = Output Compare 1 module is enabled

# REGISTER 9-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|-----|--------|--------|--------|--------|

| _      | _   | _   | _   | CMP4MD | CMP3MD | CMP2MD | CMP1MD |

| bit 15 |     |     |     |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

bit 8

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 Unimplemented: Read as '0'

bit 11 CMP4MD: Analog Comparator 4 Module Disable bit

1 =Analog Comparator 4 module is disabled

0 = Analog Comparator 4 module is enabled

bit 10 CMP3MD: Analog Comparator 3 Module Disable bit

1 = Analog Comparator 3 module is disabled0 = Analog Comparator 3 module is enabled

bit 9 CMP2MD: Analog Comparator 2 Module Disable bit

1 = Analog Comparator 2 module is disabled0 = Analog Comparator 2 module is enabled

CMP1MD: Analog Comparator 1 Module Disable bit

1 = Analog Comparator 1 module is disabled

0 = Analog Comparator 1 module is enabled

bit 7-0 **Unimplemented:** Read as '0'

### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 INT2R<5:0>: Assign External Interrupt 2 (INTR2) to the Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35

100010 = Input tied to RP34

100001 = Input tied to RP33

100000 = Input tied to RP32

•

•

•

00000 = Input tied to RP0

## REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enable; if 9-bit mode is not selected, this does not take effect 0 = Address Detect mode is disabled bit 4 RIDLE: Receiver Idle bit (read-only) 1 = Receiver is Idle 0 = Receiver is active bit 3 **PERR:** Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected bit 1 OERR: Receive Buffer Overrun Error Status bit (clear/read-only) 1 = Receive buffer has overflowed  $0 = \text{Receive buffer has not overflowed; clearing a previously set OERR bit } (1 \rightarrow 0 \text{ transition}) \text{ will reset}$ the receiver buffer and the UxRSR to the empty state bit 0 URXDA: UARTx Receive Buffer Data Available bit (read-only) 1 = Receive buffer has data, at least one more character can be read 0 = Receive buffer is empty

- **Note 1:** Refer to "UART" (DS70188) in the "dsPIC33F/PIC24H Family Reference Manual" for information on enabling the UART module for transmit operation.

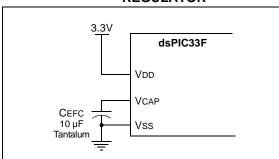

### 21.2 On-Chip Voltage Regulator

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families incorporate an on-chip regulator that allows the device to run its core logic from VDD

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 21-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 24-13 located in **Section 24.1 "DC Characteristics"**.

**Note:** It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

On a POR, it takes approximately 20  $\mu s$  for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

FIGURE 21-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

- Note 1: These are typical operating voltages. Refer to Table 24-13 located in Section 24.1 "DC Characteristics" for the full operating ranges of VDD.

- 2: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin

- **3:** Typical VCAP pin voltage = 2.5V when VDD ≥ VDDMIN.

### 21.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

TABLE 24-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |                   |                                                                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                    |     |       |                         |  |

|--------------------|-------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-------------------------|--|

| Param<br>No.       | Symbol            | Characteristic                                                        | Min                                                                                                                                                                                                    | Typ <sup>(1)</sup> | Max | Units | Conditions              |  |

| Operati            | Operating Voltage |                                                                       |                                                                                                                                                                                                        |                    |     |       |                         |  |

| DC10               | Vdd               | Supply Voltage <sup>(4)</sup>                                         | 3.0                                                                                                                                                                                                    | _                  | 3.6 | V     | Industrial and Extended |  |

| DC12               | Vdr               | RAM Data Retention Voltage <sup>(2)</sup>                             | 1.8                                                                                                                                                                                                    | _                  | _   | V     |                         |  |

| DC16               | VPOR              | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal      | _                                                                                                                                                                                                      | _                  | Vss | V     |                         |  |

| DC17               | SVDD              | VDD Rise Rate <sup>(3)</sup> to Ensure Internal Power-on Reset Signal | 0.03                                                                                                                                                                                                   | _                  | _   | V/ms  | 0V-3.0V in 0.1 seconds  |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 2: This is the limit to which VDD may be lowered without losing RAM data.

- 3: These parameters are characterized but not tested in manufacturing.

- **4:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 24-11 for BOR values.

TABLE 24-40: 10-BIT HIGH-SPEED ADC MODULE SPECIFICATIONS

| AC CHARACTERISTICS |               |                                                | Standard Operating Conditions (see Note 2): 3.0V and 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |           |      |       |                                                                       |  |

|--------------------|---------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------|-----------------------------------------------------------------------|--|

| Param<br>No.       | Symbol        | Characteristic                                 | Min.                                                                                                                                                                                                                                                            | Тур.      | Max. | Units | Conditions                                                            |  |

|                    | Device Supply |                                                |                                                                                                                                                                                                                                                                 |           |      |       |                                                                       |  |

| AD01               | AVDD          | Module VDD Supply                              | _                                                                                                                                                                                                                                                               | _         | _    | _     | AVDD is internally connected to VDD; see Parameter DC10 in Table 24-4 |  |

| AD02               | AVss          | Module Vss Supply                              | _                                                                                                                                                                                                                                                               | _         | _    | _     | AVss is internally connected to Vss                                   |  |

|                    | •             |                                                | Analog                                                                                                                                                                                                                                                          | Input     |      |       |                                                                       |  |

| AD10               | VINH-VINL     | Full-Scale Input Span                          | Vss                                                                                                                                                                                                                                                             | _         | VDD  | V     |                                                                       |  |

| AD11               | VIN           | Absolute Input Voltage                         | AVss                                                                                                                                                                                                                                                            | _         | AVdd | V     |                                                                       |  |

| AD12               | IAD           | Operating Current                              | _                                                                                                                                                                                                                                                               | 8         | _    | mΑ    |                                                                       |  |

| AD13               | _             | Leakage Current                                | _                                                                                                                                                                                                                                                               | ±0.6      | _    | μА    | VINL = AVSS = 0V, AVDD = 3.3V,<br>Source Impedance = $100\Omega$      |  |

| AD17               | RIN           | Recommended Impedance Of Analog Voltage Source | _                                                                                                                                                                                                                                                               | _         | 100  | Ω     |                                                                       |  |

|                    |               | DC Ac                                          | curacy                                                                                                                                                                                                                                                          | @ 1.5 Msp | s    |       |                                                                       |  |

| AD20A              | Nr            | Resolution                                     |                                                                                                                                                                                                                                                                 | 10 Data   | Bits |       |                                                                       |  |

| AD21A              | INL           | Integral Nonlinearity                          | -0.5                                                                                                                                                                                                                                                            | -0.3/+0.5 | +1.2 | LSb   |                                                                       |  |

| AD22A              | DNL           | Differential Nonlinearity                      | -0.9                                                                                                                                                                                                                                                            | ±0.6      | +0.9 | LSb   |                                                                       |  |

| AD23A              | GERR          | Gain Error                                     | 13                                                                                                                                                                                                                                                              | 15        | 22   | LSb   |                                                                       |  |

| AD24A              | EOFF          | Offset Error                                   | 6                                                                                                                                                                                                                                                               | 7         | 8    | LSb   |                                                                       |  |

| AD25A              | _             | Monotonicity <sup>(1)</sup>                    | _                                                                                                                                                                                                                                                               | _         |      | _     | Guaranteed                                                            |  |

|                    |               | DC Ac                                          | curacy                                                                                                                                                                                                                                                          | @ 1.7 Msp | s    |       |                                                                       |  |

| AD20B              | Nr            | Resolution                                     | 10 Data Bits                                                                                                                                                                                                                                                    |           |      |       |                                                                       |  |

| AD21B              | INL           | Integral Nonlinearity                          | -0.5                                                                                                                                                                                                                                                            | -0.4/+1.1 | +1.8 | LSb   |                                                                       |  |

| AD22B              |               | Differential Nonlinearity                      | -1.0                                                                                                                                                                                                                                                            | ±1.0      | +1.5 | LSb   |                                                                       |  |

| AD23B              | GERR          | Gain Error                                     | 13                                                                                                                                                                                                                                                              | 15        | 22   | LSb   |                                                                       |  |

| AD24B              | EOFF          | Offset Error                                   | 6                                                                                                                                                                                                                                                               | 7         | 8    | LSb   |                                                                       |  |

| AD25B              | _             | Monotonicity <sup>(1)</sup>                    | _                                                                                                                                                                                                                                                               | _         | _    | _     | Guaranteed                                                            |  |

|                    |               | DC Ac                                          | curacy                                                                                                                                                                                                                                                          | @ 2.0 Msp |      |       |                                                                       |  |

| AD20C              |               | Resolution                                     |                                                                                                                                                                                                                                                                 | 10 Data   | Bits |       |                                                                       |  |

| AD21C              |               | Integral Nonlinearity                          | -0.8                                                                                                                                                                                                                                                            | -0.5/+1.8 | +2.8 | LSb   |                                                                       |  |

| AD22C              | DNL           | Differential Nonlinearity                      | -1.0                                                                                                                                                                                                                                                            | -1.0/+1.8 | +2.8 | LSb   |                                                                       |  |

| AD23C              |               | Gain Error                                     | 14                                                                                                                                                                                                                                                              | 16        | 23   | LSb   |                                                                       |  |

| AD24C              | EOFF          | Offset Error                                   | 6                                                                                                                                                                                                                                                               | 7         | 8    | LSb   |                                                                       |  |

| AD25C              | _             | Monotonicity <sup>(1)</sup>                    |                                                                                                                                                                                                                                                                 |           | _    | _     | Guaranteed                                                            |  |

|                    | i             |                                                | amic Pe                                                                                                                                                                                                                                                         | rformance |      |       | <u>†</u>                                                              |  |

| AD30               | THD           | Total Harmonic Distortion                      |                                                                                                                                                                                                                                                                 | -73       | _    | dB    |                                                                       |  |

| AD31               | SINAD         | Signal to Noise and Distortion                 | _                                                                                                                                                                                                                                                               | 58        | _    | dB    |                                                                       |  |

| AD32               | SFDR          | Spurious Free Dynamic Range                    |                                                                                                                                                                                                                                                                 | -73       | _    | dB    |                                                                       |  |

| AD33               | FNYQ          | Input Signal Bandwidth                         |                                                                                                                                                                                                                                                                 |           | 1    | MHz   |                                                                       |  |

| AD34               | ENOB          | Effective Number of Bits                       | _                                                                                                                                                                                                                                                               | 9.4       | _    | bits  |                                                                       |  |

**Note 1:** The Analog-to-Digital conversion result never decreases with an increase in input voltage, and has no missing codes.

<sup>2:</sup> Module is functional at VBOR < VDD < VDDMIN, but with degraded performance. Module functionality is tested but not characterized.

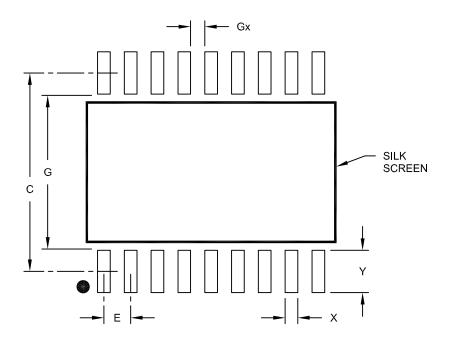

# 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

te: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                       | Units  | N    | ILLIMETER | S    |

|-----------------------|--------|------|-----------|------|

| Dimension             | Limits | MIN  | NOM       | MAX  |

| Contact Pitch         | E      |      | 1.27 BSC  |      |

| Contact Pad Spacing   | C      |      | 9.40      |      |

| Contact Pad Width     | X      |      |           | 0.60 |

| Contact Pad Length    | Υ      |      |           | 2.00 |

| Distance Between Pads | Gx     | 0.67 |           |      |

| Distance Between Pads | G      | 7.40 |           |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name             | Update Description                                                                                                                                                                                                                           |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 23.0 "Electrical | Updated Typ values for Thermal Packaging Characteristics (Table 23-3).                                                                                                                                                                       |

| Characteristics"         | Removed Typ value for DC Temperature and Voltage Specifications Parameter DC12 (Table 23-4).                                                                                                                                                 |

|                          | Updated all Typ values and conditions for DC Characteristics: Operating Current (IDD), updated last sentence in Note 2 (Table 23-5).                                                                                                         |

|                          | Updated all Typ values for DC Characteristics: Idle Current (IIDLE) (see Table 23-6).                                                                                                                                                        |

|                          | Updated all Typ values for DC Characteristics: Power Down Current (IPD) (see Table 23-7).                                                                                                                                                    |

|                          | Updated all Typ values for DC Characteristics: Doze Current (IDOZE) (see Table 23-8).                                                                                                                                                        |

|                          | Added Note 4 (reference to new table containing digital-only and analog pin information, as well as Current Sink/Source capabilities) in the I/O Pin Input Specifications (Table 23-9).                                                      |

|                          | Updated Max value for BOR electrical characteristics Parameter BO10 (see Table 23-11).                                                                                                                                                       |

|                          | Swapped Min and Typ values for Program Memory Parameters D136 and D137 (Table 23-12).                                                                                                                                                        |

|                          | Updated Typ values for Internal RC Accuracy Parameter F20 and added Extended temperature range to table heading (see Table 23-19).                                                                                                           |

|                          | Removed all values for Reset, Watchdog Timer, Oscillator Start-up Timer, and Power-up Timer Parameter SY20 and updated conditions, which now refers to <b>Section 20.4 "Watchdog Timer (WDT)"</b> and LPRC Parameter F21a (see Table 23-22). |

|                          | Added specifications to High-Speed PWM Module Timing Requirements for Tap Delay (Table 23-29).                                                                                                                                               |

|                          | Updated Min and Max values for 10-bit High-Speed Analog-to-Digital Module Parameters AD01 and AD11 (see Table 23-36).                                                                                                                        |

|                          | Updated Max value and unit of measure for DAC AC Specification (see Table 23-40).                                                                                                                                                            |