Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 50 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 2K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10b; D/A 4x10b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs504-50i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-7: | INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06G202 DEVICES ONLY |

|------------|--------------------------------------------------------------------|

|------------|--------------------------------------------------------------------|

|              | 4-1.        |         |          |          |          |         |          |          | usric.   |          |                |          |          |         |          |          |               |               |

|--------------|-------------|---------|----------|----------|----------|---------|----------|----------|----------|----------|----------------|----------|----------|---------|----------|----------|---------------|---------------|

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14   | Bit 13   | Bit 12   | Bit 11  | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6          | Bit 5    | Bit 4    | Bit 3   | Bit 2    | Bit 1    | Bit 0         | All<br>Resets |

| INTCON1      | 0080        | NSTDIS  | OVAERR   | OVBERR   | COVAERR  | COVBERR | OVATE    | OVBTE    | COVTE    | SFTACERR | <b>DIV0ERR</b> | —        | MATHERR  | ADDRERR | STKERR   | OSCFAIL  | _             | 0000          |

| INTCON2      | 0082        | ALTIVT  | DISI     | _        | _        | _       | _        | —        | _        | _        | _              | _        | _        | _       | INT2EP   | INT1EP   | INT0EP        | 0000          |

| IFS0         | 0084        | _       | _        | ADIF     | U1TXIF   | U1RXIF  | SPI1IF   | SPI1EIF  | -        | T2IF     | _              |          |          | T1IF    | OC1IF    | IC1IF    | <b>INTOIF</b> | 0000          |

| IFS1         | 0086        | _       | _        | INT2IF   | _        | _       | _        | _        | _        | _        | _              |          | INT1IF   | CNIF    | AC1IF    | MI2C1IF  | SI2C1IF       | 0000          |

| IFS3         | 008A        | _       | _        | _        | _        | -       | -        | PSEMIF   | _        | _        | _              |          |          | -       | _        | _        |               | 0000          |

| IFS4         | 008C        | _       | _        | _        | —        | _       | _        | _        | _        | —        | —              | _        | _        | _       | —        | U1EIF    | _             | 0000          |

| IFS5         | 008E        | PWM2IF  | PWM1IF   | _        | —        | _       | _        | _        | _        | —        | —              | _        | _        | _       | —        | _        | _             | 0000          |

| IFS6         | 0090        | ADCP1IF | ADCP0IF  | _        | _        | _       | _        | _        | _        | AC2IF    | _              | _        | _        | _       | _        | _        | _             | 0000          |

| IFS7         | 0092        | _       | _        | _        | _        | _       | _        | _        | _        | —        | _              | _        | ADCP6IF  | _       | _        | _        | ADCP2IF       | 0000          |

| IEC0         | 0094        | _       | _        | ADIE     | U1TXIE   | U1RXIE  | SPI1IE   | SPI1EIE  |          | T2IE     | _              |          |          | T1IE    | OC1IE    | IC1IE    | INT0IE        | 0000          |

| IEC1         | 0096        | _       | _        | INT2IE   | —        | _       |          | —        |          | —        | _              |          | INT1IE   | CNIE    | AC1IE    | MI2C1IE  | SI2C1IE       | 0000          |

| IEC3         | 009A        | _       | _        |          | _        | _       |          | PSEMIE   |          | —        | _              |          |          |         | —        | _        | _             | 0000          |

| IEC4         | 009C        | _       | _        |          | _        | _       |          | —        |          | —        | _              |          |          |         | —        | U1EIE    | _             | 0000          |

| IEC5         | 009E        | PWM2IE  | PWM1IE   |          | _        | _       |          | —        |          | —        | _              |          |          |         | —        | _        | _             | 0000          |

| IEC6         | 00A0        | ADCP1IE | ADCP0IE  |          | _        |         |          | _        |          | AC2IE    | _              |          |          |         | —        | _        |               | 0000          |

| IEC7         | 00A2        | _       |          |          | _        |         |          | _        |          | _        | _              |          | ADCP6IE  |         | —        | _        | ADCP2IE       | 0000          |

| IPC0         | 00A4        | _       | T1IP2    | T1IP1    | T1IP0    |         | OC1IP2   | OC1IP1   | OC1IP0   | _        | IC1IP2         | IC1IP1   | IC1IP0   |         | INT0IP2  | INT0IP1  | INT0IP0       | 4444          |

| IPC1         | 00A6        | _       | T2IP2    | T2IP1    | T2IP0    |         |          | _        |          | _        | _              |          |          |         | —        | _        |               | 4000          |

| IPC2         | 00A8        | _       | U1RXIP2  | U1RXIP1  | U1RXIP0  |         | SPI1IP2  | SPI1IP1  | SPI1IP0  | _        | SPI1EIP2       | SPI1EIP1 | SPI1EIP0 |         | —        | _        |               | 4440          |

| IPC3         | 00AA        | _       |          |          | _        |         |          | _        |          | _        | ADIP2          | ADIP1    | ADIP0    |         | U1TXIP2  | U1TXIP1  | U1TXIP0       | 0044          |

| IPC4         | 00AC        | _       | CNIP2    | CNIP1    | CNIP0    |         | AC1IP2   | AC1IP1   | AC1IP0   | _        | MI2C1IP2       | MI2C1IP1 | MI2C1IP0 |         | SI2C1IP2 | SI2C1IP1 | SI2C1IP0      | 4444          |

| IPC5         | 00AE        | _       |          |          | _        |         |          | _        |          | _        | _              |          |          |         | INT1IP2  | INT1IP1  | INT1IP0       | 0004          |

| IPC7         | 00B2        | _       |          |          | _        |         |          | _        |          | _        | INT2IP2        | INT2IP1  | INT2IP0  |         | —        | _        |               | 0040          |

| IPC14        | 00C0        | _       |          |          | _        |         |          | _        |          | _        | PSEMIP2        | PSEMIP1  | PSEMIP0  |         | —        | _        |               | 0040          |

| IPC16        | 00C4        | _       |          |          | _        |         |          | _        |          | _        | U1EIP2         | U1EIP1   | U1EIP0   |         | —        | _        |               | 0040          |

| IPC23        | 00D2        | _       | PWM2IP2  | PWM2IP1  | PWM2IP0  |         | PWM1IP2  | PWM1IP1  | PWM1IP0  | _        | _              |          |          |         | —        | _        |               | 4400          |

| IPC25        | 00D6        | _       | AC2IP2   | AC2IP1   | AC2IP0   |         |          | _        |          | _        | _              |          |          |         | —        | _        |               | 4000          |

| IPC27        | 00DA        | _       | ADCP1IP2 | ADCP1IP1 | ADCP1IP0 | —       | ADCP0IP2 | ADCP0IP1 | ADCP0IP0 | —        | —              | —        | _        | _       | —        | —        | _             | 4400          |

| IPC28        | 00DC        | _       | _        |          | —        | -       |          | -        |          | —        | _              |          |          |         | ADCP2IP2 | ADCP2IP1 | ADCP2IP0      | 0004          |

| IPC29        | 00DE        |         | _        | _        | —        | _       | -        | _        | _        | —        | _              | —        | _        | _       | ADCP6IP2 | ADCP6IP1 | ADCP6IP0      | 0004          |

| INTTREG      | 00E0        | —       | _        | _        | —        | ILR3    | ILR2     | ILR1     | ILR0     | —        | VECNUM6        | VECNUM5  | VECNUM4  | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

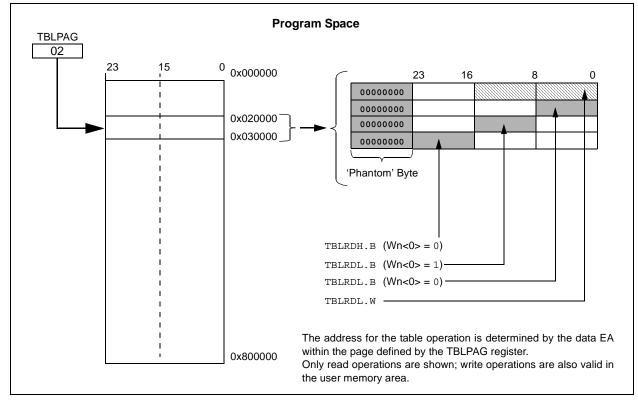

### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# 5.2 RTSP Operation

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 24-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the Table Write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

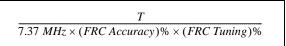

The programming time depends on the FRC accuracy (see Table 24-20) and the value of the FRC Oscillator Tuning register (see Register 8-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time, and Word Write Cycle Time parameters (see Table 24-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 8-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

# EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

# EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

# 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| <br> | -             |                            |                                         | _ |

|------|---------------|----------------------------|-----------------------------------------|---|

| ;    | Set up NVMCO  | N for row programming open | rations                                 |   |

|      | MOV           | #0x4001, W0                | ;                                       |   |

|      | MOV           | W0, NVMCON                 | ; Initialize NVMCON                     |   |

| ;    | Set up a poir | nter to the first program  | memory location to be written           |   |

| ;    | program memo: | ry selected, and writes en | nabled                                  |   |

|      | MOV           | #0x0000, W0                | ;                                       |   |

|      | MOV           | W0, TBLPAG                 | ; Initialize PM Page Boundary SFR       |   |

|      | MOV           | #0x6000, W0                | ; An example program memory address     |   |

| ;    | Perform the   | TBLWT instructions to writ | te the latches                          |   |

| ;    | 0th_program_v | word                       |                                         |   |

|      | MOV           | #LOW_WORD_0, W2            | i                                       |   |

|      | MOV           | #HIGH_BYTE_0, W3           | ;                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

| ;    | lst_program_  | word                       |                                         |   |

|      | MOV           | #LOW_WORD_1, W2            | ;                                       |   |

|      | MOV           | #HIGH_BYTE_1, W3           | i                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

| ;    | 2nd_program   | _word                      |                                         |   |

|      | MOV           | #LOW_WORD_2, W2            | i                                       |   |

|      | MOV           | #HIGH_BYTE_2, W3           | i                                       |   |

|      | TBLWTL        | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

|      | •             |                            |                                         |   |

|      | •             |                            |                                         |   |

|      | •             |                            |                                         |   |

| ;    | 63rd_program  |                            |                                         |   |

|      |               | #LOW_WORD_31, W2           | ;                                       |   |

|      |               | #HIGH_BYTE_31, W3          | ;                                       |   |

|      |               | W2, [W0]                   | ; Write PM low word into program latch  |   |

|      | TBLWTH        | W3, [W0++]                 | ; Write PM high byte into program latch |   |

|      |               |                            |                                         |   |

EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | <pre>; Block all interrupts with priority &lt;7 ; for next 5 instructions</pre> |

|------|-------------|---------------------------------------------------------------------------------|

| MOV  | #0x55, W0   |                                                                                 |

| MOV  | W0, NVMKEY  | ; Write the 55 key                                                              |

| MOV  | #0xAA, W1   | ;                                                                               |

| MOV  | W1, NVMKEY  | ; Write the AA key                                                              |

| BSET | NVMCON, #WR | ; Start the erase sequence                                                      |

| NOP  |             | ; Insert two NOPs after the                                                     |

| NOP  |             | ; erase command is asserted                                                     |

|      |             |                                                                                 |

## 6.1 System Reset

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 families of devices have two types of Reset:

- Cold Reset

- Warm Reset

A Cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a Cold Reset, the FNOSCx Configuration bits in the FOSC Configuration register select the device clock source. A Warm Reset is the result of all the other Reset sources, including the RESET instruction. On Warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection (COSC<2:0>) bits in the Oscillator Control (OSCCON<14:12>) register.

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is detailed in Figure 6-2.

| Oscillator Mode           | Oscillator<br>Startup Delay | Oscillator<br>Startup Timer | PLL Lock Time        | Total Delay                             |

|---------------------------|-----------------------------|-----------------------------|----------------------|-----------------------------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd <sup>(1)</sup>        | _                           | _                    | Toscd <sup>(1)</sup>                    |

| FRCPLL                    | Toscd <sup>(1)</sup>        | _                           | ТLОСК <sup>(3)</sup> | Toscd + Tlock <sup>(1,3)</sup>          |

| XT                        | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| HS                        | Toscd(1)                    | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| EC                        | —                           | —                           | —                    | —                                       |

| XTPLL                     | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | ТLОСК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| HSPLL                     | Toscd(1)                    | Tost <sup>(2)</sup>         | ТLOCК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| ECPLL                     | —                           | —                           | ТLОСК <sup>(3)</sup> | TLOCK <sup>(3)</sup>                    |

| LPRC                      | Toscd <sup>(1)</sup>        | _                           | —                    | Toscd <sup>(1)</sup>                    |

## TABLE 6-1:OSCILLATOR DELAY

**Note 1:** TOSCD = Oscillator start-up delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal) if PLL is enabled.

### REGISTER 7-12: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0                                                        | U-0                           | U-0              | U-0            | U-0              | U-0              | U-0             | U-0     |  |  |

|------------------------------------------------------------|-------------------------------|------------------|----------------|------------------|------------------|-----------------|---------|--|--|

| —                                                          | —                             | —                | —              | —                | —                | —               | —       |  |  |

| bit 15                                                     |                               |                  |                |                  |                  |                 | bit 8   |  |  |

|                                                            |                               |                  |                |                  |                  |                 |         |  |  |

| U-0                                                        | U-0                           | U-0              | U-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |

| —                                                          | —                             | —                | —              | —                | INT1IP2          | INT1IP1         | INT1IP0 |  |  |

| bit 7                                                      |                               |                  |                |                  | •                |                 | bit 0   |  |  |

|                                                            |                               |                  |                |                  |                  |                 |         |  |  |

| Legend:                                                    |                               |                  |                |                  |                  |                 |         |  |  |

| R = Readab                                                 | ole bit                       | W = Writable     | bit            | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |

| -n = Value a                                               | at POR                        | '1' = Bit is set |                | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |  |  |

|                                                            |                               |                  |                |                  |                  |                 |         |  |  |

| bit 15-3                                                   | Unimplemen                    | ted: Read as '   | 0'             |                  |                  |                 |         |  |  |

| bit 2-0                                                    | INT1IP<2:0>:                  | External Interr  | upt 1 Priority | bits             |                  |                 |         |  |  |

| 111 = Interrupt is Priority 7 (highest priority interrupt) |                               |                  |                |                  |                  |                 |         |  |  |

|                                                            | •                             |                  |                |                  |                  |                 |         |  |  |

|                                                            | •                             |                  |                |                  |                  |                 |         |  |  |

|                                                            | •                             |                  |                |                  |                  |                 |         |  |  |

|                                                            | 001 = Interrupt is Priority 1 |                  |                |                  |                  |                 |         |  |  |

#### REGISTER 7-24: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

## REGISTER 7-25: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0                           | U-0           | U-0                | U-0             | U-0              | U-0              | U-0                | U-0   |  |  |  |

|-------------------------------|---------------|--------------------|-----------------|------------------|------------------|--------------------|-------|--|--|--|

| —                             | —             | —                  | _               | —                | —                | —                  | —     |  |  |  |

| bit 15                        |               |                    |                 |                  |                  |                    | bit 8 |  |  |  |

|                               |               |                    |                 |                  |                  |                    |       |  |  |  |

| U-0                           | R/W-1         | R/W-0              | R/W-0           | U-0              | U-0              | U-0                | U-0   |  |  |  |

|                               | INT2IP2       | INT2IP1            | INT2IP0         | —                | —                | —                  | —     |  |  |  |

| bit 7                         |               |                    |                 |                  |                  |                    | bit 0 |  |  |  |

|                               |               |                    |                 |                  |                  |                    |       |  |  |  |

| Legend:                       |               |                    |                 |                  |                  |                    |       |  |  |  |

| R = Readable                  | e bit         | W = Writable       | bit             | U = Unimpler     | mented bit, read | l as '0'           |       |  |  |  |

| -n = Value at                 | POR           | '1' = Bit is set   |                 | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |  |  |

|                               |               |                    |                 |                  |                  |                    |       |  |  |  |

| bit 15-7                      | Unimplemen    | ted: Read as '     | 0'              |                  |                  |                    |       |  |  |  |

| bit 6-4                       | INT2IP<2:0>:  | External Interr    | rupt 2 Priority | bits             |                  |                    |       |  |  |  |

|                               | 111 = Interru | pt is Priority 7 ( | highest priorit | y interrupt)     |                  |                    |       |  |  |  |

|                               | •             |                    |                 |                  |                  |                    |       |  |  |  |

|                               | •             |                    |                 |                  |                  |                    |       |  |  |  |

|                               |               |                    |                 |                  |                  |                    |       |  |  |  |

| 001 = Interrupt is Priority 1 |               |                    |                 |                  |                  |                    |       |  |  |  |

|                               | 000 = Interru | pt source is dis   | abied           |                  |                  |                    |       |  |  |  |

|                               |               |                    |                 |                  |                  |                    |       |  |  |  |

| bit 3-0                       | Unimplemen    | ted: Read as '     | 0'              |                  |                  |                    |       |  |  |  |

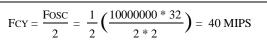

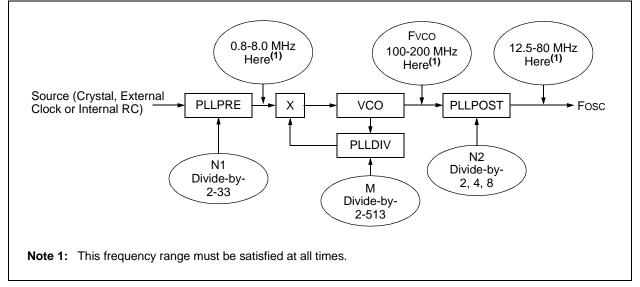

## 8.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 8-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor, 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor, 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4, or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS. For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by Equation 8-2.

## EQUATION 8-2: Fosc CALCULATION

$$FOSC = FIN * \left(\frac{M}{N1*N2}\right)$$

For example, suppose a 10 MHz crystal is being used with the selected oscillator mode of XT with PLL (see Equation 8-3).

- If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

- If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

### EQUATION 8-3: XT WITH PLL MODE EXAMPLE

### FIGURE 8-2: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 PLL BLOCK DIAGRAM

# 8.4 Oscillator Control Registers

# **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,2)</sup>

| U-0     | R-0    | R-0   | R-0   | U-0   | R/W-y                | R/W-y                | R/W-y                |

|---------|--------|-------|-------|-------|----------------------|----------------------|----------------------|

| —       | COSC2  | COSC1 | COSC0 | —     | NOSC2 <sup>(3)</sup> | NOSC1 <sup>(3)</sup> | NOSC0 <sup>(3)</sup> |

| bit 15  |        |       |       |       |                      |                      | bit 8                |

|         |        |       |       |       |                      |                      |                      |

| R/W-0   | R/W-0  | R-0   | U-0   | R/C-0 | U-0                  | U-0                  | R/W-0                |

| CLKLOCK | IOLOCK | LOCK  | —     | CF    | _                    | —                    | OSWEN                |

| bit 7   |        |       |       |       |                      |                      | bit 0                |

| Legend:           | y = Value set from Co | onfiguration bits on POR |                    |

|-------------------|-----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit    | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared     | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits (read-only)                                                                                                                                                                                                                                                                    |

|           | <pre>111 = Fast RC oscillator (FRC) with divide-by-n 110 = Fast RC oscillator (FRC) with divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Reserved 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL 000 = Fast RC oscillator (FRC)</pre> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(3)</sup>                                                                                                                                                                                                                                                                     |

|           | <pre>111 = Fast RC oscillator (FRC) with divide-by-n 110 = Fast RC oscillator (FRC) with divide-by-16 101 = Low-Power RC oscillator (LPRC) 100 = Reserved 011 = Primary oscillator (XT, HS, EC) with PLL 010 = Primary oscillator (XT, HS, EC) 001 = Fast RC oscillator (FRC) with PLL</pre>                                |

|           | 000 = Fast RC oscillator (FRC)                                                                                                                                                                                                                                                                                              |

| bit 7     | CLKLOCK: Clock Lock Enable bit                                                                                                                                                                                                                                                                                              |

|           | <pre>If Clock Switching is Enabled and FSCM is Disabled, (FOSC<fcksm> = 0b01): 1 = Clock switching is disabled, system clock source is locked 0 = Clock switching is enabled, system clock source can be modified by clock switching</fcksm></pre>                                                                          |

| bit 6     | IOLOCK: Peripheral Pin Select Lock bit                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Peripheral Pin Select is locked, write to Peripheral Pin Select registers not allowed</li> <li>0 = Peripheral Pin Select is not locked, write to Peripheral Pin Select registers allowed</li> </ul>                                                                                                            |

| bit 5     | LOCK: PLL Lock Status bit (read-only)                                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Indicates that PLL is in lock, or PLL start-up timer is satisfied</li> <li>0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled</li> </ul>                                                                                                                                  |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                  |

| Note 1:   | Writes to this register require an unlock sequence. Refer to " <b>Oscillator (Part IV)</b> " (DS70307) in the<br>"dsPIC33F/PIC24H Family Reference Manual" (available from the Microchip web site) for details.                                                                                                             |

| 2:        | This register is reset only on a Power-on Reset (POR).                                                                                                                                                                                                                                                                      |

| 3:        | Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted.<br>This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.                                            |

mode as a transition clock source between the two PLL modes.

|                             | • = • • • • • • • • • • • • • • • • • •                                                         |                                                                  |                                                                                  |                                         |                 |          |       |  |

|-----------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------|-----------------|----------|-------|--|

| U-0                         | U-0                                                                                             | U-0                                                              | U-0                                                                              | U-0                                     | U-0             | R/W-0    | R/W-0 |  |

| —                           | —                                                                                               | —                                                                | —                                                                                | —                                       | _               | IC2MD    | IC1MD |  |

| it 15                       |                                                                                                 |                                                                  |                                                                                  |                                         |                 |          | bit 8 |  |

| U-0                         | U-0                                                                                             | U-0                                                              | U-0                                                                              | U-0                                     | U-0             | R/W-0    | R/W-0 |  |

| _                           | —                                                                                               | —                                                                |                                                                                  | _                                       |                 | OC2MD    | OC1MD |  |

| oit 7                       | ·                                                                                               |                                                                  |                                                                                  |                                         |                 |          | bit C |  |

| _egend:                     |                                                                                                 |                                                                  |                                                                                  |                                         |                 |          |       |  |

| R = Readabl                 | e bit                                                                                           | W = Writable                                                     | bit                                                                              | U = Unimplem                            | nented bit, rea | d as '0' |       |  |

| -n = Value at               | POR                                                                                             | '1' = Bit is set                                                 |                                                                                  | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |

| bit 15-10<br>bit 9<br>bit 8 | <b>IC2MD</b> : Input<br>1 = Input Cap<br>0 = Input Cap<br><b>IC1MD</b> : Input<br>1 = Input Cap | ture 2 module<br>ture 2 module<br>Capture 1 Moo<br>ture 1 module | dule Disable bit<br>is disabled<br>is enabled<br>dule Disable bit<br>is disabled |                                         |                 |          |       |  |

| bit 7-2                     |                                                                                                 | ture 1 module<br>t <b>ed:</b> Read as 'd                         |                                                                                  |                                         |                 |          |       |  |

| bit 1                       | 1 = Output Co                                                                                   | out Compare 2<br>ompare 2 modu<br>ompare 2 modu                  |                                                                                  | e bit                                   |                 |          |       |  |

| bit 0                       | 1 = Output Co                                                                                   | out Compare 1<br>ompare 1 modu<br>ompare 1 modu                  |                                                                                  | e bit                                   |                 |          |       |  |

## REGISTER 9-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0          | U-0                       | U-0                                          | U-0      | U-0                  | U-0              | U-0                | U-0      |  |  |  |

|--------------|---------------------------|----------------------------------------------|----------|----------------------|------------------|--------------------|----------|--|--|--|

| _            | _                         | —                                            | _        | _                    | —                | _                  | _        |  |  |  |

| bit 15       |                           |                                              |          |                      |                  |                    | bit 8    |  |  |  |

|              |                           |                                              |          |                      |                  |                    |          |  |  |  |

| U-0          | U-0                       | R/W-1                                        | R/W-1    | R/W-1                | R/W-1            | R/W-1              | R/W-1    |  |  |  |

|              | —                         | SYNCI2R5                                     | SYNCI2R4 | SYNCI2R3             | SYNCI2R2         | SYNCI2R1           | SYNCI2R0 |  |  |  |

| bit 7        |                           |                                              |          |                      |                  |                    | bit 0    |  |  |  |

| Legend:      |                           |                                              |          |                      |                  |                    |          |  |  |  |

| R = Readab   | le bit                    | W = Writable                                 | bit      | U = Unimpler         | mented bit, read | l as '0'           |          |  |  |  |

| -n = Value a | t POR                     | '1' = Bit is set                             |          | '0' = Bit is cleared |                  | x = Bit is unknown |          |  |  |  |

|              |                           |                                              |          |                      |                  |                    | -        |  |  |  |

| bit 15-6     | Unimplemer                | nted: Read as '                              | 0'       |                      |                  |                    |          |  |  |  |

| bit 5-0      |                           | : <b>0&gt;:</b> Assign PW<br>ng RPn Pin bits |          | e Base Extern        | al Synchronizat  | ion Signal to th   | e        |  |  |  |

|              | 111111 = <b>I</b> n       | put tied to Vss                              |          |                      |                  |                    |          |  |  |  |

|              |                           | put tied to RP3                              |          |                      |                  |                    |          |  |  |  |

|              |                           | put tied to RP34                             |          |                      |                  |                    |          |  |  |  |

|              |                           | put tied to RP33<br>put tied to RP32         |          |                      |                  |                    |          |  |  |  |

|              | 100000 = 11               |                                              | 2        |                      |                  |                    |          |  |  |  |

|              | •                         |                                              |          |                      |                  |                    |          |  |  |  |

|              | •                         |                                              |          |                      |                  |                    |          |  |  |  |

|              | -<br>                     | ut tied to PP0                               |          |                      |                  |                    |          |  |  |  |

|              | 00000 = Input tied to RP0 |                                              |          |                      |                  |                    |          |  |  |  |

# REGISTER 10-14: RPINR34: PERIPHERAL PIN SELECT INPUT REGISTER 34

# REGISTER 10-15: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0                                                                                                                                    | R/W-0            | R/W-0 | R/W-0                              | R/W-0                     | R/W-0 | R/W-0 |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|------------------------------------|---------------------------|-------|-------|--|--|

| _             | _                                                                                                                                      | RP1R5            | RP1R4 | RP1R3                              | RP1R2                     | RP1R1 | RP1R0 |  |  |

| bit 15        |                                                                                                                                        |                  |       |                                    |                           |       | bit 8 |  |  |

|               |                                                                                                                                        |                  |       |                                    |                           |       |       |  |  |

| U-0           | U-0                                                                                                                                    | R/W-0            | R/W-0 | R/W-0                              | R/W-0                     | R/W-0 | R/W-0 |  |  |

| _             | —                                                                                                                                      | RP0R5            | RP0R4 | RP0R3                              | RP0R2                     | RP0R1 | RP0R0 |  |  |

| bit 7         |                                                                                                                                        |                  |       |                                    |                           |       | bit 0 |  |  |

|               |                                                                                                                                        |                  |       |                                    |                           |       |       |  |  |

| Legend:       |                                                                                                                                        |                  |       |                                    |                           |       |       |  |  |

| R = Readabl   | e bit                                                                                                                                  | W = Writable     | bit   | U = Unimplemented bit, read as '0' |                           |       |       |  |  |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set |       | '0' = Bit is cle                   | leared x = Bit is unknown |       |       |  |  |

|               |                                                                                                                                        |                  |       |                                    |                           |       |       |  |  |

| bit 15-14     | Unimplemen                                                                                                                             | ted: Read as '   | 0'    |                                    |                           |       |       |  |  |

| bit 13-8      | <b>RP1R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 10-2 for peripheral function numbers) |                  |       |                                    |                           |       |       |  |  |

| bit 7-6       | -6 Unimplemented: Read as '0'                                                                                                          |                  |       |                                    |                           |       |       |  |  |

|               |                                                                                                                                        |                  |       |                                    |                           |       |       |  |  |

bit 5-0 **RP0R<5:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-2 for peripheral function numbers)

## REGISTER 15-14: IOCONx: PWMx I/O CONTROL REGISTER (CONTINUED)

| bit 3-2 | CLDAT<1:0>: State for PWMxH and PWMxL Pins if CLMODE is Enabled bits <sup>(2)</sup>                          |  |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|         | FCLCONx <ifltmod> = 0: Normal Fault mode:</ifltmod>                                                          |  |  |  |  |  |  |  |

|         | If current-limit is active, then CLDAT<1> provides the state for PWMxH                                       |  |  |  |  |  |  |  |

|         | If current-limit is active, then CLDAT<0> provides the state for PWMxL                                       |  |  |  |  |  |  |  |

|         | FCLCONx <ifltmod> = 1: Independent Fault mode:</ifltmod>                                                     |  |  |  |  |  |  |  |

|         | CLDAT<1:0> bits are ignored.                                                                                 |  |  |  |  |  |  |  |

| bit 1   | SWAP<1:0>: Swap PWMxH and PWMxL pins                                                                         |  |  |  |  |  |  |  |

|         | 1 = PWMxH output signal is connected to the PWMxL pin and the PWMxL signal is connected to the<br>PWMxH pins |  |  |  |  |  |  |  |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                 |  |  |  |  |  |  |  |

| bit 0   | <b>OSYNC:</b> Output Override Synchronization bit                                                            |  |  |  |  |  |  |  |

|         | 1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWM time base                          |  |  |  |  |  |  |  |

|         | 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary                           |  |  |  |  |  |  |  |

| Note 1: | These bits should be changed only when PTEN = 0. Changing the clock selection during operation will          |  |  |  |  |  |  |  |

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 2: The state represents the active/inactive state of the PWM module depending on the POLH and POLL bit settings.

# 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CxSTAT are read/write:

- I2CxRSR is the shift register used for shifting data internal to the module and the user application has no access to it

- I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- The I2CxADD register holds the slave address

- A status bit, ADD10, indicates 10-Bit Addressing mode

- The I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV, and an interrupt pulse is generated.

| TABLE 22-2:        |               | INSTRUCTION SET OVERVIEW |                |                                          |               |                |                          |  |  |  |  |

|--------------------|---------------|--------------------------|----------------|------------------------------------------|---------------|----------------|--------------------------|--|--|--|--|

| Base<br>Instr<br># | nstr Mnemonic |                          |                |                                          | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |  |

| 1 ADD              |               | ADD                      | Acc            | Add Accumulators                         | 1             | 1              | OA,OB,SA,SE              |  |  |  |  |

|                    |               | ADD                      | f              | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADD                      | f,WREG         | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADD                      | #lit10,Wn      | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADD                      | Wb,Ws,Wd       | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADD                      | Wb,#lit5,Wd    | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADD                      | Wso,#Slit4,Acc | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,SE              |  |  |  |  |

| 2                  | ADDC          | ADDC                     | f              | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADDC                     | f,WREG         | WREG = $f + WREG + (C)$                  | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADDC                     | #lit10,Wn      | Wd = lit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADDC                     | Wb,Ws,Wd       | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |               | ADDC                     | Wb,#lit5,Wd    | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

| 3                  | AND           | AND                      | f              | f = f AND. WREG                          | 1             | 1              | N,Z                      |  |  |  |  |

| 0                  | 11112         | AND                      | f,WREG         | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |  |  |  |  |

|                    |               | AND                      | #lit10,Wn      | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |  |  |  |  |

|                    |               |                          |                | Wd = Wb .AND. Ws                         | 1             | 1              |                          |  |  |  |  |

|                    |               | AND                      | Wb,Ws,Wd       | Wd = Wb .AND. lit5                       |               |                | N,Z                      |  |  |  |  |

|                    |               | AND                      | Wb,#lit5,Wd    |                                          | 1             | 1              | N,Z                      |  |  |  |  |

| 4                  | ASR           | ASR                      | f              | f = Arithmetic Right Shift f             | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |               | ASR                      | f,WREG         | WREG = Arithmetic Right Shift f          | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |               | ASR                      | Ws,Wd          | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |               | ASR                      | Wb,Wns,Wnd     | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N,Z                      |  |  |  |  |

|                    |               | ASR                      | Wb,#lit5,Wnd   | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N,Z                      |  |  |  |  |

| 5                  | BCLR          | BCLR                     | f,#bit4        | Bit Clear f                              | 1             | 1              | None                     |  |  |  |  |

|                    |               | BCLR                     | Ws,#bit4       | Bit Clear Ws                             | 1             | 1              | None                     |  |  |  |  |

| 6                  | BRA           | BRA                      | C,Expr         | Branch if Carry                          | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | GE, Expr       | Branch if Greater Than or Equal          | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | GEU, Expr      | Branch if Unsigned Greater Than or Equal | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | GT,Expr        | Branch if Greater Than                   | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | GTU,Expr       | Branch if Unsigned Greater Than          | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | LE,Expr        | Branch if Less Than or Equal             | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | LEU,Expr       | Branch if Unsigned Less Than or Equal    | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | LT,Expr        | Branch if Less Than                      | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | LTU, Expr      | Branch if Unsigned Less Than             | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | N,Expr         | Branch if Negative                       | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | NC,Expr        | Branch if Not Carry                      | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | NN,Expr        | Branch if Not Negative                   | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | NOV, Expr      | Branch if Not Overflow                   | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | NZ,Expr        | Branch if Not Zero                       | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | OA,Expr        | Branch if Accumulator A Overflow         | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | OB,Expr        | Branch if Accumulator B Overflow         | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | OV,Expr        | Branch if Overflow                       | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | SA, Expr       | Branch if Accumulator A Saturated        | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | SB,Expr        | Branch if Accumulator B Saturated        | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | Expr           | Branch Unconditionally                   | 1             | 2              | None                     |  |  |  |  |

|                    |               | BRA                      | Z,Expr         | Branch if Zero                           | 1             | 1 (2)          | None                     |  |  |  |  |

|                    |               | BRA                      | Wn             | Computed Branch                          | 1             | 2              | None                     |  |  |  |  |

| 7                  | BSET          | BSET                     | f,#bit4        | Bit Set f                                | 1             | 1              | None                     |  |  |  |  |

|                    |               | BSET                     | Ws,#bit4       | Bit Set Ws                               | 1             | 1              | None                     |  |  |  |  |

| 8                  | BSW           | BSW.C                    | Ws,Wb          | Write C bit to Ws <wb></wb>              | 1             | 1              | None                     |  |  |  |  |

| 5                  | 1001          | BSW.C                    | Ws,Wb          | Write Z bit to Ws <wb></wb>              | 1             | 1              | None                     |  |  |  |  |

|                    |               | 2.wca                    | WW, 6W         |                                          |               |                |                          |  |  |  |  |

Bit Toggle f

Bit Toggle Ws

# TABLE 22-2: INSTRUCTION SET OVERVIEW

BTG

BTG

BTG

f,#bit4

Ws,#bit4

9

1

1

None

None

1

1

# 23.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> Digital Signal Controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 23.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

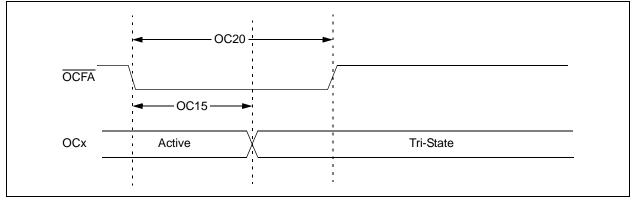

## FIGURE 24-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

### TABLE 24-28: SIMPLE OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |          |       |            |  |

|--------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min                                                                                                                                                                                                                                                                                     | Тур | Max      | Units | Conditions |  |

| OC15               | Tfd    | Fault Input to PWMx I/O<br>Change | _                                                                                                                                                                                                                                                                                       | _   | Tcy + 20 | ns    |            |  |

| OC20               | TFLT   | Fault Input Pulse Width           | Tcy + 20                                                                                                                                                                                                                                                                                | _   | —        | ns    |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

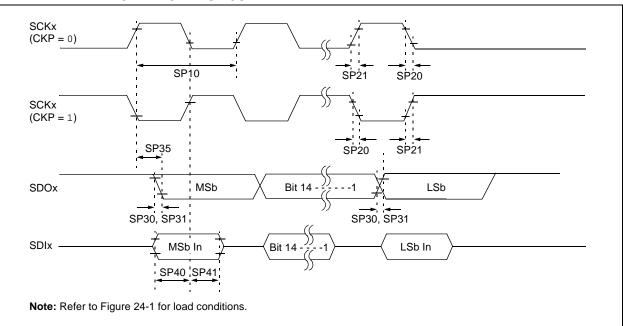

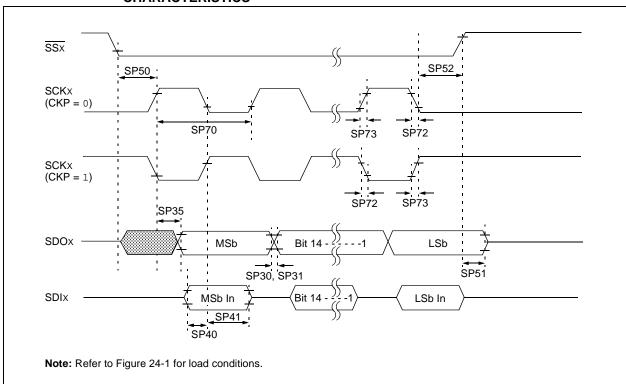

### FIGURE 24-14: SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 24-33:SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                                              |                                               |    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |       |                                      |  |  |

|--------------------|----------------------------------------------|-----------------------------------------------|----|-------------------------------------------------------|-----|-------|--------------------------------------|--|--|

| Param<br>No.       | Symbol Characteristic <sup>(1)</sup> Min Typ |                                               |    | Тур <sup>(2)</sup>                                    | Max | Units | Conditions                           |  |  |

| SP10               | TscP                                         | Maximum SCKx Frequency                        |    | —                                                     | 9   | MHz   | -40°C to +125°C and see Note 3       |  |  |

| SP20               | TscF                                         | SCKx Output Fall Time                         | _  | —                                                     | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |  |