Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

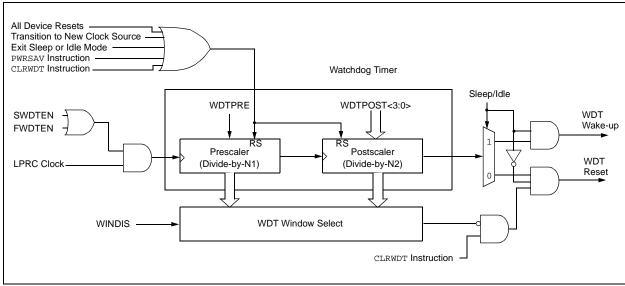

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10b; D/A 4x10b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

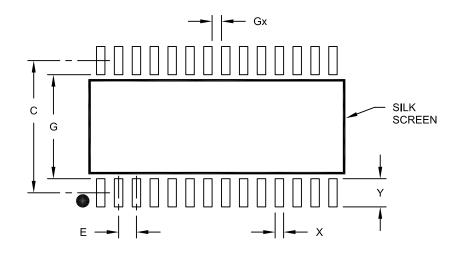

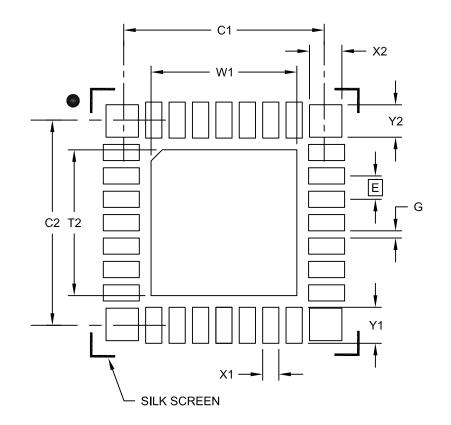

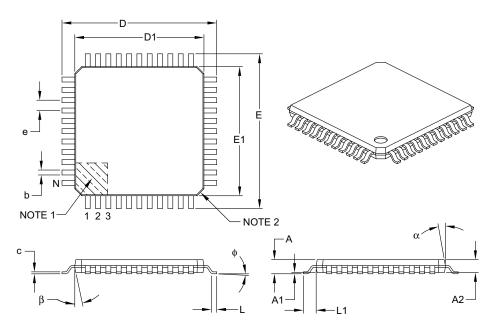

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs504-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

#### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/ 16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (for example, ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- Signed or Unsigned DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation | ACC<br>Write Back |

|-------------|------------------------|-------------------|

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

## 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY. N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

#### 6.8.2 UNINITIALIZED W REGISTER RESET

Any attempt to use the Uninitialized W register as an Address Pointer will reset the device. The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to.

#### 6.8.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (boot and secure segment), that operation will cause a Security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a call, jump, computed jump, return, return from subroutine or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an interrupt or trap vector.

Refer to Section 21.8 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

## 6.9 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the Reset.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

Table 6-3 provides a summary of the Reset flag bit operation.

| Flag Bit            | Set by:                                                             | Cleared by:                                      |

|---------------------|---------------------------------------------------------------------|--------------------------------------------------|

| TRAPR (RCON<15>)    | Trap conflict event                                                 | POR, BOR                                         |

| IOPWR (RCON<14>)    | Illegal opcode or Uninitialized W register access or Security Reset | POR, BOR                                         |

| <b>CM</b> (RCON<9>) | Configuration Mismatch                                              | POR, BOR                                         |

| EXTR (RCON<7>)      | MCLR Reset                                                          | POR                                              |

| SWR (RCON<6>)       | RESET instruction                                                   | POR, BOR                                         |

| WDTO (RCON<4>)      | WDT time-out                                                        | PWRSAV instruction, CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)     | PWRSAV #SLEEP instruction                                           | POR, BOR                                         |

| IDLE (RCON<2>)      | PWRSAV #IDLE instruction                                            | POR, BOR                                         |

| BOR (RCON<1>)       | POR, BOR                                                            | —                                                |

| POR (RCON<0>)       | POR                                                                 | _                                                |

#### TABLE 6-3: RESET FLAG BIT OPERATION

Note: All Reset flag bits can be set or cleared by user software.

| U-0    | U-0 | U-0 | U-0 | R-0  | R-0  | R-0  | R-0   |

|--------|-----|-----|-----|------|------|------|-------|

| —      | —   | _   | _   | ILR3 | ILR2 | ILR1 | ILR0  |

| bit 15 |     |     |     |      |      |      | bit 8 |

#### REGISTER 7-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0   | R-0     |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:      |                            |                                |                        |                    |  |  |  |  |  |

|--------------|----------------------------|--------------------------------|------------------------|--------------------|--|--|--|--|--|

| R = Readab   | le bit                     | W = Writable bit               | U = Unimplemented bit, | , read as '0'      |  |  |  |  |  |

| -n = Value a | t POR                      | '1' = Bit is set               | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |  |

| bit 15-12    | Unimplen                   | nented: Read as '0'            |                        |                    |  |  |  |  |  |

|              | Unimplemented: Read as '0' |                                |                        |                    |  |  |  |  |  |

| bit 11-8     |                            |                                |                        |                    |  |  |  |  |  |

|              | 1111 <b>= C</b>            | PU Interrupt Priority Level is | s 15                   |                    |  |  |  |  |  |

|              | •                          |                                |                        |                    |  |  |  |  |  |

|              | •                          |                                |                        |                    |  |  |  |  |  |

|              | •                          |                                | - 4                    |                    |  |  |  |  |  |

|              |                            | PU Interrupt Priority Level is |                        |                    |  |  |  |  |  |

|              |                            | PU Interrupt Priority Level i  | 50                     |                    |  |  |  |  |  |

| bit 7        | Unimplen                   | nented: Read as '0'            |                        |                    |  |  |  |  |  |

| bit 6-0      | VECNUM                     | <6:0>: Vector Number of P      | ending Interrupt bits  |                    |  |  |  |  |  |

|              | 0111111                    | = Interrupt vector pending i   | is Number 135          |                    |  |  |  |  |  |

|              | •                          |                                |                        |                    |  |  |  |  |  |

|              | •                          |                                |                        |                    |  |  |  |  |  |

|              | •                          |                                |                        |                    |  |  |  |  |  |

|              | 0000001                    | = Interrupt vector pending i   | is Number 9            |                    |  |  |  |  |  |

|              | 0000000                    | = Interrupt vector pending i   | is Number 8            |                    |  |  |  |  |  |

|              |                            |                                |                        |                    |  |  |  |  |  |

| R/W-0         | U-0                                                                                | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0                  | R/W-0                 | R/W-0                 |  |  |  |

|---------------|------------------------------------------------------------------------------------|----------------------------------------|---------------|-----------------------|------------------------|-----------------------|-----------------------|--|--|--|

| ROON          | _                                                                                  | ROSSLP                                 | ROSEL         | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup>  | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |

| bit 15        |                                                                                    |                                        |               |                       |                        |                       | bit 8                 |  |  |  |

|               |                                                                                    |                                        |               |                       |                        |                       |                       |  |  |  |

| U-0           | U-0                                                                                | U-0                                    | U-0           | U-0                   | U-0                    | U-0                   | U-0                   |  |  |  |

|               | _                                                                                  | —                                      |               | —                     | —                      | —                     | —                     |  |  |  |

| bit 7         |                                                                                    |                                        |               |                       |                        |                       | bit 0                 |  |  |  |

| Legend:       |                                                                                    |                                        |               |                       |                        |                       |                       |  |  |  |

| R = Readabl   | e bit                                                                              | W = Writable                           | bit           | U = Unimplen          | nented bit, read       | l as '0'              |                       |  |  |  |

| -n = Value at | POR                                                                                | '1' = Bit is set                       |               | '0' = Bit is cle      |                        | x = Bit is unkr       | iown                  |  |  |  |

|               |                                                                                    |                                        |               |                       |                        |                       |                       |  |  |  |

| bit 15        | ROON: Refer                                                                        | ence Oscillator                        | r Output Enab | ole bit               |                        |                       |                       |  |  |  |

|               |                                                                                    |                                        |               | on the REFCL          | .K0 pin <sup>(2)</sup> |                       |                       |  |  |  |

|               |                                                                                    | e oscillator outp                      |               | ł                     |                        |                       |                       |  |  |  |

| bit 14        | Unimplemen                                                                         | ted: Read as '                         | 0'            |                       |                        |                       |                       |  |  |  |

| bit 13        | ROSSLP: Reference Oscillator Run in Sleep bit                                      |                                        |               |                       |                        |                       |                       |  |  |  |

|               |                                                                                    | e oscillator outp<br>e oscillator outp |               |                       |                        |                       |                       |  |  |  |

| bit 12        | <b>ROSEL:</b> Reference Oscillator Source Select bit                               |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 1 = Oscillator                                                                     | crystal is used                        | as the refere | nce clock             |                        |                       |                       |  |  |  |

|               | •                                                                                  | lock is used as                        |               |                       |                        |                       |                       |  |  |  |

| bit 11-8      | RODIV<3:0>: Reference Oscillator Divider bits <sup>(1)</sup>                       |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 1111 = Reference clock divided by 32,768                                           |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 1110 = Reference clock divided by 16,384                                           |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 1101 = Reference clock divided by 8,192                                            |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 1100 = Reference clock divided by 4,096<br>1011 = Reference clock divided by 2,048 |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 1010 = Reference clock divided by 2,040                                            |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 1001 = Reference clock divided by 512                                              |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 1000 = Reference clock divided by 256                                              |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 0111 = Reference clock divided by 128                                              |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 0110 = Reference clock divided by 64                                               |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 0101 = Reference clock divided by 32<br>0100 = Reference clock divided by 16       |                                        |               |                       |                        |                       |                       |  |  |  |

|               |                                                                                    |                                        |               |                       |                        |                       |                       |  |  |  |

|               |                                                                                    | ence clock divi                        | -             |                       |                        |                       |                       |  |  |  |

|               |                                                                                    | ence clock divi<br>ence clock divi     | -             |                       |                        |                       |                       |  |  |  |

|               | 000T = Velet                                                                       |                                        |               |                       |                        |                       |                       |  |  |  |

|               | 0000 = Refer                                                                       |                                        |               |                       |                        |                       |                       |  |  |  |

### REGISTER 8-6: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

Note 1: The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

2: This pin is remappable. Refer to Section 10.6 "Peripheral Pin Select" for more information.

| REGISTER 9-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |     |                  |     |                                         |       |      |       |  |  |

|------------------------------------------------------------------|-----|------------------|-----|-----------------------------------------|-------|------|-------|--|--|

| U-0                                                              | U-0 | U-0              | U-0 | U-0                                     | R/W-0 | U-0  | U-0   |  |  |

| _                                                                | —   | —                | —   | —                                       | CMPMD | —    | —     |  |  |

| bit 15                                                           |     |                  |     |                                         |       |      | bit 8 |  |  |

|                                                                  |     |                  |     |                                         |       |      |       |  |  |

| U-0                                                              | U-0 | U-0              | U-0 | U-0                                     | U-0   | U-0  | U-0   |  |  |

| —                                                                | —   | —                | —   | —                                       | —     | —    | —     |  |  |

| bit 7                                                            |     |                  |     |                                         |       |      | bit 0 |  |  |

|                                                                  |     |                  |     |                                         |       |      |       |  |  |

| Legend:                                                          |     |                  |     |                                         |       |      |       |  |  |

| R = Readable b                                                   | bit | W = Writable     | bit | U = Unimplemented bit, read as '0'      |       |      |       |  |  |

| -n = Value at P                                                  | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |       | nown |       |  |  |

|                                                                  |     |                  |     |                                         |       |      |       |  |  |

| bit 15-11 | Unimplemented: Read as '0'                               |

|-----------|----------------------------------------------------------|

| bit 10    | CMPMD: Analog Comparator Module Disable bit              |

|           | <ol> <li>Analog comparator module is disabled</li> </ol> |

|           | 0 = Analog comparator module is enabled                  |

| bit 9-0   | Unimplemented: Read as '0'                               |

### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 3 **REFOMD**: Reference Clock Generator Module Disable bit

1 = Reference clock generator module is disabled

- 0 = Reference clock generator module is enabled

- bit 2-0 Unimplemented: Read as '0'

| U-0                | U-0                                                                                                                                                          | R/W-1                                                                                                                                                                                                          | R/W-1                                              | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|------------------|-----------------|--------|

| _                  |                                                                                                                                                              | T3CKR5                                                                                                                                                                                                         | T3CKR4                                             | T3CKR3            | T3CKR2           | T3CKR1          | T3CKR0 |

| bit 15             |                                                                                                                                                              |                                                                                                                                                                                                                |                                                    |                   |                  |                 | bit    |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                |                                                    |                   |                  |                 |        |

| U-0                | U-0                                                                                                                                                          | R/W-1                                                                                                                                                                                                          | R/W-1                                              | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|                    |                                                                                                                                                              | T2CKR5                                                                                                                                                                                                         | T2CKR4                                             | T2CKR3            | T2CKR2           | T2CKR1          | T2CKR0 |

| bit 7              |                                                                                                                                                              |                                                                                                                                                                                                                |                                                    |                   |                  |                 | bit    |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                |                                                    |                   |                  |                 |        |

| Legend:            | la h:t                                                                                                                                                       |                                                                                                                                                                                                                | L:4                                                |                   | antad hit waar   | L == (0)        |        |

| R = Readab         |                                                                                                                                                              | W = Writable                                                                                                                                                                                                   |                                                    | •                 | nented bit, read |                 |        |

| -n = Value a       | t POR                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                                               |                                                    | '0' = Bit is clea | ared             | x = Bit is unkr | IOWN   |

| bit 15-14          | Unimploment                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                 | o'                                                 |                   |                  |                 |        |

|                    | -                                                                                                                                                            |                                                                                                                                                                                                                |                                                    |                   |                  |                 |        |

| bit 13-8           |                                                                                                                                                              | -                                                                                                                                                                                                              | 3 External Clo                                     | ck (T3CK) to th   | ne Correspondi   | ng RPn Pin bits | 6      |

|                    |                                                                                                                                                              |                                                                                                                                                                                                                |                                                    |                   |                  |                 |        |

|                    | 111111 = Inp                                                                                                                                                 |                                                                                                                                                                                                                | _                                                  |                   |                  |                 |        |

|                    | 100011 <b>= Inp</b>                                                                                                                                          | ut tied to RP35                                                                                                                                                                                                |                                                    |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp                                                                                                                                 | out tied to RP35<br>out tied to RP34                                                                                                                                                                           | 1                                                  |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                       | 1<br>3                                             |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34                                                                                                                                                                           | 1<br>3                                             |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                       | 1<br>3                                             |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | out tied to RP35<br>out tied to RP34<br>out tied to RP33                                                                                                                                                       | 1<br>3                                             |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                 | ut tied to RP34<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                                       | 1<br>3                                             |                   |                  |                 |        |

| hit 7-6            | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                 | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP32                                                                                                                     | 4<br>3<br>2                                        |                   |                  |                 |        |

| bit 7-6            | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>00000 = Inpu<br>Unimplemen                                                               | ut tied to RP35<br>out tied to RP34<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '                                                                                          | 4<br>3<br>2<br>0'                                  | ole (T2CK) to th  | oo Corroopondi   | ng PDn Din hit  |        |

| bit 7-6<br>bit 5-0 | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | ut tied to RP35<br>out tied to RP33<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer?                                                                       | 4<br>3<br>2<br>0'                                  | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP32<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer:<br>out tied to Vss                                                     | 1<br>3<br>2<br>0'<br>2 External Clo                | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 5      |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP32<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>: Assign Timer<br>out tied to Vss<br>out tied to RP35                                  | 1<br>3<br>2<br>0'<br>2 External Clo                | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | t tied to RP35<br>out tied to RP34<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>out tied to RP35<br>out tied to RP34                                         | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1      | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>tut tied to RP34<br>tut tied to RP33<br>tut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>tut tied to Vss<br>tut tied to RP35<br>tut tied to RP34<br>tut tied to RP33 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>out tied to RP34<br>out tied to RP33<br>out tied to RP32<br>t tied to RP0<br>ted: Read as f<br>t tied to Vss<br>out tied to RP35<br>out tied to RP34                                         | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ie Correspondi   | ng RPn Pin bits | 5      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>tut tied to RP34<br>tut tied to RP33<br>tut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>tut tied to Vss<br>tut tied to RP35<br>tut tied to RP34<br>tut tied to RP33 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>tut tied to RP34<br>tut tied to RP33<br>tut tied to RP32<br>t tied to RP32<br>t tied to RP0<br>ted: Read as f<br>tut tied to Vss<br>tut tied to RP35<br>tut tied to RP34<br>tut tied to RP33 | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | t tied to RP35<br>ut tied to RP32<br>ut tied to RP33<br>ut tied to RP33<br>t tied to RP34<br>t tied to RP34<br>t tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP33<br>ut tied to RP33      | 1<br>3<br>2<br>0'<br>2 External Clo<br>5<br>1<br>3 | ck (T2CK) to th   | ne Correspondi   | ng RPn Pin bits | 3      |

## REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0                | U-0                                                                                                                                         | R/W-1                                                                                                                                                                                       | R/W-1                                               | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------|------------------|-----------------|--------|

| —                  |                                                                                                                                             | FLT3R5                                                                                                                                                                                      | FLT3R4                                              | FLT3R3            | FLT3R2           | FLT3R1          | FLT3R0 |

| bit 15             |                                                                                                                                             |                                                                                                                                                                                             |                                                     |                   |                  |                 | bit 8  |

| U-0                | U-0                                                                                                                                         | R/W-1                                                                                                                                                                                       | R/W-1                                               | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|                    | 0-0                                                                                                                                         | FLT2R5                                                                                                                                                                                      | FLT2R4                                              | FLT2R3            | FLT2R2           | FLT2R1          | FLT2R0 |

| bit 7              |                                                                                                                                             | T LIZI(                                                                                                                                                                                     | 1 21214                                             | T ETZI(0          | TLIZI            | I LIZI(I        | bit (  |

|                    |                                                                                                                                             |                                                                                                                                                                                             |                                                     |                   |                  |                 |        |

| Legend:            |                                                                                                                                             | \A/ \A/ \                                                                                                                                                                                   | 1.14                                                |                   |                  |                 |        |

| R = Readab         |                                                                                                                                             | W = Writable                                                                                                                                                                                |                                                     |                   | nented bit, read |                 |        |

| -n = Value a       | t POR                                                                                                                                       | '1' = Bit is set                                                                                                                                                                            |                                                     | '0' = Bit is clea | ared             | x = Bit is unkr | IOWN   |

| bit 15-14          | Unimplomon                                                                                                                                  | ted: Read as '                                                                                                                                                                              | 0'                                                  |                   |                  |                 |        |

|                    | -                                                                                                                                           |                                                                                                                                                                                             |                                                     |                   |                  |                 |        |

| bit 13-8           |                                                                                                                                             | •                                                                                                                                                                                           | Fault Input 3 (                                     | FLI3) to the Co   | orresponding R   | Pn Pin bits     |        |

|                    | 111111 = Inp                                                                                                                                | ut tied to Vss                                                                                                                                                                              |                                                     |                   |                  |                 |        |

|                    |                                                                                                                                             |                                                                                                                                                                                             | _                                                   |                   |                  |                 |        |

|                    |                                                                                                                                             | ut tied to RP3                                                                                                                                                                              |                                                     |                   |                  |                 |        |

|                    | 100010 <b>= Inp</b>                                                                                                                         | ut tied to RP34                                                                                                                                                                             | 1                                                   |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp                                                                                                                | ut tied to RP34<br>ut tied to RP33                                                                                                                                                          | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp                                                                                                                | ut tied to RP34                                                                                                                                                                             | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp                                                                                                                | ut tied to RP34<br>ut tied to RP33                                                                                                                                                          | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp                                                                                                                | ut tied to RP34<br>ut tied to RP33                                                                                                                                                          | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                                       | 4<br>3                                              |                   |                  |                 |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>00000 = Inpu                                                                 | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0                                                                                                                      | 4<br>3<br>2                                         |                   |                  |                 |        |

| bit 7-6            | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>00000 = Inpu<br>Unimplement                                             | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '                                                                                             | 4<br>3<br>2<br>0'                                   |                   |                  |                 |        |

| bit 7-6<br>bit 5-0 | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM                                                                               | 4<br>3<br>2<br>0'                                   | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss                                                           | 4<br>3<br>2<br>0'<br>Fault Input 2 (                | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP35                                        | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5           | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34                     | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4      | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34<br>ut tied to RP34  | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | orresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34                     | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34<br>ut tied to RP34  | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP34<br>ut tied to RP34<br>ut tied to RP34  | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to RP34<br>ut tied to RP32<br>ut tied to RP32<br>ut tied to RP32 | 4<br>3<br>2<br>0'<br>Fault Input 2 (<br>5<br>4<br>3 | FLT2) to the Co   | prresponding R   | Pn Pin bits     |        |

### REGISTER 10-10: RPINR30: PERIPHERAL PIN SELECT INPUT REGISTER 30

|                    | U-0                                                                                                                  | R/W-1                                                                                                                                                             | R/W-1                                      | R/W-1                       | R/W-1            | R/W-1            | R/W-1    |

|--------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------|------------------|------------------|----------|

|                    | _                                                                                                                    | SYNCI1R5                                                                                                                                                          | SYNCI1R4                                   | SYNCI1R3                    | SYNCI1R2         | SYNCI1R1         | SYNCI1R0 |

| bit 15             |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  | bit      |

|                    |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  |          |

| U-0                | U-0                                                                                                                  | R/W-1                                                                                                                                                             | R/W-1                                      | R/W-1                       | R/W-1            | R/W-1            | R/W-1    |

|                    | —                                                                                                                    | FLT8R5                                                                                                                                                            | FLT8R4                                     | FLT8R3                      | FLT8R2           | FLT8R1           | FLT8R0   |

| bit 7              |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  | bit      |

|                    |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  |          |

| Legend:            |                                                                                                                      |                                                                                                                                                                   |                                            |                             | 6 11 K           |                  |          |

| R = Readab         |                                                                                                                      | W = Writable                                                                                                                                                      |                                            | -                           | nented bit, read |                  |          |

| -n = Value a       | t POR                                                                                                                | '1' = Bit is set                                                                                                                                                  |                                            | '0' = Bit is cle            | ared             | x = Bit is unkr  | nown     |

|                    |                                                                                                                      |                                                                                                                                                                   | - <b>1</b>                                 |                             |                  |                  |          |

| bit 15-14          | =                                                                                                                    | ted: Read as '                                                                                                                                                    |                                            |                             |                  |                  |          |

| bit 13-8           |                                                                                                                      | <b>)&gt;:</b> Assign PW<br>g RPn Pin bits                                                                                                                         | M Master Time                              | e Base Externa              | al Synchronizat  | ion Signal to th | е        |

|                    | 1111111 = Inp                                                                                                        | -                                                                                                                                                                 |                                            |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP35                                                                                                                                                   | 5                                          |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP34                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    | 100001 - Inn                                                                                                         |                                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP33                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP33<br>ut tied to RP32                                                                                                                                |                                            |                             |                  |                  |          |

|                    |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    |                                                                                                                      |                                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    | 100000 = Inp<br>•<br>•                                                                                               | ut tied to RP32                                                                                                                                                   |                                            |                             |                  |                  |          |

|                    |                                                                                                                      | ut tied to RP32                                                                                                                                                   |                                            |                             |                  |                  |          |

| bit 7-6            | 100000 = Inp<br>•<br>•<br>00000 = Inpu                                                                               | ut tied to RP32                                                                                                                                                   | 2                                          |                             |                  |                  |          |

| bit 7-6<br>bit 5-0 | 100000 = Inp<br>•<br>•<br>00000 = Inpu<br>Unimplemen                                                                 | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '(                                                                                                        | 2<br>0'                                    | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>00000 = Inpu<br>Unimplemen<br>FLT8R<5:0>:<br>111111 = Inp                                 | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as 'd<br>Assign PWM F<br>ut tied to Vss                                                                      | 2<br><sub>0</sub> '<br>Fault Input 8 (I    | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>00000 = Inpu<br>Unimplemen<br>FLT8R<5:0>:<br>111111 = Inp<br>100011 = Inp                 | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35                                                   | 2<br><sub>0</sub> '<br>Fault Input 8 (I    | <sup>-</sup> LT8) to the Co | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>00000 = Inpu<br>Unimplement<br>FLT8R<5:0>:<br>11111 = Inp<br>100011 = Inp<br>100010 = Inp | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34                                | 2<br>0'<br>Fault Input 8 (I<br>5           | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•         | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33             | 2<br>0'<br>Fault Input 8 (I<br>5<br>4<br>3 | FLT8) to the Co             | orresponding R   | Pn Pin bits      |          |

|                    | 100000 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•         | ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '0<br>Assign PWM F<br>ut tied to Vss<br>ut tied to RP35<br>ut tied to RP34                                | 2<br>0'<br>Fault Input 8 (I<br>5<br>4<br>3 | <sup>-</sup> LT8) to the Co | orresponding R   | Pn Pin bits      |          |