Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

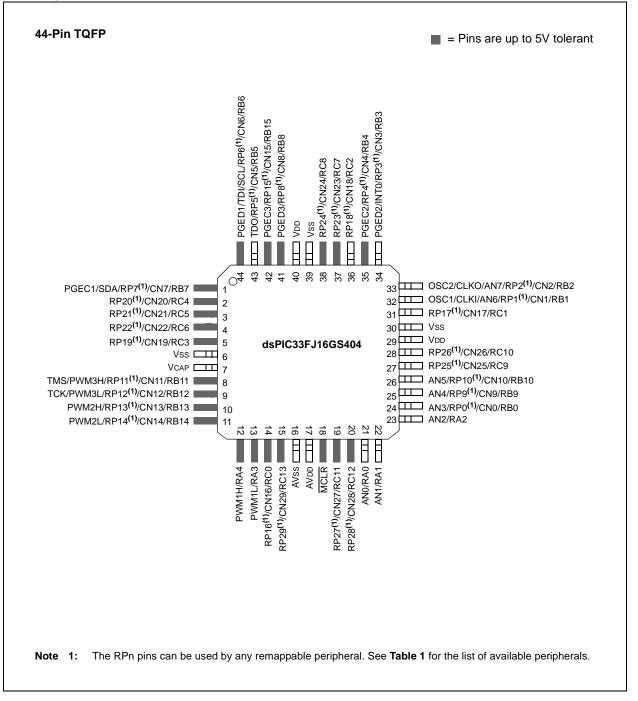

| Number of I/O              | 35                                                                                 |

| Program Memory Size        | 16KB (16K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10b; D/A 4x10b                                                              |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 44-TQFP                                                                            |

| Supplier Device Package    | 44-TQFP (10x10)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs504t-50i-pt |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Pin Diagrams (Continued)

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the primary reference for the operation of a particular module or device feature.

| Note: | To access the documents listed below,<br>browse to the documentation section<br>of the dsPIC33FJ16GS504 product<br>page of the Microchip web site<br>(www.microchip.com). |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | In addition to parameters, features, and<br>other documentation, the resulting page<br>provides links to the related family<br>reference manual sections.                 |

- "Introduction" (DS70197)

- "CPU" (DS70204)

- "Data Memory" (DS70202)

- "Program Memory" (DS70203)

- "Flash Programming" (DS70191)

- "Reset" (DS70192)

- "Watchdog Timer (WDT) and Power-Saving Modes" (DS70196)

- "I/O Ports" (DS70193)

- "Timers" (DS70205)

- "Input Capture" (DS70198)

- "Output Compare" (DS70005157)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70188)

- "Serial Peripheral Interface (SPI)" (DS70206)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195)

- "CodeGuard™ Security (DS70199)

- "Programming and Diagnostics" (DS70207)

- "Device Configuration" (DS70194)

- "Interrupts (Part IV)" (DS70300)

- "Oscillator (Part IV)" (DS70307)

- "High- Speed PWM Module" (DS70000323)

- "High-Speed 10-Bit ADC" (DS70000321)

- "High-Speed Analog Comparator" (DS70296)

- "Oscillator (Part VI)" (DS70644)

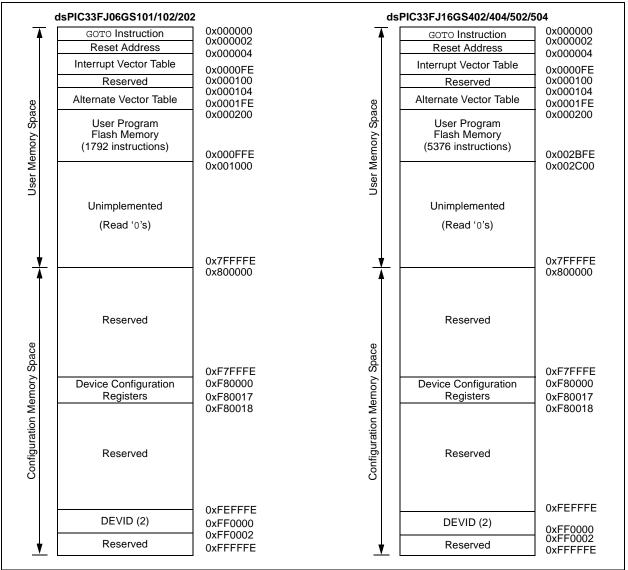

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70202) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access to program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping, as described in **Section 4.6 "Interfacing Program and Data Memory Spaces"**.

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory maps for the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices are shown in Figure 4-1.

### FIGURE 4-1: PROGRAM MEMORY MAPS FOR dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 DEVICES

| File Name | SFR<br>Addr | Bit 15   | Bit 14                       | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9         | Bit 8        | Bit 7 | Bit 6   | Bit 5    | Bit 4          | Bit 3      | Bit 2     | Bit 1      | Bit 0 | All<br>Resets |

|-----------|-------------|----------|------------------------------|----------|----------|----------|----------|---------------|--------------|-------|---------|----------|----------------|------------|-----------|------------|-------|---------------|

| WREG0     | 0000        |          |                              |          |          |          |          | Working Regi  | ster 0       |       |         |          |                |            |           |            |       | 0000          |

| WREG1     | 0002        |          |                              |          |          |          |          | Working Regi  | ster 1       |       |         |          |                |            |           |            |       | 0000          |

| WREG2     | 0004        |          |                              |          |          |          |          | Working Regi  | ster 2       |       |         |          |                |            |           |            |       | 0000          |

| WREG3     | 0006        |          |                              |          |          |          |          | Working Regi  | ster 3       |       |         |          |                |            |           |            |       | 0000          |

| WREG4     | 8000        |          |                              |          |          |          |          | Working Regi  | ster 4       |       |         |          |                |            |           |            |       | 0000          |

| WREG5     | 000A        |          |                              |          |          |          |          | Working Regi  | ster 5       |       |         |          |                |            |           |            |       | 0000          |

| WREG6     | 000C        |          |                              |          |          |          |          | Working Regi  | ster 6       |       |         |          |                |            |           |            |       | 0000          |

| WREG7     | 000E        |          |                              |          |          |          |          | Working Regi  | ster 7       |       |         |          |                |            |           |            |       | 0000          |

| WREG8     | 0010        |          |                              |          |          |          |          | Working Regi  | ster 8       |       |         |          |                |            |           |            |       | 0000          |

| WREG9     | 0012        |          |                              |          |          |          |          | Working Regi  | ster 9       |       |         |          |                |            |           |            |       | 0000          |

| WREG10    | 0014        |          |                              |          |          |          |          | Working Regis | ter 10       |       |         |          |                |            |           |            |       | 0000          |

| WREG11    | 0016        |          |                              |          |          |          |          | Working Regis | ster 11      |       |         |          |                |            |           |            |       | 0000          |

| WREG12    | 0018        |          |                              |          |          |          |          | Working Regis | ter 12       |       |         |          |                |            |           |            |       | 0000          |

| WREG13    | 001A        |          |                              |          |          |          |          | Working Regis | ter 13       |       |         |          |                |            |           |            |       | 0000          |

| WREG14    | 001C        |          |                              |          |          |          |          | Working Regis | ter 14       |       |         |          |                |            |           |            |       | 0000          |

| WREG15    | 001E        |          |                              |          |          |          |          | Working Regis | ter 15       |       |         |          |                |            |           |            |       | 0800          |

| SPLIM     | 0020        |          | Stack Pointer Limit Register |          |          |          |          | xxxx          |              |       |         |          |                |            |           |            |       |               |

| ACCAL     | 0022        |          | ACCAL                        |          |          |          |          | xxxx          |              |       |         |          |                |            |           |            |       |               |

| ACCAH     | 0024        |          |                              |          |          |          |          | ACCAH         |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCAU     | 0026        | ACCA<39> | ACCA<39>                     | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39>      | ACCA<39>     |       |         |          | ACCA           | AU         |           |            |       | xxxx          |

| ACCBL     | 0028        |          | ACCBL x                      |          |          |          |          | xxxx          |              |       |         |          |                |            |           |            |       |               |

| ACCBH     | 002A        |          |                              |          |          | -        |          | ACCBH         |              |       |         |          |                |            |           |            |       | xxxx          |

| ACCBU     | 002C        | ACCB<39> | ACCB<39>                     | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39>      | ACCB<39>     |       |         |          | ACCE           | BU         |           |            |       | XXXX          |

| PCL       | 002E        |          |                              |          |          |          | Program  | Counter Low   | Word Regist  | er    |         |          |                |            |           |            |       | 0000          |

| PCH       | 0030        | _        | _                            |          | —        | _        | —        | _             | _            |       |         | Program  | Counter H      | igh Byte I | Register  |            |       | 0000          |

| TBLPAG    | 0032        | _        |                              | _        | _        | _        | _        | _             | _            |       |         | Table Pa | ge Address     | 8 Pointer  | Register  |            |       | 0000          |

| PSVPAG    | 0034        | _        | —                            | -        | -        | _        | —        | -             | —            |       | Program | Memory \ | /isibility Pag | ge Addres  | ss Pointe | r Register | r     | 0000          |

| RCOUNT    | 0036        |          |                              |          |          |          | REPE     | AT Loop Coun  | ter Register |       |         |          |                |            |           |            |       | xxxx          |

| DCOUNT    | 0038        |          |                              |          |          |          |          | DCOUNT<1      | 5:0>         |       |         |          |                |            |           |            | -     | xxxx          |

| DOSTARTL  | 003A        |          |                              |          |          |          | DOS      | STARTL<15:1:  | >            |       |         |          |                |            |           |            | 0     | xxxx          |

| DOSTARTH  | 003C        | _        | _                            | _        | _        | _        | _        | _             | _            | _     | _       |          | D              | OSTART     | [H<5:0>   |            |       | 00xx          |

| DOENDL    | 003E        |          |                              |          |          |          | DC       | ENDL<15:1>    |              |       |         |          |                |            |           |            | 0     | xxxx          |

| DOENDH    | 0040        | _        | -                            |          | _        | —        | _        | —             | _            | —     | _       |          |                | DOEN       | IDH       |            | -     | 00xx          |

| SR        | 0042        | OA       | OB                           | SA       | SB       | OAB      | SAB      | DA            | DC           | IPL2  | IPL1    | IPL0     | RA             | N          | OV        | Z          | С     | 0000          |

| CORCON    | 0044        | _        | _                            | _        | US       | EDT      | DL2      | DL1           | DL0          | SATA  | SATB    | SATDW    | ACCSAT         | IPL3       | PSV       | RND        | IF    | 0020          |

| MODCON    | 0046        | XMODEN   | YMODEN                       | _        | _        | BWM3     | BWM2     | BWM1          | BWM0         | YWM3  | YWM2    | YWM1     | YWM0           | XWM3       | XWM2      | XWM1       | XWM0  | 0000          |

#### TABLE 4-1: CPU CORE REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

The address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

#### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

### 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM bits (W register selection) in the MODCON register are any value other than 15 (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed         |

|-------|--------------------------------------------|

|       | Addressing should not be enabled           |

|       | together. If an application attempts to do |

|       | so, Bit-Reversed Addressing will assume    |

|       | priority when active for the X WAGU and X  |

|       | WAGU; Modulo Addressing will be dis-       |

|       | abled. However, Modulo Addressing will     |

|       | continue to function in the X RAGU.        |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### 4.6 Interfacing Program and Data Memory Spaces

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 architecture uses a 24-bit-wide program space and a 16-bit-wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJ06GS101/ X02 and dsPIC33FJ16GSX02/X04 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. The application can only access the least significant word of the program word.

#### 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-50 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

|                          | Access        | Program Space Address        |           |                                   |                    |        |  |  |  |

|--------------------------|---------------|------------------------------|-----------|-----------------------------------|--------------------|--------|--|--|--|

| Access Type              | Space         | <23>                         | <22:16>   | <15>                              | <14:1>             | <0>    |  |  |  |

| Instruction Access       | User          | 0 PC<22:1>                   |           |                                   |                    | 0      |  |  |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |                                   |                    |        |  |  |  |

| TBLRD/TBLWT              | User          | TB                           | LPAG<7:0> | Data EA<15:0>                     |                    |        |  |  |  |

| (Byte/Word Read/Write)   |               | 0xxx xxxx xxxx xxxx xxxx     |           |                                   |                    |        |  |  |  |

|                          | Configuration | TBLPAG<7:0>                  |           | Data EA<15:0>                     |                    |        |  |  |  |

|                          |               | 1                            | xxx xxxx  | xxxx x                            | xxx xxxx xxxx      |        |  |  |  |

| Program Space Visibility | User          | 0 PSVPAG<7:                  |           | 7:0> Data EA<14:0> <sup>(1)</sup> |                    | :0>(1) |  |  |  |

| (Block Remap/Read)       |               | 0                            | XXXX XXX  | x                                 | xxx xxxx xxxx xxxx |        |  |  |  |

#### TABLE 4-50: PROGRAM SPACE ADDRESS CONSTRUCTION

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

| REGISTER 5-2     |                                                                           |                |      |              | LOISTEN         |           |       |

|------------------|---------------------------------------------------------------------------|----------------|------|--------------|-----------------|-----------|-------|

| U-0              | U-0                                                                       | U-0            | U-0  | U-0          | U-0             | U-0       | U-0   |

| —                |                                                                           | —              | _    | —            | _               | —         | —     |

| bit 15           |                                                                           |                |      |              |                 |           | bit 8 |

|                  |                                                                           |                |      |              |                 |           |       |

| W-0              | W-0                                                                       | W-0            | W-0  | W-0          | W-0             | W-0       | W-0   |

|                  |                                                                           |                | NVMK | EY<7:0>      |                 |           |       |

| bit 7            |                                                                           |                |      |              |                 |           | bit 0 |

|                  |                                                                           |                |      |              |                 |           |       |

| Legend:          |                                                                           |                |      |              |                 |           |       |

| R = Readable b   | it                                                                        | W = Writable b | oit  | U = Unimplem | nented bit, rea | ad as '0' |       |

| -n = Value at PC | n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown |                |      |              |                 |           | nown  |

### REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Nonvolatile Memory Key bits (write-only)

#### 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70192) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: Software RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), which is set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

#### FIGURE 6-1: **RESET SYSTEM BLOCK DIAGRAM RESET** Instruction Glitch Filter MCLR WDT Module Sleep or Idle BOR Internal SYSRST Regulator Vdd POR VDD Rise Detect Trap Conflict Illegal Opcode Uninitialized W Register Configuration Mismatch

### dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| U-0           | U-0             | R/W-0                                                                                       | U-0             | U-0               | U-0              | U-0             | U-0              |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|------------------|--|--|

| _             | _               | INT2IE                                                                                      | _               | _                 | _                | _               | _                |  |  |

| bit 15        |                 | 1                                                                                           |                 |                   |                  |                 | bit 8            |  |  |

|               |                 |                                                                                             |                 |                   |                  |                 |                  |  |  |

| U-0           | U-0             | U-0                                                                                         | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0            |  |  |

| —             | _               |                                                                                             | INT1IE          | CNIE              | AC1IE            | MI2C1IE         | SI2C1IE          |  |  |

| bit 7         | •               |                                                                                             |                 | 1 1               |                  |                 | bit C            |  |  |

|               |                 |                                                                                             |                 |                   |                  |                 |                  |  |  |

| Legend:       |                 |                                                                                             |                 |                   |                  |                 |                  |  |  |

| R = Readabl   | e bit           | W = Writable I                                                                              | oit             | U = Unimplem      | nented bit, read | d as '0'        |                  |  |  |

| -n = Value at | POR             | '1' = Bit is set                                                                            |                 | '0' = Bit is clea | ared             | x = Bit is unkr | = Bit is unknown |  |  |

|               |                 |                                                                                             |                 |                   |                  |                 |                  |  |  |

| bit 15-14     | Unimplemen      | ted: Read as 'd                                                                             | )'              |                   |                  |                 |                  |  |  |

| bit 13        | INT2IE: Exter   | nal Interrupt 2                                                                             | Enable bit      |                   |                  |                 |                  |  |  |

|               |                 | equest enabled                                                                              |                 |                   |                  |                 |                  |  |  |

|               | -               | equest not ena                                                                              |                 |                   |                  |                 |                  |  |  |

| bit 12-5      | •               | ted: Read as '0                                                                             |                 |                   |                  |                 |                  |  |  |

| bit 4         |                 | nal Interrupt 1                                                                             |                 |                   |                  |                 |                  |  |  |

|               |                 | equest enableo                                                                              |                 |                   |                  |                 |                  |  |  |

| bit 3         | •               | change Notifica                                                                             |                 | Enable bit        |                  |                 |                  |  |  |

| DIT 3         | -               | request enabled                                                                             | •               |                   |                  |                 |                  |  |  |

|               |                 | equest not ena                                                                              |                 |                   |                  |                 |                  |  |  |

| bit 2         | AC1IE: Analo    | g Comparator                                                                                | 1 Interrupt En  | able bit          |                  |                 |                  |  |  |

|               | 1 = Interrupt r | equest enabled                                                                              | k               |                   |                  |                 |                  |  |  |

|               | 0 = Interrupt r | equest not ena                                                                              | bled            |                   |                  |                 |                  |  |  |

| bit 1         | MI2C1IE: I2C    | 1 Master Event                                                                              | ts Interrupt Er | nable bit         |                  |                 |                  |  |  |

|               |                 | equest enabled                                                                              |                 |                   |                  |                 |                  |  |  |

|               | -               | -                                                                                           |                 |                   |                  |                 |                  |  |  |

|               |                 | 0 = Interrupt request not enabled<br><b>SI2C1IE:</b> I2C1 Slave Events Interrupt Enable bit |                 |                   |                  |                 |                  |  |  |

| bit 0         |                 | 1 Slave Events<br>equest enabled                                                            |                 |                   |                  |                 |                  |  |  |

### dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

| U-0                          | U-0                                        | U-0                                                                      | U-0                   | U-0                      | U-0             | U-0                | U-0    |  |

|------------------------------|--------------------------------------------|--------------------------------------------------------------------------|-----------------------|--------------------------|-----------------|--------------------|--------|--|

| _                            | —                                          |                                                                          | _                     | —                        | _               | _                  |        |  |

| oit 15                       |                                            |                                                                          |                       |                          |                 |                    | bit    |  |

|                              |                                            |                                                                          |                       |                          |                 |                    |        |  |

| U-0                          | R/W-1                                      | R/W-0                                                                    | R/W-0                 | U-0                      | R/W-1           | R/W-0              | R/W-0  |  |

| —                            | AC4IP2                                     | AC4IP1                                                                   | AC4IP0                |                          | AC3IP2          | AC3IP1             | AC3IP0 |  |

| bit 7                        |                                            |                                                                          |                       |                          |                 |                    | bit    |  |

|                              |                                            |                                                                          |                       |                          |                 |                    |        |  |

| <b>Legend:</b><br>R = Readat | le bit                                     | W = Writable                                                             | hit                   | II – Unimplen            | nented bit, rea | d as '0'           |        |  |

| -n = Value a                 |                                            | '1' = Bit is set                                                         |                       | '0' = Bit is clea        |                 | x = Bit is unknown |        |  |

|                              |                                            |                                                                          |                       |                          | aleu            |                    | 100011 |  |

| bit 15-7                     | Unimplomon                                 | ted: Read as '                                                           | 0'                    |                          |                 |                    |        |  |

|                              | -                                          |                                                                          |                       |                          |                 |                    |        |  |

| bit 6-4                      |                                            | •                                                                        |                       | upt Priority bits        |                 |                    |        |  |

|                              | ⊥⊥⊥ = Interru                              | pt is Priority 7 (                                                       | nignest priorii       | ty)                      |                 |                    |        |  |

|                              | •                                          |                                                                          |                       |                          |                 |                    |        |  |

|                              | •                                          |                                                                          |                       |                          |                 |                    |        |  |

|                              |                                            |                                                                          |                       |                          |                 |                    |        |  |

|                              | •                                          |                                                                          |                       |                          |                 |                    |        |  |

|                              | •<br>001 = Interru<br>000 = Interru        | pt is Priority 1<br>pt source is dis                                     | abled                 |                          |                 |                    |        |  |

| bit 3                        | 000 = Interru                              |                                                                          |                       |                          |                 |                    |        |  |

| bit 3<br>bit 2-0             | 000 = Interru<br>Unimplemen                | pt source is dis<br>ted: Read as '                                       | 0'                    | upt Priority bits        |                 |                    |        |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr | upt Priority bits<br>ty) |                 |                    |        |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '                                       | 0'<br>arator 3 Interr |                          |                 |                    |        |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr |                          |                 |                    |        |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '<br>Analog Comp                        | 0'<br>arator 3 Interr |                          |                 |                    |        |  |

|                              | 000 = Interru<br>Unimplemen<br>AC3IP<2:0>: | pt source is dis<br>ted: Read as '<br>Analog Compa<br>pt is Priority 7 ( | 0'<br>arator 3 Interr |                          |                 |                    |        |  |

#### REGISTER 7-31: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

#### 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices can manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### 9.1 Clock Frequency and Clock Switching

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

#### 9.2 Instruction-Based Power-Saving Modes

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

#### 9.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes the items such as the Input Change Notification on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into SLEEP mode

PWRSAV #IDLE\_MODE ; Put the device into IDLE mode

The Timer2/3 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous Counter mode, the input clock is derived from the external clock input at the TxCK pin.

The timer modes are determined by the following bits:

- TCS (TxCON<1>): Timer Clock Source Control bit

- TGATE (TxCON<6>): Timer Gate Control bit

Timer control bit settings for different operating modes are given in the Table 12-1.

| Mode                | TCS | TGATE |

|---------------------|-----|-------|

| Timer               | 0   | 0     |

| Gated Timer         | 0   | 1     |

| Synchronous Counter | 1   | x     |

#### TABLE 12-1: TIMER MODE SETTINGS

#### 12.1 16-Bit Operation

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

#### 12.2 32-Bit Operation

A 32-bit timer module can be formed by combining a Type B and a Type C 16-bit timer module. For 32-bit timer operation, the T32 control bit in the Type B Timer Control (TxCON<3>) register must be set. The Type C timer holds the most significant word (msw) and the Type B timer holds the least significant word (lsw) for 32-bit operation.

When configured for 32-bit operation, only the Type B Timer Control (TxCON) register bits are required for setup and control while the Type C Timer Control register bits are ignored (except the TSIDL bit).

For interrupt control, the combined 32-bit timer uses the interrupt enable, interrupt flag and interrupt priority control bits of the Type C timer. The interrupt control and status bits for the Type B timer are ignored during 32-bit timer operation.

The Timer2 and Timer 3 that can be combined to form a 32-bit timer are listed in Table 12-2.

#### TABLE 12-2: 32-BIT TIMER

| Type B Timer (Isw) | Type C Timer (msw) |

|--------------------|--------------------|

| Timer2             | Timer3             |

A block diagram representation of the 32-bit timer module is shown in Figure 12-3. The 32-timer module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

To configure the features of Timer2/3 for 32-bit operation:

- 1. Set the T32 control bit.

- Select the prescaler ratio for Timer2 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3 contains the most significant word of the value, while PR2 contains the least significant word.

- 5. If interrupts are required, set the interrupt enable bit, T3IE. Use the priority bits, T3IP<2:0>, to set the interrupt priority. While Timer2 controls the timer, the interrupt appears as a Timer3 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2, which always contains the most significant word of the count, while TMR2 contains the least significant word.

### dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04

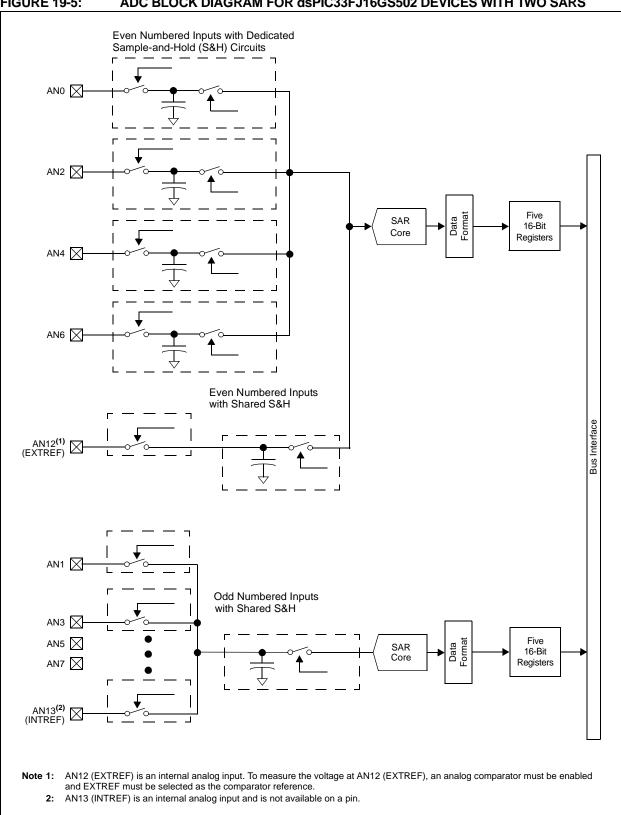

#### REGISTER 19-8: ADCPC3: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup>

| bit 4-0 | TRGSRC6<4:0>: Trigger 6 Source Selection bits<br>Selects trigger source for conversion of Analog Channels AN13 and AN12.<br>11111 = Timer2 period match |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00111 = PWM Generator 4 primary trigger is selected<br>00110 = PWM Generator 3 primary trigger is selected                                              |

- Note 1: This register is only implemented on the dsPIC33FJ16GS502 and dsPIC33FJ16GS504 devices.

- 2: The trigger source must be set as global software trigger prior to setting this bit to '1'. If other conversions are in progress, conversion will be performed when the conversion resources are available.

| AC CHARACTERISTICS   |                                          |                                             | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)           | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 24-31                              | —                                           | —                                                    | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | —                                        | Table 24-32                                 | —                                                    | 1   | 0,1 | 1   |  |  |

| 9 MHz                | —                                        | Table 24-33                                 | —                                                    | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                                        | —                                           | Table 24-34                                          | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 24-35                                          | 1   | 1   | 0   |  |  |

| 15 MHz               | —                                        | —                                           | Table 24-36                                          | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 24-37                                          | 0   | 0   | 0   |  |  |

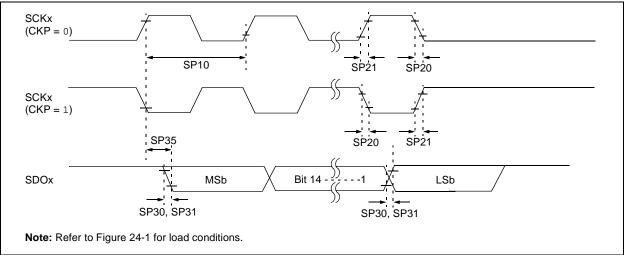

#### FIGURE 24-11: SPIx MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING **CHARACTERISTICS**

#### SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING FIGURE 24-12: **CHARACTERISTICS**

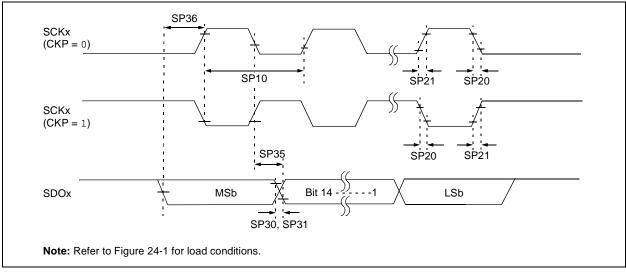

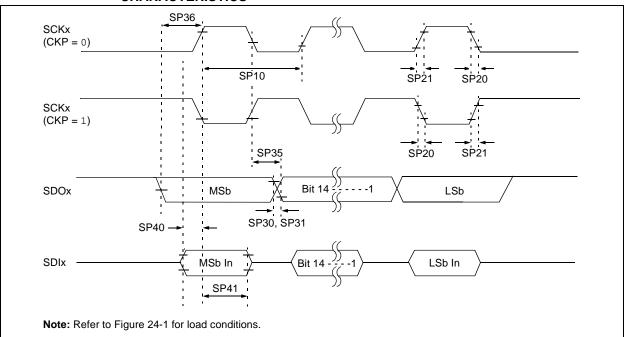

# FIGURE 24-13: SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 24-32:SPIX MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHA       | RACTERIST             | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |                    |     |       |                                      |

|--------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                        | Min | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP10         | TscP                  | Maximum SCKx Frequency                                                                                                                                                                               | —   | _                  | 9   | MHz   | See Note 3                           |

| SP20         | TscF                  | SCKx Output Fall Time                                                                                                                                                                                | —   | -                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP21         | TscR                  | SCKx Output Rise Time                                                                                                                                                                                | —   | —                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                                                                                                                                                           | —   | —                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                                                                                                                                                           | —   | -                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                                            | —   | 6                  | 20  | ns    |                                      |

| SP36         | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                                                                         | 30  | _                  | _   | ns    |                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge                                                                                                                                                        | 30  | _                  | _   | ns    |                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                                            | 30  | _                  |     | ns    |                                      |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

# TABLE 24-35:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |

|--------------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                               | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70               | TscP                  | Maximum SCKx Input<br>Frequency                              |                                                                                                                                                                                                                                                                                   |                    | 11  | MHz   | See Note 3                           |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                                                                                                                 | _                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                                                                                                                                                                                                                                                 | _                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                                                                                                                                                                                                                                                                 | —                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | _                                                                                                                                                                                                                                                                                 |                    |     | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | _                                                                                                                                                                                                                                                                                 | 6                  | 20  | ns    |                                      |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                                                                                                                                                                                                                                                | —                  | _   | ns    |                                      |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                                                                                                                                                                                                                                                | _                  | _   | ns    |                                      |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                                                                                                                                                                                                                                                | _                  | _   | ns    |                                      |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                                                                               | —                  | _   | ns    |                                      |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>        | 10                                                                                                                                                                                                                                                                                | —                  | 50  | ns    |                                      |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                                                                                                                                                                                                                                                      | —                  | —   | ns    | See Note 4                           |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                     | —                                                                                                                                                                                                                                                                                 | _                  | 50  | ns    |                                      |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| AC CHARACTERISTICS |           |                                                              |          | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                                                                             |  |  |

|--------------------|-----------|--------------------------------------------------------------|----------|-------------------------------------------------------|------|-------|-----------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol    | Characteristic                                               | Min.     | Тур.                                                  | Max. | Units | Conditions                                                                  |  |  |

|                    |           | I                                                            | Device S | Supply                                                |      |       | •                                                                           |  |  |

| AD01               | AVdd      | Module VDD Supply                                            | _        | _                                                     | _    | _     | AVDD is internally connected to<br>VDD; see Parameter DC10 in<br>Table 24-4 |  |  |

| AD02               | AVss      | Module Vss Supply                                            | —        | _                                                     |      | -     | AVss is internally connected to Vss                                         |  |  |

|                    |           |                                                              | Analog   | Input                                                 |      |       |                                                                             |  |  |

| AD10               | VINH-VINL | Full-Scale Input Span                                        | Vss      | —                                                     | Vdd  | V     |                                                                             |  |  |

| AD11               | Vin       | Absolute Input Voltage                                       | AVss     | —                                                     | AVdd | V     |                                                                             |  |  |

| AD12               | IAD       | Operating Current                                            | _        | 8                                                     |      | mA    |                                                                             |  |  |

| AD13               | —         | Leakage Current                                              | —        | ±0.6                                                  |      | μA    | VINL = AVSS = 0V, AVDD = 3.3V<br>Source Impedance = $100\Omega$             |  |  |

| AD17               | Rin       | Recommended Impedance<br>Of Analog Voltage Source            | _        |                                                       | 100  | Ω     |                                                                             |  |  |

|                    |           |                                                              | curacy   | @ 1.5 Msp                                             |      |       |                                                                             |  |  |

| AD20A              |           | Resolution                                                   |          | 10 Data                                               | Bits | -     |                                                                             |  |  |

| AD21A              |           | Integral Nonlinearity                                        | -0.5     | -0.3/+0.5                                             | +1.2 | LSb   |                                                                             |  |  |

| AD22A              |           | Differential Nonlinearity                                    | -0.9     | ±0.6                                                  | +0.9 | LSb   |                                                                             |  |  |

| AD23A              |           | Gain Error                                                   | 13       | 15                                                    | 22   | LSb   |                                                                             |  |  |

| AD24A              | EOFF      | Offset Error                                                 | 6        | 7                                                     | 8    | LSb   |                                                                             |  |  |

| AD25A              | —         | Monotonicity <sup>(1)</sup>                                  | —        | —                                                     | —    | —     | Guaranteed                                                                  |  |  |

|                    | 1         |                                                              | curacy   | @ 1.7 Msp                                             |      |       |                                                                             |  |  |

| AD20B              |           | Resolution                                                   |          | 10 Data                                               |      |       |                                                                             |  |  |

| AD21B              |           | Integral Nonlinearity                                        | -0.5     | -0.4/+1.1                                             | +1.8 | LSb   |                                                                             |  |  |

| AD22B              |           | Differential Nonlinearity                                    | -1.0     | ±1.0                                                  | +1.5 | LSb   |                                                                             |  |  |

| AD23B              |           | Gain Error                                                   | 13       | 15                                                    | 22   | LSb   |                                                                             |  |  |

| AD24B              | EOFF      | Offset Error                                                 | 6        | 7                                                     | 8    | LSb   |                                                                             |  |  |

| AD25B              |           | Monotonicity <sup>(1)</sup>                                  |          | —                                                     | —    | —     | Guaranteed                                                                  |  |  |

|                    |           |                                                              | curacy   | @ 2.0 Msp                                             |      |       | 1                                                                           |  |  |

| AD20C              |           | Resolution                                                   |          | 10 Data                                               |      | 1     |                                                                             |  |  |

| AD21C              |           | Integral Nonlinearity                                        | -0.8     | -0.5/+1.8                                             | +2.8 | LSb   |                                                                             |  |  |

| AD22C              |           | Differential Nonlinearity                                    | -1.0     | -1.0/+1.8                                             | +2.8 | LSb   |                                                                             |  |  |

| AD23C              |           | Gain Error                                                   | 14       | 16                                                    | 23   | LSb   |                                                                             |  |  |

| AD24C              | EOFF      | Offset Error                                                 | 6        | 7                                                     | 8    | LSb   |                                                                             |  |  |

| AD25C              | —         | Monotonicity <sup>(1)</sup>                                  |          |                                                       | _    | -     | Guaranteed                                                                  |  |  |

| 4000               | тир       | -                                                            | amic Pe  | rformance                                             |      | 40    |                                                                             |  |  |

| AD30               |           | Total Harmonic Distortion                                    | —        | -73                                                   |      | dB    |                                                                             |  |  |

| AD31               | SINAD     | Signal to Noise and Distortion                               |          | 58                                                    |      | dB    |                                                                             |  |  |

| AD32               | SFDR      | Spurious Free Dynamic Range                                  |          | -73                                                   |      | dB    |                                                                             |  |  |

| AD33               | FNYQ      | Input Signal Bandwidth                                       | —        | —                                                     | 1    | MHz   |                                                                             |  |  |

| AD34               | ENOB      | Effective Number of Bits alog-to-Digital conversion result r | —        | 9.4                                                   |      | bits  | 1                                                                           |  |  |

#### TABLE 24-40: 10-BIT HIGH-SPEED ADC MODULE SPECIFICATIONS

**Note 1:** The Analog-to-Digital conversion result never decreases with an increase in input voltage, and has no missing codes.

**2:** Module is functional at VBOR < VDD < VDDMIN, but with degraded performance. Module functionality is tested but not characterized.

#### Revision F (January 2012)

All occurrences of VDDCORE have been removed throughout the document.

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

#### TABLE A-4: MAJOR SECTION UPDATES