Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 50 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 35                                                                                 |

| Program Memory Size        | 16KB (16K × 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10b; D/A 4x10b                                                              |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 44-VFTLA Exposed Pad                                                               |

| Supplier Device Package    | 44-VTLA (6x6)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs504t-50i-tl |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33FJ06GS101/X02 AND dsPIC33FJ16GSX02/X04 PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed below. The following pages show their pinout diagrams.

### TABLE 1: dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 CONTROLLER FAMILIES

|                  |      | (si                           |             |                 |              | Rer           | napp           | able I | Perip | herals             |                   |                                    |            |      |      | ADC                           |                          |          |                                   |

|------------------|------|-------------------------------|-------------|-----------------|--------------|---------------|----------------|--------|-------|--------------------|-------------------|------------------------------------|------------|------|------|-------------------------------|--------------------------|----------|-----------------------------------|

| Device           | Pins | Program Flash Memory (Kbytes) | RAM (Bytes) | Remappable Pins | 16-Bit Timer | Input Capture | Output Compare | UART   | SPI   | PWM <sup>(2)</sup> | Analog Comparator | External Interrupts <sup>(3)</sup> | DAC Output | I²C™ | SARs | Sample-and-Hold (S&H) Circuit | Analog-to-Digital Inputs | I/O Pins | Packages                          |

| dsPIC33FJ06GS101 | 18   | 6                             | 256         | 8               | 2            | 0             | 1              | 1      | 1     | 2x2 <sup>(1)</sup> | 0                 | 3                                  | 0          | 1    | 1    | 3                             | 6                        | 13       | SOIC                              |

| dsPIC33FJ06GS102 | 28   | 6                             | 256         | 16              | 2            | 0             | 1              | 1      | 1     | 2x2                | 0                 | 3                                  | 0          | 1    | 1    | 3                             | 6                        | 21       | SPDIP,<br>SOIC,<br>QFN-S          |

| dsPIC33FJ06GS202 | 28   | 6                             | 1K          | 16              | 2            | 1             | 1              | 1      | 1     | 2x2                | 2                 | 3                                  | 1          | 1    | 1    | 3                             | 6                        | 21       | SPDIP,<br>SOIC,<br>QFN-S          |

| dsPIC33FJ16GS402 | 28   | 16                            | 2K          | 16              | 3            | 2             | 2              | 1      | 1     | 3x2                | 0                 | 3                                  | 0          | 1    | 1    | 4                             | 8                        | 21       | SPDIP,<br>SOIC,<br>QFN-S          |

| dsPIC33FJ16GS404 | 44   | 16                            | 2K          | 30              | 3            | 2             | 2              | 1      | 1     | 3x2                | 0                 | 3                                  | 0          | 1    | 1    | 4                             | 8                        | 35       | QFN,<br>TQFP,<br>VTLA             |

| dsPIC33FJ16GS502 | 28   | 16                            | 2K          | 16              | 3            | 2             | 2              | 1      | 1     | 4x2 <sup>(1)</sup> | 4                 | 3                                  | 1          | 1    | 2    | 6                             | 8                        | 21       | SPDIP,<br>SOIC,<br>QFN-S,<br>UQFN |

| dsPIC33FJ16GS504 | 44   | 16                            | 2K          | 30              | 3            | 2             | 2              | 1      | 1     | 4x2 <sup>(1)</sup> | 4                 | 3                                  | 1          | 1    | 2    | 6                             | 12                       | 35       | QFN,<br>TQFP,<br>VTLA             |

**Note 1:** The PWM4H:PWM4L pins are remappable.

2: The PWM Fault pins and PWM synchronization pins are remappable.

3: Only two out of three interrupts are remappable.

### **Table of Contents**

| dsPIC | C33FJ06GS101/X02 AND dsPIC33FJ16GSX02/X04 Product Families            | 2     |

|-------|-----------------------------------------------------------------------|-------|

| 1.0   | Device Overview                                                       | 17    |

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers | 21    |

| 3.0   | CPU                                                                   |       |

| 4.0   | Memory Organization                                                   | 43    |

| 5.0   | Flash Program Memory                                                  | 83    |

| 6.0   | Resets                                                                | 89    |

| 7.0   | Interrupt Controller                                                  | 97    |

| 8.0   | Oscillator Configuration                                              | . 135 |

| 9.0   | Power-Saving Features                                                 | . 147 |

| 10.0  | I/O Ports                                                             | . 155 |

| 11.0  | Timer1                                                                | . 183 |

| 12.0  | Timer2/3 Features                                                     | . 185 |

| 13.0  | Input Capture                                                         | . 191 |

| 14.0  | Output Compare                                                        | . 193 |

| 15.0  | High-Speed PWM                                                        |       |

| 16.0  |                                                                       |       |

| 17.0  | Inter-Integrated Circuit (I <sup>2</sup> C <sup>™</sup> )             |       |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART)                    | . 233 |

| 19.0  | High-Speed 10-bit Analog-to-Digital Converter (ADC)                   | . 239 |

| 20.0  | High-Speed Analog Comparator                                          |       |

| 21.0  | Special Features                                                      | . 267 |

| 22.0  | Instruction Set Summary                                               | . 275 |

| 23.0  | Development Support                                                   |       |

| 24.0  | Electrical Characteristics                                            |       |

| 25.0  | High-Temperature Electrical Characteristics                           |       |

| 26.0  | 50 MIPS Electrical Characteristics                                    |       |

|       | DC and AC Device Characteristics Graphs                               |       |

| 28.0  | Packaging Information                                                 | . 351 |

|       | /icrochip Web Site                                                    |       |

| Custo | omer Change Notification Service                                      | . 393 |

| Custo | omer Support                                                          | . 393 |

| Produ | uct Identification System                                             | . 395 |

### 6.1 System Reset

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/ X04 families of devices have two types of Reset:

- Cold Reset

- Warm Reset

A Cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a Cold Reset, the FNOSCx Configuration bits in the FOSC Configuration register select the device clock source. A Warm Reset is the result of all the other Reset sources, including the RESET instruction. On Warm Reset, the device will continue to operate from the current clock source as indicated by the Current Oscillator Selection (COSC<2:0>) bits in the Oscillator Control (OSCCON<14:12>) register.

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is detailed in Figure 6-2.

| Oscillator Mode           | Oscillator<br>Startup Delay | Oscillator<br>Startup Timer | PLL Lock Time        | Total Delay                             |

|---------------------------|-----------------------------|-----------------------------|----------------------|-----------------------------------------|

| FRC, FRCDIV16,<br>FRCDIVN | Toscd <sup>(1)</sup>        | _                           | _                    | Toscd <sup>(1)</sup>                    |

| FRCPLL                    | Toscd <sup>(1)</sup>        | _                           | ТLОСК <sup>(3)</sup> | Toscd + Tlock <sup>(1,3)</sup>          |

| XT                        | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| HS                        | Toscd(1)                    | Tost <sup>(2)</sup>         | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| EC                        | —                           | —                           | —                    | —                                       |

| XTPLL                     | Toscd <sup>(1)</sup>        | Tost <sup>(2)</sup>         | ТLОСК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| HSPLL                     | Toscd(1)                    | Tost <sup>(2)</sup>         | ТLOCК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| ECPLL                     | —                           | —                           | ТLОСК <sup>(3)</sup> | TLOCK <sup>(3)</sup>                    |

| LPRC                      | Toscd <sup>(1)</sup>        | _                           | —                    | Toscd <sup>(1)</sup>                    |

### TABLE 6-1:OSCILLATOR DELAY

**Note 1:** TOSCD = Oscillator start-up delay (1.1 μs max for FRC, 70 μs max for LPRC). Crystal oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal) if PLL is enabled.

| U-0           | U-0             | U-0              | U-0             | U-0              | U-0              | R/W-0           | U-0   |

|---------------|-----------------|------------------|-----------------|------------------|------------------|-----------------|-------|

| _             | —               |                  | —               | —                | _                | PSEMIE          |       |

| bit 15        |                 |                  |                 |                  |                  |                 | bit 8 |

|               |                 |                  |                 |                  |                  |                 |       |

| U-0           | U-0             | U-0              | U-0             | U-0              | U-0              | U-0             | U-0   |

| —             | —               | —                | —               | —                | —                | —               | —     |

| bit 7         |                 |                  |                 |                  |                  | •               | bit 0 |

|               |                 |                  |                 |                  |                  |                 |       |

| Legend:       |                 |                  |                 |                  |                  |                 |       |

| R = Readable  | e bit           | W = Writable     | bit             | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at | POR             | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|               |                 |                  |                 |                  |                  |                 |       |

| bit 15-10     | Unimplemen      | ted: Read as '   | כי              |                  |                  |                 |       |

| bit 9         | PSEMIE: PW      | M Special Ever   | nt Match Interi | rupt Enable bit  |                  |                 |       |

|               | 1 = Interrupt i | request enabled  | d               |                  |                  |                 |       |

|               |                 |                  |                 |                  |                  |                 |       |

- 0 = Interrupt request not enabled

- bit 8-0 Unimplemented: Read as '0'

### REGISTER 7-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   |     | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | —   | U1EIE | —     |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 U1EIE: UART1 Error Interrupt Enable bit

1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 Unimplemented: Read as '0'

### 9.2.2 IDLE MODE

The following occur in Idle mode:

- The CPU stops executing instructions

- The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active

The device will wake-up from Idle mode on any of these events:

- Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

### 9.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## 9.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

**Note:** If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

| <b>REGISTER 9-</b> | 3: PMD | 3: PERIPHER                                         | AL MODULE | DISABLE C                          | ONTROL RE | GISTER 3 |       |

|--------------------|--------|-----------------------------------------------------|-----------|------------------------------------|-----------|----------|-------|

| U-0                | U-0    | U-0                                                 | U-0       | U-0                                | R/W-0     | U-0      | U-0   |

| _                  | —      | —                                                   | —         | —                                  | CMPMD     | —        | —     |

| bit 15             |        |                                                     |           |                                    |           |          | bit 8 |

|                    |        |                                                     |           |                                    |           |          |       |

| U-0                | U-0    | U-0                                                 | U-0       | U-0                                | U-0       | U-0      | U-0   |

| —                  | —      | —                                                   | —         | —                                  | —         | —        | —     |

| bit 7              |        |                                                     |           |                                    |           |          | bit 0 |

|                    |        |                                                     |           |                                    |           |          |       |

| Legend:            |        |                                                     |           |                                    |           |          |       |

| R = Readable b     | bit    | W = Writable                                        | bit       | U = Unimplemented bit, read as '0' |           |          |       |

| -n = Value at P    | OR     | '1' = Bit is set '0' = Bit is cleared x = Bit is up |           | x = Bit is unkr                    | nown      |          |       |

|                    |        |                                                     |           |                                    |           |          |       |

| bit 15-11 | Unimplemented: Read as '0'                               |

|-----------|----------------------------------------------------------|

| bit 10    | CMPMD: Analog Comparator Module Disable bit              |

|           | <ol> <li>Analog comparator module is disabled</li> </ol> |

|           | 0 = Analog comparator module is enabled                  |

| bit 9-0   | Unimplemented: Read as '0'                               |

### REGISTER 9-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 3 **REFOMD**: Reference Clock Generator Module Disable bit

1 = Reference clock generator module is disabled

- 0 = Reference clock generator module is enabled

- bit 2-0 Unimplemented: Read as '0'

| U-0           | U-0                                                               | R/W-1                                                    | R/W-1          | R/W-1                                   | R/W-1          | R/W-1       | R/W-1  |  |  |

|---------------|-------------------------------------------------------------------|----------------------------------------------------------|----------------|-----------------------------------------|----------------|-------------|--------|--|--|

| _             | —                                                                 | FLT1R5                                                   | FLT1R4         | FLT1R3                                  | FLT1R2         | FLT1R1      | FLT1R0 |  |  |

| bit 15        |                                                                   |                                                          |                |                                         |                |             | bit    |  |  |

|               |                                                                   |                                                          |                |                                         |                |             |        |  |  |

| U-0           | U-0                                                               | U-0                                                      | U-0            | U-0                                     | U-0            | U-0         | U-0    |  |  |

| _             | <u> </u>                                                          | —                                                        | —              | —                                       |                |             | _      |  |  |

| bit 7         |                                                                   |                                                          |                |                                         |                |             | bit (  |  |  |

|               |                                                                   |                                                          |                |                                         |                |             |        |  |  |

| Legend:       |                                                                   |                                                          |                |                                         |                |             |        |  |  |

| R = Readable  | e bit                                                             | W = Writable                                             | bit            | U = Unimplemented bit, read as '0'      |                |             |        |  |  |

| -n = Value at | POR                                                               | '1' = Bit is set                                         |                | '0' = Bit is cleared x = Bit is unknown |                |             |        |  |  |

|               |                                                                   |                                                          |                |                                         |                |             |        |  |  |

| bit 15-14     | Unimplemer                                                        | ted: Read as '                                           | כי             |                                         |                |             |        |  |  |

| bit 13-8      | FLT1R<5:0>                                                        | : Assign PWM I                                           | ault Input 1 ( | FLT1) to the Co                         | orresponding R | Pn Pin bits |        |  |  |

|               | 111111 = Input tied to Vss                                        |                                                          |                |                                         |                |             |        |  |  |

|               | TTTTTT - UN                                                       | out fied to VSS                                          |                |                                         |                |             |        |  |  |

|               | 100011 <b>= In</b>                                                | out tied to RP35                                         |                |                                         |                |             |        |  |  |

|               | 100011 = Ing<br>100010 = Ing                                      | out tied to RP35<br>out tied to RP34                     | ŀ              |                                         |                |             |        |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                                         |                |             |        |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34                     | <br>}          |                                         |                |             |        |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                                         |                |             |        |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                                         |                |             |        |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing                      | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                                         |                |             |        |  |  |

|               | 100011 = Ing<br>100010 = Ing<br>100001 = Ing<br>100000 = Ing<br>• | out tied to RP35<br>out tied to RP34<br>out tied to RP33 | <br>}          |                                         |                |             |        |  |  |

### REGISTER 10-9: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

### 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as a time counter for the Real-Time Clock (RTC), or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low-power 32 kHz crystal oscillator available on the device

- Can be operated in Asynchronous Counter mode from an external clock source

- Optionally, the external clock input (T1CK) can be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

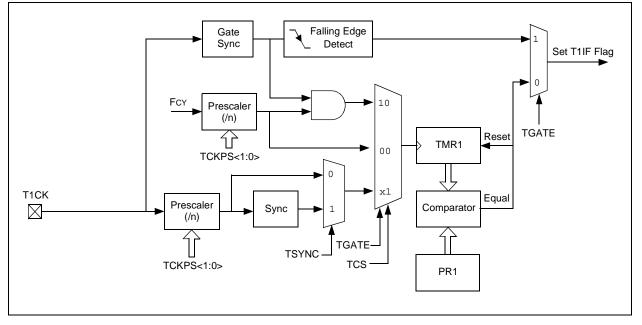

The unique features of Timer1 allow it to be used for Real-Time Clock (RTC) applications. A block diagram of Timer1 is shown in Figure 11-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

The timer control bit settings for different operating modes are given in the Table 11-1.

| TABLE 11-1: TIN | ER MODE SETTINGS |

|-----------------|------------------|

|-----------------|------------------|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | x     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| HS/HC-0      | ) HS/HC-0                | HS/HC-0                                       | R/W-0                        | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

|--------------|--------------------------|-----------------------------------------------|------------------------------|------------------|----------------------|----------------------|---------------------|

| FLTSTAT(     | 1) CLSTAT <sup>(1)</sup> | TRGSTAT                                       | FLTIEN                       | CLIEN            | TRGIEN               | ITB <sup>(3)</sup>   | MDCS <sup>(3)</sup> |

| bit 15       | ł                        |                                               |                              |                  |                      |                      | bit 8               |

|              |                          |                                               |                              |                  |                      |                      |                     |

| R/W-0        | R/W-0                    | U-0                                           | U-0                          | U-0              | R/W-0                | R/W-0                | R/W-0               |

| DTC1         | DTC0                     | —                                             | —                            |                  | CAM <sup>(2,3)</sup> | XPRES <sup>(4)</sup> | IUE                 |

| bit 7        |                          |                                               |                              |                  |                      |                      | bit                 |

| Legend:      |                          | HC = Hardware                                 | Clearable bit                | HS = Hardw       | are Settable bi      | it                   |                     |

| R = Readal   | hle hit                  | W = Writable bit                              |                              |                  | mented bit, rea      |                      |                     |

| -n = Value a |                          | '1' = Bit is set                              |                              | '0' = Bit is cle |                      | x = Bit is unl       | nown                |

|              |                          | 1 – Dit 13 Set                                |                              |                  | caleu                |                      | NIOWII              |

| bit 15       | FLTSTAT: F               | ault Interrupt Statu                          | us bit <sup>(1)</sup>        |                  |                      |                      |                     |

|              |                          | rrupt is pending                              |                              |                  |                      |                      |                     |

|              |                          | interrupt is pendin                           | g; this bit is cle           | ared by setting  | FLTIEN = 0           |                      |                     |

| bit 14       | CLSTAT: Cu               | urrent-Limit Interru                          | pt Status bit <sup>(1)</sup> |                  |                      |                      |                     |

|              |                          | mit interrupt is per<br>nt-limit interrupt is | Q                            | t is cleared by  | setting CLIEN        | = 0                  |                     |

| bit 13       | TRGSTAT: Tr              | rigger Interrupt Sta                          | itus bit                     |                  |                      |                      |                     |

|              |                          | terrupt is pending                            |                              |                  |                      |                      |                     |

|              | 0 = No trigge            | r interrupt is pendi                          | ng; this bit is cl           | eared by settin  | g TRGIEN = 0         | )                    |                     |

| bit 12       | FLTIEN: Fai              | ult Interrupt Enable                          | e bit                        |                  |                      |                      |                     |

|              |                          | rrupt is enabled                              |                              |                  |                      |                      |                     |

|              |                          | rrupt is disabled a                           |                              | T bit is cleared |                      |                      |                     |

| bit 11       |                          | rent-Limit Interrupt                          |                              |                  |                      |                      |                     |

|              |                          | mit interrupt is ena<br>mit interrupt is dis  |                              | CLSTAT bit is c  | leared               |                      |                     |

| bit 10       | TRGIEN: Trig             | ger Interrupt Enat                            | ole bit                      |                  |                      |                      |                     |

|              |                          | event generates a<br>vent interrupts are      |                              |                  | it is cleared        |                      |                     |

| bit 9        | ITB: Indepe              | ndent Time Base I                             | Mode bit <sup>(3)</sup>      |                  |                      |                      |                     |

|              | 1 = PHASEx/              | /SPHASEx registe<br>egister provides tir      | r provides time              |                  | r this PWM ge        | enerator             |                     |

| bit 8        |                          | ster Duty Cycle Re                            | -                            |                  |                      |                      |                     |

|              |                          | ister provides duty<br>Cx register provid     |                              |                  |                      | erator               |                     |

| bit 7-6      |                          | ead-Time Control                              |                              |                  | lie i till gene      |                      |                     |

|              | 11 = Reserve             |                                               | 513                          |                  |                      |                      |                     |

|              |                          | ne function is disa                           | bled                         |                  |                      |                      |                     |

|              |                          | e dead time is acti<br>dead time is activ     |                              |                  |                      |                      |                     |

| bit 5-3      |                          | ited: Read as '0'                             | - ,                          |                  |                      |                      |                     |

| Note 1:      | Software must clo        | ar the interrupt sta                          | tue here and th              | e correspondir   | a IFSy hit in t      | he interrupt or      | ontroller           |

| 2:           |                          | Time Base mode (                              |                              |                  | -                    | -                    |                     |

| 3:           | -                        | be changed only v                             | when PTEN = 0                | . Changing the   | e clock selectio     | on during ope        | ration will         |

|              |                          | real Dariad Deast                             | modo confirm                 |                  |                      |                      |                     |

#### REGISTER 15-6: PWMCONx: PWMx CONTROL REGISTER

4: To operate in External Period Reset mode, configure FCLCONx<CLMOD> = 0 and PWMCONx<ITB> = 1.

| REGISTER 15-9: PHA | SEx: PWMx PRIMARY PHASE-SHIFT REGISTER <sup>(1,2)</sup> |

|--------------------|---------------------------------------------------------|

|--------------------|---------------------------------------------------------|

| R/W-0                                                                              | R/W-0 | R/W-0           | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------------------------------------------------------|-------|-----------------|-------|------------------------------------|-------|-------|-------|

|                                                                                    |       |                 | PHAS  | Ex<15:8>                           |       |       |       |

| bit 15                                                                             |       |                 |       |                                    |       |       | bit 8 |

| R/W-0                                                                              | R/W-0 | R/W-0           | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                                    |       |                 | PHAS  | SEx<7:0>                           |       |       |       |

| bit 7                                                                              |       |                 |       |                                    |       |       | bit 0 |

|                                                                                    |       |                 |       |                                    |       |       |       |

| Legend:                                                                            |       |                 |       |                                    |       |       |       |

| R = Readable b                                                                     | bit   | W = Writable bi | it    | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR $(1)^2$ = Bit is set $(0)^2$ = Bit is cleared x = Bit is unknown |       |                 | nown  |                                    |       |       |       |

bit 15-0 PHASEx<15:0>: PWM Phase-Shift Value or Independent Time Base Period for this PWM Generator bits

- **Note 1:** If PWMCONx<ITB> = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10); PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

- True Independent Output mode (PMOD<1:0> (IOCONx<11:10>) = 11); PHASEx<15:0> = Phase-shift value for PWMxL only

- **2:** If PWMCONx<ITB> = 1, the following applies based on the mode of operation:

- Complementary, Redundant, and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10); PHASEx<15:0> = Independent Time Base period value for PWMxH and PWMxL

- True Independent Output mode (PMOD<1:0> (IOCONx<11:10>) = 11); PHASEx<15:0> = Independent Time Base period value for PWMxL only

- The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period 0x0008.

| R/W-0           | U-0                                                                                                         | R/W-0                                | R/W-1, HC      | R/W-0             | R/W-0                          | R/W-0               | R/W-0           |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|--------------------------------|---------------------|-----------------|--|--|

| I2CEN           | —                                                                                                           | I2CSIDL                              | SCLREL         | IPMIEN            | A10M                           | DISSLW              | SMEN            |  |  |

| bit 15          |                                                                                                             |                                      |                |                   |                                |                     | bit 8           |  |  |

| R/W-0           | R/W-0                                                                                                       | R/W-0                                | R/W-0, HC      | R/W-0, HC         | R/W-0, HC                      | R/W-0, HC           | R/W-0, HC       |  |  |

| GCEN            | STREN                                                                                                       | ACKDT                                | ACKEN          | RCEN              | PEN                            | RSEN                | SEN             |  |  |

| bit 7           |                                                                                                             |                                      |                |                   |                                |                     | bit (           |  |  |

| Legend:         |                                                                                                             |                                      | mented bit, re | ad as 'O'         |                                |                     |                 |  |  |

| R = Readable    | hit                                                                                                         | W = Writable                         |                |                   | re Clearable bit               |                     |                 |  |  |

| -n = Value at F |                                                                                                             | (1) = Bit is set                     |                | 0' = Bit is clear |                                | x = Bit is unkno    | nwn             |  |  |

|                 |                                                                                                             |                                      |                |                   |                                |                     |                 |  |  |

| bit 15          | 12CEN · 120                                                                                                 | Cx Enable bit                        |                |                   |                                |                     |                 |  |  |

|                 |                                                                                                             |                                      | odule, and cor | nfigures the SE   | Ax and SCLx pir                | ns as serial port r | oins            |  |  |

|                 |                                                                                                             |                                      |                |                   | trolled by port fur            |                     |                 |  |  |

| bit 14          | Unimplem                                                                                                    | ented: Read                          | <b>as</b> '0'  |                   |                                |                     |                 |  |  |

| bit 13          | I2CSIDL:                                                                                                    | 2Cx Stop in Ic                       | lle Mode bit   |                   |                                |                     |                 |  |  |

|                 |                                                                                                             | tinues module<br>ues module o        | •              |                   | ers an Idle mode               |                     |                 |  |  |

| bit 12          | SCLREL: SCLx Release Control bit (when operating as I <sup>2</sup> C slave)                                 |                                      |                |                   |                                |                     |                 |  |  |

|                 | 1 = Releases SCLx clock<br>0 = Holds SCLx clock low (clock stretch)                                         |                                      |                |                   |                                |                     |                 |  |  |

|                 | If STREN = 1:                                                                                               |                                      |                |                   |                                |                     |                 |  |  |

|                 | Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clea |                                      |                |                   |                                |                     |                 |  |  |

|                 | -                                                                                                           | -                                    | nsmission. Ha  | ardware clear a   | t end of slave ree             | ception.            |                 |  |  |

|                 | If STREN =                                                                                                  |                                      | can only wri   | te '1' to releas  | se clock). Hardw               | are clear at heri   | nning of slav   |  |  |

|                 | transmissi                                                                                                  | •                                    |                |                   |                                | are clear at begi   | Thing of Slav   |  |  |

| bit 11          | IPMIEN: Ir                                                                                                  | ntelligent Perip                     | heral Manage   | ement Interface   | e (IPMI) Enable b              | bit                 |                 |  |  |

|                 | 1 = IPMI m                                                                                                  | node is enable                       | d; all address | es are Acknow     | . ,                            |                     |                 |  |  |

| L:4 4 0         |                                                                                                             | node is disable                      |                |                   |                                |                     |                 |  |  |

| bit 10          |                                                                                                             | Bit Slave Add                        |                | _                 |                                |                     |                 |  |  |

|                 | 1 = I2CxADD is a 10-bit slave address<br>0 = I2CxADD is a 7-bit slave address                               |                                      |                |                   |                                |                     |                 |  |  |

| bit 9           |                                                                                                             | Disable Slew F                       |                | bit               |                                |                     |                 |  |  |

|                 |                                                                                                             | ate control is o<br>ate control is e |                |                   |                                |                     |                 |  |  |

| bit 8           |                                                                                                             | 1Bus Input Lev                       |                |                   |                                |                     |                 |  |  |

| bit 0           |                                                                                                             | -                                    |                | ant with SMBu     | s specification                |                     |                 |  |  |

|                 |                                                                                                             | es SMBus inp                         |                |                   | e ep comounon                  |                     |                 |  |  |

| bit 7           | GCEN: Ge                                                                                                    | eneral Call Ena                      | able bit (when | operating as I    | <sup>2</sup> C slave)          |                     |                 |  |  |

|                 | 1 = Enable<br>recept                                                                                        | -                                    | nen a general  | call address is   | received in the la             | 2CxRSR (module      | e is enabled fo |  |  |

|                 |                                                                                                             | al call addres                       | s is disabled  |                   |                                |                     |                 |  |  |

| bit 6           | STREN: S                                                                                                    | CLx Clock Str                        | etch Enable b  | oit (when opera   | ting as I <sup>2</sup> C slave | )                   |                 |  |  |

|                 |                                                                                                             | njunction with                       |                |                   |                                |                     |                 |  |  |

|                 |                                                                                                             | es software or                       |                | -                 |                                |                     |                 |  |  |

|                 | v = v sable                                                                                                 | es software or                       | receive clock  | stretching        |                                |                     |                 |  |  |

### REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER

## REGISTER 17-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                          |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                      |

|       | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit.<br/>Hardware is clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                      |

|       | 1 = Enables Receive mode for $I^2C$ . Hardware is clear at end of eighth bit of master receive data byte.<br>0 = Receive sequence is not in progress                                                                             |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                |

|       | <ul><li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at end of master Stop sequence.</li><li>0 = Stop condition is not in progress</li></ul>                                                            |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                     |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at end of master Repeated Start sequence.                                                                                                        |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                  |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                      |

|       | 1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at end of master Start sequence.                                                                                                                          |

|       | 0 = Start condition is not in progress                                                                                                                                                                                           |

#### REGISTER 19-6: ADCPC1: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 1

| R/W-0                 | R/W-0                | R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   |

|-----------------------|----------------------|-----------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| IRQEN3 <sup>(1)</sup> | PEND3 <sup>(1)</sup> | SWTRG3 <sup>(1)</sup> | TRGSRC34 <sup>(1)</sup> | TRGSRC33 <sup>(1)</sup> | TRGSRC32 <sup>(1)</sup> | TRGSRC31 <sup>(1)</sup> | TRGSRC30 <sup>(1)</sup> |

| bit 15                |                      |                       |                         |                         |                         |                         | bit 8                   |

| R/W-0                 | R/W-0                | R/W-0     | R/W-0       | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   |

|-----------------------|----------------------|-----------|-------------|-------------------------|-------------------------|-------------------------|-------------------------|

| IRQEN2 <sup>(2)</sup> | PEND2 <sup>(2)</sup> | SWTRG2(2) | TRGSRC24(2) | TRGSRC23 <sup>(2)</sup> | TRGSRC22 <sup>(2)</sup> | TRGSRC21 <sup>(2)</sup> | TRGSRC20 <sup>(2)</sup> |

| bit 7                 |                      |           |             |                         |                         |                         | bit 0                   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, reac | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  | <b>IRQEN3:</b> Interrupt Request Enable 3 bit <sup>(1)</sup><br>1 = Enables IRQ generation when requested conversion of Channels AN7 and AN6 is completed<br>0 = IRQ is not generated                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14  | PEND3: Pending Conversion Status 3 bit <sup>(1)</sup>                                                                                                                                                                         |

|         | <ul> <li>1 = Conversion of Channels AN7 and AN6 is pending; set when selected trigger is asserted</li> <li>0 = Conversion is complete</li> </ul>                                                                              |

| bit 13  | SWTRG3: Software Trigger 3 bit <sup>(1)</sup>                                                                                                                                                                                 |

|         | <ul> <li>1 = Starts conversion of AN7 and AN6 (if selected by the TRGSRCx bits)<sup>(3)</sup><br/>This bit is automatically cleared by hardware when the PEND3 bit is set.</li> <li>0 = Conversion has not started</li> </ul> |

| Note 1: | These bits are available in the dsPIC33FJ16GS402/404, dsPIC33FJ16GS504, dsPIC33FJ16GS502 and dsPIC33FJ06GS101 devices only.                                                                                                   |

- 2: These bits are available in the dsPIC33FJ16GS502, dsPIC33FJ16GS504, dsPIC33FJ06GS102, dsPIC33FJ06GS202 and dsPIC33FJ16GS402/404 devices only.

- **3:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

### REGISTER 19-8: ADCPC3: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup>

| bit 4-0 | TRGSRC6<4:0>: Trigger 6 Source Selection bits<br>Selects trigger source for conversion of Analog Channels AN13 and AN12.<br>11111 = Timer2 period match |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00111 = PWM Generator 4 primary trigger is selected<br>00110 = PWM Generator 3 primary trigger is selected                                              |

- Note 1: This register is only implemented on the dsPIC33FJ16GS502 and dsPIC33FJ16GS504 devices.

- 2: The trigger source must be set as global software trigger prior to setting this bit to '1'. If other conversions are in progress, conversion will be performed when the conversion resources are available.

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |                    |                       |       |                                                                                                                                       |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                      | Min                | Typ <sup>(1)</sup> | Max                   | Units | Conditions                                                                                                                            |

| DI60a              | licl   | Input Low Injection Current                                                                                                                                                                                                                                                         | 0                  | _                  | <sub>-5</sub> (5,8)   | mA    | All pins except VDD, Vss,<br>AVDD, AVss, MCLR,<br>VCAP and RB5                                                                        |

| DI60b              | Іісн   | Input High Injection Current                                                                                                                                                                                                                                                        | 0                  | _                  | +5 <sup>(6,7,8)</sup> | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR,<br>VCAP, RB5 and digital<br>5V-tolerant designated<br>pins                             |

| DI60c              | ∑ lict | Total Input Injection Current<br>(sum of all I/O and control pins)                                                                                                                                                                                                                  | -20 <sup>(9)</sup> | _                  | +20 <sup>(9)</sup>    | mA    | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from<br>all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |

#### TABLE 24-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for the list of 5V tolerant I/O pins.

- **5:** VIL source < (Vss 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

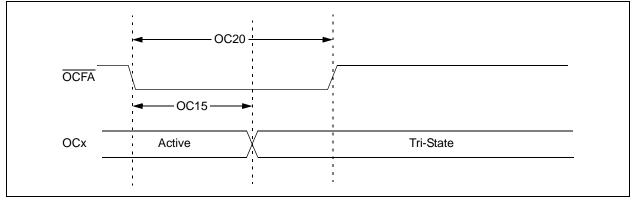

### FIGURE 24-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 24-28: SIMPLE OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |          |       |            |  |

|--------------------|--------|-----------------------------------|-------------------------------------------------------|-----|----------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min                                                   | Тур | Max      | Units | Conditions |  |

| OC15               | Tfd    | Fault Input to PWMx I/O<br>Change | _                                                     | _   | Tcy + 20 | ns    |            |  |

| OC20               | TFLT   | Fault Input Pulse Width           | Tcy + 20                                              | _   | —        | ns    |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

#### TABLE 25-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS |                                           |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                                                          |      |                         |  |

|--------------------|-------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|-------------------------|--|

| Parameter<br>No.   | Typical <sup>(1)</sup>                    | Мах  | Units                                                                                                                                                  | Conditions                                               |      |                         |  |

| Power-Down         | Power-Down Current (IPD) <sup>(2,4)</sup> |      |                                                                                                                                                        |                                                          |      |                         |  |

| HDC60e             | 1000                                      | 2000 | μA                                                                                                                                                     | +150°C                                                   | 3.3V | Base Power-Down Current |  |

| HDC61c             | 100                                       | 110  | μΑ                                                                                                                                                     | +150°C 3.3V Watchdog Timer Current: ΔΙωστ <sup>(3)</sup> |      |                         |  |

Note 1: Data in the Typical column is at 3.3V, +25°C unless otherwise stated.

2: IPD (Sleep) current is measured as follows:

- CPU core is off, oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all ones)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- JTAG disabled

- **3:** The ∆ current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

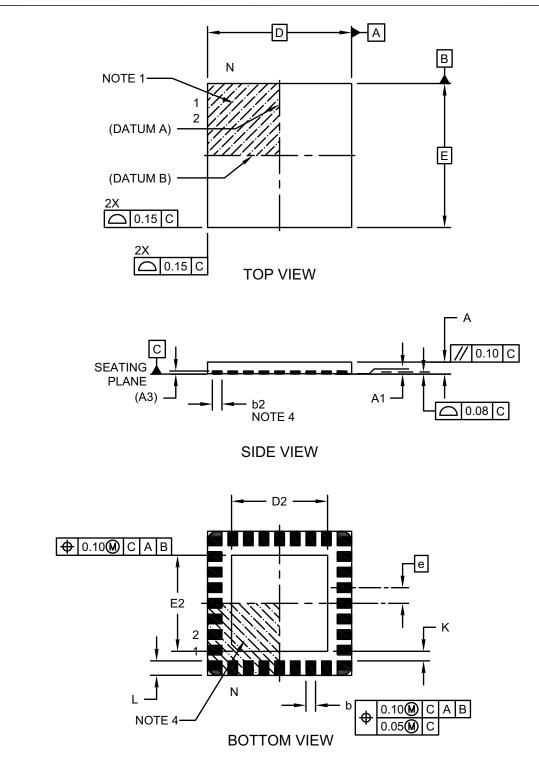

# 28-Lead Plastic Quad Flat, No Lead Package (MX) - 6x6x0.5mm Body [UQFN] Ultra-Thin with 0.40 x 0.60 mm Terminal Width/Length and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-0209B Sheet 1 of 2

# 28-Lead Plastic Quad Flat, No Lead Package (MX) - 6x6x0.5mm Body [UQFN] Ultra-Thin with 0.40 x 0.60 mm Terminal Width/Length and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |           |      |      |  |  |

|-------------------------|-------------|-----------|------|------|--|--|

| Dimension               | MIN         | NOM       | MAX  |      |  |  |

| Number of Pins          | N           |           | 28   |      |  |  |

| Pitch                   | е           | 0.65 BSC  |      |      |  |  |

| Overall Height          | Α           | 0.40      | 0.50 | 0.60 |  |  |

| Standoff                | A1          | 0.00      | 0.02 | 0.05 |  |  |

| Terminal Thickness      | (A3)        | 0.127 REF |      |      |  |  |

| Overall Width           | E           | 6.00 BSC  |      |      |  |  |

| Exposed Pad Width       | E2          |           | 4.00 |      |  |  |

| Overall Length          | D           | 6.00 BSC  |      |      |  |  |

| Exposed Pad Length      | D2          |           | 4.00 |      |  |  |

| Terminal Width          | b           | 0.35      | 0.40 | 0.45 |  |  |

| Corner Pad              | b2          | 0.25      | 0.40 | 0.45 |  |  |

| Terminal Length         | L           | 0.55      | 0.60 | 0.65 |  |  |

| Terminal-to-Exposed Pad | K           | 0.20      | -    | -    |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 4. Outermost portions of corner structures may vary slightly.

Microchip Technology Drawing C04-0209B Sheet 2 of 2

### Revision C and D (March 2009)

This revision includes minor typographical and formatting changes throughout the data sheet text.

Global changes include:

- Changed all instances of OSCI to OSC1 and OSCO to OSC2

- Changed all instances of PGCx/EMUCx and PGDx/EMUDx (where x = 1, 2, or 3) to PGECx and PGEDx

- Changed all instances of VDDCORE and VDDCORE/ VCAP to VCAP/VDDCORE

Other major changes are referenced by their respective section in the following table.

| Section Name                                                                              | Update Description                                                                                                                                            |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|