Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10b; D/A 4x10b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs504t-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

- bit 1 RND: Rounding Mode Select bit 1 = Biased (conventional) rounding is enabled

- 0 =Unbiased (convergent) rounding is enabled

- bit 0 IF: Integer or Fractional Multiplier Mode Select bit

- 1 = Integer mode is enabled for DSP multiply ops

- 0 = Fractional mode is enabled for DSP multiply ops

- Note 1: This bit will always read as '0'.

- 2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### 6.8.2 UNINITIALIZED W REGISTER RESET

Any attempt to use the Uninitialized W register as an Address Pointer will reset the device. The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to.

#### 6.8.3 SECURITY RESET

If a Program Flow Change (PFC) or Vector Flow Change (VFC) targets a restricted location in a protected segment (boot and secure segment), that operation will cause a Security Reset.

The PFC occurs when the Program Counter is reloaded as a result of a call, jump, computed jump, return, return from subroutine or other form of branch instruction.

The VFC occurs when the Program Counter is reloaded with an interrupt or trap vector.

Refer to Section 21.8 "Code Protection and CodeGuard™ Security" for more information on Security Reset.

### 6.9 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the Reset.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

Table 6-3 provides a summary of the Reset flag bit operation.

| Flag Bit            | Set by:                                                             | Cleared by:                                      |

|---------------------|---------------------------------------------------------------------|--------------------------------------------------|

| TRAPR (RCON<15>)    | Trap conflict event                                                 | POR, BOR                                         |

| IOPWR (RCON<14>)    | Illegal opcode or Uninitialized W register access or Security Reset | POR, BOR                                         |

| <b>CM</b> (RCON<9>) | Configuration Mismatch                                              | POR, BOR                                         |

| EXTR (RCON<7>)      | MCLR Reset                                                          | POR                                              |

| SWR (RCON<6>)       | RESET instruction                                                   | POR, BOR                                         |

| WDTO (RCON<4>)      | WDT time-out                                                        | PWRSAV instruction, CLRWDT instruction, POR, BOR |

| SLEEP (RCON<3>)     | PWRSAV #SLEEP instruction                                           | POR, BOR                                         |

| IDLE (RCON<2>)      | PWRSAV #IDLE instruction                                            | POR, BOR                                         |

| BOR (RCON<1>)       | POR, BOR                                                            | —                                                |

| POR (RCON<0>)       | POR                                                                 | _                                                |

#### TABLE 6-3: RESET FLAG BIT OPERATION

Note: All Reset flag bits can be set or cleared by user software.

| TABLE 7-1:       | INTERR                        | UPT VECTORS       |                           |                                          |

|------------------|-------------------------------|-------------------|---------------------------|------------------------------------------|

| Vector<br>Number | Interrupt<br>Request<br>(IQR) | IVT Address       | AIVT Address              | Interrupt Source                         |

|                  |                               | Highes            | st Natural Order Priority | /                                        |

| 8                | 0                             | 0x000014          | 0x000114                  | INT0 – External Interrupt 0              |

| 9                | 1                             | 0x000016          | 0x000116                  | IC1 – Input Capture 1                    |

| 10               | 2                             | 0x000018          | 0x000118                  | OC1 – Output Compare 1                   |

| 11               | 3                             | 0x00001A          | 0x00011A                  | T1 – Timer1                              |

| 12               | 4                             | 0x00001C          | 0x00011C                  | Reserved                                 |

| 13               | 5                             | 0x00001E          | 0x00011E                  | IC2 – Input Capture 2                    |

| 14               | 6                             | 0x000020          | 0x000120                  | OC2 – Output Compare 2                   |

| 15               | 7                             | 0x000022          | 0x000122                  | T2 – Timer2                              |

| 16               | 8                             | 0x000024          | 0x000124                  | T3 – Timer3                              |

| 17               | 9                             | 0x000026          | 0x000126                  | SPI1E – SPI1 Fault                       |

| 18               | 10                            | 0x000028          | 0x000128                  | SPI1 – SPI1 Transfer Done                |

| 19               | 11                            | 0x00002A          | 0x00012A                  | U1RX – UART1 Receiver                    |

| 20               | 12                            | 0x00002C          | 0x00012C                  | U1TX – UART1 Transmitter                 |

| 21               | 13                            | 0x00002E          | 0x00012E                  | ADC – ADC Group Convert Done             |

| 22-23            | 14-15                         | 0x000030-0x000032 | 0x000130-0x000132         | Reserved                                 |

| 24               | 16                            | 0x000034          | 0x000134                  | SI2C1 – I2C1 Slave Event                 |

| 25               | 17                            | 0x000036          | 0x000136                  | MI2C1 – I2C1 Master Event                |

| 26               | 18                            | 0x000038          | 0x000138                  | CMP1 – Analog Comparator 1 Interrupt     |

| 27               | 19                            | 0x00003A          | 0x00013A                  | CN – Input Change Notification Interrupt |

| 28               | 20                            | 0x00003C          | 0x00013C                  | INT1 – External Interrupt 1              |

| 29-36            | 21-28                         | 0x00003E-0x00004C | 0x00013E-0x00014C         | Reserved                                 |

| 37               | 29                            | 0x00004E          | 0x00014E                  | INT2 – External Interrupt 2              |

| 38-64            | 30-56                         | 0x000050-0x000084 | 0x000150-0x000184         | Reserved                                 |

| 65               | 57                            | 0x000086          | 0x000186                  | PWM PSEM Special Event Match             |

| 66-72            | 58-64                         | 0x000088-0x000094 | 0x000188-0x000194         | Reserved                                 |

| 73               | 65                            | 0x000096          | 0x000196                  | U1E – UART1 Error Interrupt              |

| 74-101           | 66-93                         | 0x000098-0x0000CE | 0x000198-0x0001CE         | Reserved                                 |

| 102              | 94                            | 0x0000D0          | 0x0001D0                  | PWM1 – PWM1 Interrupt                    |

| 103              | 95                            | 0x0000D2          | 0x0001D2                  | PWM2 – PWM2 Interrupt                    |

| 104              | 96                            | 0x0000D4          | 0x0001D4                  | PWM3 – PWM3 Interrupt                    |

| 105              | 97                            | 0x0000D6          | 0x0001D6                  | PWM4 – PWM4 Interrupt                    |

| 106-110          | 98-102                        | 0x0000D8-0x0000E0 | 0x0001D8-0x0001E0         | Reserved                                 |

| 111              | 103                           | 0x0000E2          | 0x00001E2                 | CMP2 – Analog Comparator 2               |

| 112              | 104                           | 0x0000E4          | 0x0001E4                  | CMP3 – Analog Comparator 3               |

| 113              | 105                           | 0x0000E6          | 0x0001E6                  | CMP4 – Analog Comparator 4               |

| 114-117          | 106-109                       | 0x0000E8-0x0000EE | 0x0001E8-0x0001EE         | Reserved                                 |

| 118              | 110                           | 0x0000F0          | 0x0001F0                  | ADC Pair 0 Convert Done                  |

| 119              | 111                           | 0x0000F2          | 0x0001F2                  | ADC Pair 1 Convert Done                  |

| 120              | 112                           | 0x0000F4          | 0x0001F4                  | ADC Pair 2 Convert Done                  |

| 121              | 113                           | 0x0000F6          | 0x0001F6                  | ADC Pair 3 Convert Done                  |

| 121              | 114                           | 0x0000F8          | 0x0001F8                  | ADC Pair 4 Convert Done                  |

| 122              | 115                           | 0x0000FA          | 0x0001FA                  | ADC Pair 5 Convert Done                  |

| 120              | 116                           | 0x0000FC          | 0x0001FC                  | ADC Pair 6 Convert Done                  |

| 125              | 117                           | 0x0000FE          | 0x0001FE                  | Reserved                                 |

| 0                |                               |                   | t Natural Order Priority  |                                          |

|                  |                               |                   |                           |                                          |

### TABLE 7-1:INTERRUPT VECTORS

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2 STKERR: Stack Error Trap Status bit

- 1 = Stack error trap has occurred

- 0 = Stack error trap has not occurred

- bit 1 OSCFAIL: Oscillator Failure Trap Status bit

- 1 = Oscillator failure trap has occurred

- 0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

| U-0                                                                  | U-0                                                                  | U-0 | U-0 | U-0  | U-0 | R/W-0  | U-0   |

|----------------------------------------------------------------------|----------------------------------------------------------------------|-----|-----|------|-----|--------|-------|

| —                                                                    | _                                                                    | _   | —   | _    | _   | PSEMIF | —     |

| bit 15                                                               |                                                                      |     |     |      |     |        | bit 8 |

|                                                                      |                                                                      |     |     |      |     |        |       |

| U-0                                                                  | U-0                                                                  | U-0 | U-0 | U-0  | U-0 | U-0    | U-0   |

| _                                                                    |                                                                      | _   | —   |      |     |        |       |

| bit 7                                                                |                                                                      |     |     |      |     |        | bit 0 |

|                                                                      |                                                                      |     |     |      |     |        |       |

| Legend:                                                              |                                                                      |     |     |      |     |        |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                      |     |     |      |     |        |       |

| -n = Value at P                                                      | alue at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |     | nown |     |        |       |

|                                                                      |                                                                      |     |     |      |     |        |       |

### REGISTER 7-7: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| bit 15-10 | Unimplemented: Read as '0'                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------|

| bit 9     | PSEMIF: PWM Special Event Match Interrupt Flag Status bit                                           |

|           | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 8-0   | Unimplemented: Read as '0'                                                                          |

#### REGISTER 7-8: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | —   | U1EIF | —     |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-2 Unimplemented: Read as '0'

bit 1 U1EIF: UART1 Error Interrupt Flag Status bit

I = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 0 Unimplemented: Read as '0'

| U-0           | U-0                        | U-0              | U-0             | U-0                                     | U-0              | R/W-0  | U-0   |  |

|---------------|----------------------------|------------------|-----------------|-----------------------------------------|------------------|--------|-------|--|

| _             | _                          |                  | —               | —                                       | _                | PSEMIE |       |  |

| bit 15        |                            |                  |                 |                                         |                  |        | bit 8 |  |

|               |                            |                  |                 |                                         |                  |        |       |  |

| U-0           | U-0                        | U-0              | U-0             | U-0                                     | U-0              | U-0    | U-0   |  |

| —             | —                          | —                | —               | —                                       | —                | —      | —     |  |

| bit 7         |                            |                  |                 |                                         |                  | •      | bit 0 |  |

|               |                            |                  |                 |                                         |                  |        |       |  |

| Legend:       |                            |                  |                 |                                         |                  |        |       |  |

| R = Readable  | e bit                      | W = Writable     | bit             | U = Unimpler                            | mented bit, read | as '0' |       |  |

| -n = Value at | POR                        | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is unknown |                  |        | nown  |  |

|               |                            |                  |                 |                                         |                  |        |       |  |

| bit 15-10     | Unimplemented: Read as '0' |                  |                 |                                         |                  |        |       |  |

| bit 9         | PSEMIE: PW                 | M Special Ever   | nt Match Interi | rupt Enable bit                         |                  |        |       |  |

|               | 1 = Interrupt i            | request enabled  | d               |                                         |                  |        |       |  |

|               |                            |                  |                 |                                         |                  |        |       |  |

- 0 = Interrupt request not enabled

- bit 8-0 Unimplemented: Read as '0'

#### REGISTER 7-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   |     | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | —   | U1EIE | —     |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-2 Unimplemented: Read as '0'

bit 1 U1EIE: UART1 Error Interrupt Enable bit

1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 Unimplemented: Read as '0'

| R = Readable | bit | W = Writable | bit    | U = Unimplemented bit, read as '0' |        |        |        |  |

|--------------|-----|--------------|--------|------------------------------------|--------|--------|--------|--|

| Legend:      |     |              |        |                                    |        |        |        |  |

|              |     |              |        |                                    |        |        |        |  |

| bit 7        | 1   |              |        |                                    |        | •      | bit 0  |  |

|              | —   | RP22R5       | RP22R4 | RP22R3                             | RP22R2 | RP22R1 | RP22R0 |  |

| U-0          | U-0 | R/W-0        | R/W-0  | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |

|              |     |              |        |                                    |        |        | 5110   |  |

| bit 15       | •   |              | •      | •                                  |        |        | bit 8  |  |

| _            | _   | RP23R5       | RP23R4 | RP23R3                             | RP23R2 | RP23R1 | RP23R0 |  |

| U-0          | U-0 | R/W-0        | R/W-0  | R/W-0                              | R/W-0  | R/W-0  | R/W-0  |  |

## REGISTER 10-26: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11<sup>(1)</sup>

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP23R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP23 Output Pin bits (see Table 10-2 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP22R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP22 Output Pin bits (see Table 10-2 for peripheral function numbers) |

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

| U-0                                                                                                                                              | U-0        | R/W-0                             | R/W-0  | R/W-0                | R/W-0            | R/W-0              | R/W-0  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------|--------|----------------------|------------------|--------------------|--------|--|

| _                                                                                                                                                | —          | RP25R5                            | RP25R4 | RP25R3               | RP25R2           | RP25R1             | RP25R0 |  |

| bit 15                                                                                                                                           |            |                                   |        | ·                    | •                |                    | bit 8  |  |

|                                                                                                                                                  |            |                                   |        |                      |                  |                    |        |  |

| U-0                                                                                                                                              | U-0        | R/W-0                             | R/W-0  | R/W-0                | R/W-0            | R/W-0              | R/W-0  |  |

| _                                                                                                                                                | —          | RP24R5                            | RP24R4 | RP24R3               | RP24R2           | RP24R1             | RP24R0 |  |

| bit 7                                                                                                                                            |            | •                                 |        | ·                    | ·                | •                  | bit 0  |  |

|                                                                                                                                                  |            |                                   |        |                      |                  |                    |        |  |

| Legend:                                                                                                                                          |            |                                   |        |                      |                  |                    |        |  |

| R = Readabl                                                                                                                                      | e bit      | W = Writable                      | bit    | U = Unimpler         | mented bit, read | l as '0'           |        |  |

| -n = Value at                                                                                                                                    | POR        | '1' = Bit is set                  |        | '0' = Bit is cleared |                  | x = Bit is unknown |        |  |

|                                                                                                                                                  |            |                                   |        |                      |                  |                    |        |  |

| bit 15-14                                                                                                                                        | Unimplemen | ted: Read as '                    | 0'     |                      |                  |                    |        |  |

| bit 13-8                                                                                                                                         |            | Peripheral Ou<br>-2 for periphera |        | •                    | RP25 Output F    | Pin bits           |        |  |

| bit 7-6                                                                                                                                          | Unimplemen | ted: Read as '                    | 0'     |                      |                  |                    |        |  |

| bit 5-0 <b>RP24R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP24 Output Pin bits (see Table 10-2 for peripheral function numbers) |            |                                   |        |                      |                  |                    |        |  |

|                                                                                                                                                  |            |                                   |        |                      |                  |                    |        |  |

### **REGISTER 10-27:** RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12<sup>(1)</sup>

Note 1: This register is implemented in the dsPIC33FJ16GS404 and dsPIC33FJ16GS504 devices only.

| REGISTER 1      | 1-1: T1CO                                                                      | N: TIMER1 C                     | ONTROL RE       | GISTER           |                  |                  |       |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------|---------------------------------|-----------------|------------------|------------------|------------------|-------|--|--|--|--|

| R/W-0           | U-0                                                                            | R/W-0                           | U-0             | U-0              | U-0              | U-0              | U-0   |  |  |  |  |

| TON             | —                                                                              | TSIDL                           | —               | —                | —                | —                |       |  |  |  |  |

| bit 15          |                                                                                |                                 |                 |                  |                  |                  | bit 8 |  |  |  |  |

|                 | <b>D</b> 4 4 4                                                                 |                                 |                 |                  | 5444.6           | <b>D b b c c</b> |       |  |  |  |  |

| U-0             | R/W-0                                                                          | R/W-0                           | R/W-0           | U-0              | R/W-0            | R/W-0            | U-0   |  |  |  |  |

|                 | TGATE                                                                          | TCKPS1                          | TCKPS0          | _                | TSYNC            | TCS              | —     |  |  |  |  |

| bit 7           |                                                                                |                                 |                 |                  |                  |                  | bit ( |  |  |  |  |

| Legend:         |                                                                                |                                 |                 |                  |                  |                  |       |  |  |  |  |

| R = Readable    | bit                                                                            | W = Writable                    | bit             | U = Unimpler     | mented bit, read | l as '0'         |       |  |  |  |  |

| -n = Value at I | POR                                                                            | '1' = Bit is set                |                 | '0' = Bit is cle |                  | x = Bit is unkno | own   |  |  |  |  |

|                 |                                                                                |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 15          | TON: Timer1                                                                    | On bit                          |                 |                  |                  |                  |       |  |  |  |  |

|                 | 1 = Starts 16-                                                                 | bit Timer1                      |                 |                  |                  |                  |       |  |  |  |  |

|                 | 0 = Stops 16-                                                                  | bit Timer1                      |                 |                  |                  |                  |       |  |  |  |  |

| bit 14          | Unimplemen                                                                     | ted: Read as '                  | 0'              |                  |                  |                  |       |  |  |  |  |

| bit 13          | TSIDL: Timer1 Stop in Idle Mode bit                                            |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                | ues module op<br>s module opera |                 |                  | dle mode         |                  |       |  |  |  |  |

| bit 12-7        |                                                                                | -                               |                 |                  |                  |                  |       |  |  |  |  |

| bit 6           | Unimplemented: Read as '0'<br>TGATE: Timer1 Gated Time Accumulation Enable bit |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 0           | When TCS = 1:                                                                  |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | This bit is ignored.                                                           |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | When TCS =                                                                     | 0:                              |                 |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                | e accumulation                  |                 |                  |                  |                  |       |  |  |  |  |

| bit E 1         |                                                                                | e accumulation                  |                 | - Coloct hito    |                  |                  |       |  |  |  |  |

| bit 5-4         | TCKPS<1:0> Timer1 Input Clock Prescale Select bits                             |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | 11 = 1:256<br>10 = 1:64                                                        |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | 01 = 1:8                                                                       |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | 00 = 1:1                                                                       |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 3           | Unimplemen                                                                     | ted: Read as '                  | 0'              |                  |                  |                  |       |  |  |  |  |

| bit 2           | TSYNC: Timer1 External Clock Input Synchronization Select bit                  |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 | When $TCS = 1$ :                                                               |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                | izes external c                 |                 | aput             |                  |                  |       |  |  |  |  |

|                 | When TCS =                                                                     | synchronize e>                  | Riemai Ciuck II | iput             |                  |                  |       |  |  |  |  |

|                 | This bit is igno                                                               |                                 |                 |                  |                  |                  |       |  |  |  |  |

| bit 1           | •                                                                              | Clock Source S                  | Select bit      |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                | clock from T1C                  |                 | rising edge)     |                  |                  |       |  |  |  |  |

|                 | 0 = Internal cl                                                                |                                 |                 |                  |                  |                  |       |  |  |  |  |

|                 |                                                                                |                                 |                 |                  |                  |                  |       |  |  |  |  |

### REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

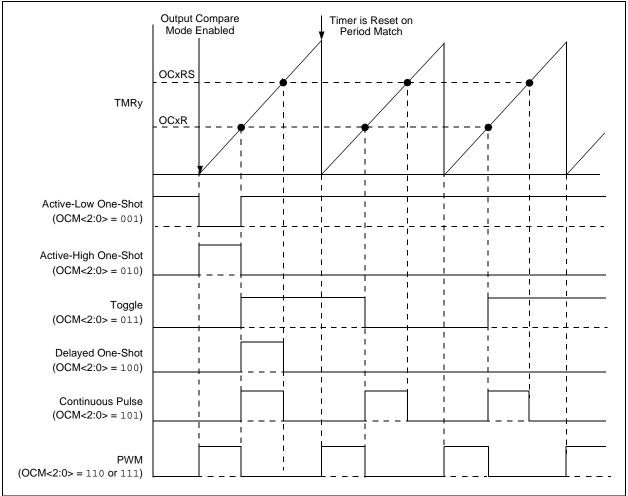

### 14.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 14-1 lists the different bit settings for the Output Compare modes. Figure 14-2 illustrates the output compare operation for various modes. The user

TABLE 14-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

| Note: | Refer to "Output Compare" (DS70209)  |  |  |  |  |  |  |

|-------|--------------------------------------|--|--|--|--|--|--|

|       | in the "dsPIC33F/PIC24H Family       |  |  |  |  |  |  |

|       | Reference Manual" for OCxR and OCxRS |  |  |  |  |  |  |

|       | register restrictions.               |  |  |  |  |  |  |

| OCM<2:0>                         | Mode                      | OCx Pin Initial State        | OCx Interrupt Generation         |  |  |

|----------------------------------|---------------------------|------------------------------|----------------------------------|--|--|

| 111                              | PWM with Fault Protection | '0', if OCxR is zero         | OCFA falling edge for OC1 to OC4 |  |  |

|                                  |                           | '1', if OCxR is non-zero     |                                  |  |  |

| 110 PWM without Fault Protection |                           | '0', if OCxR is zero         | No interrupt                     |  |  |

|                                  |                           | '1', if OCxR is non-zero     |                                  |  |  |

| 101                              | Continuous Pulse          | 0                            | OCx falling edge                 |  |  |

| 100                              | Delayed One-Shot          | 0                            | OCx falling edge                 |  |  |

| 011                              | Toggle                    | Current output is maintained | OCx rising and falling edge      |  |  |

| 010                              | Active-High One-Shot      | 1                            | OCx falling edge                 |  |  |

| 001                              | Active-Low One-Shot       | 0                            | OCx rising edge                  |  |  |

| 000                              | Module Disabled           | Controlled by GPIO register  | —                                |  |  |

#### FIGURE 14-2: OUTPUT COMPARE OPERATION

NOTES:

| HS/HC-0      | ) HS/HC-0                | HS/HC-0                                       | R/W-0                        | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |  |

|--------------|--------------------------|-----------------------------------------------|------------------------------|------------------|----------------------|----------------------|---------------------|--|--|--|--|

| FLTSTAT(     | 1) CLSTAT <sup>(1)</sup> | TRGSTAT                                       | FLTIEN                       | CLIEN            | TRGIEN               | ITB <sup>(3)</sup>   | MDCS <sup>(3)</sup> |  |  |  |  |

| bit 15       | ł                        |                                               |                              |                  |                      |                      | bit 8               |  |  |  |  |

|              |                          |                                               |                              |                  |                      |                      |                     |  |  |  |  |

| R/W-0        | R/W-0                    | U-0                                           | U-0                          | U-0              | R/W-0                | R/W-0                | R/W-0               |  |  |  |  |

| DTC1         | DTC0                     | —                                             | —                            |                  | CAM <sup>(2,3)</sup> | XPRES <sup>(4)</sup> | IUE                 |  |  |  |  |

| bit 7        |                          |                                               |                              |                  |                      |                      | bit                 |  |  |  |  |

| Legend:      |                          | HC = Hardware                                 | Clearable bit                | HS = Hardw       | are Settable bi      | it                   |                     |  |  |  |  |

| R = Readal   | hle hit                  | W = Writable bit                              |                              |                  | mented bit, rea      |                      |                     |  |  |  |  |

| -n = Value a |                          | '1' = Bit is set                              |                              | '0' = Bit is cle |                      | x = Bit is unl       | nown                |  |  |  |  |

|              |                          | 1 – Dit 13 Set                                |                              |                  | caleu                |                      | NIOWII              |  |  |  |  |

| bit 15       | FLTSTAT: F               | ault Interrupt Statu                          | us bit <sup>(1)</sup>        |                  |                      |                      |                     |  |  |  |  |

|              |                          | rrupt is pending                              |                              |                  |                      |                      |                     |  |  |  |  |

|              |                          | interrupt is pendin                           | g; this bit is cle           | ared by setting  | FLTIEN = 0           |                      |                     |  |  |  |  |

| bit 14       | CLSTAT: Cu               | urrent-Limit Interru                          | pt Status bit <sup>(1)</sup> |                  |                      |                      |                     |  |  |  |  |

|              |                          | mit interrupt is per<br>nt-limit interrupt is | Q                            | t is cleared by  | setting CLIEN        | = 0                  |                     |  |  |  |  |

| bit 13       | TRGSTAT: Tr              | rigger Interrupt Sta                          | itus bit                     |                  |                      |                      |                     |  |  |  |  |

|              |                          | terrupt is pending                            |                              |                  |                      |                      |                     |  |  |  |  |

|              | 0 = No trigge            | r interrupt is pendi                          | ng; this bit is cl           | eared by settin  | g TRGIEN = 0         | )                    |                     |  |  |  |  |

| bit 12       | FLTIEN: Fai              | FLTIEN: Fault Interrupt Enable bit            |                              |                  |                      |                      |                     |  |  |  |  |

|              |                          | rrupt is enabled                              |                              |                  |                      |                      |                     |  |  |  |  |

|              |                          | rrupt is disabled a                           |                              | T bit is cleared |                      |                      |                     |  |  |  |  |

| bit 11       |                          | rent-Limit Interrupt                          |                              |                  |                      |                      |                     |  |  |  |  |

|              |                          | mit interrupt is ena<br>mit interrupt is dis  |                              | CLSTAT bit is c  | leared               |                      |                     |  |  |  |  |

| bit 10       | TRGIEN: Trig             | ger Interrupt Enat                            | ole bit                      |                  |                      |                      |                     |  |  |  |  |

|              |                          | event generates a<br>vent interrupts are      |                              |                  | it is cleared        |                      |                     |  |  |  |  |

| bit 9        | ITB: Indepe              | ndent Time Base I                             | Mode bit <sup>(3)</sup>      |                  |                      |                      |                     |  |  |  |  |

|              | 1 = PHASEx/              | /SPHASEx registe<br>egister provides tir      | r provides time              |                  | r this PWM ge        | enerator             |                     |  |  |  |  |

| bit 8        |                          | ster Duty Cycle Re                            | -                            |                  |                      |                      |                     |  |  |  |  |

|              |                          | ister provides duty<br>Cx register provid     |                              |                  |                      | erator               |                     |  |  |  |  |

| bit 7-6      |                          | ead-Time Control                              |                              |                  | lie i till gene      |                      |                     |  |  |  |  |

|              | 11 = Reserve             |                                               | 513                          |                  |                      |                      |                     |  |  |  |  |

|              |                          | ne function is disa                           | bled                         |                  |                      |                      |                     |  |  |  |  |

|              |                          | e dead time is acti<br>dead time is activ     |                              |                  |                      |                      |                     |  |  |  |  |

| bit 5-3      |                          | ited: Read as '0'                             | - ,                          |                  |                      |                      |                     |  |  |  |  |

| Note 1:      | Software must clo        | ar the interrupt sta                          | tue here and th              | e correspondir   | a IFSy hit in t      | he interrupt or      | ontroller           |  |  |  |  |

| 2:           |                          | Time Base mode (                              |                              |                  | -                    | -                    |                     |  |  |  |  |

| 3:           | -                        | be changed only v                             | when PTEN = 0                | . Changing the   | e clock selectio     | on during ope        | ration will         |  |  |  |  |

|              |                          | real Dariad Deast                             | mode confirm                 |                  |                      |                      |                     |  |  |  |  |

#### REGISTER 15-6: PWMCONx: PWMx CONTROL REGISTER

4: To operate in External Period Reset mode, configure FCLCONx<CLMOD> = 0 and PWMCONx<ITB> = 1.

### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- - 00 = Primary prescale 64:1

- **Note 1:** The CKE bit is not used in the Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both primary and secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

NOTES:

#### REGISTER 19-5: ADCPC0: ANALOG-TO-DIGITAL CONVERT PAIR CONTROL REGISTER 0 (CONTINUED)

```

bit 4-0

TRGSRC0<4:0>: Trigger 0 Source Selection bits

Selects trigger source for conversion of Analog Channels AN1 and AN0.

11111 = Timer2 period match

11011 = Reserved

11010 = PWM Generator 4 current-limit ADC trigger

11001 = PWM Generator 3 current-limit ADC trigger

11000 = PWM Generator 2 current-limit ADC trigger

10111 = PWM Generator 1 current-limit ADC trigger

10110 = \text{Reserved}

10010 = Reserved

10001 = PWM Generator 4 secondary trigger is selected

10000 = PWM Generator 3 secondary trigger is selected

01111 = PWM Generator 2 secondary trigger is selected

01110 = PWM Generator 1 secondary trigger is selected

01101 = Reserved

01100 = Timer1 period match

01000 = Reserved

00111 = PWM Generator 4 primary trigger is selected

00110 = PWM Generator 3 primary trigger is selected

00101 = PWM Generator 2 primary trigger is selected

00100 = PWM Generator 1 primary trigger is selected

00011 = PWM Special Event Trigger is selected

00010 = Global software trigger is selected

00001 = Individual software trigger is selected

00000 = No conversion is enabled

```

**Note 1:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then the conversion will be performed when the conversion resources are available.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all Table Reads and Table Writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

| Note: | For more details on the instruction set, |

|-------|------------------------------------------|

|       | refer to the "16-bit MCU and DSC         |

|       | Programmer's Reference Manual"           |

|       | (DS70157).                               |

| Field           | Description                                                                          |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| #text           | Means literal defined by "text"                                                      |  |  |  |  |  |  |

| (text)          | Means "content of text"                                                              |  |  |  |  |  |  |

| [text]          | Means "the location addressed by text"                                               |  |  |  |  |  |  |

| { }             | Optional field or operation                                                          |  |  |  |  |  |  |

| <n:m></n:m>     | Register bit field                                                                   |  |  |  |  |  |  |

| .b              | Byte mode selection                                                                  |  |  |  |  |  |  |

| .d              | Double-Word mode selection                                                           |  |  |  |  |  |  |

| .S              | Shadow register select                                                               |  |  |  |  |  |  |

| .W              | Word mode selection (default)                                                        |  |  |  |  |  |  |

| Acc             | One of two accumulators {A, B}                                                       |  |  |  |  |  |  |

| AWB             | Accumulator Write-Back Destination Address register $\in$ {W13, [W13]+ = 2}          |  |  |  |  |  |  |

| bit4            | 4-bit bit selection field (used in word-addressed instructions) $\in \{015\}$        |  |  |  |  |  |  |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |  |  |  |  |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |  |  |  |  |  |  |

| f               | File register address ∈ {0x00000x1FFF}                                               |  |  |  |  |  |  |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                       |  |  |  |  |  |  |

| lit4            | 4-bit unsigned literal ∈ {015}                                                       |  |  |  |  |  |  |

| lit5            | 5-bit unsigned literal ∈ {031}                                                       |  |  |  |  |  |  |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                      |  |  |  |  |  |  |

| lit10           | 10-bit unsigned literal $\in \{0255\}$ for Byte mode, $\{0:1023\}$ for Word mode     |  |  |  |  |  |  |

| lit14           | 14-bit unsigned literal $\in \{016384\}$                                             |  |  |  |  |  |  |

| lit16           | 16-bit unsigned literal $\in \{065535\}$                                             |  |  |  |  |  |  |

| lit23           | 23-bit unsigned literal $\in$ {08388608}; LSb must be '0'                            |  |  |  |  |  |  |

| None            | Field does not require an entry, can be blank                                        |  |  |  |  |  |  |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |  |  |  |  |  |  |

| PC              | Program Counter                                                                      |  |  |  |  |  |  |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |  |  |  |  |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |  |  |  |  |  |  |

| Slit6           | 6-bit signed literal $\in$ {-1616}                                                   |  |  |  |  |  |  |

| Wb              | Base W register ∈ {W0W15}                                                            |  |  |  |  |  |  |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |  |  |  |  |  |  |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |  |  |  |  |  |  |

| Wm,Wn           | Dividend, Divisor Working register pair (Direct Addressing)                          |  |  |  |  |  |  |

TABLE 22-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| DC CHARACTERISTICS |                        |                  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |        |       |                            |  |

|--------------------|------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------------------------|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Мах              | Units                                                                                                                                                                                                |        |       | Conditions                 |  |

| Operating C        | Current (IDD)          | ) <sup>(2)</sup> |                                                                                                                                                                                                      |        |       |                            |  |

| DC20d              | 55                     | 70               | mA                                                                                                                                                                                                   | -40°C  |       |                            |  |

| DC20a              | 55                     | 70               | mA                                                                                                                                                                                                   | +25°C  | 3.3V  | 10 MIPS                    |  |

| DC20b              | 55                     | 70               | mA                                                                                                                                                                                                   | +85°C  | 3.3V  | See Note 2                 |  |

| DC20c              | 55                     | 70               | mA                                                                                                                                                                                                   | +125°C |       |                            |  |

| DC21d              | 68                     | 85               | mA                                                                                                                                                                                                   | -40°C  |       |                            |  |

| DC21a              | 68                     | 85               | mA                                                                                                                                                                                                   | +25°C  | 3.3V  | 16 MIPS                    |  |

| DC21b              | 68                     | 85               | mA                                                                                                                                                                                                   | +85°C  | 3.3V  | See Note 2 and Note 3      |  |

| DC21c              | 68                     | 85               | mA                                                                                                                                                                                                   | +125°C |       |                            |  |

| DC22d              | 78                     | 95               | mA                                                                                                                                                                                                   | -40°C  |       |                            |  |

| DC22a              | 78                     | 95               | mA                                                                                                                                                                                                   | +25°C  | 3.3V  | 20 MIPS                    |  |

| DC22b              | 78                     | 95               | mA                                                                                                                                                                                                   | +85°C  | 3.3V  | See Note 2 and Note 3      |  |

| DC22c              | 78                     | 95               | mA                                                                                                                                                                                                   | +125°C |       |                            |  |

| DC23d              | 88                     | 110              | mA                                                                                                                                                                                                   | -40°C  |       |                            |  |

| DC23a              | 88                     | 110              | mA                                                                                                                                                                                                   | +25°C  | 3.3V  | 30 MIPS                    |  |

| DC23b              | 88                     | 110              | mA                                                                                                                                                                                                   | +85°C  | 3.3V  | See Note 2 and Note 3      |  |

| DC23c              | 88                     | 110              | mA                                                                                                                                                                                                   | +125°C |       |                            |  |

| DC24d              | 98                     | 120              | mA                                                                                                                                                                                                   | -40°C  |       |                            |  |

| DC24a              | 98                     | 120              | mA                                                                                                                                                                                                   | +25°C  | 3.3V  | 40 MIPS                    |  |

| DC24b              | 98                     | 120              | mA                                                                                                                                                                                                   | +85°C  | 5.5 v | See Note 2                 |  |

| DC24c              | 98                     | 120              | mA                                                                                                                                                                                                   | +125°C |       |                            |  |

| DC25d              | 128                    | 160              | mA                                                                                                                                                                                                   | -40°C  |       | 40 MIPS                    |  |

| DC25a              | 125                    | 150              | mA                                                                                                                                                                                                   | +25°C  | 3.3V  | See Note 2, except PWM is  |  |

| DC25b              | 121                    | 150              | mA                                                                                                                                                                                                   | +85°C  | 5.5V  | operating at maximum speed |  |

| DC25c              | 119                    | 150              | mA                                                                                                                                                                                                   | +125°C |       | (PTCON2 = 0x0000)          |  |

| DC26d              | 115                    | 140              | mA                                                                                                                                                                                                   | -40°C  |       | 40 MIPS                    |  |

| DC26a              | 112                    | 140              | mA                                                                                                                                                                                                   | +25°C  | 3.3V  | See Note 2, except PWM is  |  |

| DC26b              | 110                    | 140              | mA                                                                                                                                                                                                   | +85°C  | 5.5V  | operating at 1/2 speed     |  |

| DC26c              | 108                    | 140              | mA                                                                                                                                                                                                   | +125°C |       | (PTCON2 = 0x0001)          |  |

#### TABLE 24-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**2:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU executing while (1) statement

- JTAG disabled

- **3:** These parameters are characterized but not tested in manufacturing.

| DC CHARACTERI                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |               |       | °C for Industrial |      |         |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|-------|-------------------|------|---------|

| Parameter No. Typical <sup>(1)</sup> Max |                                                                                                                                                                                                                                                                                         |     | Doze<br>Ratio | Units | Conditions        |      |         |

| Doze Current (IDO                        | ze) <sup>(2)</sup>                                                                                                                                                                                                                                                                      |     | ·             |       |                   |      |         |

| DC73a                                    | 75                                                                                                                                                                                                                                                                                      | 105 | 1:2           | mA    |                   |      |         |

| DC73f                                    | 60                                                                                                                                                                                                                                                                                      | 105 | 1:64          | mA    | -40°C             | 3.3V | 40 MIPS |

| DC73g                                    | 60                                                                                                                                                                                                                                                                                      | 105 | 1:128         | mA    |                   |      |         |

| DC70a                                    | 75                                                                                                                                                                                                                                                                                      | 105 | 1:2           | mA    |                   |      |         |

| DC70f                                    | 60                                                                                                                                                                                                                                                                                      | 105 | 1:64          | mA    | +25°C             | 3.3V | 40 MIPS |

| DC70g                                    | 60                                                                                                                                                                                                                                                                                      | 105 | 1:128         | mA    |                   |      |         |

| DC71a                                    | 75                                                                                                                                                                                                                                                                                      | 105 | 1:2           | mA    |                   |      |         |

| DC71f                                    | 60                                                                                                                                                                                                                                                                                      | 105 | 1:64          | mA    | +85°C             | 3.3V | 40 MIPS |

| DC71g                                    | 60                                                                                                                                                                                                                                                                                      | 105 | 1:128         | mA    | 1                 |      |         |

| DC72a                                    | 75                                                                                                                                                                                                                                                                                      | 105 | 1:2           | mA    |                   | İ    |         |

| DC72f                                    | 60                                                                                                                                                                                                                                                                                      | 105 | 1:64          | mA    | +125°C            | 3.3V | 40 MIPS |

| DC72g                                    | 60                                                                                                                                                                                                                                                                                      | 105 | 1:128         | mA    | 1                 |      |         |

#### TABLE 24-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

Note 1: Data in the Typical column is at 3.3V, +25°C unless otherwise stated.

**2:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU executing while(1) statement

- JTAG disabled

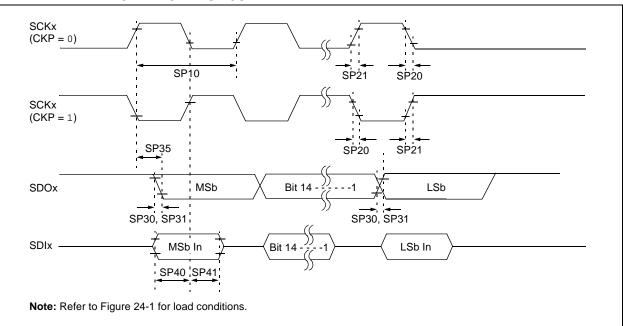

#### FIGURE 24-14: SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 24-33:SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS