Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10b; D/A 4x10b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

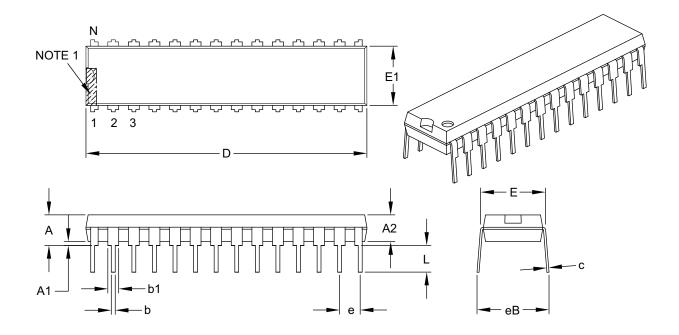

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gs504t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

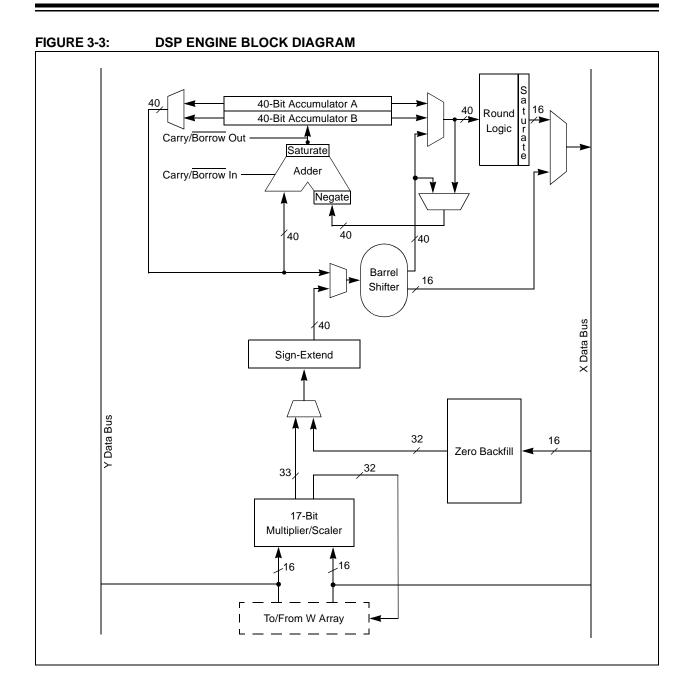

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value that is sign-extended to 40 bits. Integer data is inherently represented as a signed 2's complement value, where the Most Significant bit (MSb) is defined as a sign bit. The range of an N-bit 2's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ .

- For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0.

- For a 32-bit integer, the data range is

-2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a 2's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit 2's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product that has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiply operations.

The MUL instruction can be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

# 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled using the barrel shifter prior to accumulation.

# 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side, and either true or complement data into the other input.

- In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented).

- In the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented.

The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS Register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits, 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block that controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described previously and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS Register bits support saturation and overflow:

- OA: ACCA overflowed into guard bits

- · OB: ACCB overflowed into guard bits

- SA: ACCA saturated (bit 31 overflow and saturation) or

~

or

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation)

• SB: ACCB saturated (bit 31 overflow and saturation)

ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- OAB: Logical OR of OA and OB

- SAB: Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register are set (refer to **Section 7.0 "Interrupt Controller"**). This allows the user application to take immediate action, for example, to correct system gain.

# 4.4 Modulo Addressing

Modulo Addressing mode is a method used to provide an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.4.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that will operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled.

- If YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

MOV #0x1100, W0 Byte MOV W0, XMODSRT ;set modulo start address Address #0x1163, W0 MOV W0, MODEND MOV ;set modulo end address 0x1100 MOV #0x8001, W0 MOV W0, MODCON ;enable W1, X AGU for modulo MOV #0x0000, W0 ;W0 holds buffer fill value MOV #0x1110, W1 ;point W1 to buffer 0x1163 DO AGAIN, #0x31 ;fill the 50 buffer locations MOV WO, [W1++] ;fill the next location AGAIN: INC W0, W0 ; increment the fill value Start Addr = 0x1100End Addr = 0x1163Length = 0x0032 words

FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70192) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: Software RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), which is set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

## FIGURE 6-1: **RESET SYSTEM BLOCK DIAGRAM RESET** Instruction Glitch Filter MCLR WDT Module Sleep or Idle BOR Internal SYSRST Regulator Vdd POR VDD Rise Detect Trap Conflict Illegal Opcode Uninitialized W Register Configuration Mismatch

# 6.3 External Reset (EXTR)

The External Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to **Section 24.0** "**Electrical Characteristics**" for minimum pulse width specifications. The External Reset (MCLR) pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

#### 6.3.0.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate Reset signals to reset multiple devices in the system. This External Reset signal can be directly connected to the MCLR pin to reset the device when the rest of the system is reset.

### 6.3.0.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to reset the device, the External Reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The External Reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

### 6.4 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will remain. SYSRST is released at the next instruction cycle and the Reset vector fetch will commence.

The Software Reset (SWR) flag (instruction) in the Reset Control (RCON<6>) register is set to indicate the Software Reset.

# 6.5 Watchdog Timer Time-out Reset (WDTO)

Whenever a Watchdog time-out occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out (WDTO) flag in the Reset Control (RCON<4>) register is set to indicate the Watchdog Timer Reset. Refer to **Section 21.4 "Watchdog Timer (WDT)"** for more information on the Watchdog Timer Reset.

# 6.6 Trap Conflict Reset

If a lower priority hard trap occurs while a higher priority trap is being processed, a hard Trap Conflict Reset occurs. The hard traps include exceptions of Priority Levels 13 through 15, inclusive. The address error (Level 13) and oscillator error (Level 14) traps fall into this category.

The Trap Reset (TRAPR) flag in the Reset Control (RCON<15>) register is set to indicate the Trap Conflict Reset. Refer to **Section 7.0 "Interrupt Controller"** for more information on Trap Conflict Resets.

# 6.7 Configuration Mismatch Reset

To maintain the integrity of the Peripheral Pin Select Control registers, they are constantly monitored with shadow registers in hardware. If an unexpected change in any of the registers occur (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset occurs.

The Configuration Mismatch (CM) flag in the Reset Control (RCON<9>) register is set to indicate the Configuration Mismatch Reset. Refer to **Section 10.0 "I/O Ports"** for more information on the Configuration Mismatch Reset.

| Note: | The    | Configuration      | Mismatch     | Reset   |

|-------|--------|--------------------|--------------|---------|

|       | featu  | re and associate   | d Reset flag | are not |

|       | availa | able on all device | es.          |         |

# 6.8 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

The Illegal Opcode or Uninitialized W Access Reset (IOPUWR) flag in the Reset Control (RCON<14>) register is set to indicate the illegal condition device Reset.

### 6.8.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The Illegal Opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the Illegal Opcode Reset, use only the lower 16 bits of each program memory section to store the data values. The upper 8 bits should be programmed with 3Fh, which is an illegal opcode value.

| R/W-0           | R/W-0         | U-0              | U-0           | U-0                                     | U-0              | U-0      | U-0   |

|-----------------|---------------|------------------|---------------|-----------------------------------------|------------------|----------|-------|

| PWM2IF          | PWM1IF        | —                | _             | _                                       | —                | _        | _     |

| bit 15          |               |                  |               |                                         |                  |          | bit 8 |

|                 |               |                  |               |                                         |                  |          |       |

| U-0             | U-0           | U-0              | U-0           | U-0                                     | U-0              | U-0      | U-0   |

| —               | —             | —                | —             | —                                       | —                | —        | —     |

| bit 7           |               |                  |               |                                         |                  |          | bit 0 |

|                 |               |                  |               |                                         |                  |          |       |

| Legend:         |               |                  |               |                                         |                  |          |       |

| R = Readable    | bit           | W = Writable I   | bit           | U = Unimpler                            | mented bit, read | l as '0' |       |

| -n = Value at F | POR           | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknown |                  |          | own   |

|                 |               |                  |               |                                         |                  |          |       |

| bit 15          | PWM2IF: PW    | M2 Interrupt FI  | ag Status bit |                                         |                  |          |       |

|                 | •             | request has occ  |               |                                         |                  |          |       |

|                 | 0 = Interrupt | request has not  | occurred      |                                         |                  |          |       |

| bit 14          | PWM1IF: PV    | VM1 Interrupt FI | ag Status bit |                                         |                  |          |       |

|                 |               | request has occ  |               |                                         |                  |          |       |

|                 | 0 = Interrupt | request has not  | occurred      |                                         |                  |          |       |

| bit 13-0        | Unimplemer    | nted: Read as '0 | כ'            |                                         |                  |          |       |

|                 |               |                  |               |                                         |                  |          |       |

### REGISTER 7-9: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0           | U-0             | U-0                              | U-0            | U-0              | U-0              | U-0             | U-0     |

|---------------|-----------------|----------------------------------|----------------|------------------|------------------|-----------------|---------|

| 0-0           | 0-0             | 0-0                              | 0-0            | 0-0              | 0-0              | 0-0             | 0-0     |

|               |                 |                                  |                |                  |                  |                 |         |

| bit 15        |                 |                                  |                |                  |                  |                 | bit 8   |

|               |                 |                                  |                | -                | <b>D</b> 444 a   | <b>D A A A</b>  | -       |

| U-0           | U-0             | U-0                              | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|               |                 |                                  | ADCP6IF        | ADCP5IF          | ADCP4IF          | ADCP3IF         | ADCP2IF |

| bit 7         |                 |                                  |                |                  |                  |                 | bit (   |

|               |                 |                                  |                |                  |                  |                 |         |

| Legend:       |                 |                                  |                |                  |                  |                 |         |

| R = Readable  | e bit           | W = Writable                     | bit            | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                 |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|               |                 |                                  |                |                  |                  |                 |         |

| bit 15-5      | Unimplemen      | ted: Read as '                   | 0'             |                  |                  |                 |         |

| bit 4         | ADCP6IF: AD     | DC Pair 6 Conv                   | ersion Done li | nterrupt Flag S  | tatus bit        |                 |         |

|               | 1 = Interrupt r | equest has oc                    | curred         |                  |                  |                 |         |

|               | 0 = Interrupt r | equest has not                   | occurred       |                  |                  |                 |         |

| bit 3         | ADCP5IF: AD     | DC Pair 5 Conv                   | ersion Done I  | nterrupt Flag S  | tatus bit        |                 |         |

|               |                 | equest has oc                    |                |                  |                  |                 |         |

|               | 0 = Interrupt r | equest has not                   | occurred       |                  |                  |                 |         |

| bit 2         |                 | DC Pair 4 Conv                   |                | nterrupt Flag S  | tatus bit        |                 |         |

|               |                 | equest has oc                    |                |                  |                  |                 |         |

|               | •               | equest has not                   |                |                  |                  |                 |         |

| bit 1         |                 | DC Pair 3 Conv                   |                | nterrupt Flag S  | tatus bit        |                 |         |

|               |                 | equest has oc                    |                |                  |                  |                 |         |

| h:1.0         | •               | equest has not                   |                |                  | 4 - 4            |                 |         |

| bit 0         |                 | C Pair 2 Conv                    |                | nterrupt Flag S  | tatus bit        |                 |         |

|               |                 | equest has oco<br>equest has not |                |                  |                  |                 |         |

|               |                 | equest has no                    | occurreu       |                  |                  |                 |         |

#### REGISTER 7-11: IFS7: INTERRUPT FLAG STATUS REGISTER 7

| R/W-0           | R/W-0        | U-0                                | U-0            | U-0               | U-0             | R/W-0           | R/W-0  |

|-----------------|--------------|------------------------------------|----------------|-------------------|-----------------|-----------------|--------|

| ADCP1IE         | ADCP0IE      | —                                  | —              | —                 | _               | AC4IE           | AC3IE  |

| bit 15          |              |                                    |                |                   |                 |                 | bit    |

| R/W-0           | U-0          | U-0                                | U-0            | U-0               | U-0             | R/W-0           | R/W-0  |

| AC2IE           |              | _                                  | _              |                   | _               | PWM4IE          | PWM3IE |

| bit 7           |              |                                    |                |                   |                 |                 | bit (  |

| Legend:         |              |                                    |                |                   |                 |                 |        |

| R = Readable    | bit          | W = Writable                       | bit            | U = Unimplem      | nented bit. rea | d as '0'        |        |

| -n = Value at F | POR          | '1' = Bit is set                   |                | '0' = Bit is clea |                 | x = Bit is unkr | iown   |

|                 |              |                                    |                |                   |                 |                 |        |

| bit 15          | ADCP1IE: AD  | DC Pair 1 Conv                     | ersion Done    | Interrupt Enable  | e bit           |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

|                 |              | request is not e                   |                |                   |                 |                 |        |

| bit 14          |              |                                    |                | Interrupt Enable  | bit             |                 |        |

|                 | •            | equest is enab<br>equest is not e  |                |                   |                 |                 |        |

| bit 13-10       | •            | ted: Read as '                     |                |                   |                 |                 |        |

| bit 9           | -            | g Comparator                       |                | able bit          |                 |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

|                 |              | equest is not e                    |                |                   |                 |                 |        |

| bit 8           | AC3IE: Analo | g Comparator                       | 3 Interrupt Er | nable bit         |                 |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

|                 |              | equest is not e                    |                |                   |                 |                 |        |

| bit 7           |              | g Comparator<br>equest is enat     | •              | hable bit         |                 |                 |        |

|                 |              | equest is enaction equest is not e |                |                   |                 |                 |        |

| bit 6-2         | •            | ted: Read as '                     |                |                   |                 |                 |        |

| bit 1           | -            | /M4 Interrupt E                    |                |                   |                 |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

|                 | •            | equest is not e                    |                |                   |                 |                 |        |

| bit 0           | PWM3IE: PW   | /M3 Interrupt E                    | nable bit      |                   |                 |                 |        |

|                 |              | equest is enab                     |                |                   |                 |                 |        |

# REGISTER 7-17: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

| REGISTER 8      | -2: CLKDI                                                    | V: CLOCK D               | IVISOR REC                           | SISTER <sup>(1)</sup>                 |                  |                    |              |

|-----------------|--------------------------------------------------------------|--------------------------|--------------------------------------|---------------------------------------|------------------|--------------------|--------------|

| R/W-0           | R/W-0                                                        | R/W-1                    | R/W-1                                | R/W-0                                 | R/W-0            | R/W-0              | R/W-0        |

| ROI             | DOZE2                                                        | DOZE1                    | DOZE0                                | DOZEN <sup>(2)</sup>                  | FRCDIV2          | FRCDIV1            | FRCDIVC      |

| bit 15          |                                                              |                          |                                      |                                       |                  |                    | bit          |

| R/W-0           | R/W-1                                                        | U-0                      | R/W-0                                | R/W-0                                 | R/W-0            | R/W-0              | R/W-0        |

| PLLPOST1        | PLLPOST0                                                     | _                        | PLLPRE4                              | PLLPRE3                               | PLLPRE2          | PLLPRE1            | PLLPRE       |

| bit 7           |                                                              |                          |                                      |                                       |                  |                    | bit          |

| Legend:         |                                                              |                          |                                      |                                       |                  |                    |              |

| R = Readable    | hit                                                          | W = Writable             | hit                                  |                                       | opted bit read   |                    |              |

|                 |                                                              |                          |                                      | -                                     | nented bit, read |                    |              |

| -n = Value at F | <u>'OR</u>                                                   | '1' = Bit is se          | [                                    | '0' = Bit is clea                     | ared             | x = Bit is unkr    | IOWN         |

| bit 15          | ROI: Recover                                                 | on Interrupt b           | it                                   |                                       |                  |                    |              |

|                 |                                                              | -                        |                                      | d the processo                        | r clock/periphe  | ral clock ratio is | s set to 1:1 |

|                 |                                                              |                          | t on the DOZE                        |                                       |                  |                    |              |

| bit 14-12       | DOZE<2:0>:                                                   | Processor Clo            | ck Reduction S                       | Select bits                           |                  |                    |              |

|                 | 111 = Fcy/12                                                 | 8                        |                                      |                                       |                  |                    |              |

|                 | 110 = FCY/64                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 101 = FCY/32                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 100 = FCY/16                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 011 = FCY/8 (<br>010 = FCY/4                                 | delault)                 |                                      |                                       |                  |                    |              |

|                 | 001 = FCY/2                                                  |                          |                                      |                                       |                  |                    |              |

|                 | 000 = Fcy/1                                                  |                          |                                      |                                       |                  |                    |              |

| bit 11          | DOZEN: Doze                                                  | e Mode Enable            | e bit <sup>(2)</sup>                 |                                       |                  |                    |              |

|                 |                                                              |                          | ies the ratio be<br>eral clock ratio |                                       | pheral clocks a  | and the process    | or clocks    |

| bit 10-8        | FRCDIV<2:0>                                                  | : Internal Fas           | t RC Oscillator                      | Postscaler bits                       | 6                |                    |              |

|                 | 111 = FRC di<br>110 = FRC di<br>101 = FRC di<br>100 = FRC di | vide-by-64<br>vide-by-32 |                                      |                                       |                  |                    |              |

|                 | 011 = FRC di                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 010 = FRC di                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 001 = FRC di                                                 | •                        |                                      |                                       |                  |                    |              |

| h# 7 C          | 000 = FRC di                                                 | <b>,</b> (               | ,                                    | Calaat hita (al                       |                  |                    | eeler)       |

| bit 7-6         |                                                              |                          | Output Divider                       | Select bits (all                      | so denoted as    | 'N2', PLL posts    | caler)       |

|                 | 11 = Output/8<br>10 = Reserve                                |                          |                                      |                                       |                  |                    |              |

|                 | 01 = Output/4                                                |                          |                                      |                                       |                  |                    |              |

|                 | 00 = Output/2                                                | •                        |                                      |                                       |                  |                    |              |

| bit 5           | Unimplement                                                  | t <b>ed:</b> Read as     | 0'                                   |                                       |                  |                    |              |

| bit 4-0         | PLLPRE<4:0                                                   | >: PLL Phase             | Detector Input                       | Divider bits (a                       | so denoted as    | 'N1', PLL prese    | caler)       |

|                 | 11111 <b>= I</b> npu                                         |                          |                                      | , , , , , , , , , , , , , , , , , , , |                  | · •                | ,            |

|                 | •                                                            |                          |                                      |                                       |                  |                    |              |

|                 | •                                                            |                          |                                      |                                       |                  |                    |              |

|                 | •                                                            | 10                       |                                      |                                       |                  |                    |              |

|                 | 00001 = Inpu                                                 |                          |                                      |                                       |                  |                    |              |

|                 | 00000 = Inpu                                                 | t/2 (default)            |                                      |                                       |                  |                    |              |

#### CIGTED 0 2

Note 1: This register is reset only on a Power-on Reset (POR).

2: This bit is cleared when the ROI bit is set and an interrupt occurs.

| U-0                | U-0                                                                                                                                                          | R/W-1                                                                                                                                                                                           | R/W-1                                                | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|------------------|-----------------|--------|

| —                  |                                                                                                                                                              | FLT7R5                                                                                                                                                                                          | FLT7R4                                               | FLT7R3            | FLT7R2           | FLT7R1          | FLT7R0 |

| oit 15             |                                                                                                                                                              |                                                                                                                                                                                                 |                                                      |                   |                  |                 | bit 8  |

| U-0                | U-0                                                                                                                                                          | R/W-1                                                                                                                                                                                           | R/W-1                                                | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

| _                  | _                                                                                                                                                            | FLT6R5                                                                                                                                                                                          | FLT6R4                                               | FLT6R3            | FLT6R2           | FLT6R1          | FLT6R0 |

| bit 7              |                                                                                                                                                              |                                                                                                                                                                                                 |                                                      |                   |                  |                 | bit (  |

| Legend:            |                                                                                                                                                              |                                                                                                                                                                                                 |                                                      |                   |                  |                 |        |

| R = Readab         | le bit                                                                                                                                                       | W = Writable                                                                                                                                                                                    | bit                                                  | U = Unimplen      | nented bit, read | l as '0'        |        |

| -n = Value a       | t POR                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                                |                                                      | '0' = Bit is clea |                  | x = Bit is unkr | nown   |

|                    |                                                                                                                                                              |                                                                                                                                                                                                 | - 1                                                  |                   |                  |                 |        |

| bit 15-14          | Unimplement                                                                                                                                                  |                                                                                                                                                                                                 |                                                      |                   |                  |                 |        |

| bit 13-8           | FLT7R<5:0>:                                                                                                                                                  | Assign PWM                                                                                                                                                                                      | Fault Input 7 (                                      | FLT7) to the Co   | orresponding R   | Pn Pin bits     |        |

|                    | 1111111 = Inn                                                                                                                                                | ut tied to Vss                                                                                                                                                                                  |                                                      |                   |                  |                 |        |

|                    |                                                                                                                                                              |                                                                                                                                                                                                 |                                                      |                   |                  |                 |        |

|                    | 100011 <b>= Inp</b>                                                                                                                                          | ut tied to RP3                                                                                                                                                                                  |                                                      |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp                                                                                                                                 | ut tied to RP3<br>ut tied to RP34                                                                                                                                                               | 1                                                    |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3                                                                                                                                              | 4<br>3                                               |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp                                                                                                                                 | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3                                                                                                                                              | 4<br>3                                               |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3                                                                                                                                              | 4<br>3                                               |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3                                                                                                                                              | 4<br>3                                               |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                 | ut tied to RP34<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                        | 4<br>3                                               |                   |                  |                 |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp                                                                                                                 | ut tied to RP34<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32                                                                                                                        | 4<br>3                                               |                   |                  |                 |        |

| bit 7-6            | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp                                                                                                 | ut tied to RP35<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0                                                                                                       | 4<br>3<br>2                                          |                   |                  |                 |        |

| bit 7-6<br>bit 5-0 | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>00000 = Input<br>Unimplement                                                                  | ut tied to RP35<br>ut tied to RP32<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br>ted: Read as '                                                                                     | 4<br>3<br>2<br>0'                                    | FLT6) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | ut tied to RP34<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM                                                                | 4<br>3<br>2<br>0'                                    | FLT6) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>00000 = Input<br>Unimplement                                                                  | ut tied to RP34<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss                                            | 4<br>3<br>2<br>0'<br>Fault Input 6 (i                | FLT6) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | ut tied to RP34<br>ut tied to RP34<br>ut tied to RP33<br>ut tied to RP32<br>t tied to RP0<br><b>ted:</b> Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP35                         | 4<br>3<br>2<br>0'<br>Fault Input 6 (1                | FLT6) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Input<br>00000 = Input<br>Unimplement<br>FLT6R<5:0>:<br>11111 = Inp<br>100011 = Inp<br>100010 = Inp  | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>t tied to RP0<br>ted: Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3 | 4<br>3<br>2<br>0'<br>Fault Input 6 (1<br>5<br>4<br>3 | FLT6) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100001 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•  | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>t tied to RP0<br>ted: Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3 | 4<br>3<br>2<br>0'<br>Fault Input 6 (1<br>5<br>4<br>3 | FLT6) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Input<br>00000 = Input<br>Unimplement<br>FLT6R<5:0>:<br>11111 = Inp<br>100011 = Inp<br>100010 = Inp  | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>t tied to RP0<br>ted: Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3 | 4<br>3<br>2<br>0'<br>Fault Input 6 (1<br>5<br>4<br>3 | FLT6) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Input<br>00000 = Input<br>Unimplement<br>FLT6R<5:0>:<br>11111 = Inp<br>100011 = Inp<br>100010 = Inp  | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>t tied to RP0<br>ted: Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3 | 4<br>3<br>2<br>0'<br>Fault Input 6 (1<br>5<br>4<br>3 | FLT6) to the Co   | prresponding R   | Pn Pin bits     |        |

|                    | 100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Input<br>00000 = Input<br>Unimplement<br>FLT6R<5:0>:<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp | ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3<br>t tied to RP0<br>ted: Read as '<br>Assign PWM I<br>ut tied to Vss<br>ut tied to RP3<br>ut tied to RP3<br>ut tied to RP3 | 4<br>3<br>2<br>0'<br>Fault Input 6 (1<br>5<br>4<br>3 | FLT6) to the Co   | orresponding R   | Pn Pin bits     |        |

### REGISTER 10-12: RPINR32: PERIPHERAL PIN SELECT INPUT REGISTER 32

| R/W-0              | U-0                              | R/W-0                                    | U-0                   | U-0                          | U-0             | U-0                | U-0   |

|--------------------|----------------------------------|------------------------------------------|-----------------------|------------------------------|-----------------|--------------------|-------|

| TON <sup>(2)</sup> | _                                | TSIDL <sup>(1)</sup>                     |                       | _                            | _               | —                  | _     |

| bit 15             |                                  |                                          |                       |                              |                 |                    | bit 8 |

| U-0                | R/W-0                            | R/W-0                                    | R/W-0                 | U-0                          | U-0             | R/W-0              | U-0   |

|                    | TGATE <sup>(2)</sup>             | TCKPS1 <sup>(2)</sup>                    | TCKPS0 <sup>(2)</sup> | _                            |                 | TCS <sup>(2)</sup> |       |

| bit 7              |                                  |                                          |                       |                              |                 |                    | bit ( |

| Legend:            |                                  |                                          |                       |                              |                 |                    |       |

| R = Readabl        | e bit                            | W = Writable                             | bit                   | U = Unimplem                 | nented bit, rea | d as '0'           |       |

| -n = Value at      | POR                              | '1' = Bit is set                         |                       | '0' = Bit is clea            | ared            | x = Bit is unkn    | own   |

|                    |                                  |                                          |                       |                              |                 |                    |       |

| bit 15             | TON: Timery                      |                                          |                       |                              |                 |                    |       |

|                    | 1 = Starts 16-                   |                                          |                       |                              |                 |                    |       |

|                    | 0 = Stops 16-                    | -                                        |                       |                              |                 |                    |       |

| bit 14             | -                                | ted: Read as '                           |                       |                              |                 |                    |       |

| bit 13             |                                  | ry Stop in Idle N                        |                       |                              |                 |                    |       |

|                    |                                  | ues timer operation<br>s timer operation |                       | vice enters Idle             | mode            |                    |       |

| bit 12-7           |                                  | ited: Read as '                          |                       |                              |                 |                    |       |

| bit 6              | TGATE: Time                      | ery Gated Time                           | Accumulation          | n Enable bit <sup>(2)</sup>  |                 |                    |       |

|                    | When TCS =                       |                                          |                       |                              |                 |                    |       |

|                    | This bit is ign                  |                                          |                       |                              |                 |                    |       |

|                    | When TCS =                       |                                          |                       |                              |                 |                    |       |

|                    |                                  | ne accumulation<br>ne accumulation       |                       |                              |                 |                    |       |

| bit 5-4            |                                  | : Timery Input                           |                       | e Select bits <sup>(2)</sup> |                 |                    |       |

|                    | 11 = 1:256 pr                    |                                          |                       |                              |                 |                    |       |

|                    | 10 = 1:64 pre                    |                                          |                       |                              |                 |                    |       |

|                    | 01 = 1:8 pres                    |                                          |                       |                              |                 |                    |       |

|                    | 00 = 1:1 pres                    |                                          |                       |                              |                 |                    |       |

| bit 3-2            | -                                | ted: Read as '                           |                       |                              |                 |                    |       |

| bit 1              |                                  | Clock Source S                           |                       |                              |                 |                    |       |

|                    | 1 = External o<br>0 = Internal c | clock from TxC<br>lock (Fosc/2)          | K pin                 |                              |                 |                    |       |

|                    |                                  |                                          |                       |                              |                 |                    |       |

# REGISTER 12-2: TyCON: TIMERY CONTROL REGISTER (y = 3)

bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timerx Control (TxCON<3>) register, these

**2:** When the 32-bit timer operation is enabled (T32 = 1) in the Timerx Control (TxCON<3>) register, these bits have no effect.

#### REGISTER 15-14: IOCONx: PWMx I/O CONTROL REGISTER (CONTINUED)

| bit 3-2 | CLDAT<1:0>: State for PWMxH and PWMxL Pins if CLMODE is Enabled bits <sup>(2)</sup>                          |

|---------|--------------------------------------------------------------------------------------------------------------|

|         | FCLCONx <ifltmod> = 0: Normal Fault mode:</ifltmod>                                                          |

|         | If current-limit is active, then CLDAT<1> provides the state for PWMxH                                       |

|         | If current-limit is active, then CLDAT<0> provides the state for PWMxL                                       |

|         | FCLCONx <ifltmod> = 1: Independent Fault mode:</ifltmod>                                                     |

|         | CLDAT<1:0> bits are ignored.                                                                                 |

| bit 1   | SWAP<1:0>: Swap PWMxH and PWMxL pins                                                                         |

|         | 1 = PWMxH output signal is connected to the PWMxL pin and the PWMxL signal is connected to the<br>PWMxH pins |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                 |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                   |

|         | 1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWM time base                          |

|         | 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary                           |

| Note 1: | These bits should be changed only when PTEN = 0. Changing the clock selection during operation will          |

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 2: The state represents the active/inactive state of the PWM module depending on the POLH and POLL bit settings.

# **REGISTER 19-3:** ADBASE: ANALOG-TO-DIGITAL BASE REGISTER<sup>(1,2)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|------------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | ADBAS      | SE<15:8>          |                 |                 |       |

| bit 15          |       |                  |            |                   |                 |                 | bit 8 |

|                 |       |                  |            |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0      | R/W-0             | R/W-0           | R/W-0           | U-0   |

|                 |       | /                | ADBASE<7:1 | >                 |                 |                 | —     |

| bit 7           |       |                  |            |                   |                 |                 | bit 0 |

|                 |       |                  |            |                   |                 |                 |       |

| Legend:         |       |                  |            |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit        | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |            | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

#### bit 15-1 ADBASE<15:1>: Analog-to-Digital Base bits

This register contains the base address of the user's ADC Interrupt Service Routine jump table. This register, when read, contains the sum of the ADBASE register contents and the encoded value of the PxRDY status bits.

The encoder logic provides the bit number of the highest priority PxRDY bits, where P0RDY is the highest priority and P6RDY is the lowest priority.

#### bit 0 Unimplemented: Read as '0'

- Note 1: The encoding results are shifted left two bits, so bits 1-0 of the result are always zero.

- **2:** As an alternative to using the ADBASE register, the ADCP0-6 ADC Pair Conversion Complete interrupts can be used to invoke A to D conversion completion routines for individual ADC input pairs.

#### **REGISTER 19-4:** ADPCFG: ANALOG-TO-DIGITAL PORT CONFIGURATION REGISTER

| U-0    | U-0   | U-0   | U-0   | R/W-0                | R/W-0 | R/W-0                | R/W-0 |

|--------|-------|-------|-------|----------------------|-------|----------------------|-------|

| —      | —     | —     | —     |                      | PCFG< | 11:8> <sup>(1)</sup> |       |

| bit 15 |       |       |       |                      |       |                      | bit 8 |

|        |       |       |       |                      |       |                      |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0                | R/W-0 |

|        |       |       | PCFG  | <7:0> <sup>(1)</sup> |       |                      |       |

| bit 7  |       |       |       |                      |       |                      | bit 0 |

|        |       |       |       |                      |       |                      |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 PCFG<11:0>: Analog-to-Digital Port Configuration Control bits<sup>(1)</sup>

1 = Port pin in Digital mode; port read input is enabled, Analog-to-Digital input multiplexer is connected to AVss

0 = Port pin in Analog mode; port read input is disabled, Analog-to-Digital samples the pin voltage

**Note 1:** Not all PCFGx bits are available on all devices. See Figure 19-1 through Figure 19-6 for the available analog pins (PCFGx = ANx, where x = 0-11).

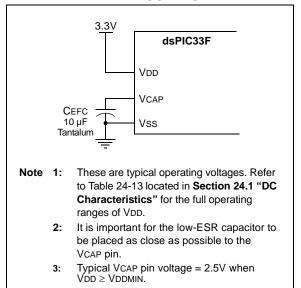

# 21.2 On-Chip Voltage Regulator

The dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 families incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 21-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 24-13 located in **Section 24.1 "DC Characteristics"**.

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 21-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### 21.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

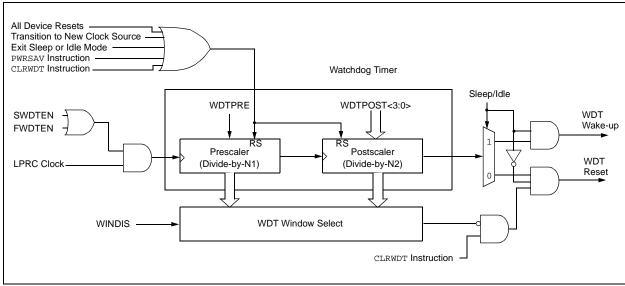

# 21.4 Watchdog Timer (WDT)

For the dsPIC33FJ06GS101/X02 and dsPIC33FJ16GSX02/X04 devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 21.4.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC<2:0> bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### FIGURE 21-2: WDT BLOCK DIAGRAM

#### 21.4.2 SLEEP AND IDLE MODES

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP bit (RCON<3>) or IDLE bit (RCON<2>) will need to be cleared in software after the device wakes up.

#### 21.4.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

### 23.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.