Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2 014110                   |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                              |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | LED, POR, Voltage Detect, WDT                                                    |

| Number of I/O              | 13                                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.5V                                                                      |

| Data Converters            | A/D 4x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                  |

| Supplier Device Package    | 20-LSSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f21284sdsp-w4 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2. Central Processing Unit (CPU)

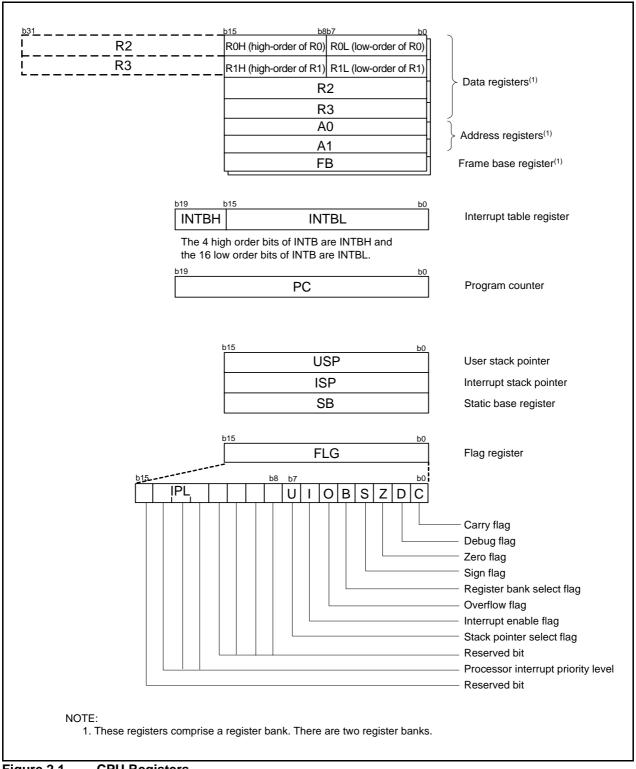

Figure 2.1 shows the CPU Registers. The CPU contains 13 registers. R0, R1, R2, R3, A0, A1, and FB configure a register bank. There are two sets of register bank.

### 2.1 Data Registers (R0, R1, R2, and R3)

R0 is a 16-bit register for transfer, arithmetic, and logic operations. The same applies to R1 to R3. R0 can be split into high-order bits (R0H) and low-order bits (R0L) to be used separately as 8-bit data registers. R1H and R1L are analogous to R0H and R0L. R2 can be combined with R0 and used as a 32-bit data register (R2R0). R3R1 is analogous to R2R0.

### 2.2 Address Registers (A0 and A1)

A0 is a 16-bit register for address register indirect addressing and address register relative addressing. It is also used for transfer, arithmetic, and logic operations. A1 is analogous to A0. A1 can be combined with A0 and as a 32-bit address register (A1A0).

### 2.3 Frame Base Register (FB)

FB is a 16-bit register for FB relative addressing.

### 2.4 Interrupt Table Register (INTB)

INTB is a 20-bit register that indicates the start address of an interrupt vector table.

## 2.5 Program Counter (PC)

PC is 20 bits wide and indicates the address of the next instruction to be executed.

## 2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

The stack pointers (SP), USP, and ISP, are each 16 bits wide. The U flag of FLG is used to switch between USP and ISP.

### 2.7 Static Base Register (SB)

SB is a 16-bit register for SB relative addressing.

### 2.8 Flag Register (FLG)

FLG is an 11-bit register indicating the CPU state.

## 2.8.1 Carry Flag (C)

The C flag retains carry, borrow, or shift-out bits that have been generated by the arithmetic and logic unit.

## 2.8.2 Debug Flag (D)

The D flag is for debugging only. Set it to 0.

## 2.8.3 Zero Flag (Z)

The Z flag is set to 1 when an arithmetic operation results in 0; otherwise to 0.

## 2.8.4 Sign Flag (S)

The S flag is set to 1 when an arithmetic operation results in a negative value; otherwise to 0.

## 2.8.5 Register Bank Select Flag (B)

Register bank 0 is selected when the B flag is 0. Register bank 1 is selected when this flag is set to 1.

### 2.8.6 Overflow Flag (O)

The O flag is set to 1 when an operation results in an overflow; otherwise to 0.

| Address | Register                                                                                                                                             | Symbol                         | After reset     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|

| 0080h   |                                                                                                                                                      |                                |                 |

| 0081h   |                                                                                                                                                      |                                |                 |

| 0082h   |                                                                                                                                                      |                                |                 |

| 0083h   |                                                                                                                                                      |                                |                 |

| 0084h   |                                                                                                                                                      |                                |                 |

| 0085h   |                                                                                                                                                      |                                |                 |

| 0086h   |                                                                                                                                                      |                                |                 |

| 0087h   |                                                                                                                                                      |                                |                 |

| 0088h   |                                                                                                                                                      |                                |                 |

| 0089h   |                                                                                                                                                      |                                |                 |

| 0089h   |                                                                                                                                                      |                                |                 |

|         |                                                                                                                                                      |                                |                 |

| 008Bh   |                                                                                                                                                      |                                |                 |

| 008Ch   |                                                                                                                                                      |                                |                 |

| 008Dh   |                                                                                                                                                      |                                |                 |

| 008Eh   |                                                                                                                                                      |                                |                 |

| 008Fh   |                                                                                                                                                      |                                |                 |

| 0090h   |                                                                                                                                                      |                                |                 |

| 0091h   |                                                                                                                                                      |                                |                 |

| 0092h   |                                                                                                                                                      |                                |                 |

| 0093h   |                                                                                                                                                      |                                |                 |

| 0094h   |                                                                                                                                                      |                                |                 |

| 0095h   |                                                                                                                                                      |                                |                 |

| 0096h   |                                                                                                                                                      |                                | 1               |

| 0097h   |                                                                                                                                                      |                                |                 |

| 0098h   |                                                                                                                                                      |                                |                 |

| 0090h   |                                                                                                                                                      |                                | +               |

| 0099h   |                                                                                                                                                      |                                |                 |

| 009An   |                                                                                                                                                      |                                |                 |

|         |                                                                                                                                                      |                                |                 |

| 009Ch   |                                                                                                                                                      |                                |                 |

| 009Dh   |                                                                                                                                                      |                                |                 |

| 009Eh   |                                                                                                                                                      |                                |                 |

| 009Fh   |                                                                                                                                                      |                                |                 |

| 00A0h   | UART0 Transmit/Receive Mode Register                                                                                                                 | U0MR                           | 00h             |

| 00A1h   | UART0 Bit Rate Register                                                                                                                              | U0BRG                          | XXh             |

| 00A2h   | UART0 Transmit Buffer Register                                                                                                                       | U0TB                           | XXh             |

| 00A3h   |                                                                                                                                                      |                                | XXh             |

| 00A4h   | UART0 Transmit/Receive Control Register 0                                                                                                            | U0C0                           | 00001000b       |

| 00A5h   | UART0 Transmit/Receive Control Register 1                                                                                                            | U0C1                           | 00000010b       |

| 00A6h   | UART0 Receive Buffer Register                                                                                                                        | UORB                           | XXh             |

| 00A7h   |                                                                                                                                                      | 00112                          | XXh             |

| 00A8h   | UART1 Transmit/Receive Mode Register                                                                                                                 | U1MR                           | 00h             |

| 00A8h   | UART1 Bit Rate Register                                                                                                                              | U1BRG                          | XXh             |

|         |                                                                                                                                                      |                                |                 |

| 00AAh   | UART1 Transmit Buffer Register                                                                                                                       | U1TB                           | XXh             |

| 00ABh   |                                                                                                                                                      |                                | XXh             |

| 00ACh   | UART1 Transmit/Receive Control Register 0                                                                                                            | U1C0                           | 00001000b       |

| 00ADh   | UART1 Transmit/Receive Control Register 1                                                                                                            | U1C1                           | 00000010b       |

| 00AEh   | UART1 Receive Buffer Register                                                                                                                        | U1RB                           | XXh             |

| 00AFh   |                                                                                                                                                      |                                | XXh             |

| 00B0h   |                                                                                                                                                      |                                |                 |

| 00B1h   |                                                                                                                                                      |                                |                 |

| 00B2h   |                                                                                                                                                      |                                |                 |

| 00B3h   |                                                                                                                                                      |                                |                 |

| 00B4h   |                                                                                                                                                      |                                |                 |

| 00B5h   |                                                                                                                                                      |                                |                 |

| 00B6h   |                                                                                                                                                      |                                |                 |

| 00B0h   |                                                                                                                                                      |                                | +               |

| 00B7h   | SS Control Deviator II / IIC hus Control Deviator 4 <sup>(2)</sup>                                                                                   | SSCRH / ICCR1                  | 00h             |

|         | SS Control Register H / IIC bus Control Register 1 <sup>(2)</sup>                                                                                    |                                |                 |

| 00B9h   | SS Control Register L / IIC bus Control Register 2 <sup>(2)</sup>                                                                                    | SSCRL / ICCR2                  | 01111101b       |

| 00BAh   | SS Mode Register / IIC bus Mode Register <sup>(2)</sup>                                                                                              | SSMR / ICMR                    | 00011000b       |

| 00BBh   | SS Enable Register / IIC bus Interrupt Enable Register <sup>(2)</sup>                                                                                | SSER / ICIER                   | 00h             |

| 00BCh   | SS Status Register / IIC bus Status Register <sup>(2)</sup>                                                                                          | SSSR / ICSR                    | 00h / 0000X000b |

| 00BDh   | SS Mode Register 2 / Slave Address Register <sup>(2)</sup>                                                                                           | SSMR2 / SAR                    | 00h             |

| 00BDh   |                                                                                                                                                      | SSIMR2 / SAR                   | FFh             |

| 00BEh   | SS Transmit Data Register / IIC bus Transmit Data Register <sup>(2)</sup><br>SS Receive Data Register / IIC bus Receive Data Register <sup>(2)</sup> | SSTDR / ICDRT<br>SSRDR / ICDRR |                 |

|         |                                                                                                                                                      |                                | FFh             |

### SFR Information (3)<sup>(1)</sup> Table 4.3

NOTES:

1. The blank regions are reserved. Do not access locations in these regions.

2. Selected by the IICSEL bit in the PMR register.

| Address          | Deviator                                                | Cumhal          |             |

|------------------|---------------------------------------------------------|-----------------|-------------|

| Address<br>0100h | Register                                                | Symbol<br>TRACR | After reset |

| 0100h            | Timer RA Control Register Timer RA I/O Control Register | TRAIOC          | 00h<br>00h  |

|                  |                                                         |                 | 00h         |

| 0102h            | Timer RA Mode Register                                  | TRAMR<br>TRAPRE | FFh         |

| 0103h            | Timer RA Prescaler Register                             |                 | FFh         |

| 0104h            | Timer RA Register                                       | TRA             | FFN         |

| 0105h            | LIN Control Devictor                                    |                 | 0.01        |

| 0106h            | LIN Control Register                                    | LINCR           | 00h         |

| 0107h            | LIN Status Register                                     | LINST           | 00h         |

| 0108h            | Timer RB Control Register                               | TRBCR           | 00h         |

| 0109h            | Timer RB One-Shot Control Register                      | TRBOCR          | 00h         |

| 010Ah            | Timer RB I/O Control Register                           | TRBIOC          | 00h         |

| 010Bh            | Timer RB Mode Register                                  | TRBMR           | 00h         |

| 010Ch            | Timer RB Prescaler Register                             | TRBPRE          | FFh         |

| 010Dh            | Timer RB Secondary Register                             | TRBSC           | FFh         |

| 010Eh            | Timer RB Primary Register                               | TRBPR           | FFh         |

| 010Fh            |                                                         |                 |             |

| 0110h            |                                                         |                 |             |

| 0111h            |                                                         |                 |             |

| 0112h            |                                                         |                 | -           |

| 0113h            |                                                         |                 |             |

| 0114h            |                                                         |                 |             |

| 0115h            |                                                         |                 |             |

| 0116h            |                                                         |                 |             |

| 0117h            |                                                         |                 |             |

| 0118h            | Timer RE Second Data Register / Counter Data Register   | TRESEC          | 00h         |

| 0119h            | Timer RE Minute Data Register / Compare Data Register   | TREMIN          | 00h         |

| 011Ah            | Timer RE Hour Data Register <sup>(2)</sup>              | TREHR           | 00h         |

| 011Bh            | Timer RE Day of Week Data Register <sup>(2)</sup>       | TREWK           | 00h         |

| 011Ch            | Timer RE Control Register 1                             | TRECR1          | 00h         |

| 011Dh            | Timer RE Control Register 2                             | TRECR2          | 00h         |

| 011Eh            | Timer RE Count Source Select Register                   | TRECSR          | 00001000b   |

| 011Fh            |                                                         |                 |             |

| 0120h            | Timer RC Mode Register                                  | TRCMR           | 01001000b   |

| 0121h            | Timer RC Control Register 1                             | TRCCR1          | 00h         |

| 0122h            | Timer RC Interrupt Enable Register                      | TRCIER          | 01110000b   |

| 0123h            | Timer RC Status Register                                | TRCSR           | 01110000b   |

| 0124h            | Timer RC I/O Control Register 0                         | TRCIOR0         | 10001000b   |

| 0125h            | Timer RC I/O Control Register 1                         | TRCIOR1         | 10001000b   |

| 0126h            | Timer RC Counter                                        | TRC             | 00h         |

| 0127h            |                                                         |                 | 00h         |

| 0128h            | Timer RC General Register A                             | TRCGRA          | FFh         |

| 0129h            |                                                         |                 | FFh         |

| 012Ah            | Timer RC General Register B                             | TRCGRB          | FFh         |

| 012Bh            | 1                                                       |                 | FFh         |

| 012Ch            | Timer RC General Register C                             | TRCGRC          | FFh         |

| 012Dh            | 1                                                       |                 | FFh         |

| 012Eh            | Timer RC General Register D                             | TRCGRD          | FFh         |

| 012Fh            | 1                                                       |                 | FFh         |

| 0130h            | Timer RC Control Register 2                             | TRCCR2          | 00011111b   |

| 0131h            | Timer RC Digital Filter Function Select Register        | TRCDF           | 00h         |

| 0132h            | Timer RC Output Master Enable Register                  | TRCOER          | 01111111b   |

| 0133h            | 1                                                       |                 | -           |

| 0134h            |                                                         | 1               |             |

| 0135h            |                                                         |                 | 1           |

| 0136h            |                                                         | 1               |             |

| 0137h            |                                                         |                 | 1           |

| 0138h            |                                                         |                 | 1           |

| 0139h            |                                                         |                 | 1           |

| 013Ah            |                                                         |                 |             |

| 013Bh            |                                                         |                 | +           |

| 013Dh            |                                                         |                 | +           |

| 013Dh            |                                                         |                 | +           |

| 013Dh            |                                                         |                 |             |

| 013En<br>013Fh   |                                                         |                 |             |

|                  |                                                         | 1               | 1           |

### SFR Information (5)<sup>(1)</sup> Table 4.5

NOTES:

The blank regions are reserved. Do not access locations in these regions.

In J, K version these regions are reserved. Do not access locations in these regions.

| Cumbal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Deremeter                              | Conditions                 |                    | Unit |                              |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------|--------------------|------|------------------------------|-------|

| -     Program/erase endurance <sup>(2)</sup> R8C/28 Group     100 <sup>(3)</sup> -       -     Byte program time     -     50     4       -     Block erase time     -     50     4       -     Block erase time     -     0.4       td(SR-SUS)     Time delay from suspend request until suspend     -     -     97 + CF       -     Interval from erase start/restart until following suspend request     650     -       -     Interval from program start/restart until following suspend request     0     -       -     Time from suspend until program/erase restart     -     3 + CP       -     Time from suspend until program/erase restart     -     -     3 + CP | Max.                                   | Unit                       |                    |      |                              |       |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Program/erase endurance <sup>(2)</sup> | R8C/28 Group               | 100 <sup>(3)</sup> | -    | -                            | times |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        | R8C/29 Group               | 1,000(3)           | -    | -                            | times |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Byte program time                      |                            | -                  | 50   | 400                          | μS    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Block erase time                       |                            | -                  | 0.4  | 9                            | S     |

| td(SR-SUS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |                            | -                  | -    | 97 + CPU clock<br>× 6 cycles | μS    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |                            | 650                | -    | -                            | μS    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |                            | 0                  | -    | -                            | ns    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |                            | -                  | -    | 3 + CPU clock<br>× 4 cycles  | μS    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Program, erase voltage                 |                            | 2.7                | -    | 5.5                          | V     |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Read voltage                           |                            | 2.2                | -    | 5.5                          | V     |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Program, erase temperature             |                            | 0                  | _    | 60                           | °C    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Data hold time <sup>(7)</sup>          | Ambient temperature = 55°C | 20                 | -    | -                            | year  |

| Table 5.4 | Flash Memory (Program ROM) Electrical Characteristics |

|-----------|-------------------------------------------------------|

|-----------|-------------------------------------------------------|

1. Vcc = 2.7 to 5.5 V at Topr = 0 to  $60^{\circ}$ C, unless otherwise specified.

2. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis.

If the programming and erasure endurance is n (n = 100 or 1,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to different addresses in block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one.

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

3. Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

4. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. It is also advisable to retain data on the erasure endurance of each block and limit the number of erase operations to a certain number.

5. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

- 6. Customers desiring program/erase failure rate information should contact their Renesas technical support representative.

- 7. The data hold time includes time that the power supply is off or the clock is not supplied.

| Symbol | Parameter                                               | Condition |      | Standard |       | Unit    |

|--------|---------------------------------------------------------|-----------|------|----------|-------|---------|

| Symbol | Farameter                                               | Condition | Min. | Тур.     | Max.  | Unit    |

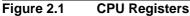

| Vpor1  | Power-on reset valid voltage <sup>(4)</sup>             |           | -    | -        | 0.1   | V       |

| Vpor2  | Power-on reset or voltage monitor 0 reset valid voltage |           | 0    | -        | Vdet0 | V       |

| trth   | External power Vcc rise gradient <sup>(2)</sup>         |           | 20   | -        | _     | mV/msec |

| Table 5.9 | Power-on Reset Circuit. | Voltage Monitor 0 Reset | Electrical Characteristics <sup>(3)</sup> |

|-----------|-------------------------|-------------------------|-------------------------------------------|

|           |                         |                         |                                           |

1. The measurement condition is Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

2. This condition (external power Vcc rise gradient) does not apply if Vcc  $\ge$  1.0 V.

- 3. To use the power-on reset function, enable voltage monitor 0 reset by setting the LVD0ON bit in the OFS register to 0, the VW0C0 and VW0C6 bits in the VW0C register to 1 respectively, and the VCA25 bit in the VCA2 register to 1.

- 4. tw(por1) indicates the duration the external power Vcc must be held below the effective voltage (Vpor1) to enable a power on reset. When turning on the power for the first time, maintain tw(por1) for 30 s or more if -20°C ≤ Topr ≤ 85°C, maintain tw(por1) for 3,000 s or more if -40°C ≤ Topr < -20°C.</p>

| Cumbal        | Paramete               |            | Conditions                                      |            | Stand | lard          | Unit                |

|---------------|------------------------|------------|-------------------------------------------------|------------|-------|---------------|---------------------|

| Symbol        |                        |            | Conditions                                      | Min.       | Тур.  | Max.          |                     |

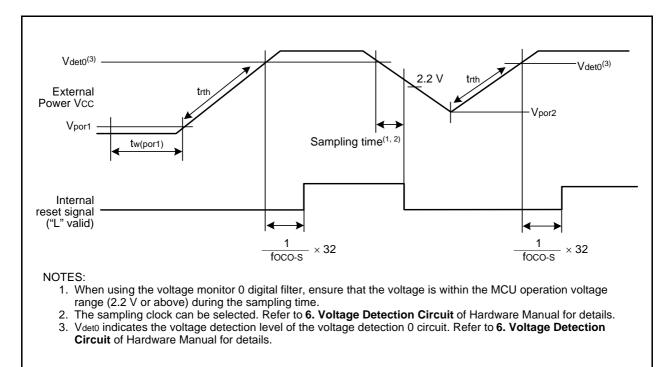

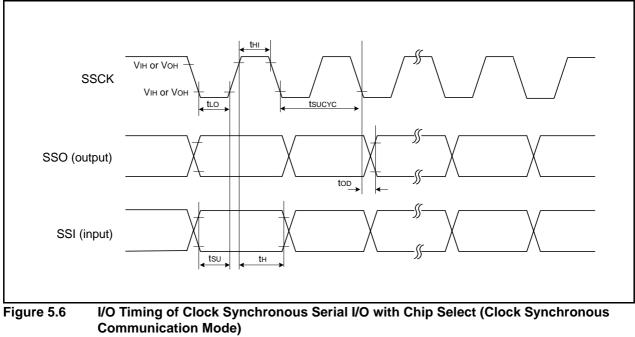

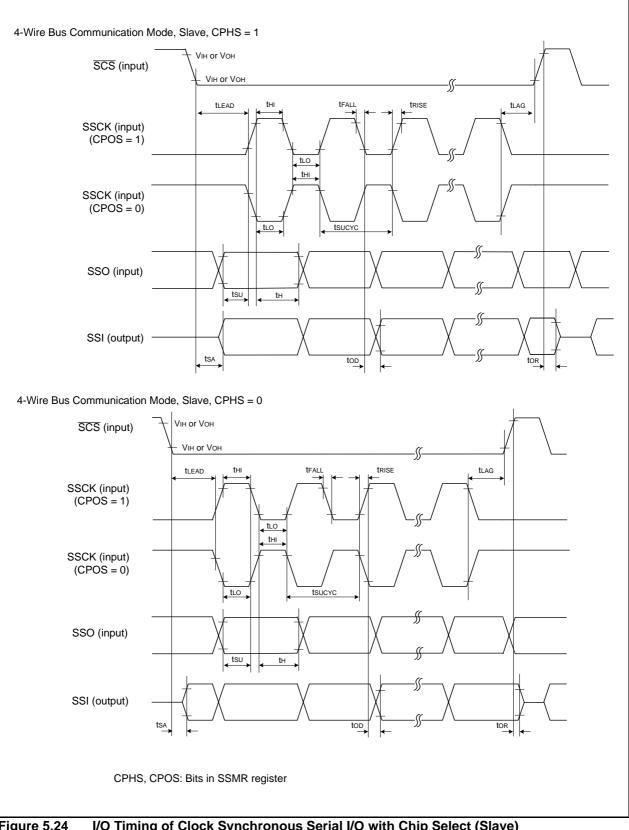

| tsucyc        | SSCK clock cycle time  | e          |                                                 | 4          | -     | -             | tCYC <sup>(2)</sup> |

| tнı           | SSCK clock "H" width   |            |                                                 | 0.4        | -     | 0.6           | tsucyc              |

| tlo           | SSCK clock "L" width   |            |                                                 | 0.4        | -     | 0.6           | tsucyc              |

| trise         | SSCK clock rising      | Master     |                                                 | -          | -     | 1             | tCYC <sup>(2)</sup> |

|               | time                   | Slave      |                                                 | -          | -     | 1             | μs                  |

| tfall         | SSCK clock falling     | Master     |                                                 | -          | -     | 1             | tCYC <sup>(2)</sup> |

|               | time                   | Slave      |                                                 | -          | -     | 1             | μs                  |

| ts∪           | SSO, SSI data input s  | etup time  |                                                 | 100        | -     | -             | ns                  |

| tн            | SSO, SSI data input h  | old time   |                                                 | 1          | -     | -             | tCYC <sup>(2)</sup> |

| <b>t</b> LEAD | SCS setup time         | Slave      |                                                 | 1tcyc + 50 | -     | _             | ns                  |

| tlag          | SCS hold time          | Slave      |                                                 | 1tcyc + 50 | -     | -             | ns                  |

| top           | SSO, SSI data output   | delay time |                                                 | -          | -     | 1             | tCYC <sup>(2)</sup> |

| tsa           | SSI slave access time  | )          | $2.7~V \leq Vcc \leq 5.5~V$                     | -          | -     | 1.5tcyc + 100 | ns                  |

|               |                        |            | $2.2 \text{ V} \leq \text{Vcc} < 2.7 \text{ V}$ | _          | -     | 1.5tcyc + 200 | ns                  |

| tOR           | SSI slave out open tir | ne         | $2.7~V \leq Vcc \leq 5.5~V$                     | -          | _     | 1.5tcyc + 100 | ns                  |

|               |                        |            | $2.2 \text{ V} \leq \text{Vcc} < 2.7 \text{ V}$ | -          | -     | 1.5tcyc + 200 | ns                  |

Table 5.13 Timing Requirements of Clock Synchronous Serial I/O with Chip Select<sup>(1)</sup>

1. Vcc = 2.2 to 5.5 V, Vss = 0 V at T<sub>opr</sub> = -20 to  $85^{\circ}$ C (N version) / -40 to  $85^{\circ}$ C (D version), unless otherwise specified. 2. 1tcrc = 1/f1(s)

| Cumhal  | Dava                | Parameter                                                                                     |                        | Condition     |           | tandard |      | Unit |

|---------|---------------------|-----------------------------------------------------------------------------------------------|------------------------|---------------|-----------|---------|------|------|

| Symbol  | Para                | ameter                                                                                        | Cond                   | ition         | Min.      | Тур.    | Max. | Unit |

| Vон     | Output "H" voltage  | Except P1_0 to P1_7,<br>XOUT                                                                  | Іон = -1 mA            |               | Vcc - 0.5 | -       | Vcc  | V    |

|         |                     | P1_0 to P1_7                                                                                  | Drive capacity<br>HIGH | Іон = -5 mA   | Vcc - 0.5 | _       | Vcc  | V    |

|         |                     |                                                                                               | Drive capacity<br>LOW  | Іон = -1 mA   | Vcc - 0.5 | -       | Vcc  | V    |

|         |                     | XOUT                                                                                          | Drive capacity<br>HIGH | Іон = -0.1 mA | Vcc - 0.5 | -       | Vcc  | V    |

|         |                     |                                                                                               | Drive capacity<br>LOW  | Іон = -50 μА  | Vcc - 0.5 | -       | Vcc  | V    |

| Vol     | Output "L" voltage  | Except P1_0 to P1_7, XOUT                                                                     | IoL = 1 mA             | ·             | -         | _       | 0.5  | V    |

|         |                     | P1_0 to P1_7                                                                                  | Drive capacity<br>HIGH | IOL = 5 mA    | _         | _       | 0.5  | V    |

|         |                     |                                                                                               | Drive capacity<br>LOW  | IOL = 1 mA    | _         | -       | 0.5  | V    |

|         |                     | XOUT                                                                                          | Drive capacity<br>HIGH | IOL = 0.1 mA  | -         | -       | 0.5  | V    |

|         |                     |                                                                                               | Drive capacity<br>LOW  | Iol = 50 μA   | -         | -       | 0.5  | V    |

| VT+-VT- | Hysteresis          | INT0, INT1, INT3,<br>KI0, KI1, KI2, KI3,<br>TRAIO, RXD0, RXD1,<br>CLK0, SSI, SCL,<br>SDA, SSO |                        |               | 0.1       | 0.3     | _    | V    |

|         |                     | RESET                                                                                         |                        |               | 0.1       | 0.4     | -    | V    |

| Ін      | Input "H" current   |                                                                                               | VI = 3 V, Vcc = 3      | V             | -         | _       | 4.0  | μA   |

| lı∟     | Input "L" current   |                                                                                               | VI = 0 V, Vcc = 3      | V             | -         | -       | -4.0 | μA   |

| Rpullup | Pull-up resistance  |                                                                                               | VI = 0 V, Vcc = 3'     | V             | 66        | 160     | 500  | kΩ   |

| Rfxin   | Feedback resistance | XIN                                                                                           |                        |               | -         | 3.0     | _    | MΩ   |

| Rfxcin  | Feedback resistance | XCIN                                                                                          |                        |               | -         | 18      | -    | MΩ   |

| Vram    | RAM hold voltage    |                                                                                               | During stop mode       | e             | 1.8       | -       | -    | V    |

| Table 5.22 | <b>Electrical Characteristics</b> | (3) [Vcc = 3 V] |

|------------|-----------------------------------|-----------------|

|            |                                   | (3)[1000 - 31]  |

1. Vcc = 2.7 to 3.3 V at Topr = -20 to 85°C (N version) / -40 to 85°C (D version), f(XIN) = 10 MHz, unless otherwise specified.

# Table 5.23Electrical Characteristics (4) [Vcc = 3 V]<br/>(Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

| Symbol | Parameter                                                                                  | Condition                                  |                                                                                                                                                                                                                                      |      | Unit |      |      |

|--------|--------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Symbol |                                                                                            |                                            |                                                                                                                                                                                                                                      | Min. | Тур. | Max. | Unit |

| Icc    | Power supply current<br>(Vcc = 2.7 to 3.3 V)<br>Single-chip mode,<br>output pins are open, | High-speed<br>clock mode                   | XIN = 10 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>No division                                                                                                          | _    | 6    | _    | mA   |

|        | other pins are Vss                                                                         |                                            | XIN = 10 MHz (square wave)<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8                                                                                                          | _    | 2    | -    | mA   |

|        |                                                                                            | High-speed<br>on-chip<br>oscillator        | XIN clock off<br>High-speed on-chip oscillator on fOCO = 10 MHz<br>Low-speed on-chip oscillator on = 125 kHz<br>No division                                                                                                          | -    | 5    | 9    | mA   |

|        |                                                                                            | mode                                       | XIN clock off<br>High-speed on-chip oscillator on fOCO = 10 MHz<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8                                                                                                          | _    | 2    | -    | mA   |

|        |                                                                                            | Low-speed<br>on-chip<br>oscillator<br>mode | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>Divide-by-8, FMR47 = 1                                                                                                            | _    | 130  | 300  | μA   |

|        |                                                                                            | Low-speed<br>clock mode                    | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>XCIN clock oscillator on = 32 kHz<br>FMR47 = 1                                                                                             | _    | 130  | 300  | μA   |

|        |                                                                                            |                                            | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>XCIN clock oscillator on = 32 kHz<br>Program operation on RAM<br>Flash memory off, FMSTP = 1                                               | _    | 30   | _    | μΑ   |

|        |                                                                                            | Wait mode                                  | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>While a WAIT instruction is executed<br>Peripheral clock operation<br>VCA27 = VCA26 = VCA25 = 0<br>VCA20 = 1                      | _    | 25   | 70   | μΑ   |

|        |                                                                                            |                                            | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator on = 125 kHz<br>While a WAIT instruction is executed<br>Peripheral clock off<br>VCA27 = VCA26 = VCA25 = 0<br>VCA20 = 1                            | _    | 23   | 55   | μΑ   |

|        |                                                                                            |                                            | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>XCIN clock oscillator on = $32 \text{ kHz}$ (high drive)<br>While a WAIT instruction is executed<br>VCA27 = VCA26 = VCA25 = 0<br>VCA20 = 1 | _    | 3.8  |      | μΑ   |

|        |                                                                                            |                                            | XIN clock off<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>XCIN clock oscillator on = 32 kHz (low drive)<br>While a WAIT instruction is executed<br>VCA27 = VCA26 = VCA25 = 0<br>VCA20 = 1            | _    | 2.0  |      | μΑ   |

|        |                                                                                            | Stop mode                                  | XIN clock off, $T_{opr} = 25^{\circ}C$<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>CM10 = 1<br>Peripheral clock off<br>VCA27 = VCA26 = VCA25 = 0                                                     | _    | 0.7  | 3.0  | μA   |

|        |                                                                                            |                                            | XIN clock off, $T_{opr} = 85^{\circ}C$<br>High-speed on-chip oscillator off<br>Low-speed on-chip oscillator off<br>CM10 = 1<br>Peripheral clock off<br>VCA27 = VCA26 = VCA25 = 0                                                     | _    | 1.1  |      | μΑ   |

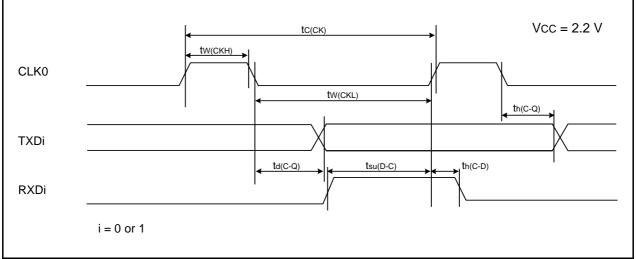

| Symbol   | Parameter                 | Star | Standard |      |

|----------|---------------------------|------|----------|------|

|          | Parameter                 | Min. | Max.     | Unit |

| tc(CK)   | CLK0 input cycle time     | 800  | -        | ns   |

| tw(CKH)  | CLK0 input "H" width      | 400  | -        | ns   |

| tW(CKL)  | CLK0 input "L" width      | 400  | -        | ns   |

| td(C-Q)  | TXDi output delay time    | -    | 200      | ns   |

| th(C-Q)  | TXDi hold time            | 0    | -        | ns   |

| tsu(D-C) | RXDi input setup time     | 150  | -        | ns   |

| th(C-D)  | RXDi input hold time 90 – |      |          |      |

i = 0 or 1

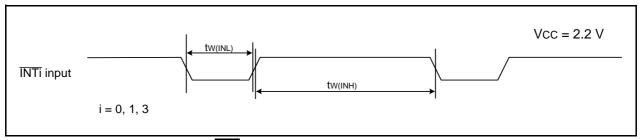

### Table 5.33 External Interrupt INTi (i = 0, 1, 3) Input

| Symbol  | Parameter                                          | Stan      | Standard |      |

|---------|----------------------------------------------------|-----------|----------|------|

| Symbol  | Falanielei                                         | Min. Max. |          | Unit |

| tw(INH) | INTi input "H" width                               | 1000(1)   | -        | ns   |

| tw(INL) | INTi input "L" width         1000 <sup>(2)</sup> - |           |          |      |

NOTES:

1. When selecting the digital filter by the INTi input filter select bit, use an INTi input HIGH width of either (1/digital filter clock frequency × 3) or the minimum value of standard, whichever is greater.

When selecting the digital filter by the INTi input filter select bit, use an INTi input LOW width of either (1/digital filter clock frequency × 3) or the minimum value of standard, whichever is greater.

Figure 5.19 External Interrupt INTi Input Timing Diagram when VCC = 2.2 V

### J, K Version 5.2

| Table 5.34 | Absolute | Maximum | Ratings |

|------------|----------|---------|---------|

|------------|----------|---------|---------|

| Symbol   | Parameter                     | Condition                       | Rated Value                                       | Unit |

|----------|-------------------------------|---------------------------------|---------------------------------------------------|------|

| Vcc/AVcc | Supply voltage                |                                 | -0.3 to 6.5                                       | V    |

| Vi       | Input voltage                 |                                 | -0.3 to Vcc + 0.3                                 | V    |

| Vo       | Output voltage                |                                 | -0.3 to Vcc + 0.3                                 | V    |

| Pd       | Power dissipation             | -40 °C $\leq$ Topr $\leq$ 85 °C | 300                                               | mW   |

|          |                               | 85 °C $\leq$ Topr $\leq$ 125 °C | 125                                               | mW   |

| Topr     | Operating ambient temperature |                                 | -40 to 85 (J version) /<br>-40 to 125 (K version) | °C   |

| Tstg     | Storage temperature           |                                 | -65 to 150                                        | °C   |

### Table 5.35 **Recommended Operating Conditions**

| Question  | Der                             |                                                  |                                                                                     |         | Standard |         | 11.2 |

|-----------|---------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------|---------|----------|---------|------|

| Symbol    | Para                            | ameter                                           | Conditions                                                                          | Min.    | Тур.     | Max.    | Unit |

| Vcc/AVcc  | Supply voltage                  |                                                  |                                                                                     | 2.7     | -        | 5.5     | V    |

| Vss/AVss  | Supply voltage                  |                                                  |                                                                                     | -       | 0        | -       | V    |

| Viн       | Input "H" voltage               |                                                  |                                                                                     | 0.8 Vcc | -        | Vcc     | V    |

| VIL       | Input "L" voltage               |                                                  |                                                                                     | 0       | -        | 0.2 Vcc | V    |

| IOH(sum)  | Peak sum output<br>"H" current  | Sum of all pins<br>IOH(peak)                     |                                                                                     | -       | -        | -60     | mA   |

| IOH(peak) | Peak output "H"<br>current      |                                                  |                                                                                     | -       | -        | -10     | mA   |

| IOH(avg)  | Average output<br>"H" current   |                                                  |                                                                                     | -       | -        | -5      | mA   |

| IOL(sum)  | Peak sum output<br>"L" currents | Sum of all pins<br>IOL(peak)                     |                                                                                     | -       | -        | 60      | mA   |

| IOL(peak) | Peak output "L"<br>currents     |                                                  |                                                                                     | -       | -        | 10      | mA   |

| IOL(avg)  | Average output<br>"L" current   |                                                  |                                                                                     | -       | -        | 5       | mA   |

| f(XIN)    | XIN clock input os              | cillation frequency                              | $3.0 \text{ V} \le \text{Vcc} \le 5.5 \text{ V}$ (other than K version)             | 0       | -        | 20      | MHz  |

|           |                                 |                                                  | $3.0 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ (K version)                      | 0       | -        | 16      | MHz  |

|           |                                 |                                                  | $2.7 \text{ V} \leq \text{Vcc} < 3.0 \text{ V}$                                     | 0       | -        | 10      | MHz  |

| -         | System clock                    | OCD2 = 0<br>XIN clock selected                   | 3.0 V $\leq$ Vcc $\leq$ 5.5 V (other than K version)                                | 0       | -        | 20      | MHz  |

|           |                                 |                                                  | $3.0 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ (K version)                      | 0       | -        | 16      | MHz  |

|           |                                 |                                                  | $2.7 \text{ V} \leq \text{Vcc} < 3.0 \text{ V}$                                     | 0       | -        | 10      | MHz  |

|           |                                 | OCD2 = 1<br>On-chip oscillator<br>clock selected | FRA01 = 0<br>Low-speed on-chip oscillator clock<br>selected                         | -       | 125      | -       | kHz  |

|           |                                 |                                                  | FRA01 = 1<br>High-speed on-chip oscillator clock<br>selected (other than K version) | -       | -        | 20      | MHz  |

|           |                                 |                                                  | FRA01 = 1<br>High-speed on-chip oscillator clock<br>selected                        | -       | -        | 10      | MHz  |

NOTES:

Vcc = 2.7 to 5.5 V at Topr = -40 to 85°C (J version) / -40 to 125°C (K version), unless otherwise specified.

The average output current indicates the average value of current measured during 100 ms.

| Symbol  |                                     | Parameter               | Conditions                              |      | Standard |      |      |

|---------|-------------------------------------|-------------------------|-----------------------------------------|------|----------|------|------|

| Symbol  |                                     | arameter                | Conditions                              | Min. | Тур.     | Max. | Unit |

| -       | Resolution                          |                         | Vref = AVCC                             | -    | -        | 10   | Bits |

| -       | Absolute                            | 10-bit mode             | $\phi$ AD = 10 MHz, Vref = AVCC = 5.0 V | -    | -        | ±3   | LSB  |

|         | accuracy                            | 8-bit mode              | $\phi$ AD = 10 MHz, Vref = AVCC = 5.0 V | -    | -        | ±2   | LSB  |

|         |                                     | 10-bit mode             | $\phi$ AD = 10 MHz, Vref = AVCC = 3.3 V | -    | -        | ±5   | LSB  |

|         |                                     | 8-bit mode              | $\phi$ AD = 10 MHz, Vref = AVCC = 3.3 V | -    | -        | ±2   | LSB  |

| Rladder | Resistor ladder                     | ·                       | Vref = AVCC                             | 10   | -        | 40   | kΩ   |

| tconv   | Conversion time                     | 10-bit mode             | $\phi$ AD = 10 MHz, Vref = AVCC = 5.0 V | 3.3  | -        | -    | μS   |

|         |                                     | 8-bit mode              | $\phi$ AD = 10 MHz, Vref = AVCC = 5.0 V | 2.8  | -        | -    | μS   |

| Vref    | Reference voltag                    | e                       |                                         | 2.7  | -        | AVcc | V    |

| Via     | Analog input voltage <sup>(2)</sup> |                         |                                         | 0    | -        | AVcc | V    |

| -       | A/D operating                       | Without sample and hold |                                         | 0.25 | -        | 10   | MHz  |

|         | clock frequency                     | With sample and hold    |                                         | 1    | -        | 10   | MHz  |

Table 5.36 A/D Converter Characteristics

1. AVcc = 2.7 to 5.5 V at T<sub>opr</sub> = -40 to 85°C (J version) / -40 to 125°C (K version), unless otherwise specified.

2. When the analog input voltage is over the reference voltage, the A/D conversion result will be 3FFh in 10-bit mode and FFh in 8-bit mode.

Figure 5.20 Ports P1, P3, and P4 Timing Measurement Circuit

| Symbol     | Parameter                                                            | Conditions                 |                       | Standard |                              | Unit  |

|------------|----------------------------------------------------------------------|----------------------------|-----------------------|----------|------------------------------|-------|

| Symbol     | Farameter                                                            | Conditions                 | Min.                  | Тур.     | Max.                         | Unit  |

| -          | Program/erase endurance <sup>(2)</sup>                               |                            | 10,000 <sup>(3)</sup> | -        | -                            | times |

| -          | Byte program time (program/erase endurance $\leq$ 1,000 times)       |                            | -                     | 50       | 400                          | μS    |

| -          | Byte program time<br>(program/erase endurance > 1,000 times)         |                            | -                     | 65       | _                            | μS    |

| -          | Block erase time<br>(program/erase endurance ≤ 1,000 times)          |                            | -                     | 0.2      | 9                            | S     |

| -          | Block erase time<br>(program/erase endurance > 1,000 times)          |                            | -                     | 0.3      | _                            | S     |

| td(SR-SUS) | Time delay from suspend request until suspend                        |                            | -                     | -        | 97 + CPU clock<br>× 6 cycles | μS    |

| -          | Interval from erase start/restart until<br>following suspend request |                            | 650                   | -        | _                            | μS    |

| -          | Interval from program start/restart until following suspend request  |                            | 0                     | -        | _                            | ns    |

| -          | Time from suspend until program/erase restart                        |                            | -                     | -        | 3 + CPU clock<br>× 4 cycles  | μS    |

| -          | Program, erase voltage                                               |                            | 2.7                   | -        | 5.5                          | V     |

| -          | Read voltage                                                         |                            | 2.7                   | -        | 5.5                          | V     |

| -          | Program, erase temperature                                           |                            | -40                   | -        | 85 <sup>(8)</sup>            | °C    |

| -          | Data hold time <sup>(9)</sup>                                        | Ambient temperature = 55°C | 20                    | -        | -                            | year  |

### **Table 5.38** Flash Memory (Data flash Block A, Block B) Electrical Characteristics<sup>(4)</sup>

NOTES:

1. Vcc = 2.7 to 5.5 V at Topr = -40 to 85°C (J version) / -40 to 125°C (K version), unless otherwise specified.

2. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis. If the programming and erasure endurance is n (n = 10,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to different addresses in block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one. However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

- 3. Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

- 4. Standard of block A and block B when program and erase endurance exceeds 1,000 times. Byte program time to 1,000 times is the same as that in program ROM.

- 5. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. In addition, averaging the erasure endurance between blocks A and B can further reduce the actual erasure endurance. It is also advisable to retain data on the erasure endurance of each block and limit the number of erase operations to a certain number.

- 6. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

- 7. Customers desiring program/erase failure rate information should contact their Renesas technical support representative. 8. 125°C for K version.

- 9. The data hold time includes time that the power supply is off or the clock is not supplied.

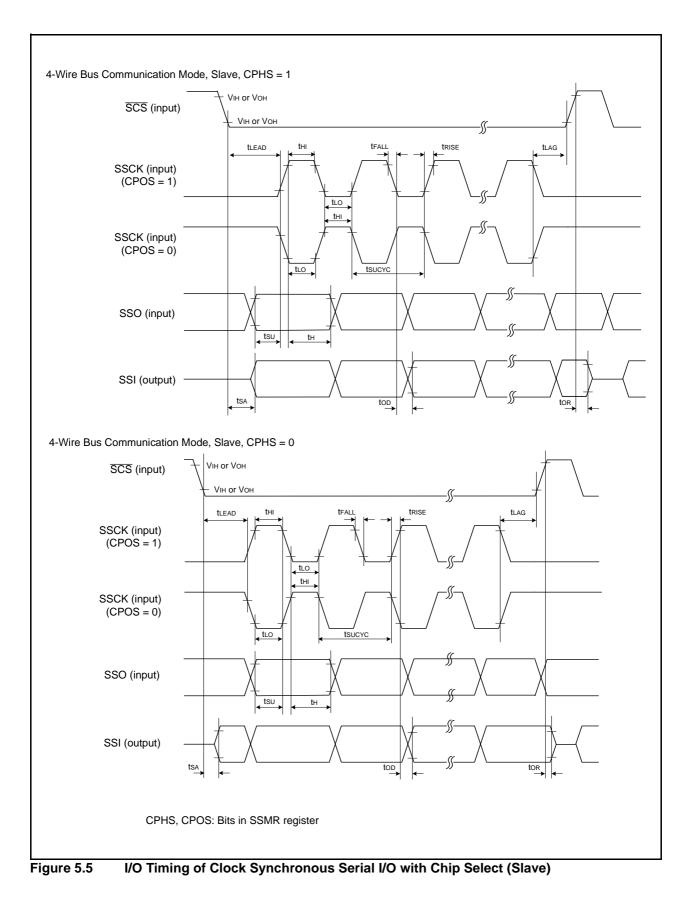

Figure 5.24 I/O Timing of Clock Synchronous Serial I/O with Chip Select (Slave)

### Timing requirements (Unless Otherwise Specified: Vcc = 3 V, Vss = 0 V at Topr = 25°C) [Vcc = 3 V]

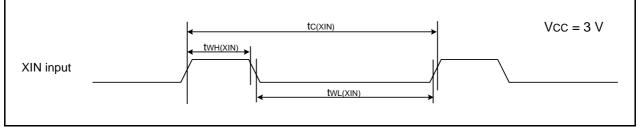

### Table 5.55 XIN Input

| Symbol   | Parameter                | Stan | dard | Unit |

|----------|--------------------------|------|------|------|

| Symbol   | Falameter                | Min. | Max. | Unit |

| tc(XIN)  | XIN input cycle time     | 100  | -    | ns   |

| twh(xin) | XIN input "H" width      | 40   | -    | ns   |

| twl(XIN) | XIN input "L" width 40 – |      |      |      |

Figure 5.31 XIN Input Timing Diagram when Vcc = 3 V

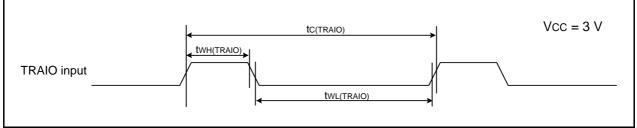

### Table 5.56 TRAIO Input

| Symbol     | Parameter                   | Standard |      | Unit |  |

|------------|-----------------------------|----------|------|------|--|

| Symbol     | Falanielei                  | Min.     | Max. | Unit |  |

| tc(TRAIO)  | TRAIO input cycle time      | 300      | -    | ns   |  |

| twh(traio) | TRAIO input "H" width 120 – |          |      |      |  |

| twl(traio) | TRAIO input "L" width 120 – |          |      |      |  |

Figure 5.32 TRAIO Input Timing Diagram when Vcc = 3 V

# **REVISION HISTORY**

# R8C/28 Group, R8C/29 Group Datasheet

|      |              |           | Description                                                                                                                 |

|------|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| Rev. | Date         | Page      | Summary                                                                                                                     |

| 0.10 | Nov 14, 2005 | _         | First Edition issued                                                                                                        |

| 0.30 | Feb 28, 2006 | all pages | "J, K version" added                                                                                                        |

|      |              | 1         | 1.1 Applications revised                                                                                                    |

|      |              | 2         | Table 1.1 Functions and Specifications for R8C/28 Group revised                                                             |