# E·XFL

## XMOS - XEF216-256-FB236-C20 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | XCore                                                          |

| Core Size                  | 32-Bit 16-Core                                                 |

| Speed                      | 2000MIPS                                                       |

| Connectivity               | RGMII, USB                                                     |

| Peripherals                | -                                                              |

| Number of I/O              | 73                                                             |

| Program Memory Size        | 2MB (2M x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | External                                                       |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 236-LFBGA                                                      |

| Supplier Device Package    | 236-FBGA (10x10)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xef216-256-fb236-c20 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 xCORE Multicore Microcontrollers

The xCORE200 Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

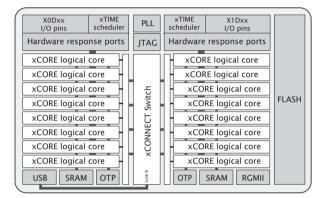

Figure 1: XEF216-512-FB236 block diagram

Key features of the XEF216-512-FB236 include:

- ► **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between five and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 6.1

- xTIME scheduler The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 6.2

- Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 6.5

- xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 6.6

-XM()S

2

| Signal | Function                                      |                 |                 |                 |                   |                   | Туре | Properties |

|--------|-----------------------------------------------|-----------------|-----------------|-----------------|-------------------|-------------------|------|------------|

| X0D41  | X <sub>0</sub> L0 <sup>0</sup> <sub>in</sub>  |                 |                 | 8D <sup>5</sup> | 16B <sup>13</sup> |                   | 1/0  | IOL, PD    |

| X0D42  | X <sub>0</sub> L0 <sup>0</sup> <sub>out</sub> |                 |                 | 8D <sup>6</sup> | 16B <sup>14</sup> |                   | 1/0  | IOL, PD    |

| X0D43  | X <sub>0</sub> L0 <sup>1</sup> <sub>out</sub> |                 |                 | 8D <sup>7</sup> | 16B <sup>15</sup> |                   | 1/0  | IOL, PD    |

| X0D49  | X <sub>0</sub> L5 <sup>4</sup>                |                 |                 |                 |                   | 32A <sup>0</sup>  | 1/0  | IOR, PD    |

| X0D50  | X <sub>0</sub> L5 <sup>3</sup>                |                 |                 |                 |                   | 32A <sup>1</sup>  | I/O  | IOR, PD    |

| X0D51  | $X_0L5_{in}^2$                                |                 |                 |                 |                   | 32A <sup>2</sup>  | 1/0  | IOR, PD    |

| X0D52  | X <sub>0</sub> L5 <sup>1</sup>                |                 |                 |                 |                   | 32A <sup>3</sup>  | I/O  | IOR, PD    |

| X0D53  | X <sub>0</sub> L5 <sup>0</sup>                |                 |                 |                 |                   | 32A <sup>4</sup>  | 1/0  | IOR, PD    |

| X0D54  | X <sub>0</sub> L5 <sup>0</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>5</sup>  | 1/0  | IOR, PD    |

| X0D55  | X <sub>0</sub> L5 <sup>1</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>6</sup>  | 1/0  | IOR, PD    |

| X0D56  | X <sub>0</sub> L5 <sup>2</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>7</sup>  | 1/0  | IOR, PD    |

| X0D57  | X <sub>0</sub> L5 <sup>3</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>8</sup>  | 1/0  | IOR, PD    |

| X0D58  | X <sub>0</sub> L5 <sup>4</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>9</sup>  | 1/0  | IOR, PD    |

| X0D61  | X <sub>0</sub> L6 <sup>4</sup>                |                 |                 |                 |                   | 32A <sup>10</sup> | 1/0  | IOR, PD    |

| X0D62  | X <sub>0</sub> L6 <sup>3</sup>                |                 |                 |                 |                   | 32A <sup>11</sup> | 1/0  | IOR, PD    |

| X0D63  | X <sub>0</sub> L6 <sup>2</sup> <sub>in</sub>  |                 |                 |                 |                   | 32A <sup>12</sup> | I/O  | IOR, PD    |

| X0D64  | X <sub>0</sub> L6 <sup>1</sup>                |                 |                 |                 |                   | 32A <sup>13</sup> | I/O  | IOR, PD    |

| X0D65  | X <sub>0</sub> L6 <sup>0</sup>                |                 |                 |                 |                   | 32A <sup>14</sup> | I/O  | IOR, PD    |

| X0D66  | X <sub>0</sub> L6 <sup>0</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>15</sup> | 1/0  | IOR, PD    |

| X0D67  | X <sub>0</sub> L6 <sup>1</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>16</sup> | 1/0  | IOR, PD    |

| X0D68  | X <sub>0</sub> L6 <sup>2</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>17</sup> | 1/0  | IOR, PD    |

| X0D69  | X <sub>0</sub> L6 <sup>3</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>18</sup> | I/O  | IOR, PD    |

| X0D70  | X <sub>0</sub> L6 <sup>4</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>19</sup> | I/O  | IOR, PD    |

| X1D00  |                                               | 1A <sup>0</sup> |                 |                 |                   |                   | I/O  | IOR, PD    |

| X1D01  |                                               | 1B <sup>0</sup> |                 |                 |                   |                   | I/0  | IOR, PD    |

| X1D02  | X <sub>0</sub> L4 <sup>0</sup>                |                 | 4A <sup>0</sup> | 8A <sup>0</sup> | 16A <sup>0</sup>  | 32A <sup>20</sup> | I/0  | IOR, PD    |

| X1D03  | X <sub>0</sub> L4 <sup>0</sup> <sub>out</sub> |                 | 4A <sup>1</sup> | 8A <sup>1</sup> | 16A <sup>1</sup>  | 32A <sup>21</sup> | I/O  | IOR, PD    |

| X1D04  | X <sub>0</sub> L4 <sup>1</sup> <sub>out</sub> |                 | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup> | I/O  | IOR, PD    |

| X1D05  | X <sub>0</sub> L4 <sup>2</sup> <sub>out</sub> |                 | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup> | I/O  | IOR, PD    |

| X1D06  | X <sub>0</sub> L4 <sup>3</sup> <sub>out</sub> |                 | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup> | I/O  | IOR, PD    |

| X1D07  | X <sub>0</sub> L4 <sup>4</sup> <sub>out</sub> |                 | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup> | I/O  | IOR, PD    |

| X1D08  | X <sub>0</sub> L7 <sup>4</sup>                |                 | 4A <sup>2</sup> | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup> | I/O  | IOR, PD    |

| X1D09  | X <sub>0</sub> L7 <sup>3</sup> <sub>in</sub>  |                 | 4A <sup>3</sup> | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup> | I/O  | IOR, PD    |

| X1D10  |                                               | 1C <sup>0</sup> |                 |                 |                   |                   | I/O  | IOT, PD    |

| X1D11  |                                               | 1D <sup>0</sup> |                 |                 |                   |                   | I/O  | IOT, PD    |

| X1D12  |                                               | 1E <sup>0</sup> |                 |                 |                   |                   | I/O  | IOL, PD    |

| X1D13  |                                               | 1F <sup>0</sup> |                 |                 |                   |                   | I/O  | IOL, PD    |

| X1D14  |                                               |                 | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup> | I/O  | IOR, PD    |

| X1D15  |                                               |                 | 4C <sup>1</sup> | 8B1             | 16A <sup>9</sup>  | 32A <sup>29</sup> | I/O  | IOR, PD    |

| X1D16  | X <sub>0</sub> L3 <sup>1</sup>                |                 | 4D <sup>0</sup> | 8B <sup>2</sup> | 16A <sup>10</sup> |                   | I/O  | IOL, PD    |

| X1D17  | X <sub>0</sub> L3 <sup>0</sup>                |                 | 4D <sup>1</sup> | 8B <sup>3</sup> | 16A <sup>11</sup> |                   | I/O  | IOL, PD    |

| X1D18  | X <sub>0</sub> L3 <sup>0</sup> <sub>out</sub> |                 | 4D <sup>2</sup> | 8B <sup>4</sup> | 16A <sup>12</sup> |                   | I/O  | IOL, PD    |

| X1D19  | X <sub>0</sub> L3 <sup>1</sup> <sub>out</sub> |                 | 4D <sup>3</sup> | 8B <sup>5</sup> | 16A <sup>13</sup> |                   | I/0  | IOL, PD    |

-XMOS<sup>®</sup>-

(continued)

| Signal | Function                                      |                |                 |                 |                   |                   | Туре | Properties |

|--------|-----------------------------------------------|----------------|-----------------|-----------------|-------------------|-------------------|------|------------|

| X1D20  | Tunction                                      |                | 4C <sup>2</sup> | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup> | 1/0  | IOR, PD    |

| X1D21  |                                               |                | 4C <sup>3</sup> | 8B <sup>7</sup> |                   | 32A <sup>31</sup> | I/O  | IOR, PD    |

| X1D22  | X <sub>0</sub> L3 <sup>4</sup> 1              | G <sup>0</sup> |                 |                 | 10/1              | 527               | 1/0  | IOL, PD    |

| X1D23  |                                               | H <sup>0</sup> |                 |                 |                   |                   | I/O  | IOL, PD    |

| X1D24  |                                               | 10             |                 |                 |                   |                   | I/O  | IOR, PD    |

| X1D25  |                                               | 10             |                 |                 |                   |                   | I/O  | IOR, PD    |

| X1D26  | tx_clk (rgmii)                                |                | 4E <sup>0</sup> | 8C <sup>0</sup> | 16B <sup>0</sup>  |                   | I/O  | IOT, PD    |

| X1D27  | tx_ctl (rgmii)                                |                | 4E <sup>1</sup> | 8C <sup>1</sup> | 16B <sup>1</sup>  |                   | I/O  | IOT, PD    |

| X1D28  | rx_clk (rgmii)                                |                | 4F <sup>0</sup> | 8C <sup>2</sup> | 16B <sup>2</sup>  |                   | I/O  | IOT, PD    |

| X1D29  | rx_ctl (rgmii)                                |                | 4F <sup>1</sup> | 8C <sup>3</sup> | 16B <sup>3</sup>  |                   | I/O  | IOT, PD    |

| X1D30  | rx0 (rgmii)                                   |                | 4F <sup>2</sup> | 8C <sup>4</sup> | 16B <sup>4</sup>  |                   | I/O  | IOT, PD    |

| X1D31  | rx0 (rgmii)                                   |                | 4F <sup>3</sup> | 8C <sup>5</sup> | 16B <sup>5</sup>  |                   | 1/0  | IOT, PD    |

| X1D32  | rx1 (rgmii)                                   |                | 4E <sup>2</sup> | 8C <sup>6</sup> | 16B <sup>6</sup>  |                   | I/O  | IOT, PD    |

| X1D33  | rx2 (rgmii)                                   |                | 4E <sup>3</sup> | 8C <sup>7</sup> | 16B <sup>7</sup>  |                   | I/O  | IOT, PD    |

| X1D34  | -                                             | К <sup>0</sup> |                 |                 | 100               |                   | I/O  | IOL, PD    |

| X1D35  |                                               | L <sup>0</sup> |                 |                 |                   |                   | I/O  | IOL, PD    |

| X1D36  | oout                                          | M <sup>0</sup> |                 | 8D <sup>0</sup> | 16B <sup>8</sup>  |                   | 1/0  | IOL, PD    |

| X1D37  |                                               | N <sup>0</sup> |                 | 8D <sup>1</sup> | 16B <sup>9</sup>  |                   | I/O  | IOL, PD    |

| X1D38  | 0 - 10                                        | 00             |                 | 8D <sup>2</sup> | 16B <sup>10</sup> |                   | I/O  | IOL, PD    |

| X1D39  | * 10                                          | P <sup>0</sup> |                 | 8D <sup>3</sup> | 16B <sup>11</sup> |                   | I/O  | IOL, PD    |

| X1D40  | tx3 (rgmii)                                   | -              |                 | 8D <sup>4</sup> | 16B <sup>12</sup> |                   | 1/0  | IOT, PD    |

| X1D41  | tx2 (rgmii)                                   |                |                 | 8D <sup>5</sup> | 16B <sup>13</sup> |                   | 1/0  | IOT, PD    |

| X1D42  | tx1 (rgmii)                                   |                |                 | 8D <sup>6</sup> | 16B <sup>14</sup> |                   | 1/0  | IOT, PD    |

| X1D43  | tx0 (rgmii)                                   |                |                 | 8D <sup>7</sup> | 16B <sup>15</sup> |                   | 1/0  | IOT, PD    |

| X1D49  | X <sub>0</sub> L1 <sup>4</sup> <sub>in</sub>  |                |                 |                 |                   | 32A <sup>0</sup>  | I/O  | IOL, PD    |

| X1D50  | X <sub>0</sub> L1 <sup>3</sup>                |                |                 |                 |                   | 32A <sup>1</sup>  | I/O  | IOL, PD    |

| X1D51  | $X_0L1_{in}^2$                                |                |                 |                 |                   | 32A <sup>2</sup>  | I/O  | IOL, PD    |

| X1D52  | X <sub>0</sub> L1 <sup>1</sup>                |                |                 |                 |                   | 32A <sup>3</sup>  | I/O  | IOL, PD    |

| X1D53  | X <sub>0</sub> L1 <sup>0</sup>                |                |                 |                 |                   | 32A <sup>4</sup>  | I/O  | IOL, PD    |

| X1D54  | X <sub>0</sub> L1 <sup>0</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>5</sup>  | I/0  | IOL, PD    |

| X1D55  | X <sub>0</sub> L1 <sup>1</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>6</sup>  | I/O  | IOL, PD    |

| X1D56  | X <sub>0</sub> L1 <sup>2</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>7</sup>  | I/O  | IOL, PD    |

| X1D57  | X <sub>0</sub> L1 <sup>3</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>8</sup>  | I/O  | IOL, PD    |

| X1D58  | X <sub>0</sub> L1 <sup>4</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>9</sup>  | I/O  | IOL, PD    |

| X1D61  | X <sub>0</sub> L2 <sup>4</sup> <sub>in</sub>  |                |                 |                 |                   | 32A <sup>10</sup> | I/O  | IOL, PD    |

| X1D62  | X <sub>0</sub> L2 <sup>3</sup>                |                |                 |                 |                   | 32A <sup>11</sup> | I/O  | IOL, PD    |

| X1D63  | X <sub>0</sub> L2 <sup>2</sup> <sub>in</sub>  |                |                 |                 |                   | 32A <sup>12</sup> | I/O  | IOL, PD    |

| X1D64  | X <sub>0</sub> L2 <sup>1</sup>                |                |                 |                 |                   | 32A <sup>13</sup> | I/O  | IOL, PD    |

| X1D65  | X <sub>0</sub> L2 <sup>0</sup>                |                |                 |                 |                   | 32A <sup>14</sup> | I/O  | IOL, PD    |

| X1D66  | X <sub>0</sub> L2 <sup>0</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>15</sup> | I/O  | IOL, PD    |

| X1D67  | X <sub>0</sub> L2 <sup>1</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>16</sup> | I/O  | IOL, PD    |

| X1D68  | X <sub>0</sub> L2 <sup>2</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>17</sup> | I/O  | IOL, PD    |

| X1D69  | X <sub>0</sub> L2 <sup>3</sup> <sub>out</sub> |                |                 |                 |                   | 32A <sup>18</sup> | I/O  | IOL, PD    |

(continued)

XS2-UEF16A-512-FB236

# 6 Product Overview

The XEF216-512-FB236 is a powerful device that consists of two xCORE Tiles, each comprising a flexible logical processing cores with tightly integrated I/O and on-chip memory.

#### 6.1 Logical cores

Each tile has 8 active logical cores, which issue instructions down a shared fivestage pipeline. Instructions from the active cores are issued round-robin. If up to five logical cores are active, each core is allocated a fifth of the processing cycles. If more than five logical cores are active, each core is allocated at least 1/n cycles (for *n* cores). Figure 3 shows the guaranteed core performance depending on the number of cores used.

Figure 3: Logical core performance

| gure 3: | Speed | MIPS      | Frequency |     | Minim | um MIF | 'S per c | ore (fo | r <i>n</i> co | res) |    |

|---------|-------|-----------|-----------|-----|-------|--------|----------|---------|---------------|------|----|

| al core | grade |           |           | 1   | 2     | 3      | 4        | 5       | 6             | 7    | 8  |

| mance   | 10    | 1000 MIPS | 500 MHz   | 100 | 100   | 100    | 100      | 100     | 83            | 71   | 63 |

There is no way that the performance of a logical core can be reduced below these predicted levels (unless *priority threads* are used: in this case the guaranteed minimum performance is computed based on the number of priority threads as defined in the architecture manual). Because cores may be delayed on I/O, however, their unused processing cycles can be taken by other cores. This means that for more than five logical cores, the performance of each core is often higher than the predicted minimum but cannot be guaranteed.

The logical cores are triggered by events instead of interrupts and run to completion. A logical core can be paused to wait for an event.

## 6.2 xTIME scheduler

The xTIME scheduler handles the events generated by xCORE Tile resources, such as channel ends, timers and I/O pins. It ensures that all events are serviced and synchronized, without the need for an RTOS. Events that occur at the I/O pins are handled by the Hardware-Response ports and fed directly to the appropriate xCORE Tile. An xCORE Tile can also choose to wait for a specified time to elapse, or for data to become available on a channel.

Tasks do not need to be prioritised as each of them runs on their own logical xCORE. It is possible to share a set of low priority tasks on a single core using cooperative multitasking.

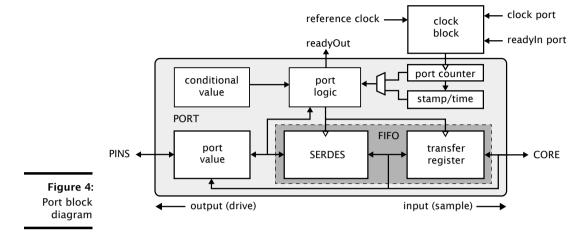

#### 6.3 Hardware Response Ports

Hardware Response ports connect an xCORE tile to one or more physical pins and as such define the interface between hardware attached to the XEF216-512-FB236, and the software running on it. A combination of 1 bit, 4 bit, 8 bit, 16 bit and 32 bit

ports are available. All pins of a port provide either output or input. Signals in different directions cannot be mapped onto the same port.

The port logic can drive its pins high or low, or it can sample the value on its pins, optionally waiting for a particular condition. Ports are accessed using dedicated instructions that are executed in a single processor cycle. xCORE-200 IO pins can be used as *open collector* outputs, where signals are driven low if a zero is output, but left high impedance if a one is output. This option is set on a per-port basis.

Data is transferred between the pins and core using a FIFO that comprises a SERDES and transfer register, providing options for serialization and buffered data.

Each port has a 16-bit counter that can be used to control the time at which data is transferred between the port value and transfer register. The counter values can be obtained at any time to find out when data was obtained, or used to delay I/O until some time in the future. The port counter value is automatically saved as a timestamp, that can be used to provide precise control of response times.

The ports and xCONNECT links are multiplexed onto the physical pins. If an xConnect Link is enabled, the pins of the underlying ports are disabled. If a port is enabled, it overrules ports with higher widths that share the same pins. The pins on the wider port that are not shared remain available for use when the narrower port is enabled. Ports always operate at their specified width, even if they share pins with another port.

## 6.4 Clock blocks

xCORE devices include a set of programmable clocks called clock blocks that can be used to govern the rate at which ports execute. Each xCORE tile has six clock blocks: the first clock block provides the tile reference clock and runs at a default frequency of 100MHz; the remaining clock blocks can be set to run at different frequencies.

- ► A 32-bit program size *s* in words.

- Program consisting of  $s \times 4$  bytes.

- A 32-bit CRC, or the value 0x0D15AB1E to indicate that no CRC check should be performed.

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

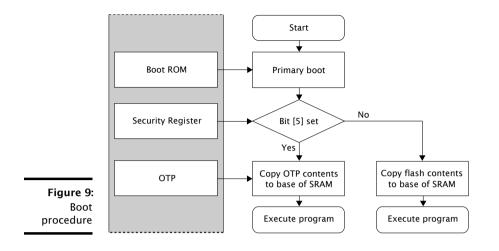

#### 8.1 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 10 provide a strong level of protection and are sufficient for providing strong IP security.

## 9 Memory

#### 9.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

| Feature              | Bit  | Description                                                                                                                                                                                                                                |  |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible<br>for the tile state or memory content to be accessed<br>via the JTAG interface.                                                                                                     |  |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state<br>via the system switch. Disabling both JTAG and Link<br>access transforms an xCORE Tile into a "secure island"<br>with other tiles free for non-secure user application<br>code. |  |

| Secure Boot          | 5    | The xCORE Tile is forced to boot from address 0 the OTP, allowing the xCORE Tile boot ROM to bypassed ( <i>see</i> §8).                                                                                                                    |  |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                             |  |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                                       |  |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                                       |  |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                                       |  |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                                       |  |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables up<br>dates to all sectors and security register.                                                                                                                                             |  |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG inter<br>face to this OTP.                                                                                                                                                                 |  |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                                        |  |

|                      | 2115 | General purpose software accessable security registe available to end-users.                                                                                                                                                               |  |

|                      | 3122 | General purpose user programmable JTAG UserIE code extension.                                                                                                                                                                              |  |

Figure 10: Security register features

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

## 9.2 SRAM

Each xCORE Tile integrates a single 256KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

# 10 USB PHY

The USB PHY provides High-Speed and Full-Speed, device, host, and on-the-go functionality. The PHY is configured through a set of peripheral registers (Appendix F), When connecting a USB cable to the device it is possible an overvoltage transient will be present on VBus due to the inductance of the USB cable combined with the required input capacitor on VBus. The circuit in Figure 12 ensures that the transient does not damage the device. The 10k series resistor and 0.1 uF capacitor ensure than any input transient is filtered and does not reach the device. The 47k resistor to ground is a bleeder resistor to discharge the input capacitor when VBus is not present. The 1-10 uF input capacitor is required as part of the USB specification. A typical value would be 2.2 uF to ensure the 1 uF minimum requirement is met even under voltage bias conditions.

In any case, extra components (such as a ferrite bead and diodes) may be required for EMC compliance and ESD protection. Different wiring is required for USB-host and USB-OTG.

#### 10.2 Logical Core Requirements

The XMOS XUD software component runs in a single logical core with endpoint and application cores communicating with it via a combination of channel communication and shared memory variables.

Each IN (host requests data from device) or OUT (data transferred from host to device) endpoint requires one logical core.

## 11 RGMII

The device has a series of pins that are dedicated to communicate with an RGMII PHY, as per the RGMII v1.3 spec. This can be used to communicate with GBit Ethernet PHYs. The pins and functions are listed in Figure 13. When RGMII mode is enabled (using processor status register 2) these pins can no longer be used as GPIO pins, and will instead be driven directly from an RGMII block that provides DDR to SDR conversion, which in turn is interfaced to a set of ports on Tile 1.

|    | Pin   | RGMII Fi | inction                   |

|----|-------|----------|---------------------------|

|    | X1D40 | TX3      | Transmit bit 3            |

|    | X1D41 | TX2      | Transmit bit 2            |

|    | X1D42 | TX1      | Transmit bit 1            |

|    | X1D43 | TX0      | Transmit bit 0            |

|    | X1D26 | TX_CLK   | Receive clock (125 MHz)   |

|    | X1D27 | TX_CTL   | Transmit data valid/error |

|    | X1D28 | RX_CLK   | Receive clock (125 MHz)   |

|    | X1D29 | RX_CTL   | Receive data valid/error  |

| _  | X1D30 | RX0      | Receive bit 0             |

| 3: | X1D31 | RX1      | Receive bit 1             |

| ck | X1D32 | RX2      | Receive bit 2             |

| ıs | X1D33 | RX3      | Receive bit 3             |

Figure 13 RGMII block pin functions

20

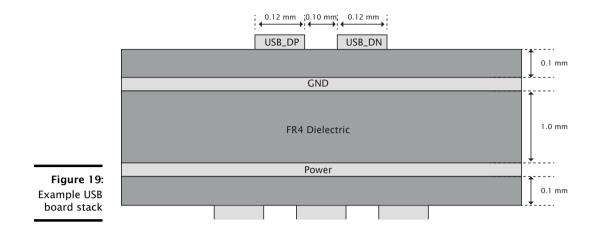

For best results, most of the routing should be done on the top layer (assuming the USB connector and XS2-UEF16A-512-FB236 are on the top layer) closest to GND. Reference planes should be below the transmission lines in order to maintain control of the trace impedance.

We recommend that the high-speed clock and high-speed USB differential pairs are routed first before any other routing. When routing high speed USB signals, the following guidelines should be followed:

- ▶ High speed differential pairs should be routed together.

- ▶ High-speed USB signal pair traces should be trace-length matched. Maximum trace-length mismatch should be no greater than 4mm.

- Ensure that high speed signals (clocks, USB differential pairs) are routed as far away from off-board connectors as possible.

- ▶ High-speed clock and periodic signal traces that run parallel should be at least 1.27mm away from USB\_DP/USB\_DN (see Figure 18).

- Low-speed and non-periodic signal traces that run parallel should be at least 0.5mm away from USB\_DP/USB\_DN (see Figure 18).

- ▶ Route high speed USB signals on the top of the PCB wherever possible.

- Route high speed USB traces over continuous power planes, with no breaks. If a trade-off must be made, changing signal layers is preferable to crossing plane splits.

- Follow the  $20 \times h$  rule; keep traces  $20 \times h$  (the height above the power plane) away from the edge of the power plane.

- ▶ Use a minimum of vias in high speed USB traces.

25

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

control-token

24-bit response

16-bit

32-bit

control-token

192

channel-end identifier

register number

data

1

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.4 Accessing a register of an analogue peripheral

Peripheral registers can be accessed through the interconnect using the functions write\_periph\_32(device, peripheral, ...), read\_periph\_32(device, peripheral, ...)  $\leftrightarrow$ , write\_periph\_8(device, peripheral, ...), and read\_periph\_8(device, peripheral  $\leftrightarrow$ , ...); where device is the name of the analogue device, and peripheral is the number of the peripheral. These functions implement the protocols described below.

A channel-end should be allocated to communicate with the configuration registers. The destination of the channel-end should be set to 0xnnnnpp02 where nnnn is the node-identifier and pp is the peripheral identifier.

A write message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | data | control-token |

|---------------|------------------------|-----------------|-------|------|---------------|

| 36            | channel-end identifier | register number | size  |      | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | control-token |

|---------------|------------------------|-----------------|-------|---------------|

| 37            | channel-end identifier | register number | size  | 1             |

The response to the read message comprises either control token 3, data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

| 0x12:     | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| Debug SSP | 31:0 | DRW  |      | Value.      |

#### **B.15 DGETREG operand 1: 0x13**

The resource ID of the logical core whose state is to be read.

| 0x13:     | Bits | Perm | Init | Description              |

|-----------|------|------|------|--------------------------|

| DGETREG   | 31:8 | RO   | -    | Reserved                 |

| operand 1 | 7:0  | DRW  |      | Thread number to be read |

#### B.16 DGETREG operand 2: 0x14

Register number to be read by DGETREG

**0x14:** DGETREG operand 2

| Bits | Perm | Init | Description                |

|------|------|------|----------------------------|

| 31:5 | RO   | -    | Reserved                   |

| 4:0  | DRW  |      | Register number to be read |

## B.17 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

| Bits  | Perm | Init | Description                                                                                                                                                                                                              |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 17:16 | DRW  |      | Number of the hardware breakpoint/watchpoint which caused<br>the interrupt (always 0 for =HOST= and =DCALL=). If multiple<br>breakpoints/watchpoints trigger at once, the lowest number is<br>taken.                     |

| 15:8  | DRW  |      | Number of thread which caused the debug interrupt (always 0 in the case of =HOST=).                                                                                                                                      |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point |

0x15: Debug interrupt type

|                | Bits  | Perm | Init | Description                                        |

|----------------|-------|------|------|----------------------------------------------------|

|                | 31:24 | CRO  |      | Processor ID of this XCore.                        |

| 0x00:          | 23:16 | CRO  |      | Number of the node in which this XCore is located. |

| Device         | 15:8  | CRO  |      | XCore revision.                                    |

| identification | 7:0   | CRO  |      | XCore version.                                     |

#### C.2 xCORE Tile description 1: 0x01

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

| Bits  | Perm | Init | Description              |

|-------|------|------|--------------------------|

| 31:24 | CRO  |      | Number of channel ends.  |

| 23:16 | CRO  |      | Number of the locks.     |

| 15:8  | CRO  |      | Number of synchronisers. |

| 7:0   | RO   | -    | Reserved                 |

#### C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02: xCORE Tile description 2

0x01: xCORE Tile description 1

|      | Bits  | Perm | Init | Description             |

|------|-------|------|------|-------------------------|

| x02: | 31:16 | RO   | -    | Reserved                |

| Tile | 15:8  | CRO  |      | Number of clock blocks. |

| on 2 | 7:0   | CRO  |      | Number of timers.       |

## C.4 Control PSwitch permissions to debug registers: 0x04

-XMOS-

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

|         |       | _    |      |                                                             |

|---------|-------|------|------|-------------------------------------------------------------|

|         | Bits  | Perm | Init | Description                                                 |

|         | 31    | CRO  |      | Disables write permission on this register                  |

|         | 30:15 | RO   | -    | Reserved                                                    |

|         | 14    | CRO  |      | Disable access to XCore's global debug                      |

|         | 13    | RO   | -    | Reserved                                                    |

|         | 12    | CRO  |      | lock all OTP sectors                                        |

|         | 11:8  | CRO  |      | lock bit for each OTP sector                                |

|         | 7     | CRO  |      | Enable OTP reduanacy                                        |

|         | 6     | RO   | -    | Reserved                                                    |

|         | 5     | CRO  |      | Override boot mode and read boot image from OTP             |

| -       | 4     | CRO  |      | Disable JTAG access to the PLL/BOOT configuration registers |

| у.<br>У | 3:1   | RO   | -    | Reserved                                                    |

| 1       | 0     | CRO  |      | Disable access to XCore's JTAG debug TAP                    |

0x07 Security configuration

#### C.8 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over the switch. This is the same set of registers as the Debug Scratch registers in the processor status.

0x20 .. 0x27: Debug scratch

| 0x27:<br>Debug | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| cratch         | 31:0 | CRW  |      | Value.      |

## C.9 PC of logical core 0: 0x40

Value of the PC of logical core 0.

0x40 PC of logical core 0

| <b>)x40:</b><br>gical | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| ore 0                 | 31:0 | CRO  |      | Value.      |

XMOS

## C.10 PC of logical core 1: 0x41

Value of the PC of logical core 1.

Bits

31:0

#### C.15 PC of logical core 6: 0x46

Value of the PC of logical core 6.

**0x46:** PC of logical core 6

Perm

Init

Description

CRO

Value.

#### C.16 PC of logical core 7: 0x47

Value of the PC of logical core 7.

0x47 PC of logical core 7

| 0x47:<br>gical | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ore 7          | 31:0 | CRO  |      | Value.      |

## C.17 SR of logical core 0: 0x60

Value of the SR of logical core 0

**0x60:** SR of logical core 0

| <b>0x60:</b><br>ogical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 0                  | 31:0 | CRO  |      | Value.      |

## C.18 SR of logical core 1: 0x61

Value of the SR of logical core 1

**0x61** SR of logical core 1

| 51:<br>al | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| 21        | 31:0 | CRO  |      | Value.      |

## C.19 SR of logical core 2: 0x62

Value of the SR of logical core 2

# **D** Node Configuration

The digital node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RO   | Device identification                 |

| 0x01      | RO   | System switch description             |

| 0x04      | RW   | Switch configuration                  |

| 0x05      | RW   | Switch node identifier                |

| 0x06      | RW   | PLL settings                          |

| 0x07      | RW   | System switch clock divider           |

| 0x08      | RW   | Reference clock                       |

| 0x09      | R    | System JTAG device ID register        |

| 0x0A      | R    | System USERCODE register              |

| 0x0C      | RW   | Directions 0-7                        |

| 0x0D      | RW   | Directions 8-15                       |

| 0x10      | RW   | DEBUG_N configuration, tile 0         |

| 0x11      | RW   | DEBUG_N configuration, tile 1         |

| 0x1F      | RO   | Debug source                          |

| 0x20 0x28 | RW   | Link status, direction, and network   |

| 0x40 0x47 | RO   | PLink status and network              |

| 0x80 0x88 | RW   | Link configuration and initialization |

| 0xA0 0xA7 | RW   | Static link configuration             |

Figure 35: Summary

## D.1 Device identification: 0x00

This register contains version and revision identifiers and the mode-pins as sampled at boot-time.

|             | Bits  | Perm | Init | Description                                       |

|-------------|-------|------|------|---------------------------------------------------|

|             | 31:24 | RO   | -    | Reserved                                          |

| 0x00:       | 23:16 | RO   |      | Sampled values of BootCtl pins on Power On Reset. |

| Device      | 15:8  | RO   |      | SSwitch revision.                                 |

| itification | 7:0   | RO   |      | SSwitch version.                                  |

-XMOS<sup>®</sup>

ident

| Bits  | Perm | Init | Description                                                                                 |  |

|-------|------|------|---------------------------------------------------------------------------------------------|--|

| 31:26 | RO   | -    | Reserved                                                                                    |  |

| 25:24 | RO   |      | Identify the SRC_TARGET type 0 - SLink, 1 - PLink, 2 - SSCTL, 3 - Undefine.                 |  |

| 23:16 | RO   |      | When the link is in use, this is the destination link number to which all packets are sent. |  |

| 15:6  | RO   | -    | Reserved                                                                                    |  |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, reset as 0.                              |  |

| 3     | RO   | -    | Reserved                                                                                    |  |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                       |  |

| 1     | RO   |      | 1 when the dest side of the link is in use.                                                 |  |

| 0     | RO   |      | 1 when the source side of the link is in use.                                               |  |

**0x40 .. 0x47:** PLink status and network

#### D.17 Link configuration and initialization: 0x80 .. 0x88

These registers contain configuration and debugging information specific to external links. The link speed and width can be set, the link can be initialized, and the link status can be monitored. The registers control links 0..7.

| Bits  | Perm | Init | Description                                                                                                                                   |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | RW   |      | Write to this bit with '1' will enable the XLink, writing '0' will disable it. This bit controls the muxing of ports with overlapping xlinks. |

| 30    | RW   | 0    | 0: operate in 2 wire mode; 1: operate in 5 wire mode                                                                                          |

| 29:28 | RO   | -    | Reserved                                                                                                                                      |

| 27    | RO   |      | Rx buffer overflow or illegal token encoding received.                                                                                        |

| 26    | RO   | 0    | This end of the xlink has issued credit to allow the remote end to transmit                                                                   |

| 25    | RO   | 0    | This end of the xlink has credit to allow it to transmit.                                                                                     |

| 24    | WO   |      | Clear this end of the xlink's credit and issue a HELLO token.                                                                                 |

| 23    | WO   |      | Reset the receiver. The next symbol that is detected will be the first symbol in a token.                                                     |

| 22    | RO   | -    | Reserved                                                                                                                                      |

| 21:11 | RW   | 0    | Specify min. number of idle system clocks between two contin-<br>uous symbols witin a transmit token -1.                                      |

| 10:0  | RW   | 0    | Specify min. number of idle system clocks between two contin-<br>uous transmit tokens -1.                                                     |

0x80 .. 0x88: Link configuration and initialization

| 0x20:  |

|--------|

| Sticky |

| flags  |

|        |

| Bits | Perm | Init | Description               |

|------|------|------|---------------------------|

| 31:7 | RO   | -    | Reserved                  |

| 6:0  | RW   | 0    | Stickyness for each flag. |

#### F.10 UIFM port masks: 0x24

Set of masks that identify how port 1N, port 1O and port 1P are affected by changes to the flags in  $\ensuremath{\mathsf{FLAGS}}$

| Bits  | Perm | Init | Description                                                                                                                                         |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1?. If any flag listed in this bitmask is high, port 1? will be high. |

| 23:16 | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1P. If any flag listed in this bitmask is high, port 1P will be high. |

| 15:8  | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 10. If any flag listed in this bitmask is high, port 10 will be high. |

| 7:0   | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1N. If any flag listed in this bitmask is high, port 1N will be high. |

**0x24:** UIFM port masks

## F.11 UIFM SOF value: 0x28

USB Start-Of-Frame counter

**0x28:** UIFM SOF value

| Bits  | Perm | Init | Description                             |

|-------|------|------|-----------------------------------------|

| 31:11 | RO   | -    | Reserved                                |

| 10:8  | RW   | 0    | Most significant 3 bits of SOF counter  |

| 7:0   | RW   | 0    | Least significant 8 bits of SOF counter |

-XMOS

## F.12 UIFM PID: 0x2C

The last USB packet identifier received

# H Schematics Design Check List

✓ This section is a checklist for use by schematics designers using the XEF216-512-FB236. Each of the following sections contains items to check for each design.

#### H.1 Power supplies

- □ VDDIO and OTP\_VCC supply is within specification before the VDD (core) supply is turned on. Specifically, the VDDIO and OTP\_VCC supply is within specification before VDD (core) reaches 0.4V (Section 13).

- The VDD (core) supply ramps monotonically (rises constantly) from 0V to its final value (0.95V 1.05V) within 10ms (Section 13).

- The VDD (core) supply is capable of supplying 700 mA (Section 13 and Figure 21).

- PLL\_AVDD is filtered with a low pass filter, for example an RC filter, see Section 13

#### H.2 Power supply decoupling

- The design has multiple decoupling capacitors per supply, for example at least four0402 or 0603 size surface mount capacitors of 100nF in value, per supply (Section 13).

- A bulk decoupling capacitor of at least 10uF is placed on each supply (Section 13).

#### H.3 Power on reset

□ The RST\_N and TRST\_N pins are asserted (low) during or after power up. The device is not used until these resets have taken place.

#### H.4 Clock

- The CLK input pin is supplied with a clock with monotonic rising edges and low jitter.

- Pins MODE0 and MODE1 are set to the correct value for the chosen oscillator frequency. The MODE settings are shown in the Oscillator section, Section 7. If you have a choice between two values, choose the value with the highest multiplier ratio since that will boot faster.

# J Associated Design Documentation

| Document Title                                   | Information                               | Document Number |

|--------------------------------------------------|-------------------------------------------|-----------------|

| Estimating Power Consumption For XS1-UEF Devices | Power consumption                         |                 |

| Programming XC on XMOS Devices                   | Timers, ports, clocks, cores and channels | X9577           |

| xTIMEcomposer User Guide                         | Compilers, assembler and linker/mapper    | X3766           |

|                                                  | Timing analyzer, xScope, debugger         |                 |

|                                                  | Flash and OTP programming utilities       |                 |

# **K** Related Documentation

| Document Title                                    | Information                         | Document Number |

|---------------------------------------------------|-------------------------------------|-----------------|

| The XMOS XS1 Architecture                         | ISA manual                          | X7879           |

| XS1 Port I/O Timing                               | Port timings                        | X5821           |

| xCONNECT Architecture                             | Link, switch and system information | X4249           |

| XS1-UEF Link Performance and Design<br>Guidelines | Link timings                        |                 |

| XS1-UEF Clock Frequency Control                   | Advanced clock control              |                 |

77