Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 12                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg16e1ctg |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Section Number                        | Title                                      | Page  |

|---------------------------------------|--------------------------------------------|-------|

| 13.5 Initialization/Application Infor | mation                                     |       |

| Serial Com                            | Chapter 14<br>munications Interface (S08S0 | CIV4) |

|                                       |                                            |       |

|                                       |                                            |       |

|                                       |                                            |       |

|                                       |                                            |       |

|                                       |                                            |       |

|                                       | ers (SCIBDH, SCIBDL)                       |       |

|                                       | 1 (SCIC1)                                  |       |

|                                       | 2 (SCIC2)                                  |       |

|                                       | (SCIS1)                                    |       |

| 14.2.5 SCI Status Register 2          | (SCIS2)                                    |       |

| 14.2.6 SCI Control Register           | 3 (SCIC3)                                  |       |

| 14.2.7 SCI Data Register (SC          | CID)                                       |       |

| 14.3 Functional Description           |                                            |       |

| 14.3.1 Baud Rate Generation           |                                            |       |

| 14.3.2 Transmitter Functiona          | 1 Description                              |       |

| 14.3.3 Receiver Functional D          | Description                                |       |

| 14.3.4 Interrupts and Status I        | Flags                                      |       |

|                                       | ons                                        |       |

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

| 15.1 | Introduction                                 |     |

|------|----------------------------------------------|-----|

|      | 15.1.1 Features                              |     |

|      | 15.1.2 Block Diagrams                        | 227 |

|      | 15.1.3 SPI Baud Rate Generation              |     |

| 15.2 | External Signal Description                  |     |

|      | 15.2.1 SPSCK — SPI Serial Clock              |     |

|      | 15.2.2 MOSI — Master Data Out, Slave Data In |     |

|      | 15.2.3 MISO — Master Data In, Slave Data Out |     |

|      | 15.2.4 $\overline{SS}$ — Slave Select        |     |

| 15.3 | Modes of Operation                           |     |

|      | 15.3.1 SPI in Stop Modes                     |     |

| 15.4 | Register Definition                          | 231 |

|      | 15.4.1 SPI Control Register 1 (SPIC1)        | 231 |

|      | 15.4.2 SPI Control Register 2 (SPIC2)        | 232 |

|      | 15.4.3 SPI Baud Rate Register (SPIBR)        | 233 |

|      | 15.4.4 SPI Status Register (SPIS)            |     |

|      | 15.4.5 SPI Data Register (SPID)              |     |

|      |                                              |     |

# Chapter 3 Modes of Operation

## 3.1 Introduction

The operating modes of the MC9S08SG32 Series are described in this chapter. Entry into each mode, exit from each mode, and functionality while in each of the modes are described.

### 3.2 Features

- Active background mode for code development

- Wait mode CPU shuts down to conserve power; system clocks are running and full regulation is maintained

- Stop modes System clocks are stopped and voltage regulator is in standby

- Stop3 All internal circuits are powered for fast recovery

- Stop2 Partial power down of internal circuits, RAM content is retained

## 3.3 Run Mode

This is the normal operating mode for the MC9S08SG32 Series. This mode is selected upon the MCU exiting reset if the BKGD/MS pin is high. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at 0xFFFE–0xFFFF after reset.

# 3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the HCS08 core. The BDC, together with the on-chip debug module (DBG), provide the means for analyzing MCU operation during software development.

Active background mode is entered in any of the following ways:

- When the BKGD/MS pin is low during POR or immediately after issuing a background debug force reset (see Section 5.7.2, "System Background Debug Force Reset Register (SBDFR)")

- When a BACKGROUND command is received through the BKGD/MS pin

- When a BGND instruction is executed

- When encountering a BDC breakpoint

- When encountering a DBG breakpoint

After entering active background mode, the CPU is held in a suspended state waiting for serial background commands rather than executing instructions from the user application program.

#### **Chapter 4 Memory**

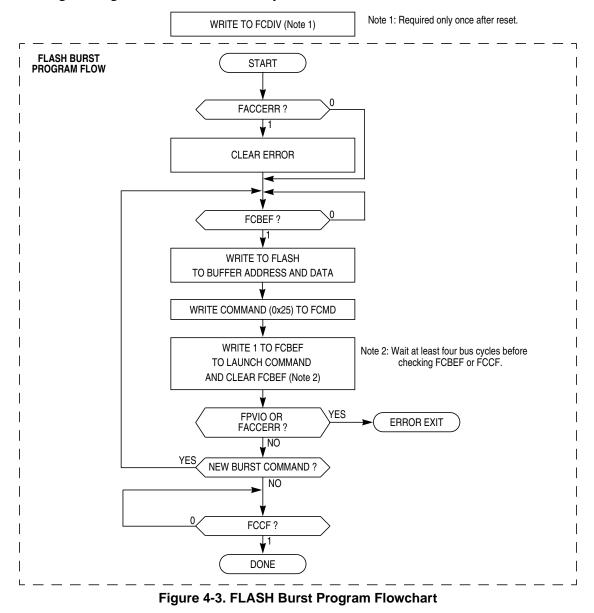

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst program time provided that the conditions above are met. In the case the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

The status flag corresponding to the interrupt source must be acknowledged (cleared) before returning from the ISR. Typically, the flag is cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

### 5.5.2 Interrupt Vectors, Sources, and Local Masks

Table 5-2 provides a summary of all interrupt sources. Higher-priority sources are located toward the bottom of the table. The high-order byte of the address for the interrupt service routine is located at the first address in the vector address column, and the low-order byte of the address for the interrupt service routine is located at the next higher address.

When an interrupt condition occurs, an associated flag bit becomes set. If the associated local interrupt enable is 1, an interrupt request is sent to the CPU. Within the CPU, if the global interrupt mask (I bit in the CCR) is 0, the CPU will finish the current instruction; stack the PCL, PCH, X, A, and CCR CPU registers; set the I bit; and then fetch the interrupt vector for the highest priority pending interrupt. Processing then continues in the interrupt service routine.

# Chapter 7 Central Processor Unit (S08CPUV3)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

### 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

### 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

## 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

### 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

### 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

#### Chapter 7 Central Processor Unit (S08CPUV3)

| Source                                                                                                          | Or constituer                                                                                                                                                                                      | ess<br>de                                           |                                                                                  | es                              | Cyc-by-Cyc                                                | Affecton CCR          |           |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------|-----------------------|-----------|--|

| Form                                                                                                            | Operation                                                                                                                                                                                          | Operation S ap o D bject Cod                        |                                                                                  | Cycles                          | Details                                                   | <b>V</b> 1 1 <b>H</b> | INZC      |  |

| INC opr8a<br>INCA<br>INCX<br>INC oprx8,X<br>INC ,X<br>INC oprx8,SP                                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                               | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C dd<br>4C<br>5C<br>6C ff<br>7C<br>9E 6C ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp                     | ↓11-                  | - ↓ ↓ -   |  |

| JMP opr8a<br>JMP opr16a<br>JMP oprx16,X<br>JMP oprx8,X<br>JMP ,X                                                | Jump<br>PC ← Jump Address                                                                                                                                                                          | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC dd<br>CC hh ll<br>DC ee ff<br>EC ff<br>FC                                     | 3<br>4<br>4<br>3<br>3           | 900<br>900<br>9000<br>9000<br>9000<br>9000<br>9000        | - 1 1 -               |           |  |

| JSR opr8a<br>JSR opr16a<br>JSR oprx16,X<br>JSR oprx8,X<br>JSR ,X                                                | Jump to Subroutine<br>PC $\leftarrow$ (PC) + n (n = 1, 2, or 3)<br>Push (PCL); SP $\leftarrow$ (SP) – \$0001<br>Push (PCH); SP $\leftarrow$ (SP) – \$0001<br>PC $\leftarrow$ Unconditional Address | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD dd<br>CD hh ll<br>DD ee ff<br>ED ff<br>FD                                     | 5<br>6<br>5<br>5                | ssppp<br>pssppp<br>ssppp<br>ssppp                         | - 1 1 -               |           |  |

| LDA #opr8i<br>LDA opr8a<br>LDA opr16a<br>LDA oprx16,X<br>LDA oprx8,X<br>LDA ,X<br>LDA oprx16,SP<br>LDA oprx8,SP | Load Accumulator from Memory $A \leftarrow (M)$                                                                                                                                                    | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A6 ii<br>B6 dd<br>C6 hh ll<br>D6 ee ff<br>E6 ff<br>F6<br>9E D6 ee ff<br>9E E6 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp  | 011-                  | - \$ \$ - |  |

| LDHX #opr16i<br>LDHX opr8a<br>LDHX opr16a<br>LDHX ,X<br>LDHX oprx16,X<br>LDHX oprx8,X<br>LDHX oprx8,SP          | Load Index Register (H:X)<br>H:X ← (M:M + \$0001)                                                                                                                                                  | IMM<br>DIR<br>EXT<br>IX<br>IX2<br>IX1<br>SP1        | 45 jj kk<br>55 dd<br>32 hh 11<br>9E AE<br>9E BE ee ff<br>9E CE ff<br>9E FE ff    | 3<br>4<br>5<br>5<br>6<br>5<br>5 | ppp<br>rrpp<br>prrpp<br>prrfp<br>pprrpp<br>prrpp<br>prrpp | 011-                  | - ↓ ↓ -   |  |

| LDX #opr8i<br>LDX opr8a<br>LDX opr16a<br>LDX oprx16,X<br>LDX oprx8,X<br>LDX ,X<br>LDX oprx16,SP<br>LDX oprx8,SP | Load X (Index Register Low) from Memory $X \leftarrow (M)$                                                                                                                                         | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AE ii<br>BE dd<br>CE hh ll<br>DE ee ff<br>EE ff<br>FE<br>9E DE ee ff<br>9E EE ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp  | 011-                  | - \$ \$ - |  |

| LSL opr8a<br>LSLA<br>LSLX<br>LSL oprx8,X<br>LSL ,X<br>LSL oprx8,SP                                              | Logical Shift Left<br>                                                                                                                                                                             | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp                | ↓11-                  | - ↓ ↓ ↓   |  |

| LSR opr8a<br>LSRA<br>LSRX<br>LSR oprx8,X<br>LSR ,X<br>LSR oprx8,SP                                              | Logical Shift Right<br>0                                                                                                                                                                           | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34 dd<br>44<br>54<br>64 ff<br>74<br>9E 64 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp                | ↓11-                  | - 0 ‡ ‡   |  |

Table 7-2. Instruction Set Summary (Sheet 5 of 9)

#### Chapter 8 Analog Comparator 5-V (S08ACMPV3)

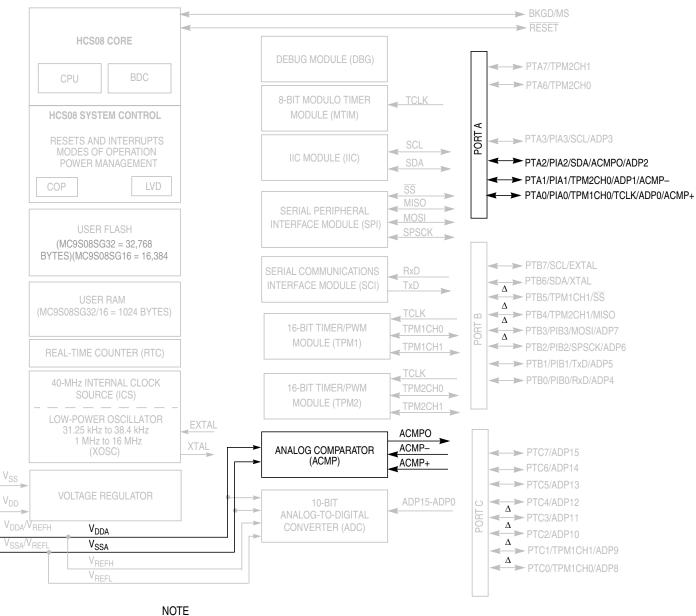

$\Delta$  = Pin can be enabled as part of the ganged output drive feature

#### Figure 8-1. MC9S08SG32 Series Block Diagram Highlighting ACMP Block and Pins

# Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

## 9.1 Introduction

The 10-bit analog-to-digital converter (ADC) is a successive approximation ADC designed for operation within an integrated microcontroller system-on-chip.

#### NOTE

- MC9S08SG32 Series devices operate at a higher voltage range (2.7 V to 5.5 V) and do not include stop1 mode. Please ignore references to stop1.

- MC9S08SG32 Series devices have up to 16 analog inputs. Consequently, the APCTL3 register is not available on these devices.

The ADC channel assignments, alternate clock function, and hardware trigger function are configured as described below for the MC9S08SG32 Series family of devices.

### 9.1.1 Channel Assignments

The ADC channel assignments for the MC9S08SG32 Series devices are shown in Table 9-1. Reserved channels convert to an unknown value. This chapter shows bits for all S08ADCV1 channels. MC9S08SG32 Series MCUs do not use all of these channels. All bits corresponding to channels that are not available on a device are reserved.

| ADCH  | Channel | Input      |

|-------|---------|------------|

| 00000 | AD0     | PTA0/AD0   |

| 00001 | AD1     | PTA1/ADP1  |

| 00010 | AD2     | PTA2/ADP2  |

| 00011 | AD3     | PTA3/ADP3  |

| 00100 | AD4     | PTB0/ADP4  |

| 00101 | AD5     | PTB1/ADP5  |

| 00110 | AD6     | PTB2/ADP6  |

| 00111 | AD7     | PTB3/ADP7  |

| 01000 | AD8     | PTC0/ADP8  |

| 01001 | AD9     | PTC1/ADP9  |

| 01010 | AD10    | PTC2/ADP10 |

| 01011 | AD11    | PTC3/ADP11 |

| 01100 | AD12    | PTC4/ADP12 |

| 01101 | AD13    | PTC5/ADP13 |

| 01110 | AD14    | PTC6/ADP14 |

#### Table 9-1. ADC Channel Assignment

| ADCH  | Channel           | Input                           |

|-------|-------------------|---------------------------------|

| 10000 | AD16              | V <sub>SS</sub>                 |

| 10001 | AD17              | V <sub>SS</sub>                 |

| 10010 | AD18              | V <sub>SS</sub>                 |

| 10011 | AD19              | V <sub>SS</sub>                 |

| 10100 | AD20              | V <sub>SS</sub>                 |

| 10101 | AD21              | V <sub>SS</sub>                 |

| 10110 | AD22              | Reserved                        |

| 10111 | AD23              | Reserved                        |

| 11000 | AD24              | Reserved                        |

| 11001 | AD25              | Reserved                        |

| 11010 | AD26              | Temperature Sensor <sup>1</sup> |

| 11011 | AD27              | Internal Bandgap <sup>2</sup>   |

| 11100 | -                 | Reserved                        |

| 11101 | V <sub>REFH</sub> | V <sub>DD</sub>                 |

| 11110 | V <sub>REFL</sub> | V <sub>SS</sub>                 |

the intermediate conversion data is lost. In 8-bit mode, there is no interlocking with ADCRH. If the MODE bits are changed, any data in ADCRL becomes invalid.

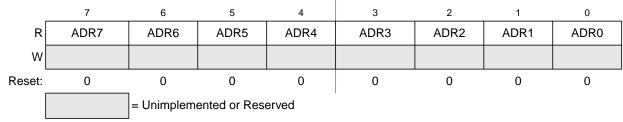

Figure 9-6. Data Result Low Register (ADCRL)

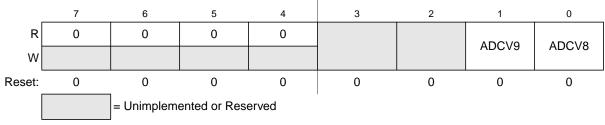

### 9.3.5 Compare Value High Register (ADCCVH)

In 10-bit mode, the ADCCVH register holds the upper two bits of the 10-bit compare value (ADCV[9:8]). When the compare function is enabled, these bits are compared to the upper two bits of the result following a conversion in 10-bit mode.

In 8-bit operation, ADCCVH is not used during compare.

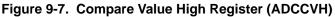

### 9.3.6 Compare Value Low Register (ADCCVL)

The ADCCVL register holds the lower eight bits of the 10-bit compare value or all eight bits of the 8-bit compare value. When the compare function is enabled, bits ADCV[7:0] are compared to the lower eight bits of the result following a conversion in 10-bit or 8-bit mode.

Figure 9-8. Compare Value Low Register (ADCCVL)

# 9.3.7 Configuration Register (ADCCFG)

ADCCFG selects the mode of operation, clock source, clock divide, and configures for low power and long sample time.

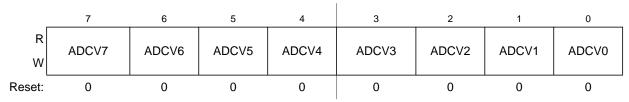

## 10.3.4 IIC Status Register (IICS)

#### Figure 10-6. IIC Status Register (IICS)

#### Table 10-7. IICS Field Descriptions

| Field                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>TCF                                                                                                                                                                                                                                                             | <ul> <li>Transfer Complete Flag. This bit is set on the completion of a byte transfer. This bit is only valid during or immediately following a transfer to the IIC module or from the IIC module. The TCF bit is cleared by reading the IICD register in receive mode or writing to the IICD in transmit mode.</li> <li>0 Transfer in progress</li> <li>1 Transfer complete</li> </ul>                                                   |  |  |  |  |  |

| 6<br>IAAS Addressed as a Slave. The IAAS bit is set when the calling address matches the programmed slave ad<br>or when the GCAEN bit is set and a general call is received. Writing the IICC register clears this bit.<br>0 Not addressed<br>1 Addressed as a slave |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 5<br>BUSY                                                                                                                                                                                                                                                            | <ul> <li>Bus Busy. The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set when a start signal is detected and cleared when a stop signal is detected.</li> <li>0 Bus is idle</li> <li>1 Bus is busy</li> </ul>                                                                                                                                                                              |  |  |  |  |  |

| 4<br>ARBL                                                                                                                                                                                                                                                            | <ul> <li>Arbitration Lost. This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by software by writing a 1 to it.</li> <li>0 Standard bus operation</li> <li>1 Loss of arbitration</li> </ul>                                                                                                                                                                                                 |  |  |  |  |  |

| 2<br>SRW                                                                                                                                                                                                                                                             | <ul> <li>Slave Read/Write. When addressed as a slave, the SRW bit indicates the value of the R/W command bit of the calling address sent to the master.</li> <li>0 Slave receive, master writing to slave</li> <li>1 Slave transmit, master reading from slave</li> </ul>                                                                                                                                                                 |  |  |  |  |  |

| 1<br>IICIF                                                                                                                                                                                                                                                           | <ul> <li>IIC Interrupt Flag. The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by writing a 1 to it in the interrupt routine. One of the following events can set the IICIF bit: <ul> <li>One byte transfer completes</li> <li>Match of slave address to calling address</li> <li>Arbitration lost</li> </ul> </li> <li>0 No interrupt pending <ul> <li>1 Interrupt pending</li> </ul> </li> </ul> |  |  |  |  |  |

| 0<br>RXAK                                                                                                                                                                                                                                                            | <ul> <li>Receive Acknowledge. When the RXAK bit is low, it indicates an acknowledge signal has been received after the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge signal is detected.</li> <li>0 Acknowledge received</li> <li>1 No acknowledge received</li> </ul>                                                                                                     |  |  |  |  |  |

Chapter 11 Internal Clock Source (S08ICSV2)

- CLKS bits are written to 00

- IREFS bit is written to 1

- RDIV bits are written to divide trimmed reference clock to be within the range of 31.25 kHz to 39.0625 kHz.

In FLL engaged internal mode, the ICSOUT clock is derived from the FLL clock, which is controlled by the internal reference clock. The FLL loop will lock the frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the internal reference clock is enabled.

### 11.4.1.2 FLL Engaged External (FEE)

The FLL engaged external (FEE) mode is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 0

- RDIV bits are written to divide reference clock to be within the range of 31.25 kHz to 39.0625 kHz

In FLL engaged external mode, the ICSOUT clock is derived from the FLL clock which is controlled by the external reference clock. The FLL loop will lock the frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the external reference clock is enabled.

### 11.4.1.3 FLL Bypassed Internal (FBI)

The FLL bypassed internal (FBI) mode is entered when all the following conditions occur:

- CLKS bits are written to 01

- IREFS bit is written to 1.

- BDM mode is active or LP bit is written to 0

In FLL bypassed internal mode, the ICSOUT clock is derived from the internal reference clock. The FLL clock is controlled by the internal reference clock, and the FLL loop will lock the FLL frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK will be available for BDC communications, and the internal reference clock is enabled.

### 11.4.1.4 FLL Bypassed Internal Low Power (FBILP)

The FLL bypassed internal low power (FBILP) mode is entered when all the following conditions occur:

- CLKS bits are written to 01

- IREFS bit is written to 1.

- BDM mode is not active and LP bit is written to 1

In FLL bypassed internal low power mode, the ICSOUT clock is derived from the internal reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications, and the internal reference clock is enabled.

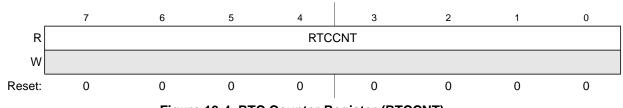

# 13.3.2 RTC Counter Register (RTCCNT)

RTCCNT is the read-only value of the current RTC count of the 8-bit counter.

Figure 13-4. RTC Counter Register (RTCCNT)

#### Table 13-4. RTCCNT Field Descriptions

| Field         | Description                                                                                                                                                                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCCNT | RTC Count. These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset, writing to RTCMOD, or writing different values to RTCLKS and RTCPS clear the count to 0x00. |

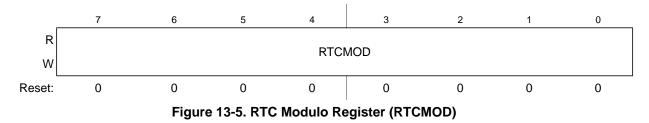

## 13.3.3 RTC Modulo Register (RTCMOD)

| Field         | Description                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCMOD | RTC Modulo. These eight read/write bits contain the modulo value used to reset the count to 0x00 upon a compare match and set the RTIF status bit. A value of 0x00 sets the RTIF bit on each rising edge of the prescaler output. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00. Reset sets the modulo to 0x00. |

## 13.4 Functional Description

The RTC is composed of a main 8-bit up-counter with an 8-bit modulo register, a clock source selector, and a prescaler block with binary-based and decimal-based selectable values. The module also contains software selectable interrupt logic.

After any MCU reset, the counter is stopped and reset to 0x00, the modulus register is set to 0x00, and the prescaler is off. The 1-kHz internal oscillator clock is selected as the default clock source. To start the prescaler, write any value other than zero to the prescaler select bits (RTCPS).

Three clock sources are software selectable: the low power oscillator clock (LPO), the external clock (ERCLK), and the internal clock (IRCLK). The RTC clock select bits (RTCLKS) select the desired clock source. If a different value is written to RTCLKS, the prescaler and RTCCNT counters are reset to 0x00.

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

# 15.1 Introduction

The serial peripheral interface (SPI) module provides for full-duplex, synchronous, serial communication between the MCU and peripheral devices. These peripheral devices can include other microcontrollers, analog-to-digital converters, shift registers, sensors, memories, and so forth.

The SPI runs at a baud rate up to that of the bus clock divided by two in master mode and bus clock divided by four in slave mode. The SPI operation can be interrupt driven or software can poll the status flags.

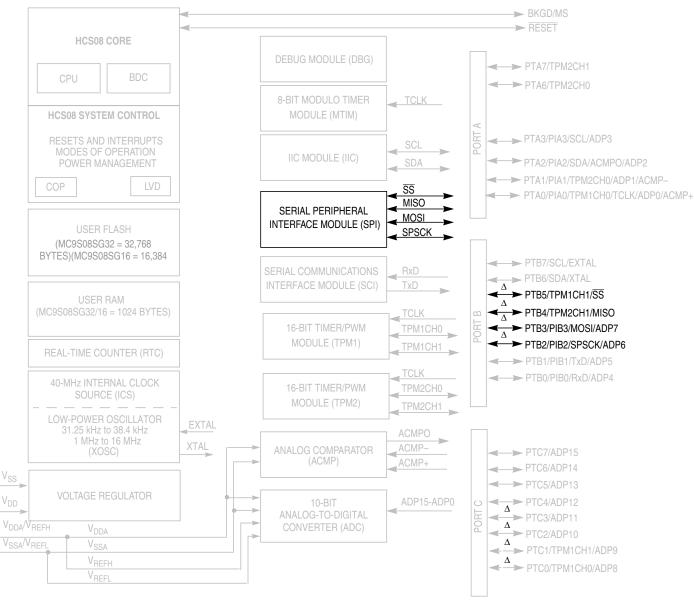

All devices in the MC9S08SG32 Series MCUs contain one SPI module, as shown in the following block diagram. Figure 15-1 shows the MC9S08SG32 Series block diagram with the SPI modules highlighted.

#### Chapter 15 Serial Peripheral Interface (S08SPIV3)

#### NOTE

- PTC7-PTC0 and PTA7-PTA6 are not available on 16-pin Packages

- PTC7-PTC4 and PTA7-PTA6 are not available on 20-pin Packages

- + For the 16-pin and 20-pin packages:  $V_{\mbox{DDA}}/V_{\mbox{REFH}}$  and  $V_{\mbox{SSA}}/V_{\mbox{REFL}}$  are

- double bonded to  $V_{\text{DD}}$  and  $V_{\text{SS}}$  respectively.

$\Delta$  = Pin can be enabled as part of the ganged output drive feature

#### Figure 15-1. MC9S08SG32 Series Block Diagram Highlighting SPI Block and Pin

|    |   |                                                                               |                                  |                                                                       |              |                  |              |      |          | mp<br>ted   |

|----|---|-------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------|--------------|------------------|--------------|------|----------|-------------|

| #  | с | C Characteristic                                                              | Symbol                           | Condition                                                             | Min          | Typ <sup>1</sup> | Max          | Unit | Standard | AEC Grade 0 |

| 9  | P | Input leakage current (per pin)                                               | I <sub>In</sub>                  | $V_{In} = V_{DD} \text{ or } V_{SS}$                                  | _            | —                | 1            | μA   | •        | —           |

|    |   | input leakage current (per pin)                                               | ['In]                            | temperature > 125<br>C                                                | —            | —                | 2            | μA   | —        | •           |

|    |   | Hi-Z (off-state) leakage current (per pin)                                    |                                  |                                                                       |              |                  |              |      |          |             |

|    | Ρ | input/output port pins                                                        | loz                              | V <sub>In</sub> = V <sub>DD</sub> or V <sub>SS</sub> ;<br>temperature | _            | —                | 1            | μA   | ٠        | _           |

| 10 |   | RESET                                                                         |                                  | $V_{In} = V_{DD} \text{ or } V_{SS}$                                  | _            | —                | 2            | μΑ   | ۲        | —           |

|    |   | Input/Output Port pins                                                        | •                                | $V_{In} = V_{DD} \text{ or } V_{SS};$<br>temperature > 125<br>C       | _            | 0.2              | 2            | μΑ   | _        | •           |

|    |   | Pullup or Pulldown <sup>2</sup> resistors;<br>when enabled                    |                                  |                                                                       |              |                  |              |      | ٠        | •           |

| 11 | Р |                                                                               | R <sub>PU</sub> ,R <sub>PD</sub> | _                                                                     | 17           | 37               | 52           | kΩ   | •        | •           |

|    | с | RESET <sup>3</sup>                                                            | R <sub>PU</sub>                  | —                                                                     | 17           | 37               | 52           | kΩ   | ٠        | •           |

|    |   | DC injection current <sup>4, 5, 6, 7</sup>                                    |                                  |                                                                       |              |                  |              |      | •        | •           |

|    |   | Single pin limit                                                              |                                  | $V_{IN} > V_{DD}$                                                     | 0            | —                | 2            | mA   | •        | •           |

| 12 | D |                                                                               | l <sub>IC</sub>                  | V <sub>IN</sub> < V <sub>SS</sub> ,                                   | 0            | —                | -0.2         | mA   | •        | •           |

|    |   | Total MCU limit,<br>includes                                                  |                                  | $V_{IN} > V_{DD}$                                                     | 0            | —                | 25           | mA   | ٠        | •           |

|    |   | sum of all stressed pins                                                      |                                  | V <sub>IN</sub> < V <sub>SS</sub> ,                                   | 0            |                  | -5           | mA   | •        | •           |

| 13 | D | Input Capacitance, all pins                                                   | C <sub>In</sub>                  | —                                                                     | —            | —                | 8            | pF   | •        | •           |

| 14 | D | RAM retention voltage                                                         | V <sub>RAM</sub>                 | —                                                                     | _            | 0.6              | 1.0          | V    | ٠        | •           |

| 15 | D | POR re-arm voltage <sup>8</sup>                                               | V <sub>POR</sub>                 | _                                                                     | 0.9          | 1.4              | 2.0          | V    | •        | •           |

| 16 | D | POR re-arm time <sup>9</sup>                                                  | t <sub>POR</sub>                 | —                                                                     | 10           | —                |              | μs   | •        | •           |

| 17 | Ρ | Low-voltage detection threshold<br>—<br>high range<br>V <sub>DD</sub> falling | V <sub>LVD1</sub>                | _                                                                     | 3.9<br>4.0   | 4.0<br>4.1       | 4.1<br>4.2   | V    | ٠        | _           |

|    |   | V <sub>DD</sub> rising                                                        |                                  | _                                                                     | 3.88<br>3.98 | 4.0<br>4.1       | 4.12<br>4.22 | V    |          | •           |

Table A-6. DC Characteristics (continued)

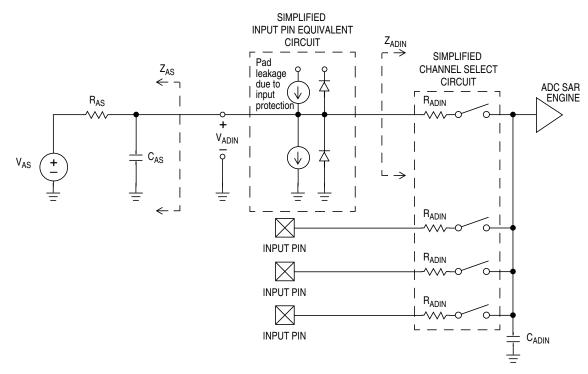

Figure A-9. ADC Input Impedance Equivalency Diagram

The following pages are mechanical specifications for MC9S08SG32 Series package options. See Table B-2 for the document number for each package type.

| Pin Count | Туре  | Designator | Document No. |

|-----------|-------|------------|--------------|

| 28        | TSSOP | TL         | 98ARS23923W  |

| 20        | TSSOP | TJ         | 98ASH70169A  |

| 16        | TSSOP | TG         | 98ASH70247A  |

#### Table B-2. Package Information

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 1-303-675-2140 Fax: 1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007-2010. All rights reserved.