Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                          |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 16                                                          |

| Program Memory Size        | 16KB (16K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 12x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                             |

| Supplier Device Package    | 20-TSSOP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08sg16e1ctj |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

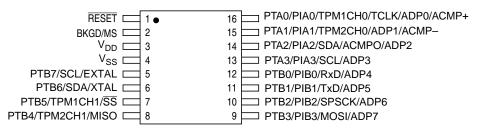

**Chapter 2 Pins and Connections**

## 4.5.5 Access Errors

An access error occurs whenever the command execution protocol is violated.

Any of the following specific actions will cause the access error flag (FACCERR) in FSTAT to be set. Before any command can be processed, write a 1 to FACCERR in FSTAT to clear the access error flag (FACCERR).

- Writing to a FLASH address before the internal FLASH clock frequency has been set by writing to the FCDIV register

- Writing to a FLASH address while FCBEF is not set (A new command cannot be started until the command buffer is empty.)

- Writing a second time to a FLASH address before launching the previous command (There is only one write to FLASH for every command.)

- Writing a second time to FCMD before launching the previous command (There is only one write to FCMD for every command.)

- Writing to any FLASH control register other than FCMD after writing to a FLASH address

- Writing any command code other than the five allowed codes (0x05, 0x20, 0x25, 0x40, or 0x41) to FCMD

- Writing any FLASH control register other than the write to FSTAT (to clear FCBEF and launch the command) after writing the command to FCMD

- The MCU enters stop mode while a program or erase command is in progress (The command is aborted.)

- Writing the byte program, burst program, or page erase command code (0x20, 0x25, or 0x40) with a background debug command while the MCU is secured (The background debug controller can only do blank check and mass erase commands when the MCU is secure.)

- Writing 0 to FCBEF to cancel a partial command

## 4.5.6 FLASH Block Protection

The block protection feature prevents the protected region of FLASH from program or erase changes. Block protection is controlled through the FLASH protection register (FPROT). When enabled, block protection begins at any 512 byte boundary below the last address of FLASH, 0xFFFF. (See Section 4.7.4, "FLASH Protection Register (FPROT and NVPROT)").

After exit from reset, FPROT is loaded with the contents of the NVPROT location, which is in the nonvolatile register block of the FLASH memory. FPROT cannot be changed directly from application software so a runaway program cannot alter the block protection settings. Because NVPROT is within the last 512 bytes of FLASH, if any amount of memory is protected, NVPROT is itself protected and cannot be altered (intentionally or unintentionally) by the application software. FPROT can be written through background debug commands, which allows a way to erase and reprogram a protected FLASH memory.

The block protection mechanism is illustrated in Figure 4-4. The FPS bits are used as the upper bits of the last address of unprotected memory. This address is formed by concatenating FPS7:FPS1 with logic 1 bits as shown. For example, to protect the last 1536 bytes of memory (addresses 0xFA00 through 0xFFFF), the FPS bits must be set to 1111 100, which results in the value 0xF9FF as the last address of unprotected

disengages security and the other three combinations engage security. Notice the erased state (1:1) makes the MCU secure. During development, whenever the FLASH is erased, it is good practice to immediately program the SEC00 bit to 0 in NVOPT so SEC01:SEC00 = 1:0. This would allow the MCU to remain unsecured after a subsequent reset.

The on-chip debug module cannot be enabled while the MCU is secure. The separate background debug controller can still be used for background memory access commands of unsecured resources.

A user can choose to allow or disallow a security unlocking mechanism through an 8-byte backdoor security key. If the nonvolatile KEYEN bit in NVOPT/FOPT is 0, the backdoor key is disabled and there is no way to disengage security without completely erasing all FLASH locations. If KEYEN is 1, a secure user program can temporarily disengage security by:

- 1. Writing 1 to KEYACC in the FCNFG register. This makes the FLASH module interpret writes to the backdoor comparison key locations (NVBACKKEY through NVBACKKEY+7) as values to be compared against the key rather than as the first step in a FLASH program or erase command.

- 2. Writing the user-entered key values to the NVBACKKEY through NVBACKKEY+7 locations. These writes must be done in order starting with the value for NVBACKKEY and ending with NVBACKKEY+7. STHX should not be used for these writes because these writes cannot be done on adjacent bus cycles. User software normally would get the key codes from outside the MCU system through a communication interface such as a serial I/O.

- 3. Writing 0 to KEYACC in the FCNFG register. If the 8-byte key that was just written matches the key stored in the FLASH locations, SEC01:SEC00 are automatically changed to 1:0 and security will be disengaged until the next reset.

The security key can be written only from secure memory (either RAM or FLASH), so it cannot be entered through background commands without the cooperation of a secure user program.

The backdoor comparison key (NVBACKKEY through NVBACKKEY+7) is located in FLASH memory locations in the nonvolatile register space so users can program these locations exactly as they would program any other FLASH memory location. The nonvolatile registers are in the same 512-byte block of FLASH as the reset and interrupt vectors, so block protecting that space also block protects the backdoor comparison key. Block protects cannot be changed from user application programs, so if the vector space is block protected, the backdoor security key mechanism cannot permanently change the block protect, security settings, or the backdoor key.

Security can always be disengaged through the background debug interface by taking these steps:

- 1. Disable any block protections by writing FPROT. FPROT can be written only with background debug commands, not from application software.

- 2. Mass erase FLASH if necessary.

- 3. Blank check FLASH. Provided FLASH is completely erased, security is disengaged until the next reset.

To avoid returning to secure mode after the next reset, program NVOPT so SEC01:SEC00 = 1:0.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>FACCERR | Access Error Flag — FACCERR is set automatically when the proper command sequence is not obeyed exactly (the erroneous command is ignored), if a program or erase operation is attempted before the FCDIV register has been initialized, or if the MCU enters stop while a command was in progress. For a more detailed discussion of the exact actions that are considered access errors, see Section 4.5.5, "Access Errors." FACCERR is cleared by writing a 1 to FACCERR. Writing a 0 to FACCERR has no meaning or effect.<br>0 No access error.<br>1 An access error has occurred. |

| 2<br>FBLANK  | <ul> <li>FLASH Verified as All Blank (erased) Flag — FBLANK is set automatically at the conclusion of a blank check command if the entire FLASH array was verified to be erased. FBLANK is cleared by clearing FCBEF to write a new valid command. Writing to FBLANK has no meaning or effect.</li> <li>0 After a blank check command is completed and FCCF = 1, FBLANK = 0 indicates the FLASH array is not completely erased.</li> <li>1 After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the FLASH array is completely erased (all 0xFF).</li> </ul>     |

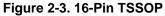

# 4.7.6 FLASH Command Register (FCMD)

Only five command codes are recognized in normal user modes as shown in Table 4-13. Refer to Section 4.5.3, "Program and Erase Command Execution," for a detailed discussion of FLASH programming and erase operations.

Figure 4-10. FLASH Command Register (FCMD)

| Command                     | FCMD | Equate File Label |  |  |

|-----------------------------|------|-------------------|--|--|

| Blank check                 | 0x05 | mBlank            |  |  |

| Byte program                | 0x20 | mByteProg         |  |  |

| Byte program — burst mode   | 0x25 | mBurstProg        |  |  |

| Page erase (512 bytes/page) | 0x40 | mPageErase        |  |  |

| Mass erase (all FLASH)      | 0x41 | mMassErase        |  |  |

Table 4-13. FLASH Commands

All other command codes are illegal and generate an access error.

It is not necessary to perform a blank check command after a mass erase operation. Only blank check is required as part of the security unlocking mechanism.

#### Table 5-3. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>ILAD | Illegal Address — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.         0       Reset not caused by an illegal address         1       Reset caused by an illegal address                              |

| 1<br>LVD  | <ul> <li>Low Voltage Detect — If the LVDRE bit is set and the supply drops below the LVD trip voltage, an LVD reset will occur. This bit is also set by POR.</li> <li>0 Reset not caused by LVD trip or POR.</li> <li>1 Reset caused by LVD trip or POR.</li> </ul> |

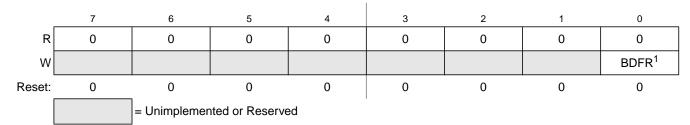

### 5.7.2 System Background Debug Force Reset Register (SBDFR)

This high page register contains a single write-only control bit. A serial background command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

<sup>1</sup> BDFR is writable only through serial background debug commands, not from user programs.

### Figure 5-3. System Background Debug Force Reset Register (SBDFR)

#### Table 5-4. SBDFR Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>BDFR | <b>Background Debug Force Reset</b> — A serial background command such as WRITE_BYTE can be used to allow an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |

**Chapter 6 Parallel Input/Output Control**

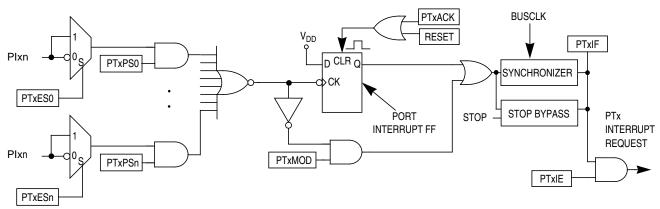

# 6.4 Pin Interrupts

Port A[3:0] and port B[3:0] pins can be configured as external interrupt inputs and as an external means of waking the MCU from stop3 or wait low-power modes.

The block diagram for the pin interrupts is shown.

Figure 6-2. Pin Interrupt Block Diagram

Writing to the PTxPSn bits in the port interrupt pin enable register (PTxPS) independently enables or disables each port pin interrupt. Each port can be configured as edge sensitive or edge and level sensitive based on the PTxMOD bit in the port interrupt status and control register (PTxSC). Edge sensitivity can be software programmed to be either falling or rising; the level can be either low or high. The polarity of the edge or edge and level sensitivity is selected using the PTxESn bits in the port interrupt edge select register (PTxES).

Synchronous logic is used to detect edges. Prior to detecting an edge, enabled pin interrupt inputs must be at the deasserted logic level. A falling edge is detected when an enabled port input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle. A rising edge is detected when the input signal is seen as a logic 0 during one bus cycle and then a logic 1 during the next cycle.

## 6.4.1 Edge-Only Sensitivity

A valid edge on an enabled pin interrupt sets PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request is presented to the CPU. To clear PTxIF, write a 1 to PTxACK in PTxSC.

### NOTE

If a pin is enabled for interrupt on edge-sensitive only, a falling (or rising) edge on the pin does not latch an interrupt request if another pin interrupt is already asserted.

To prevent losing an interrupt request on one pin because another pin is asserted, software can disable the asserted pin interrupt while having the unasserted pin interrupt enabled. The asserted status of a pin is reflected by its associated I/O general purpose data register.

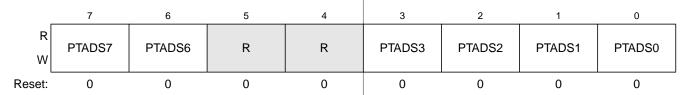

### 6.6.1.5 Port A Drive Strength Selection Register (PTADS)

Figure 6-7. Drive Strength Selection for Port A Register (PTADS)

### Table 6-6. PTADS Register Field Descriptions

| Field                         | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5,3:0<br>PTADS[7:5,<br>3:0] | <ul> <li>Output Drive Strength Selection for Port A Bits — Each of these control bits selects between low and high output drive for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port A bit n.</li> <li>1 High output drive strength selected for port A bit n.</li> </ul> |

| 5:4<br>Reserved               | <b>Reserved Bits</b> — These bits are unused on this MCU, writes have no affect and could read as 1s or 0s.                                                                                                                                                                                                                                                                       |

## 6.6.1.6 Port A Interrupt Status and Control Register (PTASC)

|        | 7 | 6 | 5 | 4 | 3     | 2      | 1     | 0      |

|--------|---|---|---|---|-------|--------|-------|--------|

| R      | 0 | 0 | 0 | 0 | PTAIF | 0      | PTAIE | PTAMOD |

| w      |   |   |   |   |       | PTAACK | FIAIC |        |

| Reset: | 0 | 0 | 0 | 0 | 0     | 0      | 0     | 0      |

Figure 6-8. Port A Interrupt Status and Control Register (PTASC)

#### Table 6-7. PTASC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PTAIF  | <ul> <li>Port A Interrupt Flag — PTAIF indicates when a port A interrupt is detected. Writes have no effect on PTAIF.</li> <li>0 No port A interrupt detected.</li> <li>1 Port A interrupt detected.</li> </ul>                         |

| 2<br>PTAACK | <b>Port A Interrupt Acknowledge</b> — Writing a 1 to PTAACK is part of the flag clearing mechanism. PTAACK always reads as 0.                                                                                                           |

| 1<br>PTAIE  | <ul> <li>Port A Interrupt Enable — PTAIE determines whether a port A interrupt is enabled.</li> <li>0 Port A interrupt request not enabled.</li> <li>1 Port A interrupt request enabled.</li> </ul>                                     |

| 0<br>PTAMOD | <ul> <li>Port A Detection Mode — PTAMOD (along with the PTAES bits) controls the detection mode of the port A interrupt pins.</li> <li>0 Port A pins detect edges only.</li> <li>1 Port A pins detect both edges and levels.</li> </ul> |

| Source         |                                                                                                          | Address<br>Mode      | Object Code    | Cycles | Cyc-by-Cyc<br>Details | Affecton CCR          |         |  |

|----------------|----------------------------------------------------------------------------------------------------------|----------------------|----------------|--------|-----------------------|-----------------------|---------|--|

| Form           | Operation                                                                                                |                      |                |        |                       | <b>V</b> 1 1 <b>H</b> | INZC    |  |

| BCC rel        | Branch if Carry Bit Clear<br>(if C = 0)                                                                  | REL                  | 24 rr          | 3      | qqq                   | - 1 1 -               |         |  |

|                |                                                                                                          | DIR (b0)<br>DIR (b1) | 11 dd          | 5<br>5 | rfwpp                 |                       |         |  |

|                |                                                                                                          | DIR (b1)             | 13 dd<br>15 dd | 5      | rfwpp<br>rfwpp        |                       |         |  |

|                | Clear Bit n in Memory                                                                                    | DIR (b2)             | 15 dd<br>17 dd | 5      | rfwpp                 |                       |         |  |

| BCLR n,opr8a   | $(Mn \leftarrow 0)$                                                                                      | DIR (b3)             | 19 dd          | 5      | rfwpp                 | - 1 1 -               |         |  |

|                |                                                                                                          | DIR (b5)             | 19 dd<br>1B dd | 5      | rfwpp                 |                       |         |  |

|                |                                                                                                          | DIR (b6)             | 1D dd<br>1D dd | 5      | rfwpp                 |                       |         |  |

|                |                                                                                                          | DIR (b7)             | 1F dd          | 5      | rfwpp                 |                       |         |  |

| BCS rel        | Branch if Carry Bit Set (if C = 1)(Same as BLO)                                                          | REL                  | 25 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BEQ rel        | Branch if Equal (if Z = 1)                                                                               | REL                  | 27 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BGE rel        | Branch if Greater Than or Equal To (if $N \oplus V = 0$ ) (Signed)                                       | REL                  | 90 rr          | 3      | ppp                   | - 1 1 -               |         |  |

| BGND           | Enter active background if ENBDM=1<br>Waits for and processes BDM commands<br>until GO, TRACE1, or TAGGO | INH                  | 82             | 5+     | fpppp                 | - 1 1 -               |         |  |

| BGT rel        | Branch if Greater Than (if $Z \mid (N \oplus V) = 0$ )<br>(Signed)                                       | REL                  | 92 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BHCC rel       | Branch if Half Carry Bit Clear (if H = 0)                                                                | REL                  | 28 rr          | 3      | ppp                   | - 1 1 -               |         |  |

| BHCS rel       | Branch if Half Carry Bit Set (if H = 1)                                                                  | REL                  | 29 rr          | 3      | ppp                   | - 1 1 -               |         |  |

| BHI rel        | Branch if Higher (if C   Z = 0)                                                                          | REL                  | 22 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BHS rel        | Branch if Higher or Same (if C = 0) (Same as BCC)                                                        | REL                  | 24 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BIH rel        | Branch if IRQ Pin High (if IRQ pin = 1)                                                                  | REL                  | 2F rr          | 3      | ppp                   | - 1 1 -               |         |  |

| BIL rel        | Branch if IRQ Pin Low (if IRQ pin = 0)                                                                   | REL                  | 2E rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BIT #opr8i     |                                                                                                          | IMM                  | A5 ii          | 2      | pp                    |                       |         |  |

| BIT opr8a      |                                                                                                          | DIR                  | B5 dd          | 3      | rpp                   |                       |         |  |

| BIT opr16a     | Dit Teet                                                                                                 | EXT                  | C5 hh 11       | 4      | prpp                  |                       |         |  |

| BIT oprx16,X   | Bit Test<br>(A) & (M)(CCR Updated but Operands Not                                                       | IX2                  | D5 ee ff       | 4      | prpp                  | 011-                  | ↑ ↑     |  |

| BIT oprx8,X    | Changed)                                                                                                 | IX1                  | E5 ff          | 3      | rpp                   |                       | - + + - |  |

| BIT ,X         | Changed)                                                                                                 | IX                   | F5             | 3      | rfp                   |                       |         |  |

| BIT oprx16,SP  |                                                                                                          | SP2                  | 9E D5 ee ff    | 5      | pprpp                 |                       |         |  |

| BIT oprx8,SP   |                                                                                                          | SP1                  | 9E E5 ff       | 4      | prpp                  |                       |         |  |

| BLE rel        | Branch if Less Than or Equal To (if $Z \mid (N \oplus V) = 1$ ) (Signed)                                 | REL                  | 93 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BLO rel        | Branch if Lower (if $C = 1$ ) (Same as BCS)                                                              | REL                  | 25 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BLS rel        | Branch if Lower or Same (if $C \mid Z = 1$ )                                                             | REL                  | 23 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BLT rel        | Branch if Less Than (if $N \oplus V = 1$ ) (Signed)                                                      | REL                  | 91 rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BMC rel        | Branch if Interrupt Mask Clear (if I = 0)                                                                | REL                  | 2C rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BMI <i>rel</i> | Branch if Minus (if N = 1)                                                                               | REL                  | 2B rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BMS rel        | Branch if Interrupt Mask Set (if I = 1)                                                                  | REL                  | 2D rr          | 3      | qqq                   | - 1 1 -               |         |  |

| BNE rel        | Branch if Not Equal (if $Z = 0$ )                                                                        | REL                  | 26 rr          | 3      | qqq                   | - 1 1 -               |         |  |

Table 7-2. Instruction Set Summary (Sheet 2 of 9)

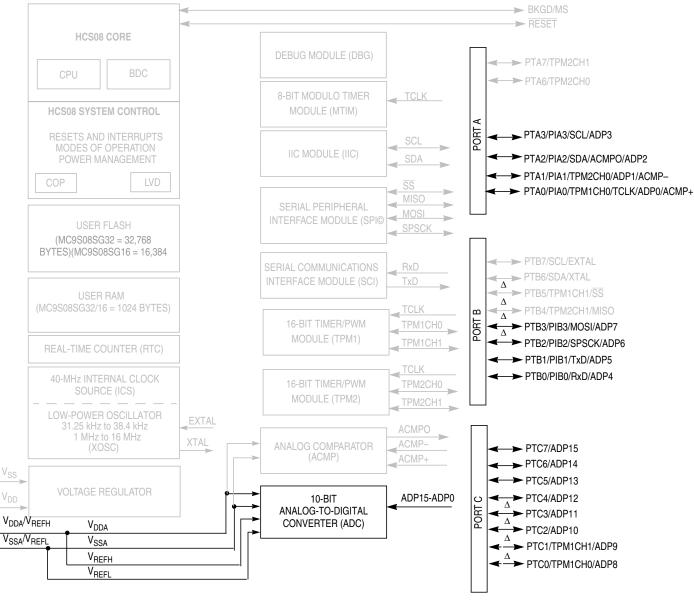

#### Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

#### NOTE

- PTC7-PTC0 and PTA7-PTA6 are not available on 16-pin packages.

- PTC7-PTC4 and PTA7-PTA6 are not available on 20-pin packages.

- + For the 16-pin and 20-pin packages:  $V_{\mbox{DDA}}/V_{\mbox{REFH}}$  and  $V_{\mbox{SSA}}/V_{\mbox{REFL}}$  are

- double bonded to  $V_{\text{DD}}$  and  $V_{\text{SS}}$  respectively.

- $\Delta$  = Pin can be enabled as part of the ganged output drive feature.

### Figure 9-1. MC9S08SG32 Series Block Diagram Highlighting ADC Block and Pins

MC9S08SG32 Data Sheet, Rev. 8

| Field      | Description                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC9 | <ul> <li>ADC Pin Control 9 — ADPC9 controls the pin associated with channel AD9.</li> <li>0 AD9 pin I/O control enabled</li> <li>1 AD9 pin I/O control disabled</li> </ul> |

| 0<br>ADPC8 | <ul> <li>ADC Pin Control 8 — ADPC8 controls the pin associated with channel AD8.</li> <li>0 AD8 pin I/O control enabled</li> <li>1 AD8 pin I/O control disabled</li> </ul> |

Table 9-11. APCTL2 Register Field Descriptions (continued)

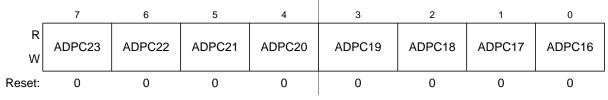

# 9.3.10 Pin Control 3 Register (APCTL3)

The pin control registers disable the digital interface to the associated MCU pins used as analog inputs to reduce digital noise and improve conversion accuracy. APCTL3 controls channels 16–23 of the ADC module. This register is not implemented on MCUs that do not have associated external analog inputs. Consult the ADC channel assignment in the module introduction for information on availability of this register.

Figure 9-12. Pin Control 3 Register (APCTL3)

| Field       | Description                                                                                                                                                                     |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>ADPC23 | <ul> <li>ADC Pin Control 23 — ADPC23 controls the pin associated with channel AD23.</li> <li>0 AD23 pin I/O control enabled</li> <li>1 AD23 pin I/O control disabled</li> </ul> |  |  |

| 6<br>ADPC22 | <ul> <li>ADC Pin Control 22 — ADPC22 controls the pin associated with channel AD22.</li> <li>0 AD22 pin I/O control enabled</li> <li>1 AD22 pin I/O control disabled</li> </ul> |  |  |

| 5<br>ADPC21 | <ul> <li>ADC Pin Control 21 — ADPC21 controls the pin associated with channel AD21.</li> <li>0 AD21 pin I/O control enabled</li> <li>1 AD21 pin I/O control disabled</li> </ul> |  |  |

| 4<br>ADPC20 | <ul> <li>ADC Pin Control 20 — ADPC20 controls the pin associated with channel AD20.</li> <li>0 AD20 pin I/O control enabled</li> <li>1 AD20 pin I/O control disabled</li> </ul> |  |  |

| 3<br>ADPC19 | <ul> <li>ADC Pin Control 19 — ADPC19 controls the pin associated with channel AD19.</li> <li>0 AD19 pin I/O control enabled</li> <li>1 AD19 pin I/O control disabled</li> </ul> |  |  |

| 2<br>ADPC18 | <ul> <li>ADC Pin Control 18 — ADPC18 controls the pin associated with channel AD18.</li> <li>0 AD18 pin I/O control enabled</li> <li>1 AD18 pin I/O control disabled</li> </ul> |  |  |

Chapter 10 Inter-Integrated Circuit (S08IICV2)

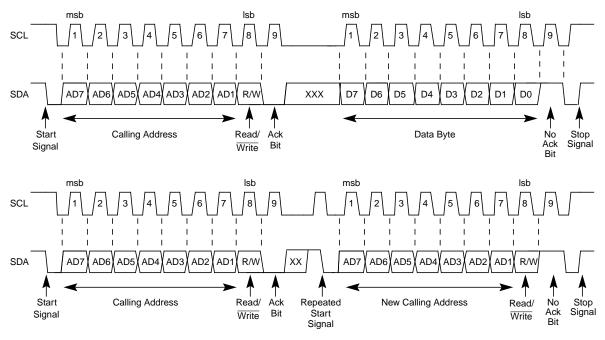

Figure 10-9. IIC Bus Transmission Signals

### 10.4.1.1 Start Signal

When the bus is free, no master device is engaging the bus (SCL and SDA lines are at logical high), a master may initiate communication by sending a start signal. As shown in Figure 10-9, a start signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

### 10.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the start signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a  $R/\overline{W}$  bit. The  $R/\overline{W}$  bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master responds by sending back an acknowledge bit. This is done by pulling the SDA low at the ninth clock (see Figure 10-9).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC reverts to slave mode and operates correctly even if it is being addressed by another master.

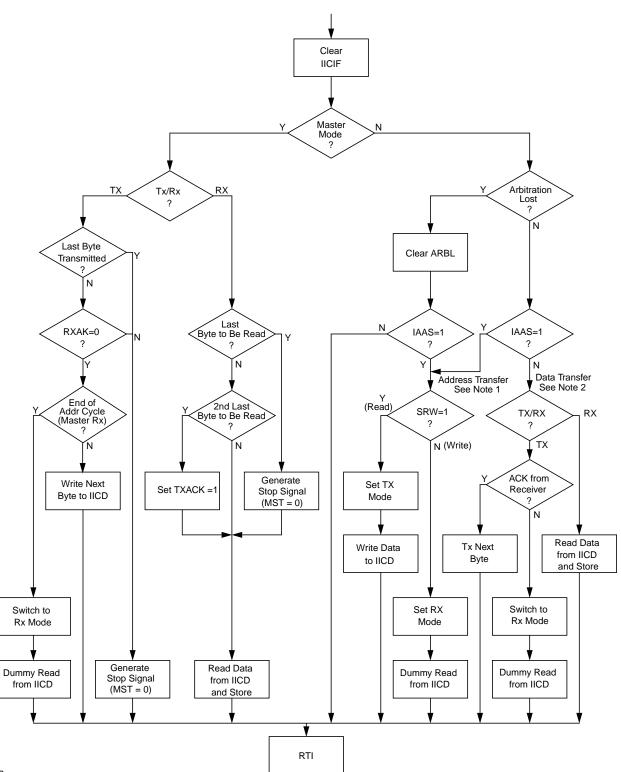

Chapter 10 Inter-Integrated Circuit (S08IICV2)

#### NOTES:

1. If general call is enabled, a check must be done to determine whether the received address was a general call address (0x00). If the received address was a general call address, then the general call must be handled by user software.

2. When 10-bit addressing is used to address a slave, the slave sees an interrupt following the first byte of the extended address. User software must ensure that for this interrupt, the contents of IICD are ignored and not treated as a valid data transfer

### Figure 10-12. Typical IIC Interrupt Routine

MC9S08SG32 Data Sheet, Rev. 8

## 11.1.2 Features

Key features of the ICS module follow. For device specific information, refer to the ICS Characteristics in the Electricals section of the documentation.

- Frequency-locked loop (FLL) is trimmable for accuracy using the internal 32 kHz reference over the specified temperature and voltage ranges

- 0.1% resolution using 9-bit TRIM:FTRIM

- 1.5% deviation for -40 °C to 125 °C standard-temperature rated devices

- 3% deviation for AEC Grade 0 high-temperature rated devices (-40 to 150 °C)

- Internal or external reference clocks up to 5 MHz can be used to control the FLL

- 3-bit select for reference divider is provided

- Internal reference clock has 9 trim bits available

- Internal or external reference clocks can be selected as the clock source for the MCU

- Whichever clock is selected as the source can be divided down

- 2-bit select for clock divider is provided

- Allowable dividers are: 1, 2, 4, 8

- BDC clock is provided as a constant divide by 2 of the DCO output

- Control signals for a low power oscillator as the external reference clock are provided — HGO, RANGE, EREFS, ERCLKEN, EREFSTEN

- FLL Engaged Internal mode is automatically selected out of reset

### 11.1.3 Block Diagram

Figure 11-2 is the ICS block diagram.

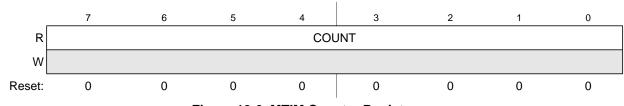

Chapter 12 Modulo Timer (S08MTIMV1)

# 12.3.3 MTIM Counter Register (MTIMCNT)

MTIMCNT is the read-only value of the current MTIM count of the 8-bit counter.

Figure 12-6. MTIM Counter Register

| Field | Description                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>MTIM Count</b> — These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset clears the count to \$00. |

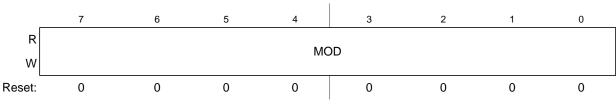

# 12.3.4 MTIM Modulo Register (MTIMMOD)

Figure 12-7. MTIM Modulo Register

| Field      | Description                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>MOD | <b>MTIM Modulo</b> — These eight read/write bits contain the modulo value used to reset the count and set TOF. A value of \$00 puts the MTIM in free-running mode. Writing to MTIMMOD resets the COUNT to \$00 and clears TOF. Reset sets the modulo to \$00. |

Chapter 14 Serial Communications Interface (S08SCIV4)

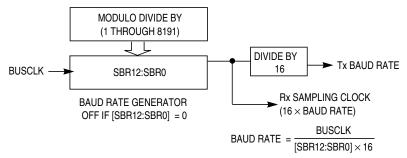

Figure 14-12. SCI Baud Rate Generation

SCI communications require the transmitter and receiver (which typically derive baud rates from independent clock sources) to use the same baud rate. Allowed tolerance on this baud frequency depends on the details of how the receiver synchronizes to the leading edge of the start bit and how bit sampling is performed.

The MCU resynchronizes to bit boundaries on every high-to-low transition, but in the worst case, there are no such transitions in the full 10- or 11-bit time character frame so any mismatch in baud rate is accumulated for the whole character time. For a Freescale Semiconductor SCI system whose bus frequency is driven by a crystal, the allowed baud rate mismatch is about 4.5percent for 8-bit data format and about 4 percent for 9-bit data format. Although baud rate modulo divider settings do not always produce baud rates that exactly match standard rates, it is normally possible to get within a few percent, which is acceptable for reliable communications.

## 14.3.2 Transmitter Functional Description

This section describes the overall block diagram for the SCI transmitter, as well as specialized functions for sending break and idle characters. The transmitter block diagram is shown in Figure 14-2.

The transmitter output (TxD) idle state defaults to logic high (TXINV = 0 following reset). The transmitter output is inverted by setting TXINV = 1. The transmitter is enabled by setting the TE bit in SCIC2. This queues a preamble character that is one full character frame of the idle state. The transmitter then remains idle until data is available in the transmit data buffer. Programs store data into the transmit data buffer by writing to the SCI data register (SCID).

The central element of the SCI transmitter is the transmit shift register that is either 10 or 11 bits long depending on the setting in the M control bit. For the remainder of this section, we will assume M = 0, selecting the normal 8-bit data mode. In 8-bit data mode, the shift register holds a start bit, eight data bits, and a stop bit. When the transmit shift register is available for a new SCI character, the value waiting in the transmit data register is transferred to the shift register (synchronized with the baud rate clock) and the transmit data register empty (TDRE) status flag is set to indicate another character may be written to the transmit data buffer at SCID.

If no new character is waiting in the transmit data buffer after a stop bit is shifted out the TxD pin, the transmitter sets the transmit complete flag and enters an idle mode, with TxD high, waiting for more characters to transmit.

Writing 0 to TE does not immediately release the pin to be a general-purpose I/O pin. Any transmit activity that is in progress must first be completed. This includes data characters in progress, queued idle characters, and queued break characters.

### 14.3.2.1 Send Break and Queued Idle

The SBK control bit in SCIC2 is used to send break characters which were originally used to gain the attention of old teletype receivers. Break characters are a full character time of logic 0 (10 bit times including the start and stop bits). A longer break of 13 bit times can be enabled by setting BRK13 = 1. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 1 and then write 0 to the SBK bit. This action queues a break character to be sent as soon as the shifter is available. If SBK is still 1 when the queued break moves into the shifter (synchronized to the baud rate clock), an additional break character is queued. If the receiving device is another Freescale Semiconductor SCI, the break characters will be received as 0s in all eight data bits and a framing error (FE = 1) occurs.

When idle-line wakeup is used, a full character time of idle (logic 1) is needed between messages to wake up any sleeping receivers. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 0 and then write 1 to the TE bit. This action queues an idle character to be sent as soon as the shifter is available. As long as the character in the shifter does not finish while TE = 0, the SCI transmitter never actually releases control of the TxD pin. If there is a possibility of the shifter finishing while TE = 0, set the general-purpose I/O controls so the pin that is shared with TxD is an output driving a logic 1. This ensures that the TxD line will look like a normal idle line even if the SCI loses control of the port pin between writing 0 and then 1 to TE.

The length of the break character is affected by the BRK13 and M bits as shown below.

| BRK13 | М | Break Character Length |

|-------|---|------------------------|

| 0     | 0 | 10 bit times           |

| 0     | 1 | 11 bit times           |

| 1     | 0 | 13 bit times           |

| 1     | 1 | 14 bit times           |

Table 14-8. Break Character Length

### 14.3.3 Receiver Functional Description

In this section, the receiver block diagram (Figure 14-3) is used as a guide for the overall receiver functional description. Next, the data sampling technique used to reconstruct receiver data is described in more detail. Finally, two variations of the receiver wakeup function are explained.

The receiver input is inverted by setting RXINV = 1. The receiver is enabled by setting the RE bit in SCIC2. Character frames consist of a start bit of logic 0, eight (or nine) data bits (LSB first), and a stop bit of logic 1. For information about 9-bit data mode, refer to Section 14.3.5.1, "8- and 9-Bit Data Modes." For the remainder of this discussion, we assume the SCI is configured for normal 8-bit data mode.

After receiving the stop bit into the receive shifter, and provided the receive data register is not already full, the data character is transferred to the receive data register and the receive data register full (RDRF) status

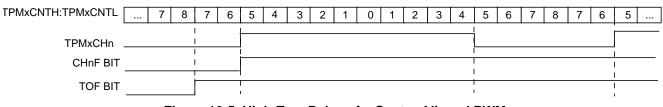

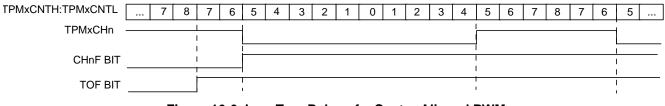

When the TPM is configured for center-aligned PWM (and ELSnB:ELSnA not = 0:0), the data direction for all channels in this TPM are overridden, the TPMxCHn pins are forced to be outputs controlled by the TPM, and the ELSnA bits control the polarity of each TPMxCHn output. If ELSnB:ELSnA=1:0, the corresponding TPMxCHn pin is cleared when the timer counter is counting up, and the channel value register matches the timer counter; the TPMxCHn pin is set when the timer counter is counting down, and the channel value register matches the timer counter. If ELSnA=1, the corresponding TPMxCHn pin is set when the timer counter; the TPMxCHn pin is cleared when the channel value register matches the timer counter is counting up and the channel value register matches the timer counter; the TPMxCHn pin is cleared when the timer counter is the timer counter; the timer counter is counting up and the channel value register matches the timer counter is counting the timer counter; the timer counter is counter is counter is counter; the timer counter is counter is counter is counter is counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

Figure 16-6. Low-True Pulse of a Center-Aligned PWM

**Chapter 17 Development Support**

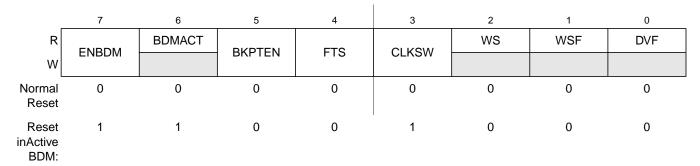

## 17.4.1.1 BDC Status and Control Register (BDCSCR)

This register can be read or written by serial BDC commands (READ\_STATUS and WRITE\_CONTROL) but is not accessible to user programs because it is not located in the normal memory map of the MCU.

= Unimplemented or Reserved

### Figure 17-5. BDC Status and Control Register (BDCSCR)

#### Table 17-2. BDCSCR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>ENBDM  | <ul> <li>Enable BDM (Permit Active Background Mode) — Typically, this bit is written to 1 by the debug host shot after the beginning of a debug session or whenever the debug host resets the target and remains 1 until a no reset clears it.</li> <li>BDM cannot be made active (non-intrusive commands still allowed)</li> <li>BDM can be made active to allow active background mode commands</li> </ul>                                                                                                                                                                                                                                                           |  |  |

| 6<br>BDMACT | Background Mode Active Status — This is a read-only status bit.         0       BDM not active (user application program running)         1       BDM active and waiting for serial commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 5<br>BKPTEN | <ul> <li>BDC Breakpoint Enable — If this bit is clear, the BDC breakpoint is disabled and the FTS (force tag select) control bit and BDCBKPT match register are ignored.</li> <li>0 BDC breakpoint disabled</li> <li>1 BDC breakpoint enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 4<br>FTS    | <ul> <li>Force/Tag Select — When FTS = 1, a breakpoint is requested whenever the CPU address bus matches the BDCBKPT match register. When FTS = 0, a match between the CPU address bus and the BDCBKPT register causes the fetched opcode to be tagged. If this tagged opcode ever reaches the end of the instruction queue, the CPU enters active background mode rather than executing the tagged opcode.</li> <li>0 Tag opcode at breakpoint address and enter active background mode if CPU attempts to execute that instruction</li> <li>1 Breakpoint match forces active background mode at next instruction boundary (address need not be an opcode)</li> </ul> |  |  |

| 3<br>CLKSW  | Select Source for BDC Communications Clock — CLKSW defaults to 0, which selects the alternate BDC clock source.         0 Alternate BDC clock source         1 MCU bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

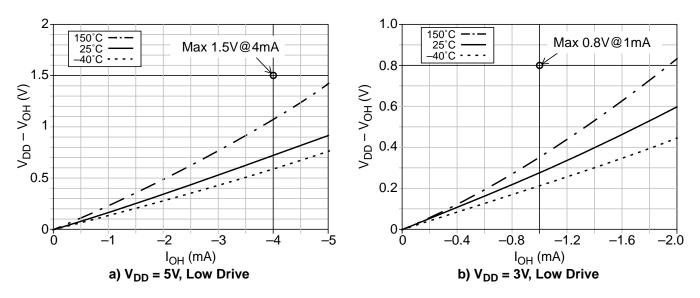

Figure A-4. Typical  $V_{DD} - V_{OH}$  vs I<sub>OH</sub>, Low Drive Strength

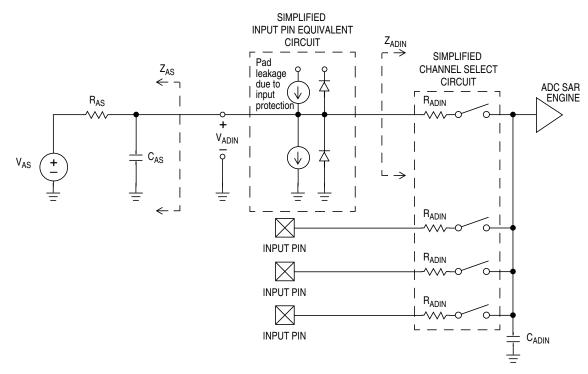

Figure A-9. ADC Input Impedance Equivalency Diagram