Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package    | 20-TSSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg16e1mtjr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Freescale Semiconductor, Inc. Data Sheet Addendum

Document Number: MC9S08SG32AD Rev. 2, 04/2015

## Addendum to Rev. 8.1 of the MC9S08SG32 Covers: MC9S08SG32 and MC9S08SG16

This addendum identifies changes to Rev. 8.1 of the MC9S08SG32 data sheet (covering MC9S08SG32 and MC9S08SG16). The changes described in this addendum have not been implemented in the specified pages.

## 1 Update to the "Nonvolatile Register Summary" table for NVFTRIM and NVOPT

Location: Table 4-4. Nonvolatile Register Summary, Page 47

For the NVFTRIM and NVOPT registers in Table 4-4, "Nonvolatile Register Summary," all reserved bits should be marked as "—" (not "0").

# 2 Update to the "Instruction Set Summary" table for BRA and BRN

Location: Table 7-2. Instruction Set Summary (Sheet 3 of 9), Page 106

In Table 7-2, "Instruction Set Summary," remove "(if I = 1)" from the BRA instruction and remove "(if I = 0)" from the BRN instruction. The BRA and BRN instructions do not depend on the I bit.

© 2015 Freescale Semiconductor, Inc. All rights reserved.

## **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                  | 6/2007           | Updated the TPM module, incorporated minor revisions for the $T_j$ , PTxSE slew rate, FPROT and Appendix B packaging informationSAMPLES DRAFT-                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 2                  | 10/2007          | Qualify Draft includes updates to TPM module and the Electricals appendix.<br>Also, revised the order numbering information.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 3                  | 5/2008           | Updated some electricals and made some minor grammatical/formatting revi-<br>sions. Corrected the SPI block module version. Removed incorrect ADC temper-<br>ature sensor value from the Features section. Updated the package information<br>with a special mask set identifier.                                                                                                                                                                                                                      |  |  |

| 4                  | 5/2008           | Added the EMC Radiated Emissions data. Removed the Susceptibility Data.<br>Updated the Corporate addresses on the back cover.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 5                  | 03/2009          | Added the High Temperature Device Specifications and updated the charts.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 6                  | 04/2009          | Updated ADC characteristics for Temp Sensor Slope to be a range of 25 C–150 Çadded Control Timing table row 2 to separate standard characteristics from the AEC Grade 0 characteristics, and included the text, "AEC Grade 0" to the text of footnote 3 for Table B-1 Device Numbering System. Added notes to the ADC chapter specifying that, for this device, there are only 16 analog input pins and consequently no APCTL3 register. Updated the Literature Request information on the back cover. |  |  |

| 7                  | 10/2009          | Revised Table A-6 DC Characteristics, Row 24 Bandgap Voltage Reference for AEC Grade 0 from 1.21V to 1.22 V. Removed AEC Grade 0 (red diamond) from the Table A-9 ICS Frequency Specifications, Row 9 Total deviation of trimmed DCO output frequency over voltage and temperature so that it is not listed for AEC Grade 0.                                                                                                                                                                           |  |  |

## Contents

**Section Number**

Page

## Chapter 1 Device Overview

| 1.1 | Devices in the MC9S08SG32 Series | . 21 |

|-----|----------------------------------|------|

|     | MCU Block Diagram                |      |

|     | System Clock Distribution        |      |

## Chapter 2 Pins and Connections

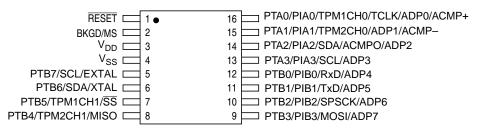

| 2.1 | Device | Pin Assignment                           | 25 |

|-----|--------|------------------------------------------|----|

|     |        | nended System Connections                |    |

|     |        | Power                                    |    |

|     | 2.2.2  | Oscillator (XOSC)                        | 28 |

|     | 2.2.3  | RESET                                    | 28 |

|     | 2.2.4  | Background / Mode Select (BKGD/MS)       | 29 |

|     | 2.2.5  | General-Purpose I/O and Peripheral Ports | 29 |

## Chapter 3 Modes of Operation

| 3.1 | Introdu  | ction                                    | 33 |

|-----|----------|------------------------------------------|----|

| 3.2 | Feature  | S                                        | 33 |

| 3.3 | Run Mo   | ode                                      | 33 |

| 3.4 | Active ] | Background Mode                          | 33 |

|     |          | ode                                      |    |

| 3.6 | Stop M   | odes                                     |    |

|     | 3.6.1    | Stop3 Mode                               | 35 |

|     |          | Stop2 Mode                               |    |

|     | 3.6.3    | On-Chip Peripheral Modules in Stop Modes |    |

|     |          |                                          |    |

## Chapter 4 Memory

| 4.1 | MC9S0    | 8SG32 Series Memory Map             | . 39 |

|-----|----------|-------------------------------------|------|

| 4.2 | Reset an | nd Interrupt Vector Assignments     | . 40 |

|     |          | Addresses and Bit Assignments       |      |

|     | -        | Ÿ                                   |      |

| 4.5 | FLASH    |                                     | . 48 |

|     | 4.5.1    | Features                            | . 49 |

|     | 4.5.2    | Program and Erase Times             | . 49 |

|     |          | Program and Erase Command Execution |      |

|     |          |                                     |      |

MC9S08SG32 Data Sheet, Rev. 8

**Chapter 2 Pins and Connections**

**Chapter 6 Parallel Input/Output Control**

## 6.4 Pin Interrupts

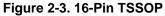

Port A[3:0] and port B[3:0] pins can be configured as external interrupt inputs and as an external means of waking the MCU from stop3 or wait low-power modes.

The block diagram for the pin interrupts is shown.

Figure 6-2. Pin Interrupt Block Diagram

Writing to the PTxPSn bits in the port interrupt pin enable register (PTxPS) independently enables or disables each port pin interrupt. Each port can be configured as edge sensitive or edge and level sensitive based on the PTxMOD bit in the port interrupt status and control register (PTxSC). Edge sensitivity can be software programmed to be either falling or rising; the level can be either low or high. The polarity of the edge or edge and level sensitivity is selected using the PTxESn bits in the port interrupt edge select register (PTxES).

Synchronous logic is used to detect edges. Prior to detecting an edge, enabled pin interrupt inputs must be at the deasserted logic level. A falling edge is detected when an enabled port input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle. A rising edge is detected when the input signal is seen as a logic 0 during one bus cycle and then a logic 1 during the next cycle.

## 6.4.1 Edge-Only Sensitivity

A valid edge on an enabled pin interrupt sets PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request is presented to the CPU. To clear PTxIF, write a 1 to PTxACK in PTxSC.

### NOTE

If a pin is enabled for interrupt on edge-sensitive only, a falling (or rising) edge on the pin does not latch an interrupt request if another pin interrupt is already asserted.

To prevent losing an interrupt request on one pin because another pin is asserted, software can disable the asserted pin interrupt while having the unasserted pin interrupt enabled. The asserted status of a pin is reflected by its associated I/O general purpose data register.

## 6.6.3 **Port C Registers**

Port C is controlled by the registers listed below.

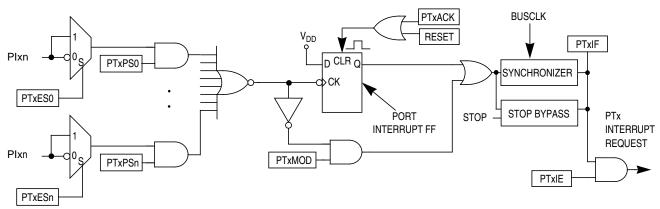

## 6.6.3.1 Port C Data Register (PTCD)

#### Figure 6-19. Port C Data Register (PTCD)

#### Table 6-18. PTCD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCD[7:0] | <b>Port C Data Register Bits</b> — For port C pins that are inputs, reads return the logic level on the pin. For port C pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port C pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTCD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups disabled. |

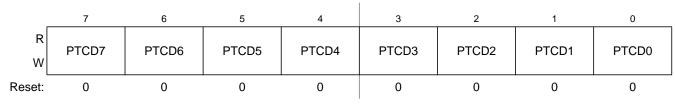

## 6.6.3.2 Port C Data Direction Register (PTCDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTCDD7 | PTCDD6 | PTCDD5 | PTCDD4 | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-20. Port C Data Direction Register (PTCDD)

#### Table 6-19. PTCDD Register Field Descriptions

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data Direction for Port C Bits</b> — These read/write bits control the direction of port C pins and what is read for PTCD reads.                                             |

|       | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port C bit n and PTCD reads return the contents of PTCDn.</li> </ol> |

Chapter 8 Analog Comparator 5-V (S08ACMPV3)

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SCL Hold<br>(Stop)<br>Value |

|--------------|----------------|-------------------|------------------------------|-----------------------------|

| 00           | 20             | 7                 | 6                            | 11                          |

| 01           | 22             | 7                 | 7                            | 12                          |

| 02           | 24             | 8                 | 8                            | 13                          |

| 03           | 26             | 8                 | 9                            | 14                          |

| 04           | 28             | 9                 | 10                           | 15                          |

| 05           | 30             | 9                 | 11                           | 16                          |

| 06           | 34             | 10                | 13                           | 18                          |

| 07           | 40             | 10                | 16                           | 21                          |

| 08           | 28             | 7                 | 10                           | 15                          |

| 09           | 32             | 7                 | 12                           | 17                          |

| 0A           | 36             | 9                 | 14                           | 19                          |

| 0B           | 40             | 9                 | 16                           | 21                          |

| 0C           | 44             | 11                | 18                           | 23                          |

| 0D           | 48             | 11                | 20                           | 25                          |

| 0E           | 56             | 13                | 24                           | 29                          |

| 0F           | 68             | 13                | 30                           | 35                          |

| 10           | 48             | 9                 | 18                           | 25                          |

| 11           | 56             | 9                 | 22                           | 29                          |

| 12           | 64             | 13                | 26                           | 33                          |

| 13           | 72             | 13                | 30                           | 37                          |

| 14           | 80             | 17                | 34                           | 41                          |

| 15           | 88             | 17                | 38                           | 45                          |

| 16           | 104            | 21                | 46                           | 53                          |

| 17           | 128            | 21                | 58                           | 65                          |

| 18           | 80             | 9                 | 38                           | 41                          |

| 19           | 96             | 9                 | 46                           | 49                          |

| 1A           | 112            | 17                | 54                           | 57                          |

| 1B           | 128            | 17                | 62                           | 65                          |

| 1C           | 144            | 25                | 70                           | 73                          |

| 1D           | 160            | 25                | 78                           | 81                          |

| 1E           | 192            | 33                | 94                           | 97                          |

| 1F           | 240            | 33                | 118                          | 121                         |

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SCL Hold<br>(Stop)<br>Value |

|--------------|----------------|-------------------|------------------------------|-----------------------------|

| 20           | 160            | 17                | 78                           | 81                          |

| 21           | 192            | 17                | 94                           | 97                          |

| 22           | 224            | 33                | 110                          | 113                         |

| 23           | 256            | 33                | 126                          | 129                         |

| 24           | 288            | 49                | 142                          | 145                         |

| 25           | 320            | 49                | 158                          | 161                         |

| 26           | 384            | 65                | 190                          | 193                         |

| 27           | 480            | 65                | 238                          | 241                         |

| 28           | 320            | 33                | 158                          | 161                         |

| 29           | 384            | 33                | 190                          | 193                         |

| 2A           | 448            | 65                | 222                          | 225                         |

| 2B           | 512            | 65                | 254                          | 257                         |

| 2C           | 576            | 97                | 286                          | 289                         |

| 2D           | 640            | 97                | 318                          | 321                         |

| 2E           | 768            | 129               | 382                          | 385                         |

| 2F           | 960            | 129               | 478                          | 481                         |

| 30           | 640            | 65                | 318                          | 321                         |

| 31           | 768            | 65                | 382                          | 385                         |

| 32           | 896            | 129               | 446                          | 449                         |

| 33           | 1024           | 129               | 510                          | 513                         |

| 34           | 1152           | 193               | 574                          | 577                         |

| 35           | 1280           | 193               | 638                          | 641                         |

| 36           | 1536           | 257               | 766                          | 769                         |

| 37           | 1920           | 257               | 958                          | 961                         |

| 38           | 1280           | 129               | 638                          | 641                         |

| 39           | 1536           | 129               | 766                          | 769                         |

| 3A           | 1792           | 257               | 894                          | 897                         |

| 3B           | 2048           | 257               | 1022                         | 1025                        |

| 3C           | 2304           | 385               | 1150                         | 1153                        |

| 3D           | 2560           | 385               | 1278                         | 1281                        |

| 3E           | 3072           | 513               | 1534                         | 1537                        |

| 3F           | 3840           | 513               | 1918                         | 1921                        |

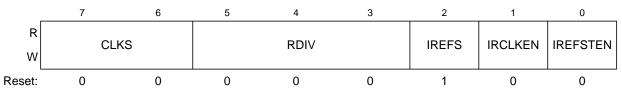

## 11.3.1 ICS Control Register 1 (ICSC1)

Figure 11-3. ICS Control Register 1 (ICSC1)

| Table 11-2. ICS Control Register 1 | I Field Descriptions |

|------------------------------------|----------------------|

|------------------------------------|----------------------|

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>CLKS   | <ul> <li>Clock Source Select — Selects the clock source that controls the bus frequency. The actual bus frequency depends on the value of the BDIV bits.</li> <li>O Output of FLL is selected.</li> <li>O1 Internal reference clock is selected.</li> <li>I0 External reference clock is selected.</li> <li>I1 Reserved, defaults to 00.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |

| 5:3<br>RDIV   | Reference Divider — Selects the amount to divide down the FLL reference clock selected by the IREFS bits.         Resulting frequency must be in the range 31.25 kHz to 39.0625 kHz.         000       Encoding 0 — Divides reference clock by 1 (reset default)         001       Encoding 1 — Divides reference clock by 2         010       Encoding 2 — Divides reference clock by 4         011       Encoding 3 — Divides reference clock by 8         100       Encoding 4 — Divides reference clock by 16         101       Encoding 5 — Divides reference clock by 32         110       Encoding 6 — Divides reference clock by 64         111       Encoding 7 — Divides reference clock by 128 |

| 2<br>IREFS    | Internal Reference Select — The IREFS bit selects the reference clock source for the FLL.<br>1 Internal reference clock selected<br>0 External reference clock selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1<br>IRCLKEN  | Internal Reference Clock Enable — The IRCLKEN bit enables the internal reference clock for use as ICSIRCLK.<br>1 ICSIRCLK active<br>0 ICSIRCLK inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0<br>IREFSTEN | <ul> <li>Internal Reference Stop Enable — The IREFSTEN bit controls whether or not the internal reference clock remains enabled when the ICS enters stop mode.</li> <li>1 Internal reference clock stays enabled in stop if IRCLKEN is set or if ICS is in FEI, FBI, or FBILP mode before entering stop</li> <li>0 Internal reference clock is disabled in stop</li> </ul>                                                                                                                                                                                                                                                                                                                                |

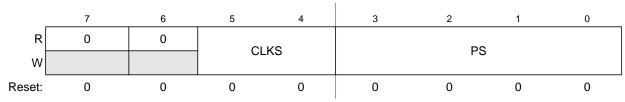

## 12.3.2 MTIM Clock Configuration Register (MTIMCLK)

MTIMCLK contains the clock select bits (CLKS) and the prescaler select bits (PS).

Figure 12-5. MTIM Clock Configuration Register

| Table 12-3. MTIM Clock Configuration R | Register Field Description |

|----------------------------------------|----------------------------|

|----------------------------------------|----------------------------|

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7:6         | Unused register bits, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| 5:4<br>CLKS | Clock Source Select — These two read/write bits select one of four different clock sources as the input to the MTIM prescaler. Changing the clock source while the counter is active does not clear the counter. The count continues with the new clock source. Reset clears CLKS to 000.         00       Encoding 0. Bus clock (BUSCLK)         01       Encoding 1. Fixed-frequency clock (XCLK)         10       Encoding 3. External source (TCLK pin), falling edge         11       Encoding 4. External source (TCLK pin), rising edge         All other encodings default to the bus clock (BUSCLK).                                                                                   |  |  |  |  |  |  |  |

| 3:0<br>PS   | Clock Source Prescaler — These four read/write bits select one of nine outputs from the 8-bit prescaler.<br>Changing the prescaler value while the counter is active does not clear the counter. The count continues with the<br>new prescaler value. Reset clears PS to 0000.<br>0000 Encoding 0. MTIM clock source ÷ 1<br>0001 Encoding 1. MTIM clock source ÷ 2<br>0010 Encoding 2. MTIM clock source ÷ 4<br>0011 Encoding 3. MTIM clock source ÷ 8<br>0100 Encoding 4. MTIM clock source ÷ 16<br>0101 Encoding 5. MTIM clock source ÷ 32<br>0110 Encoding 6. MTIM clock source ÷ 128<br>1000 Encoding 8. MTIM clock source ÷ 256<br>All other encodings default to MTIM clock source ÷ 256. |  |  |  |  |  |  |  |

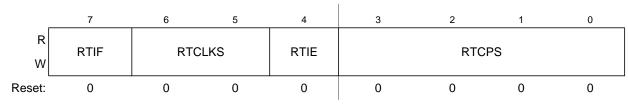

## 13.3.1 RTC Status and Control Register (RTCSC)

RTCSC contains the real-time interrupt status flag (RTIF), the clock select bits (RTCLKS), the real-time interrupt enable bit (RTIE), and the prescaler select bits (RTCPS).

Figure 13-3. RTC Status and Control Register (RTCSC)

| Table 13-2. RTC | CSC Field | Descriptions |

|-----------------|-----------|--------------|

|-----------------|-----------|--------------|

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTIF     | <ul> <li>Real-Time Interrupt Flag This status bit indicates the RTC counter register reached the value in the RTC modulo register. Writing a logic 0 has no effect. Writing a logic 1 clears the bit and the real-time interrupt request. Reset clears RTIF.</li> <li>0 RTC counter has not reached the value in the RTC modulo register.</li> <li>1 RTC counter has reached the value in the RTC modulo register.</li> </ul>                                                                                                                     |

| 6–5<br>RTCLKS | Real-Time Clock Source Select. These two read/write bits select the clock source input to the RTC prescaler.<br>Changing the clock source clears the prescaler and RTCCNT counters. When selecting a clock source, ensure<br>that the clock source is properly enabled (if applicable) to ensure correct operation of the RTC. Reset clears<br>RTCLKS.<br>00 Real-time clock source is the 1-kHz low power oscillator (LPO)<br>01 Real-time clock source is the external clock (ERCLK)<br>1x Real-time clock source is the internal clock (IRCLK) |

| 4<br>RTIE     | <ul> <li>Real-Time Interrupt Enable. This read/write bit enables real-time interrupts. If RTIE is set, then an interrupt is generated when RTIF is set. Reset clears RTIE.</li> <li>0 Real-time interrupt requests are disabled. Use software polling.</li> <li>1 Real-time interrupt requests are enabled.</li> </ul>                                                                                                                                                                                                                            |

| 3–0<br>RTCPS  | Real-Time Clock Prescaler Select. These four read/write bits select binary-based or decimal-based divide-by values for the clock source. See Table 13-3. Changing the prescaler value clears the prescaler and RTCCNT counters. Reset clears RTCPS.                                                                                                                                                                                                                                                                                               |

Table 13-3. RTC Prescaler Divide-by values

| RTCLKS[0] |     |                 |                 |                 |                 |                 |                 |                 | RTCP            | S                 |                   |                 |                   |                   |                   |                   |

|-----------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|-------------------|-----------------|-------------------|-------------------|-------------------|-------------------|

|           | 0   | 1               | 2               | 3               | 4               | 5               | 6               | 7               | 8               | 9                 | 10                | 11              | 12                | 13                | 14                | 15                |

| 0         | Off | 2 <sup>3</sup>  | 2 <sup>5</sup>  | 2 <sup>6</sup>  | 2 <sup>7</sup>  | 2 <sup>8</sup>  | 2 <sup>9</sup>  | 2 <sup>10</sup> | 1               | 2                 | 2 <sup>2</sup>    | 10              | 2 <sup>4</sup>    | 10 <sup>2</sup>   | 5x10 <sup>2</sup> | 10 <sup>3</sup>   |

| 1         | Off | 2 <sup>10</sup> | 2 <sup>11</sup> | 2 <sup>12</sup> | 2 <sup>13</sup> | 2 <sup>14</sup> | 2 <sup>15</sup> | 2 <sup>16</sup> | 10 <sup>3</sup> | 2x10 <sup>3</sup> | 5x10 <sup>3</sup> | 10 <sup>4</sup> | 2x10 <sup>4</sup> | 5x10 <sup>4</sup> | 10 <sup>5</sup>   | 2x10 <sup>5</sup> |

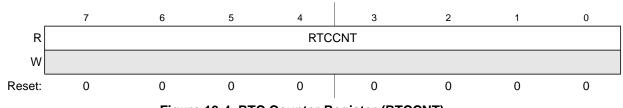

## 13.3.2 RTC Counter Register (RTCCNT)

RTCCNT is the read-only value of the current RTC count of the 8-bit counter.

Figure 13-4. RTC Counter Register (RTCCNT)

#### Table 13-4. RTCCNT Field Descriptions

| Field         | Description                                                                                                                                                                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCCNT | RTC Count. These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset, writing to RTCMOD, or writing different values to RTCLKS and RTCPS clear the count to 0x00. |

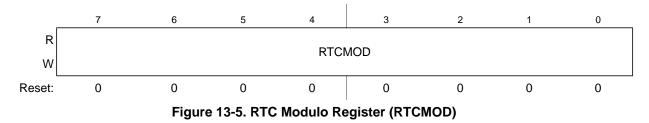

## 13.3.3 RTC Modulo Register (RTCMOD)

| Field         | Description                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>RTCMOD | RTC Modulo. These eight read/write bits contain the modulo value used to reset the count to 0x00 upon a compare match and set the RTIF status bit. A value of 0x00 sets the RTIF bit on each rising edge of the prescaler output. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00. Reset sets the modulo to 0x00. |

## 13.4 Functional Description

The RTC is composed of a main 8-bit up-counter with an 8-bit modulo register, a clock source selector, and a prescaler block with binary-based and decimal-based selectable values. The module also contains software selectable interrupt logic.

After any MCU reset, the counter is stopped and reset to 0x00, the modulus register is set to 0x00, and the prescaler is off. The 1-kHz internal oscillator clock is selected as the default clock source. To start the prescaler, write any value other than zero to the prescaler select bits (RTCPS).

Three clock sources are software selectable: the low power oscillator clock (LPO), the external clock (ERCLK), and the internal clock (IRCLK). The RTC clock select bits (RTCLKS) select the desired clock source. If a different value is written to RTCLKS, the prescaler and RTCCNT counters are reset to 0x00.

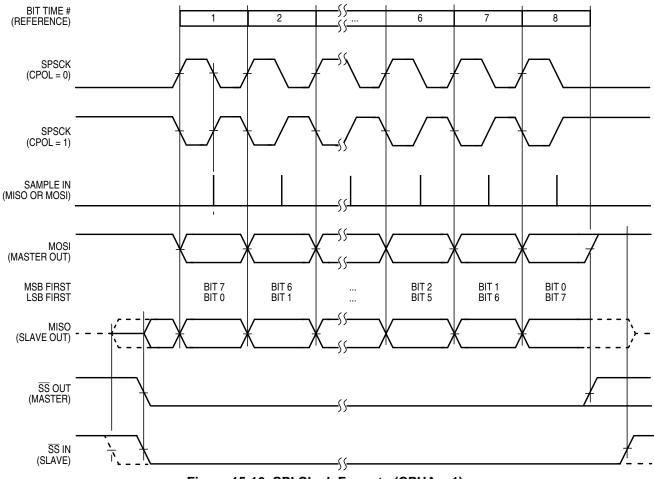

pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low one-half SPSCK cycle before the start of the transfer and goes back high at the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 15-10. SPI Clock Formats (CPHA = 1)

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

Figure 15-11 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting

| CLKSB:CLKSA | TPM Clock Source to Prescaler Input     |  |  |  |  |

|-------------|-----------------------------------------|--|--|--|--|

| 00          | No clock selected (TPM counter disable) |  |  |  |  |

| 01          | Bus rate clock                          |  |  |  |  |

| 10          | Fixed system clock                      |  |  |  |  |

| 11          | External source                         |  |  |  |  |

Table 16-4. TPM-Clock-Source Selection

| Table 16-5 | Prescale | Factor | Selection |

|------------|----------|--------|-----------|

|------------|----------|--------|-----------|

| PS2:PS1:PS0 | TPM Clock Source Divided-by |  |  |  |  |  |  |

|-------------|-----------------------------|--|--|--|--|--|--|

| 000         | 1                           |  |  |  |  |  |  |

| 001         | 2                           |  |  |  |  |  |  |

| 010         | 4                           |  |  |  |  |  |  |

| 011         | 8                           |  |  |  |  |  |  |

| 100         | 16                          |  |  |  |  |  |  |

| 101         | 32                          |  |  |  |  |  |  |

| 110         | 64                          |  |  |  |  |  |  |

| 111         | 128                         |  |  |  |  |  |  |

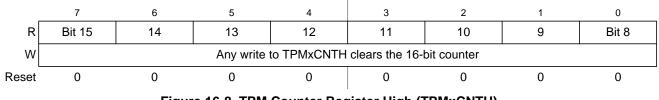

## 16.3.2 TPM-Counter Registers (TPMxCNTH:TPMxCNTL)

The two read-only TPM counter registers contain the high and low bytes of the value in the TPM counter. Reading either byte (TPMxCNTH or TPMxCNTL) latches the contents of both bytes into a buffer where they remain latched until the other half is read. This allows coherent 16-bit reads in either big-endian or little-endian order which makes this more friendly to various compiler implementations. The coherency mechanism is automatically restarted by an MCU reset or any write to the timer status/control register (TPMxSC).

Reset clears the TPM counter registers. Writing any value to TPMxCNTH or TPMxCNTL also clears the TPM counter (TPMxCNTH:TPMxCNTL) and resets the coherency mechanism, regardless of the data involved in the write.

Figure 16-8. TPM Counter Register High (TPMxCNTH)

TPM counter changes from (TPMxMODH:L - 1) to (TPMxMODH:L). If the TPM counter is a free-running counter, then this update is made when the TPM counter changes from \$FFFE to \$FFFF. Instead, the TPM v2 makes this update after that the both bytes were written and when the TPM counter changes from TPMxMODH:L to \$0000.

— Center-Aligned PWM (Section 16.4.2.4, "Center-Aligned PWM Mode)

In this mode and if (CLKSB:CLKSA not = 00), the TPM v3 updates the TPMxCnVH:L registers with the value of their write buffer after that the both bytes were written and when the TPM counter changes from (TPMxMODH:L - 1) to (TPMxMODH:L). If the TPM counter is a free-running counter, then this update is made when the TPM counter changes from \$FFFE to \$FFFF. Instead, the TPM v2 makes this update after that the both bytes were written and when the TPM counter changes from TPMxMODH:L to (TPMxMODH:L - 1).

- 5. Center-Aligned PWM (Section 16.4.2.4, "Center-Aligned PWM Mode)

- TPMxCnVH:L = TPMxMODH:L [SE110-TPM case 1] In this case, the TPM v3 produces 100% duty cycle. Instead, the TPM v2 produces 0% duty cycle.

- TPMxCnVH:L = (TPMxMODH:L 1) [SE110-TPM case 2]

In this case, the TPM v3 produces almost 100% duty cycle. Instead, the TPM v2 produces 0% duty cycle.

- TPMxCnVH:L is changed from 0x0000 to a non-zero value [SE110-TPM case 3 and 5] In this case, the TPM v3 waits for the start of a new PWM period to begin using the new duty cycle setting. Instead, the TPM v2 changes the channel output at the middle of the current PWM period (when the count reaches 0x0000).

- TPMxCnVH:L is changed from a non-zero value to 0x0000 [SE110-TPM case 4]

In this case, the TPM v3 finishes the current PWM period using the old duty cycle setting.

Instead, the TPM v2 finishes the current PWM period using the new duty cycle setting.

- 6. Write to TPMxMODH:L registers in BDM mode (Section 16.3.3, "TPM Counter Modulo Registers (TPMxMODH:TPMxMODL))

In the TPM v3 a write to TPMxSC register in BDM mode clears the write coherency mechanism of TPMxMODH:L registers. Instead, in the TPM v2 this coherency mechanism is not cleared when there is a write to TPMxSC register.

7. Update of EPWM signal when CLKSB:CLKSA = 00

In the TPM v3 if CLKSB:CLKSA = 00, then the EPWM signal in the channel output is not update (it is frozen while CLKSB:CLKSA = 00). Instead, in the TPM v2 the EPWM signal is updated at the next rising edge of bus clock after a write to TPMxCnSC register.

The Figure 16-17 and Figure 16-18 show when the EPWM signals generated by TPM v2 and TPM v3 after the reset (CLKSB:CLKSA = 00) and if there is a write to TPMxCnSC register.

Chapter 16 Timer/PWM Module (S08TPMV3)

| # |                           |                                                                     | Symbol                   | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max <sup>2</sup> | Unit | Temp Rated |                |

|---|---------------------------|---------------------------------------------------------------------|--------------------------|------------------------|------------------|------------------|------|------------|----------------|

|   | с                         | Parameter                                                           |                          |                        |                  |                  |      | Standard   | AEC<br>Grade 0 |

| 5 | Stop2 mode supply current |                                                                     |                          |                        |                  | 1                |      |            |                |

|   | С                         | -40°C (C,M, and V suffix)                                           |                          | 5                      | 0.94             | -                | μA   | •          | _              |

|   | Р                         | 25°C (All parts)                                                    |                          |                        | 1.25             | -                | μA   | •          | _              |

|   | P <sup>5</sup>            | 85°C (C suffix only)                                                |                          |                        | 13.4             | 30               | μΑ   | •          | _              |

|   | P <sup>5</sup>            | 105°C (V suffix only)                                               |                          |                        | 30               | 65               | μΑ   | •          | _              |

|   | P <sup>5</sup>            | 125°C (M suffix only)                                               | S2I <sub>DD</sub>        |                        | 65               | 120              | μΑ   | •          | _              |

|   | С                         | –40°C (C,M, and V suffix)                                           |                          | 3                      | 0.83             | _                | μΑ   | •          | —              |

|   | Р                         | 25°C (All parts)                                                    |                          |                        | 1.1              | _                | μΑ   | •          | —              |

|   | P <sup>5</sup>            | 85°C (C suffix only)                                                |                          |                        | 11.5             | 25               | μΑ   | •          | —              |

|   | P <sup>5</sup>            | 105°C (V suffix only)                                               |                          |                        | 25               | 55               | μΑ   | •          | _              |

|   | P <sup>5</sup>            | 125°C (M suffix only)                                               |                          |                        | 57               | 100              | μΑ   | •          | _              |

| 6 |                           | RTC adder to stop2 or stop3 <sup>6</sup>                            | S23I <sub>DDR</sub>      | 5                      | 300              | 500              | nA   | •          | —              |

|   | С                         |                                                                     |                          | 3                      | 300              | 500              | nA   | •          | _              |

| 7 |                           | LVD adder to stop3 (LVDE = LVDSE = 1)                               | S3I <sub>DDLVD</sub>     | 5                      | 110              | 180              | μΑ   | •          | _              |

|   | С                         |                                                                     |                          | 3                      | 90               | 160              | μΑ   | •          | _              |

| 8 | С                         | Adder to stop3 for oscillator enabled <sup>7</sup><br>(EREFSTEN =1) | S3I <sub>DDOS</sub><br>c | 5,3                    | 5                | 8                | μΑ   | ٠          | —              |

<sup>1</sup> Typical values are based on characterization data at 25°C. See Figure A-5 through Figure A-7 for typical curves across temperature and voltage.

- <sup>2</sup> Max values in this column apply for the full operating temperature range of the device unless otherwise noted.

- <sup>3</sup> All modules except ADC active, ICS configured for FBELP, and does not include any dc loads on port pins

- <sup>4</sup> All modules except ADC active, ICS configured for FEI, and does not include any dc loads on port pins

- <sup>5</sup> Stop Currents are tested in production for 25 Con all parts. Tests at other temperatures depend upon the part number suffix and maturity of the product. Freescale may eliminate a test insertion at a particular temperature from the production test flow once sufficient data has been collected and is approved.

<sup>6</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode.

<sup>7</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768kHz crystal and low power mode (HGO = 0).

#### Appendix A Electrical Characteristics

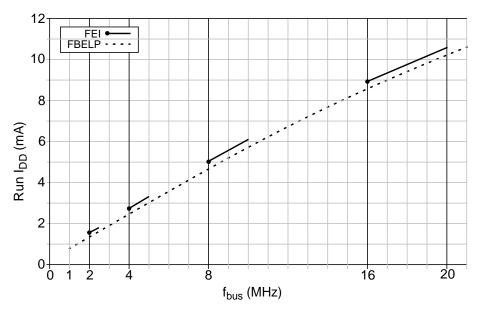

Figure A-5. Typical Run  $I_{DD}$  vs. Bus Frequency ( $V_{DD}$  = 5V)

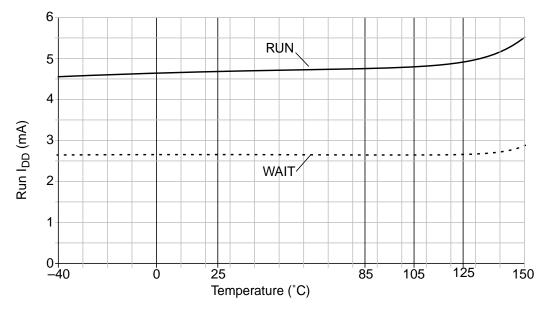

Figure A-6. Typical Run and Wait  $I_{DD}$  vs. Temperature (V<sub>DD</sub> = 5V; f<sub>bus</sub> = 8MHz)

Appendix B Ordering Information and Mechanical Drawings

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 1-303-675-2140 Fax: 1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007-2010. All rights reserved.