# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package    | 28-TSSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg16e1mtlr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 2 Pins and Connections**

Whenever any reset is initiated (whether from an external signal or from an internal system), the  $\overline{\text{RESET}}$  pin is driven low for about 66 bus cycles. The reset circuitry decodes the cause of reset and records it by setting a corresponding bit in the system reset status register (SRS).

### NOTE

- This pin does not contain a clamp diode to  $V_{\mbox{\scriptsize DD}}$  and should not be driven above  $V_{\mbox{\scriptsize DD}}.$

- The voltage measured on the internally pulled up  $\overline{\text{RESET}}$  pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the  $\overline{\text{RESET}}$  pin is required to drive to a  $V_{DD}$  level, an external pullup should be used.

- In EMC-sensitive applications, an external RC filter is recommended on the RESET. See Figure 2-4 for an example.

# 2.2.4 Background / Mode Select (BKGD/MS)

During a power-on-reset (POR) or background debug force reset (see Section 5.7.2, "System Background Debug Force Reset Register (SBDFR)," for more information), the BKGD/MS pin functions as a mode select pin. Immediately after any reset, the pin functions as the background pin and can be used for background debug communication. The BKGD/MS pin contains an internal pullup device.

If nothing is connected to this pin, the MCU enters normal operating mode at the rising edge of the internal reset after a POR or force BDC reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during a POR or immediately after issuing a background debug force reset, which will force the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the maximum bus clock rate, so there must never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

# 2.2.5 General-Purpose I/O and Peripheral Ports

The MC9S08SG32 Series of MCUs support up to 22 general-purpose I/O pins which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc.).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

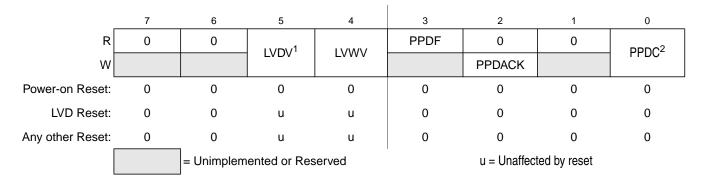

# 5.7.7 System Power Management Status and Control 2 Register (SPMSC2)

This register is used to report the status of the low voltage warning function, and to configure the stop mode behavior of the MCU. This register should be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

<sup>1</sup> This bit can be written only one time after power-on reset. Additional writes are ignored.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Figure 5-9. System Power Management Status and Control 2 Register (SPMSC2)

| Table 5-10. SPMSC2 R | Register Field | Descriptions |

|----------------------|----------------|--------------|

|----------------------|----------------|--------------|

| Field       | Description                                                                                                                                                                                                               |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5<br>LVDV   | <b>Low-Voltage Detect Voltage Select</b> — This write-once bit selects the low voltage detect (LVD) trip point setting It also selects the warning voltage range. See Table 5-11.                                         |  |  |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — This bit selects the low voltage warning (LVW) trip point voltage. See Table 5-11.                                                                                            |  |  |

| 3<br>PPDF   | <ul> <li>Partial Power Down Flag — This read-only status bit indicates that the MCU has recovered from stop2 mode.</li> <li>0 MCU has not recovered from stop2 mode.</li> <li>1 MCU recovered from stop2 mode.</li> </ul> |  |  |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit                                                                                                                                                |  |  |

| 0<br>PPDC   | <ul> <li>Partial Power Down Control — This write-once bit controls whether stop2 or stop3 mode is selected.</li> <li>0 Stop3 mode enabled.</li> <li>1 Stop2, partial power down, mode enabled.</li> </ul>                 |  |  |

**Chapter 6 Parallel Input/Output Control**

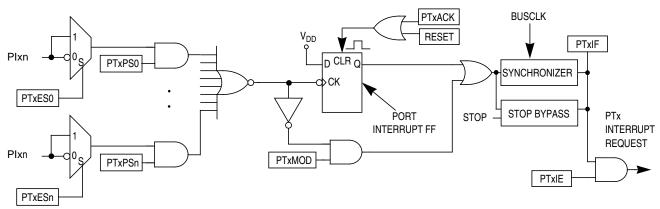

# 6.4 Pin Interrupts

Port A[3:0] and port B[3:0] pins can be configured as external interrupt inputs and as an external means of waking the MCU from stop3 or wait low-power modes.

The block diagram for the pin interrupts is shown.

Figure 6-2. Pin Interrupt Block Diagram

Writing to the PTxPSn bits in the port interrupt pin enable register (PTxPS) independently enables or disables each port pin interrupt. Each port can be configured as edge sensitive or edge and level sensitive based on the PTxMOD bit in the port interrupt status and control register (PTxSC). Edge sensitivity can be software programmed to be either falling or rising; the level can be either low or high. The polarity of the edge or edge and level sensitivity is selected using the PTxESn bits in the port interrupt edge select register (PTxES).

Synchronous logic is used to detect edges. Prior to detecting an edge, enabled pin interrupt inputs must be at the deasserted logic level. A falling edge is detected when an enabled port input signal is seen as a logic 1 (the deasserted level) during one bus cycle and then a logic 0 (the asserted level) during the next cycle. A rising edge is detected when the input signal is seen as a logic 0 during one bus cycle and then a logic 1 during the next cycle.

# 6.4.1 Edge-Only Sensitivity

A valid edge on an enabled pin interrupt sets PTxIF in PTxSC. If PTxIE in PTxSC is set, an interrupt request is presented to the CPU. To clear PTxIF, write a 1 to PTxACK in PTxSC.

### NOTE

If a pin is enabled for interrupt on edge-sensitive only, a falling (or rising) edge on the pin does not latch an interrupt request if another pin interrupt is already asserted.

To prevent losing an interrupt request on one pin because another pin is asserted, software can disable the asserted pin interrupt while having the unasserted pin interrupt enabled. The asserted status of a pin is reflected by its associated I/O general purpose data register.

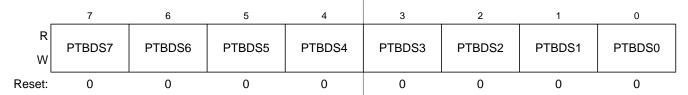

# 6.6.2.5 Port B Drive Strength Selection Register (PTBDS)

Figure 6-15. Drive Strength Selection for Port B Register (PTBDS)

### Table 6-14. PTBDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDS[7:0] | <ul> <li>Output Drive Strength Selection for Port B Bits — Each of these control bits selects between low and high output drive for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port B bit n.</li> <li>1 High output drive strength selected for port B bit n.</li> </ul> |

# 6.6.2.6 Port B Interrupt Status and Control Register (PTBSC)

|        | 7 | 6 | 5 | 4 | 3     | 2      | 1     | 0        |

|--------|---|---|---|---|-------|--------|-------|----------|

| R      | 0 | 0 | 0 | 0 | PTBIF | 0      | PTBIE | PTBMOD   |

| W      |   |   |   |   |       | PTBACK | FIDIC | FIDIVIOD |

| Reset: | 0 | 0 | 0 | 0 | 0     | 0      | 0     | 0        |

Figure 6-16. Port B Interrupt Status and Control Register (PTBSC)

### Table 6-15. PTBSC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                             |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3<br>PTBIF  | <ul> <li>Port B Interrupt Flag — PTBIF indicates when a Port B interrupt is detected. Writes have no effect on PTBIF.</li> <li>0 No Port B interrupt detected.</li> <li>1 Port B interrupt detected.</li> </ul>                         |  |  |

| 2<br>PTBACK | <b>Port B Interrupt Acknowledge</b> — Writing a 1 to PTBACK is part of the flag clearing mechanism. PTBACK always reads as 0.                                                                                                           |  |  |

| 1<br>PTBIE  | <ul> <li>Port B Interrupt Enable — PTBIE determines whether a port B interrupt is enabled.</li> <li>0 Port B interrupt request not enabled.</li> <li>1 Port B interrupt request enabled.</li> </ul>                                     |  |  |

| 0<br>PTBMOD | <ul> <li>Port B Detection Mode — PTBMOD (along with the PTBES bits) controls the detection mode of the port B interrupt pins.</li> <li>0 Port B pins detect edges only.</li> <li>1 Port B pins detect both edges and levels.</li> </ul> |  |  |

Chapter 6 Parallel Input/Output Control

# 7.4.5 **BGND** Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

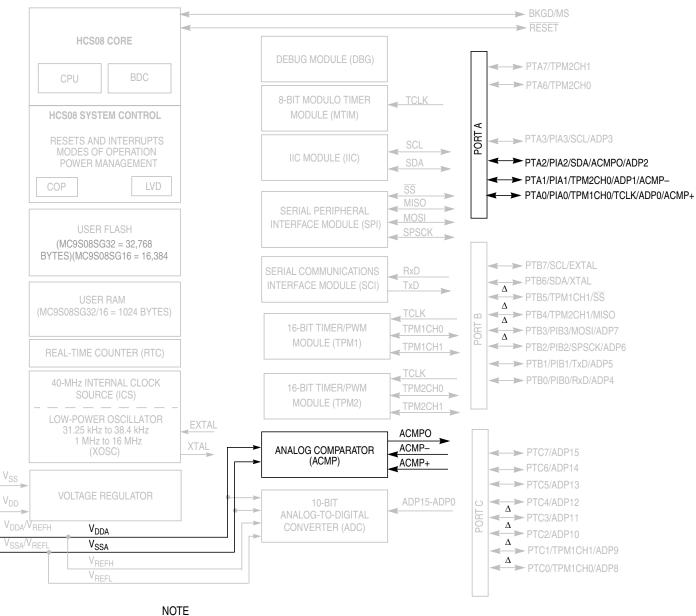

#### Chapter 8 Analog Comparator 5-V (S08ACMPV3)

$\Delta$  = Pin can be enabled as part of the ganged output drive feature

### Figure 8-1. MC9S08SG32 Series Block Diagram Highlighting ACMP Block and Pins

MC9S08SG32 Data Sheet, Rev. 8

Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

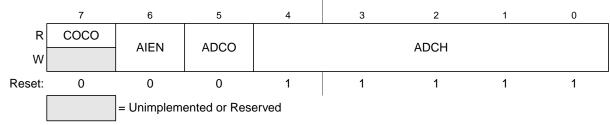

# 9.3.1 Status and Control Register 1 (ADCSC1)

This section describes the function of the ADC status and control register (ADCSC1). Writing ADCSC1 aborts the current conversion and initiates a new conversion (if the ADCH bits are equal to a value other than all 1s).

Figure 9-3. Status and Control Register (ADCSC1)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COCO   | <ul> <li>Conversion Complete Flag — The COCO flag is a read-only bit set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1), the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared when ADCSC1 is written or whenever ADCRL is read.</li> <li>0 Conversion not completed</li> <li>1 Conversion completed</li> </ul>                                                                                                                                                                                                                                                                  |

| 6<br>AIEN   | Interrupt Enable — AIEN enables conversion complete interrupts. When COCO becomes set while AIEN is high, an interrupt is asserted.<br>0 Conversion complete interrupt disabled<br>1 Conversion complete interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5<br>ADCO   | <ul> <li>Continuous Conversion Enable — ADCO enables continuous conversions.</li> <li>One conversion following a write to the ADCSC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.</li> <li>Continuous conversions initiated following a write to ADCSC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.</li> </ul>                                                                                                                                                                                                        |

| 4:0<br>ADCH | Input Channel Select — The ADCH bits form a 5-bit field which that selects one of the input channels. The input channels are detailed in Table 9-4.<br>The successive approximation converter subsystem is turned off when the channel select bits are all set. This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources. Terminating continuous conversions this way prevents an additional, single conversion from being performed. It is not necessary to set the channel select bits to all ones to place the ADC in a low-power state when continuous conversions are not enabled because the module automatically enters a low-power state when a conversion completes. |

### Table 9-4. Input Channel Select

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| ADCH  | Input Select |

|-------|--------------|

| 10000 | AD16         |

| 10001 | AD17         |

| 10010 | AD18         |

| 10011 | AD19         |

#### MC9S08SG32 Data Sheet, Rev. 8

Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

# 9.6.2 Sources of Error

Several sources of error exist for A/D conversions. These are discussed in the following sections.

# 9.6.2.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately  $7k\Omega$  and input capacitance of approximately 5.5 pF, sampling to within 1/4LSB (at 10-bit resolution) can be achieved within the minimum sample window (3.5 cycles @ 8 MHz maximum ADCK frequency) provided the resistance of the external analog source ( $R_{AS}$ ) is kept below 5 k $\Omega$ .

Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

# 9.6.2.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{DDA} / (2^{N*}I_{LEAK})$  for less than 1/4LSB leakage error (N = 8 in 8-bit mode or 10 in 10-bit mode).

# 9.6.2.3 Noise-Induced Errors

System noise that occurs during the sample or conversion process can affect the accuracy of the conversion. The ADC accuracy numbers are guaranteed as specified only if the following conditions are met:

- There is a 0.1  $\mu F$  low-ESR capacitor from  $V_{REFH}$  to  $V_{REFL}.$

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>DDA</sub> to V<sub>SSA</sub>.

- If inductive isolation is used from the primary supply, an additional 1  $\mu$ F capacitor is placed from V<sub>DDA</sub> to V<sub>SSA</sub>.

- $V_{SSA}$  (and  $V_{REFL}$ , if connected) is connected to  $V_{SS}$  at a quiet point in the ground plane.

- Operate the MCU in wait or stop3 mode before initiating (hardware triggered conversions) or immediately after initiating (hardware or software triggered conversions) the ADC conversion.

- For software triggered conversions, immediately follow the write to ADCSC1 with a wait instruction or stop instruction.

- For stop3 mode operation, select ADACK as the clock source. Operation in stop3 reduces  $V_{DD}$  noise but increases effective conversion time due to stop recovery.

- There is no I/O switching, input or output, on the MCU during the conversion.

There are some situations where external system activity causes radiated or conducted noise emissions or excessive  $V_{DD}$  noise is coupled into the ADC. In these situations, or when the MCU cannot be placed in wait or stop3 or I/O activity cannot be halted, these recommended actions may reduce the effect of noise on the accuracy:

• Place a 0.01  $\mu$ F capacitor (C<sub>AS</sub>) on the selected input channel to V<sub>REFL</sub> or V<sub>SSA</sub> (this improves noise issues, but affects the sample rate based on the external analog source resistance).

# Chapter 10 Inter-Integrated Circuit (S08IICV2)

# 10.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

### NOTE

The SDA and SCL should not be driven above  $V_{DD}$ . These pins are pseudo open-drain containing a protection diode to  $V_{DD}$ .

# **10.1.1 Module Configuration**

The IIC module pins, SDA and SCL can be repositioned under software control using IICPS in SOPT1 as as shown in Table 10-1. IICPS in SOPT1 selects which general-purpose I/O ports are associated with IIC operation.

| IICPS in SOPT1 | Port Pin for SDA | Port Pin for SCL |

|----------------|------------------|------------------|

| 0 (default)    | PTA2             | PTA3             |

| 1              | PTB6             | PTB7             |

### Table 10-1. IIC Position Options

Figure 10-1 shows the MC9S08SG32 Series block diagram with the IIC module highlighted.

Chapter 11 Internal Clock Source (S08ICSV2)

- CLKS bits are written to 00

- IREFS bit is written to 1

- RDIV bits are written to divide trimmed reference clock to be within the range of 31.25 kHz to 39.0625 kHz.

In FLL engaged internal mode, the ICSOUT clock is derived from the FLL clock, which is controlled by the internal reference clock. The FLL loop will lock the frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the internal reference clock is enabled.

# 11.4.1.2 FLL Engaged External (FEE)

The FLL engaged external (FEE) mode is entered when all the following conditions occur:

- CLKS bits are written to 00

- IREFS bit is written to 0

- RDIV bits are written to divide reference clock to be within the range of 31.25 kHz to 39.0625 kHz

In FLL engaged external mode, the ICSOUT clock is derived from the FLL clock which is controlled by the external reference clock. The FLL loop will lock the frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK is available for BDC communications, and the external reference clock is enabled.

# 11.4.1.3 FLL Bypassed Internal (FBI)

The FLL bypassed internal (FBI) mode is entered when all the following conditions occur:

- CLKS bits are written to 01

- IREFS bit is written to 1.

- BDM mode is active or LP bit is written to 0

In FLL bypassed internal mode, the ICSOUT clock is derived from the internal reference clock. The FLL clock is controlled by the internal reference clock, and the FLL loop will lock the FLL frequency to 1024 times the reference frequency, as selected by the RDIV bits. The ICSLCLK will be available for BDC communications, and the internal reference clock is enabled.

# 11.4.1.4 FLL Bypassed Internal Low Power (FBILP)

The FLL bypassed internal low power (FBILP) mode is entered when all the following conditions occur:

- CLKS bits are written to 01

- IREFS bit is written to 1.

- BDM mode is not active and LP bit is written to 1

In FLL bypassed internal low power mode, the ICSOUT clock is derived from the internal reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications, and the internal reference clock is enabled.

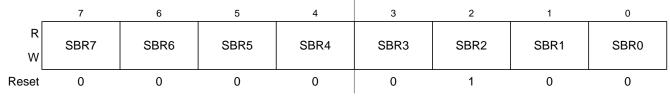

### Figure 14-5. SCI Baud Rate Register (SCIBDL)

Table 14-2. SCIBDL Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>SBR[7:0] | <b>Baud Rate Modulo Divisor</b> — These 13 bits in SBR[12:0] are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/(16×BR). See also BR bits in Table 14-1. |

# 14.2.2 SCI Control Register 1 (SCIC1)

This read/write register is used to control various optional features of the SCI system.

| _      | 7     | 6       | 5    | 4 | 3    | 2   | 1  | 0  |

|--------|-------|---------|------|---|------|-----|----|----|

| R<br>W | LOOPS | SCISWAI | RSRC | М | WAKE | ILT | PE | PT |

| Reset  | 0     | 0       | 0    | 0 | 0    | 0   | 0  | 0  |

Figure 14-6. SCI Control Register 1 (SCIC1)

### Table 14-3. SCIC1 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | <ul> <li>Loop Mode Select — Selects between loop back modes and normal 2-pin full-duplex modes. When LOOPS = 1, the transmitter output is internally connected to the receiver input.</li> <li>0 Normal operation — RxD and TxD use separate pins.</li> <li>1 Loop mode or single-wire mode where transmitter outputs are internally connected to receiver input. (See RSRC bit.) RxD pin is not used by SCI.</li> </ul>                                                                 |

| 6<br>SCISWAI | <ul> <li>SCI Stops in Wait Mode</li> <li>SCI clocks continue to run in wait mode so the SCI can be the source of an interrupt that wakes up the CPU.</li> <li>SCI clocks freeze while CPU is in wait mode.</li> </ul>                                                                                                                                                                                                                                                                    |

| 5<br>RSRC    | <ul> <li>Receiver Source Select — This bit has no meaning or effect unless the LOOPS bit is set to 1. When LOOPS = 1, the receiver input is internally connected to the TxD pin and RSRC determines whether this connection is also connected to the transmitter output.</li> <li>Provided LOOPS = 1, RSRC = 0 selects internal loop back mode and the SCI does not use the RxD pins.</li> <li>Single-wire SCI mode where the TxD pin is connected to the transmitter output.</li> </ul> |

| 4<br>M       | <ul> <li>9-Bit or 8-Bit Mode Select</li> <li>0 Normal — start + 8 data bits (LSB first) + stop.</li> <li>1 Receiver and transmitter use 9-bit data characters start + 8 data bits (LSB first) + 9th data bit + stop.</li> </ul>                                                                                                                                                                                                                                                          |

Chapter 14 Serial Communications Interface (S08SCIV4)

# 15.3 Modes of Operation

### 15.3.1 SPI in Stop Modes

The SPI is disabled in all stop modes, regardless of the settings before executing the STOP instruction. During stop2 mode, the SPI module will be fully powered down. Upon wake-up from stop2 mode, the SPI module will be in the reset state. During stop3 mode, clocks to the SPI module are halted. No registers are affected. If stop3 is exited with a reset, the SPI will be put into its reset state. If stop3 is exited with an interrupt, the SPI continues from the state it was in when stop3 was entered.

# 15.4 Register Definition

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

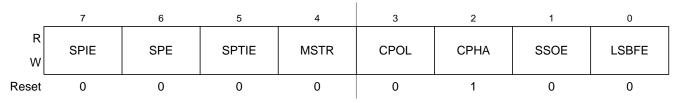

# 15.4.1 SPI Control Register 1 (SPIC1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 15-5. SPI Control Register 1 (SPIC1)

| Table 15-1 | SPIC1 | Field | Descriptions |

|------------|-------|-------|--------------|

|------------|-------|-------|--------------|

| Field      | Description                                                                                                                                                                                                                                                                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable (for SPRF and MODF) — This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.</li> <li>Interrupts from SPRF and MODF inhibited (use polling)</li> <li>When SPRF or MODF is 1, request a hardware interrupt</li> </ul>                    |

| 6<br>SPE   | <ul> <li>SPI System Enable — Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.</li> <li>SPI system inactive</li> <li>SPI system enabled</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).</li> <li>Interrupts from SPTEF inhibited (use polling)</li> <li>When SPTEF is 1, hardware interrupt requested</li> </ul>                                                                    |

Chapter 16 Timer/PWM Module (S08TPMV3)

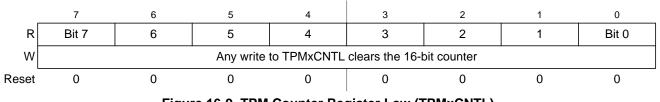

When BDM is active, the timer counter is frozen (this is the value that will be read by user); the coherency mechanism is frozen such that the buffer latches remain in the state they were in when the BDM became active, even if one or both counter halves are read while BDM is active. This assures that if the user was in the middle of reading a 16-bit register when BDM became active, it will read the appropriate value from the other half of the 16-bit value after returning to normal execution.

In BDM mode, writing any value to TPMxSC, TPMxCNTH or TPMxCNTL registers resets the read coherency mechanism of the TPMxCNTH:L registers, regardless of the data involved in the write.

# 16.3.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock, and the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits the TOF bit and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000 which results in a free running timer counter (modulo disabled).

Writing to either byte (TPMxMODH or TPMxMODL) latches the value into a buffer and the registers are updated with the value of their write buffer according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), then the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), then the registers are updated after both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter, the update is made when the TPM counter changes from 0xFFFE to 0xFFFF

The latching mechanism may be manually reset by writing to the TPMxSC address (whether BDM is active or not).

When BDM is active, the coherency mechanism is frozen (unless reset by writing to TPMxSC register) such that the buffer latches remain in the state they were in when the BDM became active, even if one or both halves of the modulo register are written while BDM is active. Any write to the modulo registers bypasses the buffer latches and directly writes to the modulo register while BDM is active.

|        | 7      | 6  | 5  | 4  | 3  | 2  | 1 | 0     |

|--------|--------|----|----|----|----|----|---|-------|

| R<br>W | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 |

| Reset  | 0      | 0  | 0  | 0  | 0  | 0  | 0 | 0     |

Figure 16-10. TPM Counter Modulo Register High (TPMxMODH)

MC9S08SG32 Data Sheet, Rev. 8

Chapter 16 Timer/PWM Module (S08TPMV3)

Chapter 17 Development Support

# 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

| Command<br>Mnemonic | Active BDM/<br>Non-intrusive | Coding<br>Structure | Description                                                                              |

|---------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------|

| SYNC                | Non-intrusive                | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed              |

| ACK_ENABLE          | Non-intrusive                | D5/d                | Enable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.       |

| ACK_DISABLE         | Non-intrusive                | D6/d                | Disable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.      |

| BACKGROUND          | Non-intrusive                | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |

| READ_STATUS         | Non-intrusive                | E4/SS               | Read BDC status from BDCSCR                                                              |

| WRITE_CONTROL       | Non-intrusive                | C4/CC               | Write BDC controls in BDCSCR                                                             |

| READ_BYTE           | Non-intrusive                | E0/AAAA/d/RD        | Read a byte from target memory                                                           |

| READ_BYTE_WS        | Non-intrusive                | E1/AAAA/d/SS/RD     | Read a byte and report status                                                            |

| READ_LAST           | Non-intrusive                | E8/SS/RD            | Re-read byte from address just read and report status                                    |

| WRITE_BYTE          | Non-intrusive                | C0/AAAA/WD/d        | Write a byte to target memory                                                            |

| WRITE_BYTE_WS       | Non-intrusive                | C1/AAAA/WD/d/SS     | Write a byte and report status                                                           |

| READ_BKPT           | Non-intrusive                | E2/RBKP             | Read BDCBKPT breakpoint register                                                         |

| WRITE_BKPT          | Non-intrusive                | C2/WBKP             | Write BDCBKPT breakpoint register                                                        |

| GO                  | Active BDM                   | 08/d                | Go to execute the user application program starting at the address currently in the PC   |

| TRACE1              | Active BDM                   | 10/d                | Trace 1 user instruction at the address in the PC, then return to active background mode |

| TAGGO               | Active BDM                   | 18/d                | Same as GO but enable external tagging<br>(HCS08 devices have no external tagging pin)   |

| READ_A              | Active BDM                   | 68/d/RD             | Read accumulator (A)                                                                     |

| READ_CCR            | Active BDM                   | 69/d/RD             | Read condition code register (CCR)                                                       |

| READ_PC             | Active BDM                   | 6B/d/RD16           | Read program counter (PC)                                                                |

| READ_HX             | Active BDM                   | 6C/d/RD16           | Read H and X register pair (H:X)                                                         |

| READ_SP             | Active BDM                   | 6F/d/RD16           | Read stack pointer (SP)                                                                  |

| READ_NEXT           | Active BDM                   | 70/d/RD             | Increment H:X by one then read memory byte<br>located at H:X                             |

| READ_NEXT_WS        | Active BDM                   | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.       |

| WRITE_A             | Active BDM                   | 48/WD/d             | Write accumulator (A)                                                                    |

| WRITE_CCR           | Active BDM                   | 49/WD/d             | Write condition code register (CCR)                                                      |

| WRITE_PC            | Active BDM                   | 4B/WD16/d           | Write program counter (PC)                                                               |

| WRITE_HX            | Active BDM                   | 4C/WD16/d           | Write H and X register pair (H:X)                                                        |

| WRITE_SP            | Active BDM                   | 4F/WD16/d           | Write stack pointer (SP)                                                                 |

| WRITE_NEXT          | Active BDM                   | 50/WD/d             | Increment H:X by one, then write memory byte<br>located at H:X                           |

| WRITE_NEXT_WS       | Active BDM                   | 51/WD/d/SS          | Increment H:X by one, then write memory byte<br>located at H:X. Also report status.      |

| Table | 17-1. | BDC | Command | Summary |

|-------|-------|-----|---------|---------|

|       |       |     |         |         |

<sup>1</sup> The SYNC command is a special operation that does not have a command code.

#### A.12.3 SPI

Table A-15 and Figure A-14 through Figure A-17 describe the timing requirements for the SPI system.

|                  |   |                                              |                   |                              |                                       |                                      | Temp<br>Rated |             |

|------------------|---|----------------------------------------------|-------------------|------------------------------|---------------------------------------|--------------------------------------|---------------|-------------|

| Num <sup>1</sup> | С | Rating <sup>2</sup>                          | Symbol            | Min                          | Max                                   | Unit                                 | Standard      | AEC Grade 0 |

| 1                | D | Cycle time<br>Master<br>Slave                |                   | 2<br>4                       | 2048                                  | t <sub>cyc</sub><br>t <sub>cyc</sub> | ٠             | •           |

| 2                | D | Enable lead time<br>Master<br>Slave          |                   | <br>1/2                      | 1/2                                   | t <sub>SCK</sub><br>t <sub>SCK</sub> | •             | •           |

| 3                | D | Enable lag time<br>Master<br>Slave           |                   | <br>1/2                      | 1/2                                   | t <sub>SCK</sub><br>t <sub>SCK</sub> | ٠             | •           |

| 4                | D | Clock (SPSCK) high time<br>Master and Slave  | t <sub>SCKH</sub> | 1/2 t <sub>SCK</sub> – 25    | _                                     | ns                                   | ٠             | •           |

| 5                | D | Clock (SPSCK) low time<br>Master and Slave   | t <sub>SCKL</sub> | 1/2 t <sub>SCK</sub> – 25    | _                                     | ns                                   | ٠             | •           |

| 6                | D | Data setup time (inputs)<br>Master<br>Slave  |                   | 30<br>30                     |                                       | ns<br>ns                             | ٠             | •           |

| 7                | D | Data hold time (inputs)<br>Master<br>Slave   |                   | 30<br>30                     |                                       | ns<br>ns                             | ٠             | •           |

| 8                | D | Access time, slave <sup>3</sup>              | t <sub>A</sub>    | 0                            | 40                                    | ns                                   | ٠             | •           |

| 9                | D | Disable time, slave <sup>4</sup>             | t <sub>dis</sub>  | _                            | 40                                    | ns                                   | •             | •           |

| 10               | D | Data setup time (outputs)<br>Master<br>Slave |                   |                              | 25<br>25                              | ns<br>ns                             | •             | •           |

| 11               | D | Data hold time (outputs)<br>Master<br>Slave  |                   | -10<br>-10                   | _                                     | ns<br>ns                             | ٠             | •           |

| 12               | D | Operating frequency<br>Master<br>Slave       |                   | f <sub>Bus</sub> /2048<br>dc | 5 <sup>5</sup><br>f <sub>Bus</sub> /4 | MHz                                  | •             | •           |

| Table | A-15. | SPI          | Electrical | Characteristic |

|-------|-------|--------------|------------|----------------|

| IUNIC | A 10. | <b>U</b> I I | LICOUIDUI  | onaraotoristio |

<sup>1</sup> Refer to Figure A-14 through Figure A-17.

<sup>2</sup> All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins. All timing assumes slew rate control disabled and high drive strength enabled for SPI output pins.

# Appendix B Ordering Information and Mechanical Drawings

# **B.1** Ordering Information

This section contains ordering information for MC9S08SG32 and MC9S08SG16 devices.

| Part Number <sup>1</sup> | Mem   | ory | Temp     | Rated       | Available Packages <sup>2</sup> |                       |          |

|--------------------------|-------|-----|----------|-------------|---------------------------------|-----------------------|----------|

|                          | Flash | RAM | Standard | AEC Grade 0 | 28-Pin                          | 20-Pin                | 16-Pin   |

| MC9S08SG32               | 32K   | 1K  | •        | •           | 28 TSSOP                        | 20 TSSOP <sup>3</sup> | 16 TSSOP |

| MC9S08SG16               | 16K   |     | •        | •           | 201000F                         | 2013306               | 101330F  |

### Table B-1. Device Numbering System

<sup>1</sup> See Table 1-1 for a complete description of modules included on each device.

<sup>2</sup> See Table B-2 for package information.

<sup>3</sup> 20-pin TSSOP package is not available on the AEC Grade 0 high-temperature rated devices.