Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                      |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | · .                                                                     |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package    | 20-TSSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg32e1ctjr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.4 RAM

The MC9S08SG32 Series includes static RAM. The locations in RAM below 0x0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait, stop2, or stop3 mode. At power-on the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention ( $V_{RAM}$ ).

For compatibility with M68HC05 MCUs, the HCS08 resets the stack pointer to 0x00FF. In the MC9S08SG32 Series, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM in the Freescale Semiconductor-provided equate file).

LDHX #RamLast+1 ;point one past RAM TXS ;SP<-(H:X-1)

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.6, "Security", for a detailed description of the security feature.

# 4.5 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I,* Freescale Semiconductor document order number HCS08RMv1/D.

Chapter 5 Resets, Interrupts, and General System Control

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COP watchdog is enabled (see Section 5.7.3, "System Options Register 1 (SOPT1)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPT bits in SOPT1.

The COP counter is reset by writing 0x0055 and 0x00AA (in this order) to the address of SRS during the selected timeout period. Writes do not affect the data in the read-only SRS. As soon as the write sequence is done, the COP timeout period is restarted. If the program fails to do this during the time-out period, the MCU will reset. Also, if any value other than 0x0055 or 0x00AA is written to SRS, the MCU is immediately reset.

The COPCLKS bit in SOPT2 (see Section 5.7.4, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there are three associated time-outs controlled by the COPT bits in SOPT1. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 1-kHz clock source and the longest time-out (2<sup>10</sup> cycles).

| Contr   | ol Bits   | Clock Source | COP Window <sup>1</sup> Opens | COP Overflow Count                             |

|---------|-----------|--------------|-------------------------------|------------------------------------------------|

| COPCLKS | COPT[1:0] |              | (COPW = 1)                    | COP Overnow Count                              |

| N/A     | 0:0       | N/A          | N/A                           | COP is disabled                                |

| 0       | 0:1       | 1 kHz        | N/A                           | 2 <sup>5</sup> cycles (32 ms <sup>2</sup> )    |

| 0       | 1:0       | 1 kHz        | N/A                           | 2 <sup>8</sup> cycles (256 ms <sup>1</sup> )   |

| 0       | 1:1       | 1 kHz        | N/A                           | 2 <sup>10</sup> cycles (1.024 s <sup>1</sup> ) |

| 1       | 0:1       | Bus          | 6144 cycles                   | 2 <sup>13</sup> cycles                         |

| 1       | 1:0       | Bus          | 49,152 cycles                 | 2 <sup>16</sup> cycles                         |

| 1       | 1:1       | Bus          | 196,608 cycles                | 2 <sup>18</sup> cycles                         |

### Table 5-1. COP Configuration Options

<sup>1</sup> Windowed COP operation requires the user to clear the COP timer in the last 25% of the selected timeout period. This column displays the minimum number of clock counts required before the COP timer can be reset when in windowed COP mode (COPW = 1).

<sup>2</sup> Values shown in milliseconds based on  $t_{LPO} = 1$  ms. See  $t_{LPO}$  in the appendix Section A.12.1, "Control Timing," for the tolerance of this value.

When the bus clock source is selected, windowed COP operation is available by setting COPW in the SOPT2 register. In this mode, writes to the SRS register to clear the COP timer must occur in the last 25% of the selected timeout period. A premature write immediately resets the MCU. When the 1-kHz clock source is selected, windowed COP operation is not available.

| Vector<br>Priority  | Vector<br>Number | Address<br>(High/Low) | Vector<br>Name | Module            | Source                                                           | Enable                           | Description                                                                               |

|---------------------|------------------|-----------------------|----------------|-------------------|------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------|

|                     | 31               | 0xFFC0/0xFFC1         | _              | _                 |                                                                  |                                  | _                                                                                         |

| Lowest              | 30               | 0xFFC2/0xFFC3         | Vacmp          | ACMP              | ACF                                                              | ACIE                             | Analog comparator                                                                         |

|                     | 29               | 0xFFC4/0xFFC5         | _              | _                 |                                                                  |                                  | —                                                                                         |

|                     | 28               | 0xFFC6/0xFFC7         | _              |                   |                                                                  |                                  | _                                                                                         |

|                     | 27               | 0xFFC8/0xFFC9         |                | _                 |                                                                  | —                                | _                                                                                         |

|                     | 26               | 0xFFCA/0xFFCB         | Vmtim          | MTIM              | TOF                                                              | TOIE                             | MTIM overflow                                                                             |

|                     | 25               | 0xFFCC/0xFFCD         | Vrtc           | RTC               | RTIF                                                             | RTIE                             | Real-time interrupt                                                                       |

|                     | 24               | 0xFFCE/0xFFCF         | Viic           | IIC               | IICIS                                                            | IICIE                            | IIC control                                                                               |

|                     | 23               | 0xFFD0/0xFFD1         | Vadc           | ADC               | COCO                                                             | AIEN                             | ADC                                                                                       |

|                     | 22               | 0xFFD2/0xFFD3         | _              | _                 | —                                                                | —                                | —                                                                                         |

|                     | 21               | 0xFFD4/0xFFD5         | Vportb         | Port B            | PTBIF                                                            | PTBIE                            | Port B Pins                                                                               |

|                     | 20               | 0xFFD6/0xFFD7         | Vporta         | Port A            | PTAIF                                                            | PTAIE                            | Port A Pins                                                                               |

|                     | 19               | 0xFFD8/0xFFD9         |                | _                 | _                                                                | _                                | _                                                                                         |

|                     | 18               | 0xFFDA/0xFFDB         | Vscitx         | SCI               | TDRE, TC                                                         | TIE, TCIE                        | SCI transmit                                                                              |

|                     | 17               | 0xFFDC/0xFFDD         | Vscirx         | SCI               | IDLE, RDRF,<br>LDBKDIF,<br>RXEDGIF                               | ILIE, RIE,<br>LBKDIE,<br>RXEDGIE | SCI receive                                                                               |

|                     | 16 0xFFDE/0xFFDF |                       | Vscierr        | SCI               | OR, NF,<br>FE, PF                                                | ORIE, NFIE,<br>FEIE, PFIE        | SCI error                                                                                 |

|                     | 15               | 0xFFE0/0xFFE1         | Vspi           | SPI               | SPIF, MODF,<br>SPTEF                                             | SPIE, SPIE, SPTIE                | SPI                                                                                       |

|                     | 14               | 0xFFE2/0xFFE3         | Vtpm2ovf       | TPM2              | TOF                                                              | TOIE                             | TPM2 overflow                                                                             |

|                     | 13               | 0xFFE4/0xFFE5         | Vtpm2ch1       | TPM2              | CH1F                                                             | CH1IE                            | TPM2 channel 1                                                                            |

|                     | 12               | 0xFFE6/0xFFE7         | Vtpm2ch0       | TPM2              | CH0F                                                             | CH0IE                            | TPM2 channel 0                                                                            |

|                     | 11               | 0xFFE8/0xFFE9         | Vtpm1ovf       | TPM1              | TOF                                                              | TOIE                             | TPM1 overflow                                                                             |

|                     | 10               | 0xFFEA/0xFFEB         | —              | —                 | —                                                                | —                                | —                                                                                         |

|                     | 9                | 0xFFEC/0xFFED         | _              | _                 | —                                                                |                                  | —                                                                                         |

|                     | 8                | 0xFFEE/0xFFEF         | —              | —                 | —                                                                |                                  | —                                                                                         |

|                     | 7                | 0xFFF0/0xFFF1         | —              | —                 | —                                                                | —                                | —                                                                                         |

|                     | 6                | 0xFFF2/0xFFF3         | Vtpm1ch1       | TPM1              | CH1F                                                             | CH1IE                            | TPM1 channel 1                                                                            |

|                     | 5                | 0xFFF4/0xFFF5         | Vtpm1ch0       | TPM1              | CH0F                                                             | CH0IE                            | TPM1 channel 0                                                                            |

|                     | 4                | 0xFFF6/0xFFF7         | —              | —                 | —                                                                | —                                | —                                                                                         |

|                     | 3                | 0xFFF8/0xFFF9         | Vlvd           | Systemcon<br>trol | LVWF                                                             | LVWIE                            | Low-voltage warning                                                                       |

|                     | 2                | 0xFFFA/0xFFFB         | _              | —                 | —                                                                |                                  | —                                                                                         |

|                     | 1                | 0xFFFC/0xFFFD         | Vswi           | Core              | SWI Instruction                                                  | —                                | Software interrupt                                                                        |

| <b>▼</b><br>Highest | 0                | 0xFFFE/0xFFFF         | Vreset         | System<br>control | COP,<br>LVD,<br>RESET pin,<br>Illegal opcode,<br>Illegal address | COPE<br>LVDRE<br>—<br>—<br>—     | Watchdog timer<br>Low-voltage detect<br>External pin<br>Illegal opcode<br>Illegal address |

#### Table 5-2. Vector Summary

Chapter 6 Parallel Input/Output Control

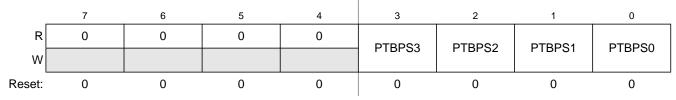

## 6.6.2.7 Port B Interrupt Pin Select Register (PTBPS)

Figure 6-17. Port B Interrupt Pin Select Register (PTBPS)

#### Table 6-16. PTBPS Register Field Descriptions

| Fie          | əld | Description                                                                                                                                                                                             |

|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTBPS |     | <ul> <li>Port B Interrupt Pin Selects — Each of the PTBPSn bits enable the corresponding port B interrupt pin.</li> <li>0 Pin not enabled as interrupt.</li> <li>1 Pin enabled as interrupt.</li> </ul> |

### 6.6.2.8 Port B Interrupt Edge Select Register (PTBES)

|        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

| R      | 0 | 0 | 0 | 0 | PTBES3 | PTBES2 | PTBES1 | PTBES0 |

| W      |   |   |   |   | FIDESS | FIDESZ | FIDESI | FIDESU |

| Reset: | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

#### Figure 6-18. Port B Edge Select Register (PTBES)

#### Table 6-17. PTBES Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port B Edge Selects — Each of the PTBESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.</li> <li>0 A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.</li> <li>1 A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation.</li> </ul> |

## 7.2.3 Stack Pointer (SP)

This 16-bit address pointer register points at the next available location on the automatic last-in-first-out (LIFO) stack. The stack may be located anywhere in the 64-Kbyte address space that has RAM and can be any size up to the amount of available RAM. The stack is used to automatically save the return address for subroutine calls, the return address and CPU registers during interrupts, and for local variables. The AIS (add immediate to stack pointer) instruction adds an 8-bit signed immediate value to SP. This is most often used to allocate or deallocate space for local variables on the stack.

SP is forced to 0x00FF at reset for compatibility with the earlier M68HC05 Family. HCS08 programs normally change the value in SP to the address of the last location (highest address) in on-chip RAM during reset initialization to free up direct page RAM (from the end of the on-chip registers to 0x00FF).

The RSP (reset stack pointer) instruction was included for compatibility with the M68HC05 Family and is seldom used in new HCS08 programs because it only affects the low-order half of the stack pointer.

## 7.2.4 Program Counter (PC)

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

During normal program execution, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, interrupt, and return operations load the program counter with an address other than that of the next sequential location. This is called a change-of-flow.

During reset, the program counter is loaded with the reset vector that is located at 0xFFFE and 0xFFFF. The vector stored there is the address of the first instruction that will be executed after exiting the reset state.

# 7.2.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask (I) and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code bits in general terms. For a more detailed explanation of how each instruction sets the CCR bits, refer to the *HCS08 Family Reference Manual, volume 1*, Freescale Semiconductor document order number HCS08RMv1.

## 7.4.5 **BGND** Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

#### Chapter 7 Central Processor Unit (S08CPUV3)

| Source                                                                                                          |                                                                                                                                                                                                                              | ess<br>de                                           |                                                                                  | les                             | Cyc-by-Cyc                                                | Affecton CCR          |           |  |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------|-----------------------|-----------|--|

| Form                                                                                                            | Operation                                                                                                                                                                                                                    | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Details                                                   | <b>V</b> 1 1 <b>H</b> | INZC      |  |

| INC opr8a<br>INCA<br>INCX<br>INC oprx8,X<br>INC ,X<br>INC oprx8,SP                                              | $\begin{array}{ccc} \text{Increment} & M \leftarrow (M) + \$01 \\ & A \leftarrow (A) + \$01 \\ & X \leftarrow (X) + \$01 \\ & M \leftarrow (M) + \$01 \\ & M \leftarrow (M) + \$01 \\ & M \leftarrow (M) + \$01 \end{array}$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C dd<br>4C<br>5C<br>6C ff<br>7C<br>9E 6C ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp                     | ↓11-                  | - ↓ ↓ -   |  |

| JMP opr8a<br>JMP opr16a<br>JMP oprx16,X<br>JMP oprx8,X<br>JMP ,X                                                | Jump<br>PC ← Jump Address                                                                                                                                                                                                    | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC dd<br>CC hh ll<br>DC ee ff<br>EC ff<br>FC                                     | 3<br>4<br>4<br>3<br>3           | 900<br>900<br>9000<br>9000<br>9000<br>9000<br>9000        | - 1 1 -               |           |  |

| JSR opr8a<br>JSR opr16a<br>JSR oprx16,X<br>JSR oprx8,X<br>JSR ,X                                                | Jump to Subroutine<br>PC $\leftarrow$ (PC) + n (n = 1, 2, or 3)<br>Push (PCL); SP $\leftarrow$ (SP) – \$0001<br>Push (PCH); SP $\leftarrow$ (SP) – \$0001<br>PC $\leftarrow$ Unconditional Address                           | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD dd<br>CD hh ll<br>DD ee ff<br>ED ff<br>FD                                     | 5<br>6<br>5<br>5                | ssppp<br>pssppp<br>ssppp<br>ssppp                         | - 1 1 -               |           |  |

| LDA #opr8i<br>LDA opr8a<br>LDA opr16a<br>LDA oprx16,X<br>LDA oprx8,X<br>LDA ,X<br>LDA oprx16,SP<br>LDA oprx8,SP | Load Accumulator from Memory $A \leftarrow (M)$                                                                                                                                                                              | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A6 ii<br>B6 dd<br>C6 hh ll<br>D6 ee ff<br>E6 ff<br>F6<br>9E D6 ee ff<br>9E E6 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp  | 011-                  | - \$ \$ - |  |

| LDHX #opr16i<br>LDHX opr8a<br>LDHX opr16a<br>LDHX ,X<br>LDHX oprx16,X<br>LDHX oprx8,X<br>LDHX oprx8,SP          | Load Index Register (H:X)<br>H:X ← (M:M + \$0001)                                                                                                                                                                            | IMM<br>DIR<br>EXT<br>IX<br>IX2<br>IX1<br>SP1        | 45 jj kk<br>55 dd<br>32 hh 11<br>9E AE<br>9E BE ee ff<br>9E CE ff<br>9E FE ff    | 3<br>4<br>5<br>5<br>6<br>5<br>5 | ppp<br>rrpp<br>prrpp<br>prrfp<br>pprrpp<br>prrpp<br>prrpp | 011-                  | - ↓ ↓ -   |  |

| LDX #opr8i<br>LDX opr8a<br>LDX opr16a<br>LDX oprx16,X<br>LDX oprx8,X<br>LDX ,X<br>LDX oprx16,SP<br>LDX oprx8,SP | Load X (Index Register Low) from Memory $X \leftarrow (M)$                                                                                                                                                                   | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AE ii<br>BE dd<br>CE hh ll<br>DE ee ff<br>EE ff<br>FE<br>9E DE ee ff<br>9E EE ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp  | 011-                  | - \$ \$ - |  |

| LSL opr8a<br>LSLA<br>LSLX<br>LSL oprx8,X<br>LSL ,X<br>LSL oprx8,SP                                              | Logical Shift Left<br>- $        -$                                                                                                                                                                                          | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp                | ↓11-                  | - ↓ ↓ ↓   |  |

| LSR opr8a<br>LSRA<br>LSRX<br>LSR oprx8,X<br>LSR ,X<br>LSR oprx8,SP                                              | Logical Shift Right<br>0                                                                                                                                                                                                     | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34 dd<br>44<br>54<br>64 ff<br>74<br>9E 64 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp                | ↓11-                  | - 0 ‡ ‡   |  |

Table 7-2. Instruction Set Summary (Sheet 5 of 9)

## 9.2.1 Analog Power (V<sub>DDA</sub>)

The ADC analog portion uses  $V_{DDA}$  as its power connection. In some packages,  $V_{DDA}$  is connected internally to  $V_{DD}$ . If externally available, connect the  $V_{DDA}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDA}$  for good results.

## 9.2.2 Analog Ground (V<sub>SSA</sub>)

The ADC analog portion uses  $V_{SSA}$  as its ground connection. In some packages,  $V_{SSA}$  is connected internally to  $V_{SS}$ . If externally available, connect the  $V_{SSA}$  pin to the same voltage potential as  $V_{SS}$ .

## 9.2.3 Voltage Reference High (V<sub>REFH</sub>)

$V_{REFH}$  is the high reference voltage for the converter. In some packages,  $V_{REFH}$  is connected internally to  $V_{DDA}$ . If externally available,  $V_{REFH}$  may be connected to the same potential as  $V_{DDA}$  or may be driven by an external source between the minimum  $V_{DDA}$  spec and the  $V_{DDA}$  potential ( $V_{REFH}$  must never exceed  $V_{DDA}$ ).

## 9.2.4 Voltage Reference Low (V<sub>REFL</sub>)

$V_{REFL}$  is the low-reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSA}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSA}$ .

### 9.2.5 Analog Channel Inputs (ADx)

The ADC module supports up to 28 separate analog inputs. An input is selected for conversion through the ADCH channel select bits.

## 9.3 Register Definition

These memory-mapped registers control and monitor operation of the ADC:

- Status and control register, ADCSC1

- Status and control register, ADCSC2

- Data result registers, ADCRH and ADCRL

- Compare value registers, ADCCVH and ADCCVL

- Configuration register, ADCCFG

- Pin control registers, APCTLx<sup>1</sup>

<sup>1.</sup> Number of APCTLx registers depends on the number of external analog inputs available on the device. Please refer to the introduction of this module for external analog input assignments.

the intermediate conversion data is lost. In 8-bit mode, there is no interlocking with ADCRH. If the MODE bits are changed, any data in ADCRL becomes invalid.

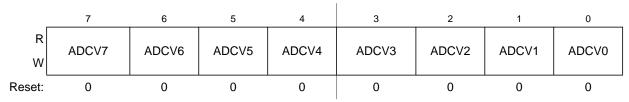

Figure 9-6. Data Result Low Register (ADCRL)

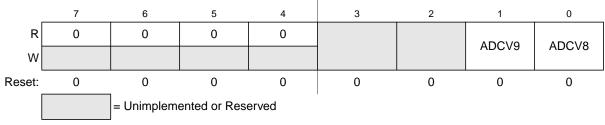

## 9.3.5 Compare Value High Register (ADCCVH)

In 10-bit mode, the ADCCVH register holds the upper two bits of the 10-bit compare value (ADCV[9:8]). When the compare function is enabled, these bits are compared to the upper two bits of the result following a conversion in 10-bit mode.

In 8-bit operation, ADCCVH is not used during compare.

## 9.3.6 Compare Value Low Register (ADCCVL)

The ADCCVL register holds the lower eight bits of the 10-bit compare value or all eight bits of the 8-bit compare value. When the compare function is enabled, bits ADCV[7:0] are compared to the lower eight bits of the result following a conversion in 10-bit or 8-bit mode.

Figure 9-8. Compare Value Low Register (ADCCVL)

# 9.3.7 Configuration Register (ADCCFG)

ADCCFG selects the mode of operation, clock source, clock divide, and configures for low power and long sample time.

MC9S08SG32 Data Sheet, Rev. 8

| Field       | Description                                                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC17 | <ul> <li>ADC Pin Control 17 — ADPC17 controls the pin associated with channel AD17.</li> <li>0 AD17 pin I/O control enabled</li> <li>1 AD17 pin I/O control disabled</li> </ul> |

| 0<br>ADPC16 | <ul> <li>ADC Pin Control 16 — ADPC16 controls the pin associated with channel AD16.</li> <li>0 AD16 pin I/O control enabled</li> <li>1 AD16 pin I/O control disabled</li> </ul> |

#### Table 9-12. APCTL3 Register Field Descriptions (continued)

# 9.4 Functional Description

The ADC module is disabled during reset or when the ADCH bits are all high. The module is idle when a conversion has completed and another conversion has not been initiated. When idle, the module is in its lowest power state.

The ADC can perform an analog-to-digital conversion on any of the software selectable channels. The selected channel voltage is converted by a successive approximation algorithm into an 11-bit digital result. In 8-bit mode, the selected channel voltage is converted by a successive approximation algorithm into a 9-bit digital result.

When the conversion is completed, the result is placed in the data registers (ADCRH and ADCRL). In 10-bit mode, the result is rounded to 10 bits and placed in ADCRH and ADCRL. In 8-bit mode, the result is rounded to 8 bits and placed in ADCRL. The conversion complete flag (COCO) is then set and an interrupt is generated if the conversion complete interrupt has been enabled (AIEN = 1).

The ADC module has the capability of automatically comparing the result of a conversion with the contents of its compare registers. The compare function is enabled by setting the ACFE bit and operates with any of the conversion modes and configurations.

## 9.4.1 Clock Select and Divide Control

One of four clock sources can be selected as the clock source for the ADC module. This clock source is then divided by a configurable value to generate the input clock to the converter (ADCK). The clock is selected from one of the following sources by means of the ADICLK bits.

- The bus clock, which is equal to the frequency at which software is executed. This is the default selection following reset.

- The bus clock divided by two. For higher bus clock rates, this allows a maximum divide by 16 of the bus clock.

- ALTCLK, as defined for this MCU (See module section introduction).

- The asynchronous clock (ADACK). This clock is generated from a clock source within the ADC module. When selected as the clock source, this clock remains active while the MCU is in wait or stop3 mode and allows conversions in these modes for lower noise operation.

Whichever clock is selected, its frequency must fall within the specified frequency range for ADCK. If the available clocks are too slow, the ADC does not perform according to specifications. If the available clocks

Chapter 10 Inter-Integrated Circuit (S08IICV2)

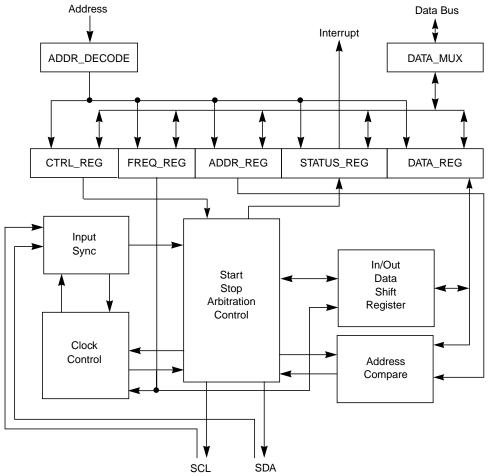

## 10.1.4 Block Diagram

Figure 10-2 is a block diagram of the IIC.

Figure 10-2. IIC Functional Block Diagram

# **10.2 External Signal Description**

This section describes each user-accessible pin signal.

## 10.2.1 SCL — Serial Clock Line

The bidirectional SCL is the serial clock line of the IIC system.

## 10.2.2 SDA — Serial Data Line

The bidirectional SDA is the serial data line of the IIC system.

## **10.3 Register Definition**

This section consists of the IIC register descriptions in address order.

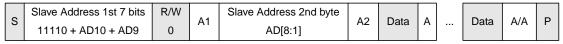

### 10.4.2 10-bit Address

For 10-bit addressing, 0x11110 is used for the first 5 bits of the first address byte. Various combinations of read/write formats are possible within a transfer that includes 10-bit addressing.

### 10.4.2.1 Master-Transmitter Addresses a Slave-Receiver

The transfer direction is not changed (see Table 10-10). When a 10-bit address follows a start condition, each slave compares the first seven bits of the first byte of the slave address (11110XX) with its own address and tests whether the eighth bit ( $R/\overline{W}$  direction bit) is 0. More than one device can find a match and generate an acknowledge (A1). Then, each slave that finds a match compares the eight bits of the second byte of the slave address with its own address. Only one slave finds a match and generates an acknowledge (A2). The matching slave remains addressed by the master until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

Table 10-10. Master-Transmitter Addresses Slave-Receiver with a 10-bit Address

After the master-transmitter has sent the first byte of the 10-bit address, the slave-receiver sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

### 10.4.2.2 Master-Receiver Addresses a Slave-Transmitter

The transfer direction is changed after the second  $R/\overline{W}$  bit (see Table 10-11). Up to and including acknowledge bit A2, the procedure is the same as that described for a master-transmitter addressing a slave-receiver. After the repeated start condition (Sr), a matching slave remembers that it was addressed before. This slave then checks whether the first seven bits of the first byte of the slave address following Sr are the same as they were after the start condition (S) and tests whether the eighth ( $R/\overline{W}$ ) bit is 1. If there is a match, the slave considers that it has been addressed as a transmitter and generates acknowledge A3. The slave-transmitter remains addressed until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

After a repeated start condition (Sr), all other slave devices also compare the first seven bits of the first byte of the slave address with their own addresses and test the eighth  $(R/\overline{W})$  bit. However, none of them are addressed because  $R/\overline{W} = 1$  (for 10-bit devices) or the 11110XX slave address (for 7-bit devices) does not match.

| s | Slave Address<br>1st 7 bits | R/W | A1 | Slave Address<br>2nd byte | A2 | Sr | Slave Address<br>1st 7 bits | R/W | A3 | Data | A | <br>Data | A | Р |

|---|-----------------------------|-----|----|---------------------------|----|----|-----------------------------|-----|----|------|---|----------|---|---|

|   | 11110 + AD10 + AD9          | 0   |    | AD[8:1]                   |    |    | 11110 + AD10 + AD9          | 1   |    |      |   |          |   |   |

Table 10-11. Master-Receiver Addresses a Slave-Transmitter with a 10-bit Address

After the master-receiver has sent the first byte of the 10-bit address, the slave-transmitter sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

Chapter 14 Serial Communications Interface (S08SCIV4)

# 14.2 Register Definition

The SCI has eight 8-bit registers to control baud rate, select SCI options, report SCI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SCI registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

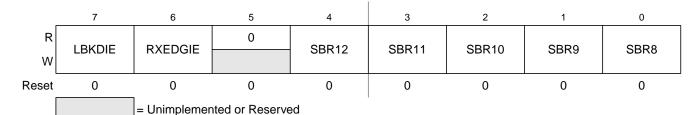

# 14.2.1 SCI Baud Rate Registers (SCIBDH, SCIBDL)

This pair of registers controls the prescale divisor for SCI baud rate generation. To update the 13-bit baud rate setting [SBR12:SBR0], first write to SCIBDH to buffer the high half of the new value and then write to SCIBDL. The working value in SCIBDH does not change until SCIBDL is written.

SCIBDL is reset to a non-zero value, so after reset the baud rate generator remains disabled until the first time the receiver or transmitter is enabled (RE or TE bits in SCIC2 are written to 1).

### Figure 14-4. SCI Baud Rate Register (SCIBDH)

| Field            | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LBKDIE      | <ul> <li>LIN Break Detect Interrupt Enable (for LBKDIF)</li> <li>0 Hardware interrupts from LBKDIF disabled (use polling).</li> <li>1 Hardware interrupt requested when LBKDIF flag is 1.</li> </ul>                                                                                                                                        |

| 6<br>RXEDGIE     | RxD Input Active Edge Interrupt Enable (for RXEDGIF)         0       Hardware interrupts from RXEDGIF disabled (use polling).         1       Hardware interrupt requested when RXEDGIF flag is 1.                                                                                                                                          |

| 4:0<br>SBR[12:8] | <b>Baud Rate Modulo Divisor</b> — The 13 bits in SBR[12:0] are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/(16×BR). See also BR bits in Table 14-2. |

Chapter 16 Timer/PWM Module (S08TPMV3)

are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

# 16.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

The following sections describe the main counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend upon the operating mode, these topics will be covered in the associated mode explanation sections.

## 16.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, end-of-count overflow, up-counting vs. up/down counting, and manual counter reset.

### 16.4.1.1 Counter Clock Source

The 2-bit field, CLKSB:CLKSA, in the timer status and control register (TPMxSC) selects one of three possible clock sources or OFF (which effectively disables the TPM). See Table 16-4. After any MCU reset, CLKSB:CLKSA=0:0 so no clock source is selected, and the TPM is in a very low power state. These control bits may be read or written at any time and disabling the timer (writing 00 to the CLKSB:CLKSA field) does not affect the values in the counter or other timer registers.

| Command<br>Mnemonic | Active BDM/<br>Non-intrusive | Coding<br>Structure | Description                                                                              |

|---------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------|

| SYNC                | Non-intrusive                | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed              |

| ACK_ENABLE          | Non-intrusive                | D5/d                | Enable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.       |

| ACK_DISABLE         | Non-intrusive                | D6/d                | Disable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.      |

| BACKGROUND          | Non-intrusive                | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |

| READ_STATUS         | Non-intrusive                | E4/SS               | Read BDC status from BDCSCR                                                              |

| WRITE_CONTROL       | Non-intrusive                | C4/CC               | Write BDC controls in BDCSCR                                                             |

| READ_BYTE           | Non-intrusive                | E0/AAAA/d/RD        | Read a byte from target memory                                                           |

| READ_BYTE_WS        | Non-intrusive                | E1/AAAA/d/SS/RD     | Read a byte and report status                                                            |

| READ_LAST           | Non-intrusive                | E8/SS/RD            | Re-read byte from address just read and report status                                    |

| WRITE_BYTE          | Non-intrusive                | C0/AAAA/WD/d        | Write a byte to target memory                                                            |

| WRITE_BYTE_WS       | Non-intrusive                | C1/AAAA/WD/d/SS     | Write a byte and report status                                                           |

| READ_BKPT           | Non-intrusive                | E2/RBKP             | Read BDCBKPT breakpoint register                                                         |

| WRITE_BKPT          | Non-intrusive                | C2/WBKP             | Write BDCBKPT breakpoint register                                                        |

| GO                  | Active BDM                   | 08/d                | Go to execute the user application program starting at the address currently in the PC   |

| TRACE1              | Active BDM                   | 10/d                | Trace 1 user instruction at the address in the PC, then return to active background mode |

| TAGGO               | Active BDM                   | 18/d                | Same as GO but enable external tagging<br>(HCS08 devices have no external tagging pin)   |

| READ_A              | Active BDM                   | 68/d/RD             | Read accumulator (A)                                                                     |

| READ_CCR            | Active BDM                   | 69/d/RD             | Read condition code register (CCR)                                                       |

| READ_PC             | Active BDM                   | 6B/d/RD16           | Read program counter (PC)                                                                |

| READ_HX             | Active BDM                   | 6C/d/RD16           | Read H and X register pair (H:X)                                                         |

| READ_SP             | Active BDM                   | 6F/d/RD16           | Read stack pointer (SP)                                                                  |

| READ_NEXT           | Active BDM                   | 70/d/RD             | Increment H:X by one then read memory byte<br>located at H:X                             |

| READ_NEXT_WS        | Active BDM                   | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.       |

| WRITE_A             | Active BDM                   | 48/WD/d             | Write accumulator (A)                                                                    |

| WRITE_CCR           | Active BDM                   | 49/WD/d             | Write condition code register (CCR)                                                      |

| WRITE_PC            | Active BDM                   | 4B/WD16/d           | Write program counter (PC)                                                               |

| WRITE_HX            | Active BDM                   | 4C/WD16/d           | Write H and X register pair (H:X)                                                        |

| WRITE_SP            | Active BDM                   | 4F/WD16/d           | Write stack pointer (SP)                                                                 |

| WRITE_NEXT          | Active BDM                   | 50/WD/d             | Increment H:X by one, then write memory byte<br>located at H:X                           |

| WRITE_NEXT_WS       | Active BDM                   | 51/WD/d/SS          | Increment H:X by one, then write memory byte located at H:X. Also report status.         |

| Table | 17-1. | BDC | Command | Summary |

|-------|-------|-----|---------|---------|

|       |       |     |         |         |

<sup>1</sup> The SYNC command is a special operation that does not have a command code.

**Chapter 17 Development Support**

A-Only — Trigger when the address matches the value in comparator A

A OR B — Trigger when the address matches either the value in comparator A or the value in comparator B

A Then B — Trigger when the address matches the value in comparator B but only after the address for another cycle matched the value in comparator A. There can be any number of cycles after the A match and before the B match.

A AND B Data (Full Mode) — This is called a full mode because address, data, and R/W (optionally) must match within the same bus cycle to cause a trigger event. Comparator A checks address, the low byte of comparator B checks data, and R/W is checked against RWA if RWAEN = 1. The high-order half of comparator B is not used.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

A AND NOT B Data (Full Mode) — Address must match comparator A, data must not match the low half of comparator B, and R/W must match RWA if RWAEN = 1. All three conditions must be met within the same bus cycle to cause a trigger.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**Event-Only B** (Store Data) — Trigger events occur each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

A Then Event-Only B (Store Data) — After the address has matched the value in comparator A, a trigger event occurs each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

**Inside Range** ( $A \le Address \le B$ ) — A trigger occurs when the address is greater than or equal to the value in comparator A and less than or equal to the value in comparator B at the same time.

**Outside Range** (Address < A or Address > B) — A trigger occurs when the address is either less than the value in comparator A or greater than the value in comparator B.

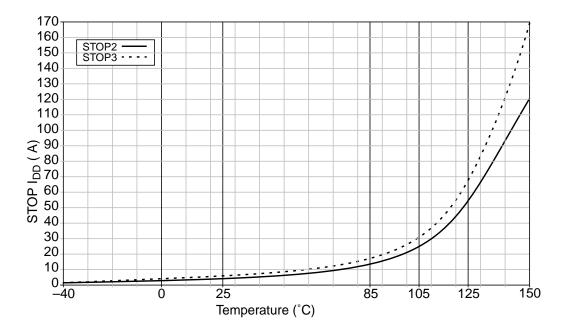

Figure A-7. Typical Stop  $I_{DD}$  vs. Temperature ( $V_{DD}$  = 5V)

- $^1\,$  Typical data was characterized at 5.0 V, 25°C or is recommended value.

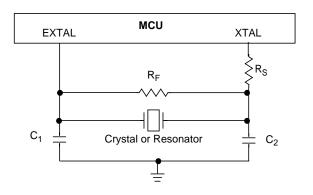

- $^2$  The input clock source must be divided using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

- <sup>3</sup> Characterized and not tested on each device. Proper PC board layout procedures must be followed to achieve specifications.

- <sup>4</sup> 4 MHz crystal

# A.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see the Memory section.

| # C |                                         |                                                  |                             |        |         |        | Temp<br>Rated     |          |             |

|-----|-----------------------------------------|--------------------------------------------------|-----------------------------|--------|---------|--------|-------------------|----------|-------------|

|     | С                                       | Characteristic                                   | Symbol                      | Min    | Typical | Max    | Unit              | Standard | AEC Grade 0 |

| 1   | _                                       | Supply voltage for program/erase                 | V <sub>prog/era</sub><br>se | 2.7    | _       | 5.5    | V                 | •        | •           |

| 2   | _                                       | Supply voltage for read operation                | V <sub>Read</sub>           | 2.7    | —       | 5.5    | V                 | •        | •           |

| 3   | —                                       | Internal FCLK frequency <sup>1</sup>             | f <sub>FCLK</sub>           | 150    | —       | 200    | kHz               | •        | •           |

| 4   | —                                       | Internal FCLK period (1/f <sub>FCLK</sub> )      | t <sub>Fcyc</sub>           | 5      | —       | 6.67   | μs                | •        | •           |

| 5   | _                                       | Byte program time (random location) <sup>2</sup> | t <sub>prog</sub>           | 9      |         |        | t <sub>Fcyc</sub> | •        | •           |

| 6   | -                                       | Byte program time (burst mode) <sup>2</sup>      | t <sub>Burst</sub>          | 4      |         |        | t <sub>Fcyc</sub> | •        | •           |

| 7   | _                                       | Page erase time <sup>2</sup>                     | t <sub>Page</sub>           | 4000   |         |        | t <sub>Fcyc</sub> | •        | •           |

| 8   | _                                       | Mass erase time <sup>2</sup>                     | t <sub>Mass</sub>           | 20,000 |         |        | t <sub>Fcyc</sub> |          |             |

| 9 C | Program/erase endurance <sup>3</sup>    | n <sub>FLPE</sub>                                |                             |        |         | cycles |                   |          |             |

|     | $T_L$ to $T_H = -40^{\circ}C$ to +125°C |                                                  | 10,000                      | _      | —       |        | •                 | _        |             |

|     |                                         | $T_L$ to $T_H = -40^{\circ}C$ to +150°C          |                             | 10,000 | _       | —      |                   | _        | •           |

|     |                                         | T = 25°C                                         |                             | 10,000 | 100,000 |        |                   | •        | •           |

| 10  | С                                       | Data retention <sup>4</sup>                      | t <sub>D_ret</sub>          | 15     | 100     |        | years             | •        | •           |

Table A-16. Flash Characteristics

<sup>1</sup> The frequency of this clock is controlled by a software setting.

<sup>2</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>3</sup> **Typical endurance for Flash** is based upon the intrinsic bit cell performance. For additional information on how Freescale defines typical endurance, please refer to Engineering Bulletin EB619/D, *Typical Endurance for Nonvolatile Memory*.

<sup>4</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines typical data retention, please refer to Engineering Bulletin EB618/D, *Typical Data Retention for Nonvolatile Memory.*

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 1-303-675-2140 Fax: 1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007-2010. All rights reserved.