Welcome to **E-XFL.COM**

## **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                   |

|--------------------------------|-----------------------------------------------------------------------------------|

| Product Status                 | Active                                                                            |

| Number of LABs/CLBs            | 264                                                                               |

| Number of Logic Elements/Cells | 2112                                                                              |

| Total RAM Bits                 | 75776                                                                             |

| Number of I/O                  | 206                                                                               |

| Number of Gates                | -                                                                                 |

| Voltage - Supply               | 2.375V ~ 3.465V                                                                   |

| Mounting Type                  | Surface Mount                                                                     |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                                |

| Package / Case                 | 256-LBGA                                                                          |

| Supplier Device Package        | 256-FTBGA (17x17)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-2000hc-4ftg256i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Introduction

The MachXO2 family of ultra low power, instant-on, non-volatile PLDs has six devices with densities ranging from 256 to 6864 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, User Flash Memory (UFM), Phase Locked Loops (PLLs), preengineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and timer/counter. These features allow these devices to be used in low cost, high volume consumer and system applications.

The MachXO2 devices are designed on a 65 nm non-volatile low power process. The device architecture has several features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs and oscillators dynamically. These features help manage static and dynamic power consumption resulting in low static power for all members of the family.

The MachXO2 devices are available in two versions – ultra low power (ZE) and high performance (HC and HE) devices. The ultra low power devices are offered in three speed grades –1, –2 and –3, with –3 being the fastest. Similarly, the high-performance devices are offered in three speed grades: –4, –5 and –6, with –6 being the fastest. HC devices have an internal linear voltage regulator which supports external  $V_{CC}$  supply voltages of 3.3 V or 2.5 V. ZE and HE devices only accept 1.2 V as the external  $V_{CC}$  supply voltage. With the exception of power supply voltage all three types of devices (ZE, HC and HE) are functionally compatible and pin compatible with each other.

The MachXO2 PLDs are available in a broad range of advanced halogen-free packages ranging from the space saving 2.5 mm x 2.5 mm WLCSP to the 23 mm x 23 mm fpBGA. MachXO2 devices support density migration within the same package. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters.

The pre-engineered source synchronous logic implemented in the MachXO2 device family supports a broad range of interface standards, including LPDDR, DDR, DDR2 and 7:1 gearing for display I/Os.

The MachXO2 devices offer enhanced I/O features such as drive strength control, slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a "per-pin" basis.

A user-programmable internal oscillator is included in MachXO2 devices. The clock output from this oscillator may be divided by the timer/counter for use as clock input in functions such as LED control, key-board scanner and similar state machines.

The MachXO2 devices also provide flexible, reliable and secure configuration from on-chip Flash memory. These devices can also configure themselves from external SPI Flash or be configured by an external master through the JTAG test access port or through the I<sup>2</sup>C port. Additionally, MachXO2 devices support dual-boot capability (using external Flash memory) and remote field upgrade (TransFR) capability.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the MachXO2 family of devices. Popular logic synthesis tools provide synthesis library support for MachXO2. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the MachXO2 device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) LatticeCORE™ modules, including a number of reference designs licensed free of charge, optimized for the MachXO2 PLD family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increasing their productivity.

The logic blocks, Programmable Functional Unit (PFU) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each row has either the logic blocks or the EBR blocks. The PIO cells are located at the periphery of the device, arranged in banks. The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the MachXO2 family, the number of sysIO banks varies by device. There are different types of I/O buffers on the different banks. Refer to the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks; these blocks are found in MachXO2-640/U and larger devices. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT usage.

The MachXO2 registers in PFU and sysl/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

The MachXO2 architecture also provides up to two sysCLOCK Phase Locked Loop (PLL) blocks on MachXO2-640U, MachXO2-1200/U and larger devices. These blocks are located at the ends of the on-chip Flash block. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

MachXO2 devices provide commonly used hardened functions such as SPI controller, I<sup>2</sup>C controller and timer/counter. MachXO2-640/U and higher density devices also provide User Flash Memory (UFM). These hardened functions and the UFM interface to the core logic and routing through a WISHBONE interface. The UFM can also be accessed through the SPI, I<sup>2</sup>C and JTAG ports.

Every device in the family has a JTAG port that supports programming and configuration of the device as well as access to the user logic. The MachXO2 devices are available for operation from 3.3 V, 2.5 V and 1.2 V power supplies, providing easy integration into the overall system.

#### **PFU Blocks**

The core of the MachXO2 device consists of PFU blocks, which can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. Each PFU block consists of four interconnected slices numbered 0 to 3 as shown in Figure 2-3. Each slice contains two LUTs and two registers. There are 53 inputs and 25 outputs associated with each PFU block.

## Programmable I/O Cells (PIC)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the MachXO2 devices, the PIO cells are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the MachXO2 devices, two adjacent PIOs can be combined to provide a complementary output driver pair.

The MachXO2-640U, MachXO2-1200/U and higher density devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. Half of the PIO pairs on the top edge of these devices can be configured as true LVDS transmit pairs. The PIO pairs on the bottom edge of these higher density devices have on-chip differential termination and also provide PCI support.

### **Hot Socketing**

The MachXO2 devices have been carefully designed to ensure predictable behavior during power-up and power-down. Leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of the system. These capabilities make the MachXO2 ideal for many multiple power supply and hot-swap applications.

## **On-chip Oscillator**

Every MachXO2 device has an internal CMOS oscillator. The oscillator output can be routed as a clock to the clock tree or as a reference clock to the sysCLOCK PLL using general routing resources. The oscillator frequency can be divided by internal logic. There is a dedicated programming bit and a user input to enable/disable the oscillator. The oscillator frequency ranges from 2.08 MHz to 133 MHz. The software default value of the Master Clock (MCLK) is nominally 2.08 MHz. When a different MCLK is selected during the design process, the following sequence takes place:

- 1. Device powers up with a nominal MCLK frequency of 2.08 MHz.

- During configuration, users select a different master clock frequency.

- The MCLK frequency changes to the selected frequency once the clock configuration bits are received.

- 4. If the user does not select a master clock frequency, then the configuration bitstream defaults to the MCLK frequency of 2.08 MHz.

Table 2-14 lists all the available MCLK frequencies.

Table 2-14. Available MCLK Frequencies

| MCLK (MHz, Nominal) | MCLK (MHz, Nominal) | MCLK (MHz, Nominal) |

|---------------------|---------------------|---------------------|

| 2.08 (default)      | 9.17                | 33.25               |

| 2.46                | 10.23               | 38                  |

| 3.17                | 13.3                | 44.33               |

| 4.29                | 14.78               | 53.2                |

| 5.54                | 20.46               | 66.5                |

| 7                   | 26.6                | 88.67               |

| 8.31                | 29.56               | 133                 |

## **Embedded Hardened IP Functions and User Flash Memory**

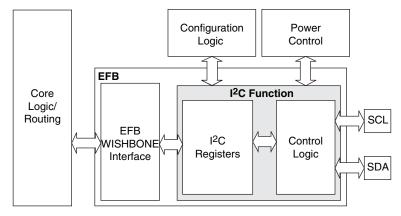

All MachXO2 devices provide embedded hardened functions such as SPI, I<sup>2</sup>C and Timer/Counter. MachXO2-640/U and higher density devices also provide User Flash Memory (UFM). These embedded blocks interface through the WISHBONE interface with routing as shown in Figure 2-20.

Figure 2-21. PC Core Block Diagram

Table 2-15 describes the signals interfacing with the I<sup>2</sup>C cores.

Table 2-15. I'C Core Signal Description

| Signal Name | I/O            | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i2c_scl     | Bi-directional | Bi-directional clock line of the I <sup>2</sup> C core. The signal is an output if the I <sup>2</sup> C core is in master mode. The signal is an input if the I <sup>2</sup> C core is in slave mode. MUST be routed directly to the pre-assigned I/O of the chip. Refer to the Pinout Information section of this document for detailed pad and pin locations of I <sup>2</sup> C ports in each MachXO2 device.                |

| i2c_sda     | Bi-directional | Bi-directional data line of the I <sup>2</sup> C core. The signal is an output when data is transmitted from the I <sup>2</sup> C core. The signal is an input when data is received into the I <sup>2</sup> C core. MUST be routed directly to the pre-assigned I/O of the chip. Refer to the Pinout Information section of this document for detailed pad and pin locations of I <sup>2</sup> C ports in each MachXO2 device. |

| i2c_irqo    | Output         | Interrupt request output signal of the I <sup>2</sup> C core. The intended usage of this signal is for it to be connected to the WISHBONE master controller (i.e. a microcontroller or state machine) and request an interrupt when a specific condition is met. These conditions are described with the I <sup>2</sup> C register definitions.                                                                                 |

| cfg_wake    | Output         | Wake-up signal – To be connected only to the power module of the MachXO2 device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, I <sup>2</sup> C Tab.                                                                                                                                                                                                                               |

| cfg_stdby   | Output         | Stand-by signal – To be connected only to the power module of the MachXO2 device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, I <sup>2</sup> C Tab.                                                                                                                                                                                                                              |

### **Hardened SPI IP Core**

Every MachXO2 device has a hard SPI IP core that can be configured as a SPI master or slave. When the IP core is configured as a master it will be able to control other SPI enabled chips connected to the SPI bus. When the core is configured as the slave, the device will be able to interface to an external SPI master. The SPI IP core on MachXO2 devices supports the following functions:

- · Configurable Master and Slave modes

- · Full-Duplex data transfer

- Mode fault error flag with CPU interrupt capability

- · Double-buffered data register

- · Serial clock with programmable polarity and phase

- · LSB First or MSB First Data Transfer

- Interface to custom logic through 8-bit WISHBONE interface

When implementing background programming of the on-chip Flash, care must be taken for the operation of the PLL. For devices that have two PLLs (XO2-2000U, -4000 and -7000), the system must put the RPLL (Right-side PLL) in reset state during the background Flash programming. More detailed description can be found in TN1204, MachXO2 Programming and Configuration Usage Guide.

#### **Security and One-Time Programmable Mode (OTP)**

For applications where security is important, the lack of an external bitstream provides a solution that is inherently more secure than SRAM-based FPGAs. This is further enhanced by device locking. MachXO2 devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile Flash memory spaces. The device can be in one of two modes:

- Unlocked Readback of the SRAM configuration and non-volatile Flash memory spaces is allowed.

- 2. Permanently Locked The device is permanently locked.

Once set, the only way to clear the security bits is to erase the device. To further complement the security of the device, a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the Flash and SRAM OTP portions of the device. For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.

#### **Dual Boot**

MachXO2 devices can optionally boot from two patterns, a primary bitstream and a golden bitstream. If the primary bitstream is found to be corrupt while being downloaded into the SRAM, the device shall then automatically re-boot from the golden bitstream. Note that the primary bitstream must reside in the on-chip Flash. The golden image MUST reside in an external SPI Flash. For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.

#### **Soft Error Detection**

The SED feature is a CRC check of the SRAM cells after the device is configured. This check ensures that the SRAM cells were configured successfully. This feature is enabled by a configuration bit option. The Soft Error Detection can also be initiated in user mode via an input to the fabric. The clock for the Soft Error Detection circuit is generated using a dedicated divider. The undivided clock from the on-chip oscillator is the input to this divider. For low power applications users can switch off the Soft Error Detection circuit. For more details, refer to TN1206, MachXO2 Soft Error Detection Usage Guide.

#### **TraceID**

Each MachXO2 device contains a unique (per device), TraceID that can be used for tracking purposes or for IP security applications. The TraceID is 64 bits long. Eight out of 64 bits are user-programmable, the remaining 56 bits are factory-programmed. The TraceID is accessible through the EFB WISHBONE interface and can also be accessed through the SPI, I<sup>2</sup>C, or JTAG interfaces.

## **Density Shifting**

The MachXO2 family has been designed to enable density migration within the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case. When migrating from lower to higher density or higher to lower density, ensure to review all the power supplies and NC pins of the chosen devices. For more details refer to the MachXO2 migration files.

## Programming and Erase Flash Supply Current – ZE Devices<sup>1, 2, 3, 4</sup>

| Symbol            | Parameter                      | Device        | Typ.⁵ | Units |

|-------------------|--------------------------------|---------------|-------|-------|

|                   |                                | LCMXO2-256ZE  | 13    | mA    |

| Icc               |                                | LCMXO2-640ZE  | 14    | mA    |

|                   | Core Power Supply              | LCMXO2-1200ZE | 15    | mA    |

|                   | Core i ower Supply             | LCMXO2-2000ZE | 17    | mA    |

|                   |                                | LCMXO2-4000ZE | 18    | mA    |

|                   |                                | LCMXO2-7000ZE | 20    | mA    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>6</sup> | All devices   | 0     | mA    |

- 1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

- 2. Assumes all inputs are held at  $\ensuremath{V_{\text{CCIO}}}$  or GND and all outputs are tri-stated.

- 3. Typical user pattern.

- 4. JTAG programming is at 25 MHz.

- 5. TJ = 25 °C, power supplies at nominal voltage.

- 6. Per bank.  $V_{CCIO} = 2.5 \text{ V}$ . Does not include pull-up/pull-down.

## sysIO Single-Ended DC Electrical Characteristics<sup>1, 2</sup>

| Input/Output    | V <sub>IL</sub>       |                          | V <sub>IH</sub>          |          | V <sub>OL</sub> Max. | V <sub>OH</sub> Min.     | V <sub>OH</sub> Min. I <sub>OL</sub> Max. <sup>4</sup> I <sub>O</sub> |                               |    |

|-----------------|-----------------------|--------------------------|--------------------------|----------|----------------------|--------------------------|-----------------------------------------------------------------------|-------------------------------|----|

| Standard        | Min. (V) <sup>3</sup> | Max. (V)                 | Min. (V)                 | Max. (V) | (V)                  | (V)                      | (mA)                                                                  | I <sub>OH</sub> Max.⁴<br>(mA) |    |

|                 |                       |                          |                          |          |                      |                          | 4                                                                     | -4                            |    |

|                 | -0.3                  |                          |                          |          |                      |                          | 8                                                                     | -8                            |    |

| LVCMOS 3.3      |                       | 0.8                      | 2.0                      | 3.6      | 0.4                  | V <sub>CCIO</sub> – 0.4  | 12                                                                    | -12                           |    |

| LVTTL           | -0.5                  | 0.6                      | 2.0                      | 3.0      |                      |                          | 16                                                                    | -16                           |    |

|                 |                       |                          |                          |          |                      |                          | 24                                                                    | -24                           |    |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                                                                   | -0.1                          |    |

|                 |                       |                          |                          |          |                      |                          | 4                                                                     | -4                            |    |

|                 |                       |                          |                          |          | 0.4                  | V <sub>CCIO</sub> – 0.4  | 8                                                                     | -8                            |    |

| LVCMOS 2.5      | -0.3                  | 0.7                      | 1.7                      | 3.6      | 0.4                  | VCCIO - 0.4              | 12                                                                    | -12                           |    |

|                 |                       |                          |                          |          |                      |                          | 16                                                                    | -16                           |    |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                                                                   | -0.1                          |    |

|                 |                       |                          |                          |          |                      |                          | 4                                                                     | -4                            |    |

| LVCMOS 1.8      | -0.3                  | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4  | 8                                                                     | -8                            |    |

| LVCIVIOS 1.0    | -0.5                  | 0.33 V CCIO              | 0.03 V CCIO              | 5.0      |                      |                          | 12                                                                    | -12                           |    |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                                                                   | -0.1                          |    |

|                 |                       |                          | 0.65V <sub>CCIO</sub>    |          | 0.4                  | 0.4                      | V <sub>CCIO</sub> - 0.4                                               | 4                             | -4 |

| LVCMOS 1.5      | -0.3                  | 0.35V <sub>CCIO</sub>    |                          | 3.6      | 0.4                  | VCCIO - 0.4              | 8                                                                     | -8                            |    |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> - 0.2  | 0.1                                                                   | -0.1                          |    |

|                 |                       |                          |                          |          | 0.4                  | V <sub>CCIO</sub> - 0.4  | 4                                                                     | -2                            |    |

| LVCMOS 1.2      | -0.3                  | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | 4 CCIO 0:4               | 8                                                                     | -6                            |    |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> – 0.2  | 0.1                                                                   | -0.1                          |    |

| PCI             | -0.3                  | 0.3V <sub>CCIO</sub>     | 0.5V <sub>CCIO</sub>     | 3.6      | 0.1V <sub>CCIO</sub> | 0.9V <sub>CCIO</sub>     | 1.5                                                                   | -0.5                          |    |

| SSTL25 Class I  | -0.3                  | V <sub>REF</sub> – 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.54                 | V <sub>CCIO</sub> - 0.62 | 8                                                                     | 8                             |    |

| SSTL25 Class II | -0.3                  | V <sub>REF</sub> – 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | NA                   | NA                       | NA                                                                    | NA                            |    |

| SSTL18 Class I  | -0.3                  | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | 0.40                 | V <sub>CCIO</sub> - 0.40 | 8                                                                     | 8                             |    |

| SSTL18 Class II | -0.3                  | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | NA                   | NA                       | NA                                                                    | NA                            |    |

| HSTL18 Class I  | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.40                 | V <sub>CCIO</sub> - 0.40 | 8                                                                     | 8                             |    |

| HSTL18 Class II | -0.3                  | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                                                                    | NA                            |    |

| LVCMOS25R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                                                                    | NA                            |    |

| LVCMOS18R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                                                                    | NA                            |    |

| LVCMOS18R25     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                                                                    | NA                            |    |

| LVCMOS15R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                                                                    | NA                            |    |

| LVCMOS15R25     | -0.3                  | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                                                                    | NA                            |    |

| LVCMOS12R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.40                 | NA Open<br>Drain         | 24, 16, 12,<br>8, 4                                                   | NA Open<br>Drain              |    |

| LVCMOS12R25     | -0.3                  | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.40                 | NA Open<br>Drain         | 16, 12, 8, 4                                                          | NA Open<br>Drain              |    |

| LVCMOS10R33     | -0.3                  | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.40                 | NA Open<br>Drain         | 24, 16, 12,<br>8, 4                                                   | NA Open<br>Drain              |    |

| Input/Output | V <sub>IL</sub>       |                        | V <sub>IH</sub>        |          | V <sub>OL</sub> Max. | V <sub>OH</sub> Min. | I <sub>OL</sub> Max. <sup>4</sup> | I <sub>OH</sub> Max.⁴ |  |

|--------------|-----------------------|------------------------|------------------------|----------|----------------------|----------------------|-----------------------------------|-----------------------|--|

| Standard     | Min. (V) <sup>3</sup> | Max. (V)               | Min. (V)               | Max. (V) | (V)                  | (V)                  | (mA)                              | (mA)                  |  |

| LVCMOS10R25  | -0.3                  | V <sub>REF</sub> - 0.1 | V <sub>REF</sub> + 0.1 | 3.6      | 0.40                 | NA Open<br>Drain     | 16, 12, 8, 4                      | NA Open<br>Drain      |  |

- MachXO2 devices allow LVCMOS inputs to be placed in I/O banks where V<sub>CCIO</sub> is different from what is specified in the applicable JEDEC specification. This is referred to as a ratioed input buffer. In a majority of cases this operation follows or exceeds the applicable JEDEC specification. The cases where MachXO2 devices do not meet the relevant JEDEC specification are documented in the table below.

- MachXO2 devices allow for LVCMOS referenced I/Os which follow applicable JEDEC specifications. For more details about mixed mode operation please refer to please refer to TN1202, MachXO2 sysIO Usage Guide.

- 3. The dual function  $I^2C$  pins SCL and SDA are limited to a  $V_{IL}$  min of -0.25 V or to -0.3 V with a duration of <10 ns.

- 4. For electromigration, the average DC current sourced or sinked by I/O pads between two consecutive VCCIO or GND pad connections, or between the last VCCIO or GND in an I/O bank and the end of an I/O bank, as shown in the Logic Signal Connections table (also shown as I/O grouping) shall not exceed a maximum of n \* 8 mA. "n" is the number of I/O pads between the two consecutive bank VCCIO or GND connections or between the last VCCIO and GND in a bank and the end of a bank. IO Grouping can be found in the Data Sheet Pin Tables, which can also be generated from the Lattice Diamond software.

| Input Standard | V <sub>CCIO</sub> (V) | V <sub>IL</sub> Max. (V) |

|----------------|-----------------------|--------------------------|

| LVCMOS 33      | 1.5                   | 0.685                    |

| LVCMOS 25      | 1.5                   | 0.687                    |

| LVCMOS 18      | 1.5                   | 0.655                    |

## sysIO Differential Electrical Characteristics

The LVDS differential output buffers are available on the top side of MachXO2-640U, MachXO2-1200/U and higher density devices in the MachXO2 PLD family.

#### **LVDS**

#### **Over Recommended Operating Conditions**

| Parameter<br>Symbol               | Parameter Description                                      | Test Conditions                                 | Min.  | Тур.  | Max.  | Units |

|-----------------------------------|------------------------------------------------------------|-------------------------------------------------|-------|-------|-------|-------|

| V <sub>INP</sub> V <sub>INM</sub> | Input Voltage                                              | V <sub>CCIO</sub> = 3.3 V                       | 0     | _     | 2.605 | V     |

| VINP VINM                         | Imput voltage                                              | V <sub>CCIO</sub> = 2.5 V                       | 0     | _     | 2.05  | V     |

| $V_{THD}$                         | Differential Input Threshold                               |                                                 | ±100  | _     |       | mV    |

| V                                 | Input Common Mode Voltage                                  | V <sub>CCIO</sub> = 3.3 V                       | 0.05  | _     | 2.6   | V     |

| V <sub>CM</sub>                   | Imput Common wode voltage                                  | V <sub>CCIO</sub> = 2.5 V                       | 0.05  | _     | 2.0   | V     |

| I <sub>IN</sub>                   | Input current                                              | Power on                                        | _     | _     | ±10   | μΑ    |

| V <sub>OH</sub>                   | Output high voltage for V <sub>OP</sub> or V <sub>OM</sub> | R <sub>T</sub> = 100 Ohm                        | _     | 1.375 |       | V     |

| V <sub>OL</sub>                   | Output low voltage for V <sub>OP</sub> or V <sub>OM</sub>  | R <sub>T</sub> = 100 Ohm                        | 0.90  | 1.025 | _     | V     |

| V <sub>OD</sub>                   | Output voltage differential                                | $(V_{OP} - V_{OM}), R_T = 100 Ohm$              | 250   | 350   | 450   | mV    |

| $\Delta V_{OD}$                   | Change in V <sub>OD</sub> between high and low             |                                                 | _     | _     | 50    | mV    |

| V <sub>OS</sub>                   | Output voltage offset                                      | $(V_{OP} + V_{OM})/2$ , $R_T = 100 \text{ Ohm}$ | 1.125 | 1.20  | 1.395 | V     |

| ΔV <sub>OS</sub>                  | Change in V <sub>OS</sub> between H and L                  |                                                 | _     | _     | 50    | mV    |

| I <sub>OSD</sub>                  | Output short circuit current                               | V <sub>OD</sub> = 0 V driver outputs shorted    | _     |       | 24    | mA    |

#### **BLVDS**

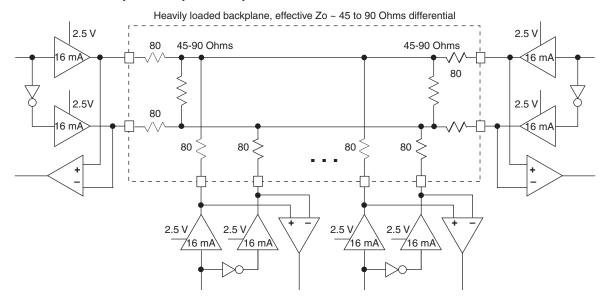

The MachXO2 family supports the BLVDS standard through emulation. The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs. The input standard is supported by the LVDS differential input buffer. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

Figure 3-2. BLVDS Multi-point Output Example

Table 3-2. BLVDS DC Conditions<sup>1</sup>

#### **Over Recommended Operating Conditions**

|                     |                             | Non     | ninal   |       |

|---------------------|-----------------------------|---------|---------|-------|

| Symbol              | Description                 | Zo = 45 | Zo = 90 | Units |

| Z <sub>OUT</sub>    | Output impedance            | 20      | 20      | Ohms  |

| R <sub>S</sub>      | Driver series resistance    | 80      | 80      | Ohms  |

| R <sub>TLEFT</sub>  | Left end termination        | 45      | 90      | Ohms  |

| R <sub>TRIGHT</sub> | Right end termination       | 45      | 90      | Ohms  |

| V <sub>OH</sub>     | Output high voltage         | 1.376   | 1.480   | V     |

| V <sub>OL</sub>     | Output low voltage          | 1.124   | 1.020   | V     |

| V <sub>OD</sub>     | Output differential voltage | 0.253   | 0.459   | V     |

| V <sub>CM</sub>     | Output common mode voltage  | 1.250   | 1.250   | V     |

| I <sub>DC</sub>     | DC output current           | 11.236  | 10.204  | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

# Typical Building Block Function Performance – HC/HE Devices<sup>1</sup> Pin-to-Pin Performance (LVCMOS25 12 mA Drive)

| Function        | -6 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions | ·         |       |

| 16-bit decoder  | 8.9       | ns    |

| 4:1 MUX         | 7.5       | ns    |

| 16:1 MUX        | 8.3       | ns    |

### **Register-to-Register Performance**

| Function                                                                     | -6 Timing | Units |

|------------------------------------------------------------------------------|-----------|-------|

| Basic Functions                                                              |           | •     |

| 16:1 MUX                                                                     | 412       | MHz   |

| 16-bit adder                                                                 | 297       | MHz   |

| 16-bit counter                                                               | 324       | MHz   |

| 64-bit counter                                                               | 161       | MHz   |

| Embedded Memory Functions                                                    |           | •     |

| 1024x9 True-Dual Port RAM<br>(Write Through or Normal, EBR output registers) | 183       | MHz   |

| Distributed Memory Functions                                                 |           |       |

| 16x4 Pseudo-Dual Port RAM (one PFU)                                          | 500       | MHz   |

<sup>1.</sup> The above timing numbers are generated using the Diamond design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions, including industrial, can be extracted from the Diamond software.

|                        |                                         |                                                                         | _     | -3    | _     | 2     | _     | -1    |       |

|------------------------|-----------------------------------------|-------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Parameter              | Description                             | Device                                                                  | Min.  | Max.  | Min.  | Max.  | Min.  | Max.  | Units |

| LPDDR <sup>9, 12</sup> |                                         | l                                                                       | 1     |       |       |       |       |       | ı     |

| t <sub>DVADQ</sub>     | Input Data Valid After DQS<br>Input     |                                                                         | _     | 0.349 | _     | 0.381 | _     | 0.396 | UI    |

| t <sub>DVEDQ</sub>     | Input Data Hold After DQS<br>Input      |                                                                         | 0.665 | _     | 0.630 | _     | 0.613 | _     | UI    |

| t <sub>DQVBS</sub>     | Output Data Invalid Before DQS Output   | MachXO2-1200/U                                                          | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| t <sub>DQVAS</sub>     | Output Data Invalid After DQS<br>Output | and larger devices,<br>right side only. <sup>13</sup>                   | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| f <sub>DATA</sub>      | MEM LPDDR Serial Data<br>Speed          |                                                                         |       | 120   | _     | 110   | _     | 96    | Mbps  |

| f <sub>SCLK</sub>      | SCLK Frequency                          |                                                                         | _     | 60    |       | 55    |       | 48    | MHz   |

| f <sub>LPDDR</sub>     | LPDDR Data Transfer Rate                |                                                                         | 0     | 120   | 0     | 110   | 0     | 96    | Mbps  |

| DDR <sup>9, 12</sup>   | •                                       |                                                                         | •     |       |       | •     |       | •     |       |

| t <sub>DVADQ</sub>     | Input Data Valid After DQS<br>Input     |                                                                         | _     | 0.347 | _     | 0.374 | _     | 0.393 | UI    |

| t <sub>DVEDQ</sub>     | Input Data Hold After DQS<br>Input      |                                                                         | 0.665 | _     | 0.637 | _     | 0.616 | _     | UI    |

| t <sub>DQVBS</sub>     | Output Data Invalid Before DQS Output   | MachXO2-1200/U<br>and larger devices,                                   | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| t <sub>DQVAS</sub>     | Output Data Invalid After DQS<br>Output | right side only. <sup>13</sup>                                          | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| f <sub>DATA</sub>      | MEM DDR Serial Data Speed               |                                                                         | _     | 140   | _     | 116   | _     | 98    | Mbps  |

| f <sub>SCLK</sub>      | SCLK Frequency                          |                                                                         | _     | 70    | _     | 58    | _     | 49    | MHz   |

| f <sub>MEM_DDR</sub>   | MEM DDR Data Transfer Rate              |                                                                         | N/A   | 140   | N/A   | 116   | N/A   | 98    | Mbps  |

| DDR2 <sup>9, 12</sup>  | 1                                       |                                                                         | 1     |       |       | 1     |       |       |       |

| t <sub>DVADQ</sub>     | Input Data Valid After DQS<br>Input     |                                                                         | _     | 0.372 | _     | 0.394 | _     | 0.410 | UI    |

| t <sub>DVEDQ</sub>     | Input Data Hold After DQS<br>Input      |                                                                         | 0.690 | _     | 0.658 | _     | 0.618 | _     | UI    |

| t <sub>DQVBS</sub>     | Output Data Invalid Before DQS Output   | MachXO2-1200/U<br>and larger devices,<br>right side only. <sup>13</sup> | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| t <sub>DQVAS</sub>     | Output Data Invalid After DQS<br>Output |                                                                         | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| f <sub>DATA</sub>      | MEM DDR Serial Data Speed               |                                                                         | _     | 140   | _     | 116   | _     | 98    | Mbps  |

| f <sub>SCLK</sub>      | SCLK Frequency                          | 1                                                                       | _     | 70    | _     | 58    | _     | 49    | MHz   |

| f <sub>MEM_DDR2</sub>  | MEM DDR2 Data Transfer<br>Rate          |                                                                         | N/A   | 140   | N/A   | 116   | N/A   | 98    | Mbps  |

- 1. Exact performance may vary with device and design implementation. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions, including industrial, can be extracted from the Diamond software.

- 2. General I/O timing numbers based on LVCMOS 2.5, 8 mA, 0 pf load, fast slew rate.

- 3. Generic DDR timing numbers based on LVDS I/O (for input, output, and clock ports).

- 4. DDR timing numbers based on SSTL25. DDR2 timing numbers based on SSTL18. LPDDR timing numbers based in LVCMOS18.

- 5. 7:1 LVDS (GDDR71) uses the LVDS I/O standard (for input, output, and clock ports).

- 6. For Generic DDRX1 mode  $t_{SU} = t_{HO} = (t_{DVE} t_{DVA} 0.03 \text{ ns})/2$ .

- 7. The  $t_{SU\_DEL}$  and  $t_{H\_DEL}$  values use the SCLK\_ZERHOLD default step size. Each step is 167 ps (-3), 182 ps (-2), 195 ps (-1).

- 8. This number for general purpose usage. Duty cycle tolerance is +/-10%.

- 9. Duty cycle is +/- 5% for system usage.

- 10. The above timing numbers are generated using the Diamond design tool. Exact performance may vary with the device selected.

- 11. High-speed DDR and LVDS not supported in SG32 (32-Pin QFN) packages.

- 12. Advance information for MachXO2 devices in 48 QFN packages.

- 13. DDR memory interface not supported in QN84 (84 QFN) and SG32 (32 QFN) packages.

## **MachXO2 Oscillator Output Frequency**

| Symbol                 | Parameter                                                                | Min.    | Тур.  | Max     | Units |

|------------------------|--------------------------------------------------------------------------|---------|-------|---------|-------|

| f                      | Oscillator Output Frequency (Commercial Grade Devices, 0 to 85°C)        |         | 133   | 140.315 | MHz   |

| † <sub>MAX</sub>       | Oscillator Output Frequency (Industrial Grade Devices, –40 °C to 100 °C) | 124.355 | 133   | 141.645 | MHz   |

| t <sub>DT</sub>        | Output Clock Duty Cycle                                                  | 43      | 50    | 57      | %     |

| t <sub>OPJIT</sub> 1   | Output Clock Period Jitter                                               | 0.01    | 0.012 | 0.02    | UIPP  |

| t <sub>STABLEOSC</sub> | STDBY Low to Oscillator Stable                                           | 0.01    | 0.05  | 0.1     | μs    |

<sup>1.</sup> Output Clock Period Jitter specified at 133 MHz. The values for lower frequencies will be smaller UIPP. The typical value for 133 MHz is 95 ps and for 2.08 MHz the typical value is 1.54 ns.

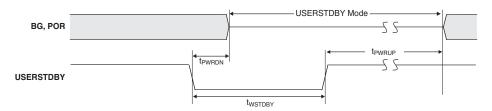

## **MachXO2 Standby Mode Timing – HC/HE Devices**

| Symbol             | Parameter                 | Device       | Min. | Тур. | Max | Units |

|--------------------|---------------------------|--------------|------|------|-----|-------|

| t <sub>PWRDN</sub> | USERSTDBY High to Stop    | All          | _    | _    | 9   | ns    |

|                    |                           | LCMXO2-256   |      | _    |     | μs    |

|                    |                           | LCMXO2-640   |      | _    |     | μs    |

|                    |                           | LCMXO2-640U  |      | _    |     | μs    |

|                    |                           | LCMXO2-1200  | 20   | _    | 50  | μs    |

| t <sub>PWRUP</sub> | USERSTDBY Low to Power Up | LCMXO2-1200U |      | _    |     | μs    |

|                    |                           | LCMXO2-2000  |      | _    |     | μs    |

|                    |                           | LCMXO2-2000U |      | _    |     | μs    |

|                    |                           | LCMXO2-4000  |      | _    |     | μs    |

|                    |                           | LCMXO2-7000  |      | _    |     | μs    |

| twstdby            | USERSTDBY Pulse Width     | All          | 18   | _    | _   | ns    |

## **MachXO2 Standby Mode Timing – ZE Devices**

| Symbol                  | Parameter                        | Device      | Min. | Тур. | Max | Units |

|-------------------------|----------------------------------|-------------|------|------|-----|-------|

| t <sub>PWRDN</sub>      | USERSTDBY High to Stop           | All         | _    | _    | 13  | ns    |

|                         |                                  | LCMXO2-256  |      | _    |     | μs    |

|                         | USERSTDBY Low to Power Up        | LCMXO2-640  |      | _    |     | μs    |

|                         |                                  | LCMXO2-1200 | 20   | _    | 50  | μs    |

| <sup>T</sup> PWRUP      |                                  | LCMXO2-2000 |      | _    |     | μs    |

|                         |                                  | LCMXO2-4000 |      | _    |     | μs    |

|                         |                                  | LCMXO2-7000 |      | _    |     | μs    |

| t <sub>WSTDBY</sub>     | USERSTDBY Pulse Width            | All         | 19   | _    | _   | ns    |

| t <sub>BNDGAPSTBL</sub> | USERSTDBY High to Bandgap Stable | All         | _    | _    | 15  | ns    |

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-2000UHC-4FG484C | 2112 | 2.5 V / 3.3 V  | -4         | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHC-5FG484C | 2112 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHC-6FG484C | 2112 | 2.5 V / 3.3 V  | -6         | Halogen-Free fpBGA | 484   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade          | Package            | Leads | Temp. |

|------------------------|------|----------------|----------------|--------------------|-------|-------|

| LCMXO2-4000HC-4QN84C   | 4320 | 2.5 V / 3.3 V  | -4             | Halogen-Free QFN   | 84    | СОМ   |

| LCMXO2-4000HC-5QN84C   | 4320 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free QFN   | 84    | COM   |

| LCMXO2-4000HC-6QN84C   | 4320 | 2.5 V / 3.3 V  | -6             | Halogen-Free QFN   | 84    | COM   |

| LCMXO2-4000HC-4MG132C  | 4320 | 2.5 V / 3.3 V  | -4             | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HC-5MG132C  | 4320 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HC-6MG132C  | 4320 | 2.5 V / 3.3 V  | -6             | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HC-4TG144C  | 4320 | 2.5 V / 3.3 V  | -4             | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HC-5TG144C  | 4320 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HC-6TG144C  | 4320 | 2.5 V / 3.3 V  | -6             | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HC-4BG256C  | 4320 | 2.5 V / 3.3 V  | -4             | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HC-5BG256C  | 4320 | 2.5 V / 3.3 V  | <del>-</del> 5 | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HC-6BG256C  | 4320 | 2.5 V / 3.3 V  | -6             | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HC-4FTG256C | 4320 | 2.5 V / 3.3 V  | -4             | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HC-5FTG256C | 4320 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HC-6FTG256C | 4320 | 2.5 V / 3.3 V  | -6             | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HC-4BG332C  | 4320 | 2.5 V / 3.3 V  | -4             | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HC-5BG332C  | 4320 | 2.5 V / 3.3 V  | <del>-</del> 5 | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HC-6BG332C  | 4320 | 2.5 V / 3.3 V  | -6             | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HC-4FG484C  | 4320 | 2.5 V / 3.3 V  | -4             | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-4000HC-5FG484C  | 4320 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-4000HC-6FG484C  | 4320 | 2.5 V / 3.3 V  | -6             | Halogen-Free fpBGA | 484   | COM   |

# High-Performance Commercial Grade Devices without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100C  | 2112 | 1.2 V          | -4         | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-5TG100C  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-6TG100C  | 2112 | 1.2 V          | -6         | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-4TG144C  | 2112 | 1.2 V          | -4         | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-5TG144C  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-6TG144C  | 2112 | 1.2 V          | -6         | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-4MG132C  | 2112 | 1.2 V          | -4         | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-5MG132C  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-6MG132C  | 2112 | 1.2 V          | -6         | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-4BG256C  | 2112 | 1.2 V          | -4         | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-5BG256C  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-6BG256C  | 2112 | 1.2 V          | -6         | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-4FTG256C | 2112 | 1.2 V          | -4         | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-5FTG256C | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-6FTG256C | 2112 | 1.2 V          | -6         | Halogen-Free ftBGA | 256   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484C | 2112 | 1.2 V          | -4         | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-5FG484C | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-6FG484C | 2112 | 1.2 V          | -6         | Halogen-Free fpBGA | 484   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade          | Package            | Leads | Temp. |

|------------------------|------|----------------|----------------|--------------------|-------|-------|

| LCMXO2-4000HE-4TG144C  | 4320 | 1.2 V          | -4             | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-5TG144C  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-6TG144C  | 4320 | 1.2 V          | -6             | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-4MG132C  | 4320 | 1.2 V          | -4             | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-5MG132C  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-6MG132C  | 4320 | 1.2 V          | -6             | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-4BG256C  | 4320 | 1.2 V          | -4             | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4MG184C  | 4320 | 1.2 V          | -4             | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5MG184C  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-6MG184C  | 4320 | 1.2 V          | -6             | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5BG256C  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-6BG256C  | 4320 | 1.2 V          | -6             | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4FTG256C | 4320 | 1.2 V          | -4             | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-5FTG256C | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-6FTG256C | 4320 | 1.2 V          | -6             | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-4BG332C  | 4320 | 1.2 V          | -4             | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HE-5BG332C  | 4320 | 1.2 V          | <del>-</del> 5 | Halogen-Free caBGA | 332   | COM   |

# Ordering Information MachXO2 Family Data Sheet

| Part Number           | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|-----------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-4000HE-6BG332C | 4320 | 1.2 V          | -6         | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HE-4FG484C | 4320 | 1.2 V          | -4         | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-4000HE-5FG484C | 4320 | 1.2 V          | <b>-</b> 5 | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-4000HE-6FG484C | 4320 | 1.2 V          | -6         | Halogen-Free fpBGA | 484   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-7000HE-4TG144C  | 6864 | 1.2 V          | -4         | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HE-5TG144C  | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HE-6TG144C  | 6864 | 1.2 V          | -6         | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HE-4BG256C  | 6864 | 1.2 V          | -4         | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HE-5BG256C  | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HE-6BG256C  | 6864 | 1.2 V          | -6         | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HE-4FTG256C | 6864 | 1.2 V          | -4         | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HE-5FTG256C | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HE-6FTG256C | 6864 | 1.2 V          | -6         | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HE-4BG332C  | 6864 | 1.2 V          | -4         | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HE-5BG332C  | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HE-6BG332C  | 6864 | 1.2 V          | -6         | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HE-4FG484C  | 6864 | 1.2 V          | -4         | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HE-5FG484C  | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HE-6FG484C  | 6864 | 1.2 V          | -6         | Halogen-Free fpBGA | 484   | COM   |

## Ordering Information MachXO2 Family Data Sheet

| Part Number                            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000ZE-1UWG49ITR <sup>1</sup>   | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1UWG49ITR50 <sup>3</sup> | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1UWG49ITR1K <sup>2</sup> | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1TG100I                  | 2112 | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-2TG100I                  | 2112 | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-3TG100I                  | 2112 | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-1MG132I                  | 2112 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-2MG132I                  | 2112 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-3MG132I                  | 2112 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-1TG144I                  | 2112 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-2TG144I                  | 2112 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-3TG144I                  | 2112 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-1BG256I                  | 2112 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-2BG256I                  | 2112 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-3BG256I                  | 2112 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-1FTG256I                 | 2112 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000ZE-2FTG256I                 | 2112 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000ZE-3FTG256I                 | 2112 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | IND   |

<sup>1.</sup> This part number has a tape and reel quantity of 5,000 units with a minimum order quantity of 10,000 units. Order quantities must be in increments of 5,000 units. For example, a 10,000 unit order will be shipped in two reels with one reel containing 5,000 units and the other reel with less than 5,000 units (depending on test yields). Unserviced backlog will be canceled.

<sup>2.</sup> This part number has a tape and reel quantity of 1,000 units with a minimum order quantity of 1,000. Order quantities must be in increments of 1,000 units. For example, a 5,000 unit order will be shipped as 5 reels of 1000 units each.

<sup>3.</sup> This part number has a tape and reel quantity of 50 units with a minimum order quantity of 50. Order quantities must be in increments of 50 units. For example, a 1,000 unit order will be shipped as 20 reels of 50 units each.

| Part Number           | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|-----------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-1200HC-4SG32I  | 1280 | 2.5 V / 3.3 V  | -4         | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-5SG32I  | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-6SG32I  | 1280 | 2.5 V / 3.3 V  | -6         | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-4TG100I | 1280 | 2.5 V / 3.3 V  | -4         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-5TG100I | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-6TG100I | 1280 | 2.5 V / 3.3 V  | -6         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-4MG132I | 1280 | 2.5 V / 3.3 V  | -4         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-5MG132I | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-6MG132I | 1280 | 2.5 V / 3.3 V  | -6         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-4TG144I | 1280 | 2.5 V / 3.3 V  | -4         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-5TG144I | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-6TG144I | 1280 | 2.5 V/ 3.3 V   | -6         | Halogen-Free TQFP  | 144   | IND   |

| Part Number             | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|-------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-1200UHC-4FTG256I | 1280 | 2.5 V / 3.3 V  | -4         | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-1200UHC-5FTG256I | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-1200UHC-6FTG256I | 1280 | 2.5 V / 3.3 V  | -6         | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-2000HC-4TG100I  | 2112 | 2.5 V / 3.3 V  | -4         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-5TG100I  | 2112 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-6TG100I  | 2112 | 2.5 V / 3.3 V  | -6         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-4MG132I  | 2112 | 2.5 V / 3.3 V  | -4         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-5MG132I  | 2112 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-6MG132I  | 2112 | 2.5 V / 3.3 V  | -6         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-4TG144I  | 2112 | 2.5 V / 3.3 V  | -4         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-5TG144I  | 2112 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-6TG144I  | 2112 | 2.5 V / 3.3 V  | -6         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-4BG256I  | 2112 | 2.5 V / 3.3 V  | -4         | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-5BG256I  | 2112 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-6BG256I  | 2112 | 2.5 V / 3.3 V  | -6         | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-4FTG256I | 2112 | 2.5 V / 3.3 V  | -4         | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HC-5FTG256I | 2112 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HC-6FTG256I | 2112 | 2.5 V / 3.3 V  | -6         | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade          | Package            | Leads | Temp. |

|------------------------|------|----------------|----------------|--------------------|-------|-------|

| LCMXO2-2000UHC-4FG484I | 2112 | 2.5 V / 3.3 V  | -4             | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHC-5FG484I | 2112 | 2.5 V / 3.3 V  | <del>-</del> 5 | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHC-6FG484I | 2112 | 2.5 V / 3.3 V  | -6             | Halogen-Free fpBGA | 484   | IND   |

# High Performance Industrial Grade Devices Without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100I  | 2112 | 1.2 V          | -4         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-5TG100I  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-6TG100I  | 2112 | 1.2 V          | -6         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-4MG132I  | 2112 | 1.2 V          | -4         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-5MG132I  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-6MG132I  | 2112 | 1.2 V          | -6         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-4TG144I  | 2112 | 1.2 V          | -4         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-5TG144I  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-6TG144I  | 2112 | 1.2 V          | -6         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-4BG256I  | 2112 | 1.2 V          | -4         | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-5BG256I  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-6BG256I  | 2112 | 1.2 V          | -6         | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-4FTG256I | 2112 | 1.2 V          | -4         | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HE-5FTG256I | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HE-6FTG256I | 2112 | 1.2 V          | -6         | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484I | 2112 | 1.2 V          | -4         | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHE-5FG484I | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHE-6FG484I | 2112 | 1.2 V          | -6         | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade          | Package            | Leads | Temp. |

|------------------------|------|----------------|----------------|--------------------|-------|-------|

| LCMXO2-4000HE-4MG132I  | 4320 | 1.2 V          | -4             | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-5MG132I  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-6MG132I  | 4320 | 1.2 V          | -6             | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-4TG144I  | 4320 | 1.2 V          | -4             | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-5TG144I  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-6TG144I  | 4320 | 1.2 V          | -6             | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-4MG184I  | 4320 | 1.2 V          | -4             | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-5MG184I  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-6MG184I  | 4320 | 1.2 V          | -6             | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-4BG256I  | 4320 | 1.2 V          | -4             | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-5BG256I  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-6BG256I  | 4320 | 1.2 V          | -6             | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-4FTG256I | 4320 | 1.2 V          | -4             | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-5FTG256I | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-6FTG256I | 4320 | 1.2 V          | -6             | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-4BG332I  | 4320 | 1.2 V          | -4             | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-5BG332I  | 4320 | 1.2 V          | <b>-</b> 5     | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-6BG332I  | 4320 | 1.2 V          | -6             | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-4FG484I  | 4320 | 1.2 V          | -4             | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000HE-5FG484I  | 4320 | 1.2 V          | <del>-</del> 5 | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000HE-6FG484I  | 4320 | 1.2 V          | -6             | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-7000HE-4TG144I  | 6864 | 1.2 V          | -4         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-5TG144I  | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-6TG144I  | 6864 | 1.2 V          | -6         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-4BG256I  | 6864 | 1.2 V          | -4         | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-5BG256I  | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-6BG256I  | 6864 | 1.2 V          | -6         | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-4FTG256I | 6864 | 1.2 V          | -4         | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-5FTG256I | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-6FTG256I | 6864 | 1.2 V          | -6         | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-4BG332I  | 6864 | 1.2 V          | -4         | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-5BG332I  | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-6BG332I  | 6864 | 1.2 V          | -6         | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-4FG484I  | 6864 | 1.2 V          | -4         | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000HE-5FG484I  | 6864 | 1.2 V          | <b>-</b> 5 | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000HE-6FG484I  | 6864 | 1.2 V          | -6         | Halogen-Free fpBGA | 484   | IND   |