## E · K Hat lice Semiconductor Corporation - <u>LCMXO2-2000HC-5TG144I Datasheet</u>

Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| 2 0 000                        |                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------|

| Product Status                 | Active                                                                           |

| Number of LABs/CLBs            | 264                                                                              |

| Number of Logic Elements/Cells | 2112                                                                             |

| Total RAM Bits                 | 75776                                                                            |

| Number of I/O                  | 111                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 2.375V ~ 3.465V                                                                  |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                               |

| Package / Case                 | 144-LQFP                                                                         |

| Supplier Device Package        | 144-TQFP (20x20)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-2000hc-5tg144i |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Introduction

The MachXO2 family of ultra low power, instant-on, non-volatile PLDs has six devices with densities ranging from 256 to 6864 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, User Flash Memory (UFM), Phase Locked Loops (PLLs), preengineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and timer/counter. These features allow these devices to be used in low cost, high volume consumer and system applications.

The MachXO2 devices are designed on a 65 nm non-volatile low power process. The device architecture has several features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs and oscillators dynamically. These features help manage static and dynamic power consumption resulting in low static power for all members of the family.

The MachXO2 devices are available in two versions – ultra low power (ZE) and high performance (HC and HE) devices. The ultra low power devices are offered in three speed grades –1, –2 and –3, with –3 being the fastest. Similarly, the high-performance devices are offered in three speed grades: –4, –5 and –6, with –6 being the fastest. HC devices have an internal linear voltage regulator which supports external V<sub>CC</sub> supply voltages of 3.3 V or 2.5 V. ZE and HE devices only accept 1.2 V as the external V<sub>CC</sub> supply voltage. With the exception of power supply voltage all three types of devices (ZE, HC and HE) are functionally compatible and pin compatible with each other.

The MachXO2 PLDs are available in a broad range of advanced halogen-free packages ranging from the space saving 2.5 mm x 2.5 mm WLCSP to the 23 mm x 23 mm fpBGA. MachXO2 devices support density migration within the same package. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters.

The pre-engineered source synchronous logic implemented in the MachXO2 device family supports a broad range of interface standards, including LPDDR, DDR, DDR2 and 7:1 gearing for display I/Os.

The MachXO2 devices offer enhanced I/O features such as drive strength control, slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a "per-pin" basis.

A user-programmable internal oscillator is included in MachXO2 devices. The clock output from this oscillator may be divided by the timer/counter for use as clock input in functions such as LED control, key-board scanner and similar state machines.

The MachXO2 devices also provide flexible, reliable and secure configuration from on-chip Flash memory. These devices can also configure themselves from external SPI Flash or be configured by an external master through the JTAG test access port or through the I<sup>2</sup>C port. Additionally, MachXO2 devices support dual-boot capability (using external Flash memory) and remote field upgrade (TransFR) capability.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the MachXO2 family of devices. Popular logic synthesis tools provide synthesis library support for MachXO2. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the MachXO2 device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) LatticeCORE<sup>™</sup> modules, including a number of reference designs licensed free of charge, optimized for the MachXO2 PLD family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increasing their productivity.

### **ROM Mode**

ROM mode uses the LUT logic; hence, slices 0-3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information on the RAM and ROM modes, please refer to TN1201, Memory Usage Guide for MachXO2 Devices.

## Routing

There are many resources provided in the MachXO2 devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with three different types of routing resources: x1 (spans two PFUs), x2 (spans three PFUs) and x6 (spans seven PFUs). The x1, x2, and x6 connections provide fast and efficient connections in the horizontal and vertical directions.

The design tools take the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock/Control Distribution Network**

Each MachXO2 device has eight clock inputs (PCLK [T, C] [Banknum]\_[2..0]) – three pins on the left side, two pins each on the bottom and top sides and one pin on the right side. These clock inputs drive the clock nets. These eight inputs can be differential or single-ended and may be used as general purpose I/O if they are not used to drive the clock nets. When using a single ended clock input, only the PCLKT input can drive the clock tree directly.

The MachXO2 architecture has three types of clocking resources: edge clocks, primary clocks and secondary high fanout nets. MachXO2-640U, MachXO2-1200/U and higher density devices have two edge clocks each on the top and bottom edges. Lower density devices have no edge clocks. Edge clocks are used to clock I/O registers and have low injection time and skew. Edge clock inputs are from PLL outputs, primary clock pads, edge clock bridge outputs and CIB sources.

The eight primary clock lines in the primary clock network drive throughout the entire device and can provide clocks for all resources within the device including PFUs, EBRs and PICs. In addition to the primary clock signals, MachXO2 devices also have eight secondary high fanout signals which can be used for global control signals, such as clock enables, synchronous or asynchronous clears, presets, output enables, etc. Internal logic can drive the global clock network for internally-generated global clocks and control signals.

The maximum frequency for the primary clock network is shown in the MachXO2 External Switching Characteristics table.

The primary clock signals for the MachXO2-256 and MachXO2-640 are generated from eight 17:1 muxes The available clock sources include eight I/O sources and 9 routing inputs. Primary clock signals for the MachXO2-640U, MachXO2-1200/U and larger devices are generated from eight 27:1 muxes The available clock sources include eight I/O sources, 11 routing inputs, eight clock divider inputs and up to eight sysCLOCK PLL outputs.

Table 2-5. sysMEM Block Configurations

| Memory Mode      | Configurations                                               |

|------------------|--------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

### Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. EBR initialization data can be loaded from the UFM. To maximize the number of UFM bits, initialize the EBRs used in your design to an all-zero pattern. Initializing to an all-zero pattern does not use up UFM bits. MachXO2 devices have been designed such that multiple EBRs share the same initialization memory space if they are initialized to the same pattern.

By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

### Memory Cascading

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

### Single, Dual, Pseudo-Dual Port and FIFO Modes

Figure 2-8 shows the five basic memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and addresses for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the memory array output.

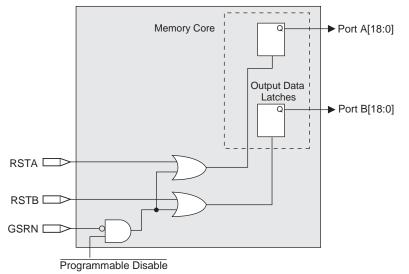

### Figure 2-9. Memory Core Reset

For further information on the sysMEM EBR block, please refer to TN1201, Memory Usage Guide for MachXO2 Devices.

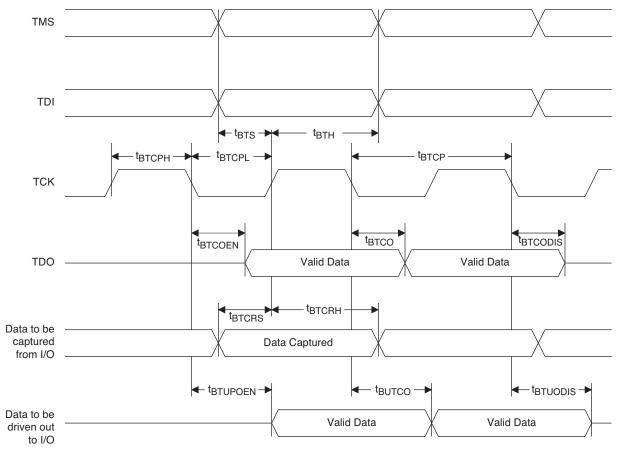

### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-10. The GSR input to the EBR is always asynchronous.

### Figure 2-10. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device wake up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-10. The reset timing rules apply to the RPReset input versus the RE input and the RST input versus the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs. For more details refer to TN1201, Memory Usage Guide for MachXO2 Devices.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

For more details on these embedded functions, please refer to TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices.

## **User Flash Memory (UFM)**

MachXO2-640/U and higher density devices provide a User Flash Memory block, which can be used for a variety of applications including storing a portion of the configuration image, initializing EBRs, to store PROM data or, as a general purpose user Flash memory. The UFM block connects to the device core through the embedded function block WISHBONE interface. Users can also access the UFM block through the JTAG, I<sup>2</sup>C and SPI interfaces of the device. The UFM block offers the following features:

- Non-volatile storage up to 256 kbits

- 100K write cycles

- Write access is performed page-wise; each page has 128 bits (16 bytes)

- Auto-increment addressing

- WISHBONE interface

For more information on the UFM, please refer to TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices.

## **Standby Mode and Power Saving Options**

MachXO2 devices are available in three options for maximum flexibility: ZE, HC and HE devices. The ZE devices have ultra low static and dynamic power consumption. These devices use a 1.2 V core voltage that further reduces power consumption. The HC and HE devices are designed to provide high performance. The HC devices have a built-in voltage regulator to allow for 2.5 V V<sub>CC</sub> and 3.3 V V<sub>CC</sub> while the HE devices operate at 1.2 V V<sub>CC</sub>.

MachXO2 devices have been designed with features that allow users to meet the static and dynamic power requirements of their applications by controlling various device subsystems such as the bandgap, power-on-reset circuitry, I/O bank controllers, power guard, on-chip oscillator, PLLs, etc. In order to maximize power savings, MachXO2 devices support an ultra low power Stand-by mode. While most of these features are available in all three device types, these features are mainly intended for use with MachXO2 ZE devices to manage power consumption.

In the stand-by mode the MachXO2 devices are powered on and configured. Internal logic, I/Os and memories are switched on and remain operational, as the user logic waits for an external input. The device enters this mode when the standby input of the standby controller is toggled or when an appropriate I<sup>2</sup>C or JTAG instruction is issued by an external master. Various subsystems in the device such as the band gap, power-on-reset circuitry etc can be configured such that they are automatically turned "off" or go into a low power consumption state to save power when the device enters this state. Note that the MachXO2 devices are powered on when in standby mode and all power supplies should remain in the Recommended Operating Conditions.

# MachXO2 Family Data Sheet DC and Switching Characteristics

### March 2017

### Data Sheet DS1035

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                               | MachXO2 ZE/HE (1.2 V) | MachXO2 HC (2.5 V / 3.3 V) |

|-----------------------------------------------|-----------------------|----------------------------|

| Supply Voltage V <sub>CC</sub>                | –0.5 V to 1.32 V      | –0.5 V to 3.75 V           |

| Output Supply Voltage V <sub>CCIO</sub>       | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| I/O Tri-state Voltage Applied <sup>4, 5</sup> | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| Dedicated Input Voltage Applied <sup>4</sup>  | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| Storage Temperature (Ambient)                 | –55 °C to 125 °C      | –55 °C to 125 °C           |

| Junction Temperature (T <sub>J</sub> )        | –40 °C to 125 °C      | –40 °C to 125 °C           |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

5. The dual function  $I^2C$  pins SCL and SDA are limited to -0.25 V to 3.75 V or to -0.3 V with a duration of <20 ns.

## **Recommended Operating Conditions**<sup>1</sup>

| Symbol                               | nbol Parameter                                |       | Max. | Units |

|--------------------------------------|-----------------------------------------------|-------|------|-------|

| V <sub>CC</sub> <sup>1</sup>         | Core Supply Voltage for 1.2 V Devices         | 1.14  | 1.26 | V     |

| VCC                                  | Core Supply Voltage for 2.5 V / 3.3 V Devices | 2.375 | 3.6  | V     |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup> | I/O Driver Supply Voltage                     | 1.14  | 3.6  | V     |

| t <sub>JCOM</sub>                    | Junction Temperature Commercial Operation     | 0     | 85   | °C    |

| t <sub>JIND</sub>                    | Junction Temperature Industrial Operation     | -40   | 100  | °C    |

1. Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both the same voltage, they must also be the same supply.

2. See recommended voltages by I/O standard in subsequent table.

3. V<sub>CCIO</sub> pins of unused I/O banks should be connected to the V<sub>CC</sub> power supply on boards.

## **Power Supply Ramp Rates**<sup>1</sup>

| Symbol            | Parameter                                       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------------------|------|------|------|-------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies. | 0.01 |      | 100  | V/ms  |

1. Assumes monotonic ramp rates.

<sup>© 2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Typical Building Block Function Performance – HC/HE Devices<sup>1</sup>

## Pin-to-Pin Performance (LVCMOS25 12 mA Drive)

| Function        | -6 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions |           |       |

| 16-bit decoder  | 8.9       | ns    |

| 4:1 MUX         | 7.5       | ns    |

| 16:1 MUX        | 8.3       | ns    |

## **Register-to-Register Performance**

| Function                                                                     | -6 Timing | Units |

|------------------------------------------------------------------------------|-----------|-------|

| Basic Functions                                                              |           |       |

| 16:1 MUX                                                                     | 412       | MHz   |

| 16-bit adder                                                                 | 297       | MHz   |

| 16-bit counter                                                               | 324       | MHz   |

| 64-bit counter                                                               | 161       | MHz   |

| Embedded Memory Functions                                                    |           |       |

| 1024x9 True-Dual Port RAM<br>(Write Through or Normal, EBR output registers) | 183       | MHz   |

| Distributed Memory Functions                                                 |           |       |

| 16x4 Pseudo-Dual Port RAM (one PFU)                                          | 500       | MHz   |

The above timing numbers are generated using the Diamond design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions, including industrial, can be extracted from the Diamond software.

## Typical Building Block Function Performance – ZE Devices<sup>1</sup>

## Pin-to-Pin Performance (LVCMOS25 12 mA Drive)

| Function        | –3 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions |           |       |

| 16-bit decoder  | 13.9      | ns    |

| 4:1 MUX         | 10.9      | ns    |

| 16:1 MUX        | 12.0      | ns    |

### **Register-to-Register Performance**

| –3 Timing | Units                         |

|-----------|-------------------------------|

|           |                               |

| 191       | MHz                           |

| 134       | MHz                           |

| 148       | MHz                           |

| 77        | MHz                           |

|           |                               |

| 90        | MHz                           |

|           |                               |

| 214       | MHz                           |

|           | 191<br>134<br>148<br>77<br>90 |

1. The above timing numbers are generated using the Diamond design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

## **Derating Logic Timing**

Logic timing provided in the following sections of the data sheet and the Lattice design tools are worst case numbers in the operating range. Actual delays may be much faster. Lattice design tools can provide logic timing numbers at a particular temperature and voltage.

## sysCLOCK PLL Timing (Continued)

### **Over Recommended Operating Conditions**

| Parameter              | Descriptions          | Conditions | Min. | Max. | Units      |

|------------------------|-----------------------|------------|------|------|------------|

| t <sub>ROTATE_WD</sub> | PHASESTEP Pulse Width |            | 4    | _    | VCO Cycles |

1. Period jitter sample is taken over 10,000 samples of the primary PLL output with a clean reference clock. Cycle-to-cycle jitter is taken over 1000 cycles. Phase jitter is taken over 2000 cycles. All values per JESD65B.

2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

3. Using LVDS output buffers.

4. CLKOS as compared to CLKOP output for one phase step at the maximum VCO frequency. See TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide for more details.

5. At minimum  $f_{PFD}$  As the  $f_{PFD}$  increases the time will decrease to approximately 60% the value listed.

6. Maximum allowed jitter on an input clock. PLL unlock may occur if the input jitter exceeds this specification. Jitter on the input clock may be transferred to the output clocks, resulting in jitter measurements outside the output specifications listed in this table.

7. Edge Duty Trim Accuracy is a percentage of the setting value. Settings available are 70 ps, 140 ps, and 280 ps in addition to the default value of none.

8. Jitter values measured with the internal oscillator operating. The jitter values will increase with loading of the PLD fabric and in the presence of SSO noise.

|                                                            | MachXO2-1200 |           |          |          | MachXO2-1200U       |           |

|------------------------------------------------------------|--------------|-----------|----------|----------|---------------------|-----------|

|                                                            | 100 TQFP     | 132 csBGA | 144 TQFP | 25 WLCSP | 32 QFN <sup>1</sup> | 256 ftBGA |

| General Purpose I/O per Bank                               |              |           |          |          |                     | ·         |

| Bank 0                                                     | 18           | 25        | 27       | 11       | 9                   | 50        |

| Bank 1                                                     | 21           | 26        | 26       | 0        | 2                   | 52        |

| Bank 2                                                     | 20           | 28        | 28       | 7        | 9                   | 52        |

| Bank 3                                                     | 20           | 25        | 26       | 0        | 2                   | 16        |

| Bank 4                                                     | 0            | 0         | 0        | 0        | 0                   | 16        |

| Bank 5                                                     | 0            | 0         | 0        | 0        | 0                   | 20        |

| Total General Purpose Single Ended I/O                     | 79           | 104       | 107      | 18       | 22                  | 206       |

| Differential I/O per Bank                                  |              |           |          |          |                     |           |

| Bank 0                                                     | 9            | 13        | 14       | 5        | 4                   | 25        |

| Bank 1                                                     | 10           | 13        | 13       | 0        | 1                   | 26        |

| Bank 2                                                     | 10           | 14        | 14       | 2        | 4                   | 26        |

| Bank 3                                                     | 10           | 12        | 13       | 0        | 1                   | 8         |

| Bank 4                                                     | 0            | 0         | 0        | 0        | 0                   | 8         |

| Bank 5                                                     | 0            | 0         | 0        | 0        | 0                   | 10        |

| Total General Purpose Differential I/O                     | 39           | 52        | 54       | 7        | 10                  | 103       |

| Dual Function I/O                                          | 31           | 33        | 33       | 18       | 22                  | 33        |

| High-speed Differential I/O                                | _            |           |          | _        |                     |           |

| Bank 0                                                     | 4            | 7         | 7        | 0        | 0                   | 14        |

| Gearboxes                                                  |              |           |          |          |                     |           |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0)  | 4            | 7         | 7        | 0        | 0                   | 14        |

| Number of 7:1 or 8:1 Input Gearbox Avail-<br>able (Bank 2) | 5            | 7         | 7        | 0        | 2                   | 14        |

| DQS Groups                                                 |              |           |          |          |                     | ·         |

| Bank 1                                                     | 1            | 2         | 2        | 0        | 0                   | 2         |

| VCCIO Pins                                                 |              |           |          |          |                     |           |

| Bank 0                                                     | 2            | 3         | 3        | 1        | 2                   | 4         |

| Bank 1                                                     | 2            | 3         | 3        | 0        | 1                   | 4         |

| Bank 2                                                     | 2            | 3         | 3        | 1        | 2                   | 4         |

| Bank 3                                                     | 3            | 3         | 3        | 0        | 1                   | 1         |

| Bank 4                                                     | 0            | 0         | 0        | 0        | 0                   | 2         |

| Bank 5                                                     | 0            | 0         | 0        | 0        | 0                   | 1         |

| VCC                                                        | 2            | 4         | 4        | 2        | 2                   | 8         |

| GND                                                        | 8            | 10        | 12       | 2        | 2                   | 24        |

| NC                                                         | 1            | 1         | 8        | 0        | 0                   | 1         |

| Reserved for Configuration                                 | 1            | 1         | 1        | 1        | 1                   | 1         |

| Total Count of Bonded Pins                                 | 100          | 132       | 144      | 25       | 32                  | 256       |

| 1. Lattice recommends soldering the centra                 |              |           |          |          |                     |           |

1. Lattice recommends soldering the central thermal pad onto the top PCB ground for improved thermal resistance.

|                                                           |           |              |             | MachX        | <b>D2-4000</b> |              |              |              |

|-----------------------------------------------------------|-----------|--------------|-------------|--------------|----------------|--------------|--------------|--------------|

|                                                           | 84<br>QFN | 132<br>csBGA | 144<br>TQFP | 184<br>csBGA | 256<br>caBGA   | 256<br>ftBGA | 332<br>caBGA | 484<br>fpBGA |

| General Purpose I/O per Bank                              |           |              |             |              |                |              |              |              |

| Bank 0                                                    | 27        | 25           | 27          | 37           | 50             | 50           | 68           | 70           |

| Bank 1                                                    | 10        | 26           | 29          | 37           | 52             | 52           | 68           | 68           |

| Bank 2                                                    | 22        | 28           | 29          | 39           | 52             | 52           | 70           | 72           |

| Bank 3                                                    | 0         | 7            | 9           | 10           | 16             | 16           | 24           | 24           |

| Bank 4                                                    | 9         | 8            | 10          | 12           | 16             | 16           | 16           | 16           |

| Bank 5                                                    | 0         | 10           | 10          | 15           | 20             | 20           | 28           | 28           |

| Total General Purpose Single Ended I/O                    | 68        | 104          | 114         | 150          | 206            | 206          | 274          | 278          |

| Differential I/O per Bank                                 |           |              |             |              |                |              |              |              |

| Bank 0                                                    | 13        | 13           | 14          | 18           | 25             | 25           | 34           | 35           |

| Bank 1                                                    | 4         | 13           | 14          | 18           | 26             | 26           | 34           | 34           |

| Bank 2                                                    | 11        | 14           | 14          | 19           | 26             | 26           | 35           | 36           |

| Bank 3                                                    | 0         | 3            | 4           | 4            | 8              | 8            | 12           | 12           |

| Bank 4                                                    | 4         | 4            | 5           | 6            | 8              | 8            | 8            | 8            |

| Bank 5                                                    | 0         | 5            | 5           | 7            | 10             | 10           | 14           | 14           |

| Total General Purpose Differential I/O                    | 32        | 52           | 56          | 72           | 103            | 103          | 137          | 139          |

| Dual Function I/O                                         | 28        | 37           | 37          | 37           | 37             | 37           | 37           | 37           |

| High-speed Differential I/O                               |           |              |             | •            |                |              |              |              |

| Bank 0                                                    | 8         | 8            | 9           | 8            | 18             | 18           | 18           | 18           |

| Gearboxes                                                 |           |              |             | •            |                |              |              |              |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 8         | 8            | 9           | 9            | 18             | 18           | 18           | 18           |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 11        | 14           | 14          | 12           | 18             | 18           | 18           | 18           |

| DQS Groups                                                | 1         | 1            |             |              |                |              |              |              |

| Bank 1                                                    | 1         | 2            | 2           | 2            | 2              | 2            | 2            | 2            |

| VCCIO Pins                                                |           |              |             |              |                |              |              |              |

| Bank 0                                                    | 3         | 3            | 3           | 3            | 4              | 4            | 4            | 10           |

| Bank 1                                                    | 1         | 3            | 3           | 3            | 4              | 4            | 4            | 10           |

| Bank 2                                                    | 2         | 3            | 3           | 3            | 4              | 4            | 4            | 10           |

| Bank 3                                                    | 1         | 1            | 1           | 1            | 1              | 1            | 2            | 3            |

| Bank 4                                                    | 1         | 1            | 1           | 1            | 2              | 2            | 1            | 4            |

| Bank 5                                                    | 1         | 1            | 1           | 1            | 1              | 1            | 2            | 3            |

| VCC                                                       | 4         | 4            | 4           | 4            | 8              | 8            | 8            | 12           |

| GND                                                       | 4         | 10           | 12          | 16           | 24             | 24           | 27           | 48           |

| NC                                                        | 1         | 1            | 1           | 1            | 1              | 1            | 5            | 105          |

| Reserved for configuration                                | 1         | 1            | 1           | 1            | 1              | 1            | 1            | 1            |

| liebel ved for bernigaration                              |           |              |             |              |                |              |              |              |

\_

|                                                           | MachXO2-7000 |           |           |           |           |           |  |  |  |  |

|-----------------------------------------------------------|--------------|-----------|-----------|-----------|-----------|-----------|--|--|--|--|

|                                                           | 144 TQFP     | 256 caBGA | 256 ftBGA | 332 caBGA | 400 caBGA | 484 fpBGA |  |  |  |  |

| General Purpose I/O per Bank                              |              | 1         | 1         |           |           | 1         |  |  |  |  |

| Bank 0                                                    | 27           | 50        | 50        | 68        | 83        | 82        |  |  |  |  |

| Bank 1                                                    | 29           | 52        | 52        | 70        | 84        | 84        |  |  |  |  |

| Bank 2                                                    | 29           | 52        | 52        | 70        | 84        | 84        |  |  |  |  |

| Bank 3                                                    | 9            | 16        | 16        | 24        | 28        | 28        |  |  |  |  |

| Bank 4                                                    | 10           | 16        | 16        | 16        | 24        | 24        |  |  |  |  |

| Bank 5                                                    | 10           | 20        | 20        | 30        | 32        | 32        |  |  |  |  |

| Total General Purpose Single Ended I/O                    | 114          | 206       | 206       | 278       | 335       | 334       |  |  |  |  |

| Differential I/O per Bank                                 |              |           |           |           |           |           |  |  |  |  |

| Bank 0                                                    | 14           | 25        | 25        | 34        | 42        | 41        |  |  |  |  |

| Bank 1                                                    | 14           | 26        | 26        | 35        | 42        | 42        |  |  |  |  |

| Bank 2                                                    | 14           | 26        | 26        | 35        | 42        | 42        |  |  |  |  |

| Bank 3                                                    | 4            | 8         | 8         | 12        | 14        | 14        |  |  |  |  |

| Bank 4                                                    | 5            | 8         | 8         | 8         | 12        | 12        |  |  |  |  |

| Bank 5                                                    | 5            | 10        | 10        | 15        | 16        | 16        |  |  |  |  |

| Total General Purpose Differential I/O                    | 56           | 103       | 103       | 139       | 168       | 167       |  |  |  |  |

| Dual Function I/O                                         | 37           | 37        | 37        | 37        | 37        | 37        |  |  |  |  |

| High-speed Differential I/O                               |              | -         | -         | -         | -         | -         |  |  |  |  |

| Bank 0                                                    | 9            | 20        | 20        | 21        | 21        | 21        |  |  |  |  |

| Gearboxes                                                 |              |           |           |           |           |           |  |  |  |  |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 9            | 20        | 20        | 21        | 21        | 21        |  |  |  |  |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 14           | 20        | 20        | 21        | 21        | 21        |  |  |  |  |

| DQS Groups                                                |              |           |           |           | •         | •         |  |  |  |  |

| Bank 1                                                    | 2            | 2         | 2         | 2         | 2         | 2         |  |  |  |  |

| VCCIO Pins                                                |              |           |           |           |           |           |  |  |  |  |

| Bank 0                                                    | 3            | 4         | 4         | 4         | 5         | 10        |  |  |  |  |

| Bank 1                                                    | 3            | 4         | 4         | 4         | 5         | 10        |  |  |  |  |

| Bank 2                                                    | 3            | 4         | 4         | 4         | 5         | 10        |  |  |  |  |

| Bank 3                                                    | 1            | 1         | 1         | 2         | 2         | 3         |  |  |  |  |

| Bank 4                                                    | 1            | 2         | 2         | 1         | 2         | 4         |  |  |  |  |

| Bank 5                                                    | 1            | 1         | 1         | 2         | 2         | 3         |  |  |  |  |

| 200                                                       |              |           |           |           |           | 4.0       |  |  |  |  |

| VCC                                                       | 4            | 8         | 8         | 8         | 10        | 12        |  |  |  |  |

| GND                                                       | 12           | 24        | 24        | 27        | 33        | 48        |  |  |  |  |

| NC                                                        | 1            | 1         | 1         | 1         | 0         | 49        |  |  |  |  |

| Reserved for Configuration                                | 1            | 1         | 1         | 1         | 1         | 1         |  |  |  |  |

| Total Count of Bonded Pins                                | 144          | 256       | 256       | 332       | 400       | 484       |  |  |  |  |

| Part Number           | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|-----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200HC-4SG32C  | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-1200HC-5SG32C  | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-1200HC-6SG32C  | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-1200HC-4TG100C | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-5TG100C | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-6TG100C | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-4MG132C | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-5MG132C | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-6MG132C | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-4TG144C | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200HC-5TG144C | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200HC-6TG144C | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | COM   |

| Part Number             | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|-------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200UHC-4FTG256C | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-1200UHC-5FTG256C | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-1200UHC-6FTG256C | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HC-4TG100C  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HC-5TG100C  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HC-6TG100C  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HC-4MG132C  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HC-5MG132C  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HC-6MG132C  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HC-4TG144C  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HC-5TG144C  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HC-6TG144C  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HC-4BG256C  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HC-5BG256C  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HC-6BG256C  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HC-4FTG256C | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HC-5FTG256C | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HC-6FTG256C | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | COM   |

| Part Number                            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000ZE-1UWG49ITR1               | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1UWG49ITR50 <sup>3</sup> | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1UWG49ITR1K <sup>2</sup> | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1TG100I                  | 2112 | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-2TG100I                  | 2112 | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-3TG100I                  | 2112 | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-1MG132I                  | 2112 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-2MG132I                  | 2112 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-3MG132I                  | 2112 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-1TG144I                  | 2112 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-2TG144I                  | 2112 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-3TG144I                  | 2112 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-1BG256I                  | 2112 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-2BG256I                  | 2112 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-3BG256I                  | 2112 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-1FTG256I                 | 2112 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000ZE-2FTG256I                 | 2112 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000ZE-3FTG256I                 | 2112 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | IND   |

1. This part number has a tape and reel quantity of 5,000 units with a minimum order quantity of 10,000 units. Order quantities must be in increments of 5,000 units. For example, a 10,000 unit order will be shipped in two reels with one reel containing 5,000 units and the other reel with less than 5,000 units (depending on test yields). Unserviced backlog will be canceled.

2. This part number has a tape and reel quantity of 1,000 units with a minimum order quantity of 1,000. Order quantities must be in increments of 1,000 units. For example, a 5,000 unit order will be shipped as 5 reels of 1000 units each.

3. This part number has a tape and reel quantity of 50 units with a minimum order quantity of 50. Order quantities must be in increments of 50 units. For example, a 1,000 unit order will be shipped as 20 reels of 50 units each.

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000ZE-1QN84I   | 4320 | 1.2 V          | -1    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000ZE-2QN84I   | 4320 | 1.2 V          | -2    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000ZE-3QN84I   | 4320 | 1.2 V          | -3    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000ZE-1MG132I  | 4320 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000ZE-2MG132I  | 4320 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000ZE-3MG132I  | 4320 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000ZE-1TG144I  | 4320 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000ZE-2TG144I  | 4320 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000ZE-3TG144I  | 4320 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000ZE-1BG256I  | 4320 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000ZE-2BG256I  | 4320 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000ZE-3BG256I  | 4320 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000ZE-1FTG256I | 4320 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000ZE-2FTG256I | 4320 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000ZE-3FTG256I | 4320 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000ZE-1BG332I  | 4320 | 1.2 V          | -1    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000ZE-2BG332I  | 4320 | 1.2 V          | -2    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000ZE-3BG332I  | 4320 | 1.2 V          | -3    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000ZE-1FG484I  | 4320 | 1.2 V          | -1    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000ZE-2FG484I  | 4320 | 1.2 V          | -2    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000ZE-3FG484I  | 4320 | 1.2 V          | -3    | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000ZE-1TG144I  | 6864 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000ZE-2TG144I  | 6864 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000ZE-3TG144I  | 6864 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000ZE-1BG256I  | 6864 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000ZE-2BG256I  | 6864 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000ZE-3BG256I  | 6864 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000ZE-1FTG256I | 6864 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000ZE-2FTG256I | 6864 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000ZE-3FTG256I | 6864 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000ZE-1BG332I  | 6864 | 1.2 V          | -1    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000ZE-2BG332I  | 6864 | 1.2 V          | -2    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000ZE-3BG332I  | 6864 | 1.2 V          | -3    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000ZE-1FG484I  | 6864 | 1.2 V          | -1    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000ZE-2FG484I  | 6864 | 1.2 V          | -2    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000ZE-3FG484I  | 6864 | 1.2 V          | -3    | Halogen-Free fpBGA | 484   | IND   |

| Part Number           | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|-----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200HC-4SG32I  | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-5SG32I  | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-6SG32I  | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-4TG100I | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-5TG100I | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-6TG100I | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-4MG132I | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-5MG132I | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-6MG132I | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-4TG144I | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-5TG144I | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-6TG144I | 1280 | 2.5 V/ 3.3 V   | -6    | Halogen-Free TQFP  | 144   | IND   |

| Part Number             | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|-------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200UHC-4FTG256I | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-1200UHC-5FTG256I | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-1200UHC-6FTG256I | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HC-4TG100I  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-5TG100I  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-6TG100I  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-4MG132I  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-5MG132I  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-6MG132I  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-4TG144I  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-5TG144I  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-6TG144I  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-4BG256I  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-5BG256I  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-6BG256I  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-4FTG256I | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HC-5FTG256I | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HC-6FTG256I | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000UHC-4FG484I | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHC-5FG484I | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHC-6FG484I | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 484   | IND   |

| Date          | Version | Section                             | Change Summary                                                                                                                                                                                                  |

|---------------|---------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2014 | 2.9     | Introduction                        | Updated the Features section. Revised Table 1-1, MachXO2 Family<br>Selection Guide.<br>— Removed XO2-4000U data.<br>— Removed 400-ball ftBGA.<br>— Removed 25-ball WLCSP value for XO2-2000U.                   |

|               |         | DC and Switching<br>Characteristics | Updated the Recommended Operating Conditions section. Adjusted Max. values for $V_{CC}$ and $V_{CCIO}$                                                                                                          |

|               |         |                                     | Updated the sysIO Recommended Operating Conditions section.<br>Adjusted Max. values for LVCMOS 3.3, LVTTL, PCI, LVDS33 and<br>LVPECL.                                                                           |

|               |         | Pinout Information                  | Updated the Pinout Information Summary section. Removed MachXO2-4000U.                                                                                                                                          |

|               |         | Ordering Information                | Updated the MachXO2 Part Number Description section. Removed BG400 package.                                                                                                                                     |

|               |         |                                     | Updated the High-Performance Commercial Grade Devices with Volt-<br>age Regulator, Halogen Free (RoHS) Packaging section. Removed<br>LCMXO2-4000UHC part numbers.                                               |

|               |         |                                     | Updated the High-Performance Industrial Grade Devices with Voltage<br>Regulator, Halogen Free (RoHS) Packaging section. Removed<br>LCMXO2-4000UHC part numbers.                                                 |

| November 2014 | 2.8     | Introduction                        | Updated the Features section.<br>— Revised I/Os under Flexible Logic Architecture.<br>— Revised standby power under Ultra Low Power Devices.<br>— Revise input frequency range under Flexible On-Chip Clocking. |

|               |         |                                     | Updated Table 1-1, MachXO2 Family Selection Guide.<br>— Added XO2-4000U data.<br>— Removed HE and ZE device options for XO2-4000.<br>— Added 400-ball ftBGA.                                                    |

|               |         | Pinout Information                  | Updated the Pinout Information Summary section. Added MachXO2-4000U caBGA400 and MachXO2-7000 caBGA400.                                                                                                         |

|               |         | Ordering Information                | Updated the MachXO2 Part Number Description section. Added BG400 package.                                                                                                                                       |

|               |         |                                     | Updated the Ordering Information section. Added MachXO2-4000U caBGA400 and MachXO2-7000 caBGA400 part numbers.                                                                                                  |

| October 2014  | 2.7     | Ordering Information                | Updated the Ultra Low Power Industrial Grade Devices, Halogen Free<br>(RoHS) Packaging section. Fixed typo in LCMXO2-2000ZE-<br>1UWG49ITR part number package.                                                  |

|               |         | Architecture                        | Updated the Supported Standards section. Added MIPI information to Table 2-12. Supported Input Standards and Table 2-13. Supported Output Standards.                                                            |

|               |         | DC and Switching<br>Characteristics | Updated the BLVDS section. Changed output impedance nominal values in Table 3-2, BLVDS DC Condition.                                                                                                            |

|               |         |                                     | Updated the LVPECL section. Changed output impedance nominal value in Table 3-3, LVPECL DC Condition.                                                                                                           |

|               |         |                                     | Updated the sysCONFIG Port Timing Specifications section.<br>Updated INITN low time values.                                                                                                                     |

| July 2014     | 2.6     | DC and Switching<br>Characteristics | Updated sysIO Single-Ended DC Electrical Characteristics <sup>1, 2</sup> section.<br>Updated footnote 4.                                                                                                        |

|               |         |                                     | Updated Register-to-Register Performance section. Updated foot-<br>note.                                                                                                                                        |

|               |         | Ordering Information                | Updated UW49 package to UWG49 in MachXO2 Part Number Description.                                                                                                                                               |

|               |         |                                     | Updated LCMXO2-2000ZE-1UWG49CTR package in Ultra Low Power Commercial Grade Devices, Halogen Free (RoHS) Packaging.                                                                                             |

| Image: space with the second secon         | Date           | Version | Section              | Change Summary                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|----------------------|----------------------------------------------------------------------------------------------------|

| Guide table.           Architecture         Added information to Standby Mode and Power Saving Options section.           Pinout Information         Added the XO2-2000 49 WLCSP in the Pinout Information Summary table.           Ordering Information         Added the XO2-2000 2E in the Pinout Information Summary table.           Ordering Information         Added the XO2-2000ZE-1UWG49CTR in Ultra Low Power Commercial Grade Devices, Halogen Free (RoHS) Packaging section.           Added and LCMXO2-2000ZE-1UWG49ITR in Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging section.         Added and LCMXO2-2000ZE-1UWG49ITR in Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging section.           December 2013         02.3         Architecture         Updated Information on CLKOS output divider in sysCLOCK Phase Locked Loops (PLLs) section.           DC and Switching         Updated footnote 4 in sysIO Single-Ended DC Electrical Characteristics table; Updated V <sub>IL</sub> Max. (V) data for LVCMOS 25 and LVCMOS 28.           Updated V <sub>OS</sub> test condition in sysIO Differential Electrical Characteristics - LVDS table.         Updated Supported Input Standards table.           DC and Switching         Updated Power-On-Reset Voltage Levels table.         Updated Supported Input Standards table.           June 2013         02.1         Architecture         Architecture Overview – Added information on the state of the register on power up and after configuration.           June 2013         02.1         Architecture         Architec                                                                                                                                                                                                                                                                                                                                                                                                                                             | May 2014       | 2.5     | Architecture         | Updated TransFR description for PLL use during background Flash                                    |

| Image: section of the sectio | February 2014  | 02.4    | Introduction         |                                                                                                    |

| Image: series of the series         |                |         | Architecture         |                                                                                                    |

| Added and LCMXO2-2000ZE-1UWG49CTR in Ultra Low Power<br>Commercial Grade Devices, Halogen Free (RoHS) Packaging section.           Added and LCMXO2-2000ZE-1UWG49ITR in Ultra Low Power<br>Industrial Grade Devices, Halogen Free (RoHS) Packaging section.           December 2013         02.3           Architecture         Updated information on CLKOS output divider in sysCLOCK Phase<br>Locked Loops (PLLs) section.           DC and Switching<br>Characteristics         Updated Static Supply Current – ZE Devices table.           Updated footnote 4 in sysIO Single-Ended DC Electrical Characteris<br>tics table; Updated V <sub>IL</sub> Max. (V) data for LVCMOS 25 and LVCMOS<br>28.           Updated Vos test condition in sysIO Differential Electrical Characteri-<br>istics - LVDS table.           September 2013         02.2           Oz and Switching<br>Characteristics         Removed I <sup>2</sup> C Clock-Stretching feature per PCN #10A-13.           Removed information on PDPR memory in RAM Mode section.         Updated Supported Input Standards table.           June 2013         02.1         Architecture         Architecture Overview – Added information on the state of the regis-<br>ter on power up and after configuration.           sysCLOCK Phase Locked Loops (PLLs) section – Added missing<br>cross reference to sysCLOC KPLL Timing table.         Added slew rate information to footnote 2 of the MachXO2 External<br>Switching Characteristics – HC/HE Devices and the MachXO2 External<br>Switching Characteristics – ZE Devices tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |         | Pinout Information   | Added the XO2-2000 49 WLCSP in the Pinout Information Summary table.                               |

| Image: bit is a series of the serie |                |         | Ordering Information | Added UW49 package in MachXO2 Part Number Description.                                             |

| Industrial Grade Devices, Halogen Free (RoHS) Packaging section.           December 2013         02.3         Architecture         Updated information on CLKOS output divider in sysCLOCK Phase<br>Locked Loops (PLLs) section.           DC and Switching<br>Characteristics         Updated Static Supply Current – ZE Devices table.         Updated footnote 4 in sysIO Single-Ended DC Electrical Characteris<br>tics table; Updated V <sub>IL</sub> Max. (V) data for LVCMOS 25 and LVCMOS<br>28.           September 2013         02.2         Architecture         Removed I <sup>2</sup> C Clock-Stretching feature per PCN #10A-13.           Removed I <sup>2</sup> C Clock-Stretching feature per PCN #10A-13.         Removed information on PDPR memory in RAM Mode section.           Updated Supported Input Standards table.         Updated Power-On-Reset Voltage Levels table.           June 2013         02.1         Architecture         Architecture Overview – Added information on the state of the register on power up and after configuration.           SysCLOCK Phase Locked Loops (PLLs) section – Added missing<br>cross reference to sysCLOCK PLL Timing table.         DC and Switching<br>Characteristics         Added slew rate information to footnote 2 of the MachXO2 External<br>Switching Characteristics – ED Povices and the MachXO2 External<br>Switching Characteristics – ZE Devices tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |         |                      | Commercial Grade Devices, Halogen Free (RoHS) Packaging sec-                                       |

| DC and Switching<br>Characteristics         Updated Static Supply Current – ZE Devices table.           Updated footnote 4 in sysIO Single-Ended DC Electrical Characteristics table; Updated footnote 4 in sysIO Single-Ended DC Electrical Characteristics table; Updated V <sub>IL</sub> Max. (V) data for LVCMOS 25 and LVCMOS 28.           September 2013         02.2         Architecture         Removed I <sup>2</sup> C Clock-Stretching feature per PCN #10A-13.           Removed information on PDPR memory in RAM Mode section.         Updated Supported Input Standards table.           June 2013         02.1         Architecture         Architecture Overview – Added information on the state of the register on power up and after configuration.           sysCLOCK Phase Locked Loops (PLLs) section – Added missing cross reference to sysCLOCK PLL Timing table.         DC and Switching Characteristics           DC and Switching Characteristics         Added slew rate information to footnote 2 of the MachXO2 External Switching Characteristics – ZE Devices tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |         |                      |                                                                                                    |