Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------|

| Product Status                 | Active                                                                           |

| Number of LABs/CLBs            | 264                                                                              |

| Number of Logic Elements/Cells | 2112                                                                             |

| Total RAM Bits                 | 75776                                                                            |

| Number of I/O                  | 111                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 2.375V ~ 3.465V                                                                  |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                               |

| Package / Case                 | 144-LQFP                                                                         |

| Supplier Device Package        | 144-TQFP (20x20)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-2000hc-6tg144i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Introduction

The MachXO2 family of ultra low power, instant-on, non-volatile PLDs has six devices with densities ranging from 256 to 6864 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, User Flash Memory (UFM), Phase Locked Loops (PLLs), preengineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and timer/counter. These features allow these devices to be used in low cost, high volume consumer and system applications.

The MachXO2 devices are designed on a 65 nm non-volatile low power process. The device architecture has several features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs and oscillators dynamically. These features help manage static and dynamic power consumption resulting in low static power for all members of the family.

The MachXO2 devices are available in two versions – ultra low power (ZE) and high performance (HC and HE) devices. The ultra low power devices are offered in three speed grades –1, –2 and –3, with –3 being the fastest. Similarly, the high-performance devices are offered in three speed grades: –4, –5 and –6, with –6 being the fastest. HC devices have an internal linear voltage regulator which supports external  $V_{CC}$  supply voltages of 3.3 V or 2.5 V. ZE and HE devices only accept 1.2 V as the external  $V_{CC}$  supply voltage. With the exception of power supply voltage all three types of devices (ZE, HC and HE) are functionally compatible and pin compatible with each other.

The MachXO2 PLDs are available in a broad range of advanced halogen-free packages ranging from the space saving 2.5 mm x 2.5 mm WLCSP to the 23 mm x 23 mm fpBGA. MachXO2 devices support density migration within the same package. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters.

The pre-engineered source synchronous logic implemented in the MachXO2 device family supports a broad range of interface standards, including LPDDR, DDR, DDR2 and 7:1 gearing for display I/Os.

The MachXO2 devices offer enhanced I/O features such as drive strength control, slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a "per-pin" basis.

A user-programmable internal oscillator is included in MachXO2 devices. The clock output from this oscillator may be divided by the timer/counter for use as clock input in functions such as LED control, key-board scanner and similar state machines.

The MachXO2 devices also provide flexible, reliable and secure configuration from on-chip Flash memory. These devices can also configure themselves from external SPI Flash or be configured by an external master through the JTAG test access port or through the I<sup>2</sup>C port. Additionally, MachXO2 devices support dual-boot capability (using external Flash memory) and remote field upgrade (TransFR) capability.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the MachXO2 family of devices. Popular logic synthesis tools provide synthesis library support for MachXO2. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the MachXO2 device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) LatticeCORE™ modules, including a number of reference designs licensed free of charge, optimized for the MachXO2 PLD family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increasing their productivity.

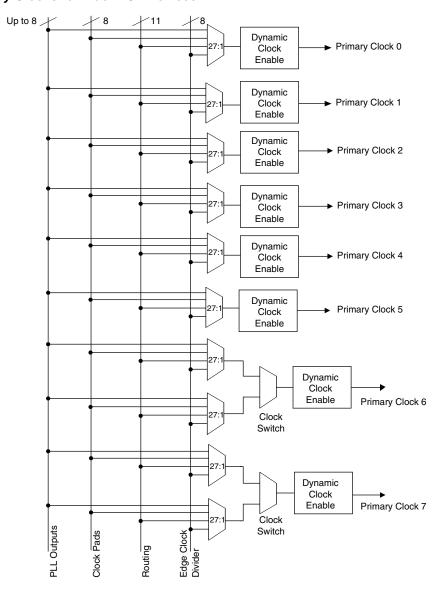

Figure 2-5. Primary Clocks for MachXO2 Devices

Primary clocks for MachXO2-640U, MachXO2-1200/U and larger devices.

Note: MachXO2-640 and smaller devices do not have inputs from the Edge Clock Divider or PLL and fewer routing inputs. These devices have 17:1 muxes instead of 27:1 muxes.

Eight secondary high fanout nets are generated from eight 8:1 muxes as shown in Figure 2-6. One of the eight inputs to the secondary high fanout net input mux comes from dual function clock pins and the remaining seven come from internal routing. The maximum frequency for the secondary clock network is shown in MachXO2 External Switching Characteristics table.

## Table 2-5. sysMEM Block Configurations

| Memory Mode      | Configurations                                               |

|------------------|--------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

#### **Bus Size Matching**

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

## **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. EBR initialization data can be loaded from the UFM. To maximize the number of UFM bits, initialize the EBRs used in your design to an all-zero pattern. Initializing to an all-zero pattern does not use up UFM bits. MachXO2 devices have been designed such that multiple EBRs share the same initialization memory space if they are initialized to the same pattern.

By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

## **Memory Cascading**

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

#### Single, Dual, Pseudo-Dual Port and FIFO Modes

Figure 2-8 shows the five basic memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and addresses for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the memory array output.

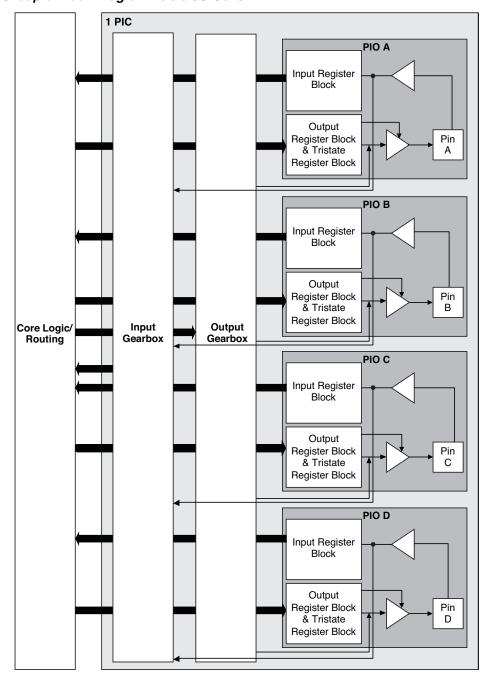

Figure 2-11. Group of Four Programmable I/O Cells

#### Notes

- 1. Input gearbox is available only in PIC on the bottom edge of MachXO2-640U, MachXO2-1200/U and larger devices.

- 2. Output gearbox is available only in PIC on the top edge of MachXO2-640U, MachXO2-1200/U and larger devices.

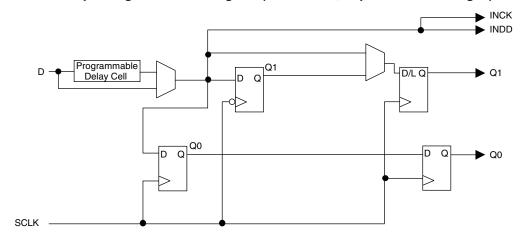

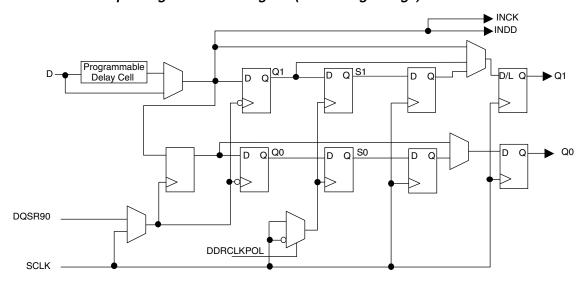

Figure 2-12. MachXO2 Input Register Block Diagram (PIO on Left, Top and Bottom Edges)

# **Right Edge**

The input register block on the right edge is a superset of the same block on the top, bottom, and left edges. In addition to the modes described above, the input register block on the right edge also supports DDR memory mode.

In DDR memory mode, two registers are used to sample the data on the positive and negative edges of the modified DQS (DQSR90) in the DDR Memory mode creating two data streams. Before entering the core, these two data streams are synchronized to the system clock to generate two data streams.

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures adequate timing when data is transferred to the system clock domain from the DQS domain. The DQSR90 and DDRCLKPOL signals are generated in the DQS read-write block.

Figure 2-13. MachXO2 Input Register Block Diagram (PIO on Right Edge)

More information on the input gearbox is available in TN1203, Implementing High-Speed Interfaces with MachXO2 Devices.

# **Output Gearbox**

Each PIC on the top edge has a built-in 8:1 output gearbox. Each of these output gearboxes may be programmed as a 7:1 serializer or as one ODDRX4 (8:1) gearbox or as two ODDRX2 (4:1) gearboxes. Table 2-10 shows the gearbox signals.

Table 2-10. Output Gearbox Signal List

| Name                       | I/O Type | Description                     |

|----------------------------|----------|---------------------------------|

| Q                          | Output   | High-speed data output          |

| D[7:0]                     | Input    | Low-speed data from device core |

| Video TX(7:1): D[6:0]      |          |                                 |

| GDDRX4(8:1): D[7:0]        |          |                                 |

| GDDRX2(4:1)(IOL-A): D[3:0] |          |                                 |

| GDDRX2(4:1)(IOL-C): D[7:4] |          |                                 |

| SCLK                       | Input    | Slow-speed system clock         |

| ECLK [1:0]                 | Input    | High-speed edge clock           |

| RST                        | Input    | Reset                           |

The gearboxes have three stage pipeline registers. The first stage registers sample the low-speed input data on the low-speed system clock. The second stage registers transfer data from the low-speed clock registers to the high-speed clock registers. The third stage pipeline registers controlled by high-speed edge clock shift and mux the high-speed data out to the sysIO buffer. Figure 2-17 shows the output gearbox block diagram.

Table 2-13. Supported Output Standards

| Output Standard                 | V <sub>CCIO</sub> (Typ.) |

|---------------------------------|--------------------------|

| Single-Ended Interfaces         |                          |

| LVTTL                           | 3.3                      |

| LVCMOS33                        | 3.3                      |

| LVCMOS25                        | 2.5                      |

| LVCMOS18                        | 1.8                      |

| LVCMOS15                        | 1.5                      |

| LVCMOS12                        | 1.2                      |

| LVCMOS33, Open Drain            | _                        |

| LVCMOS25, Open Drain            | _                        |

| LVCMOS18, Open Drain            | _                        |

| LVCMOS15, Open Drain            | _                        |

| LVCMOS12, Open Drain            | _                        |

| PCI33                           | 3.3                      |

| SSTL25 (Class I)                | 2.5                      |

| SSTL18 (Class I)                | 1.8                      |

| HSTL18(Class I)                 | 1.8                      |

| Differential Interfaces         |                          |

| LVDS <sup>1, 2</sup>            | 2.5, 3.3                 |

| BLVDS, MLVDS, RSDS <sup>2</sup> | 2.5                      |

| LVPECL <sup>2</sup>             | 3.3                      |

| MIPI <sup>2</sup>               | 2.5                      |

| Differential SSTL18             | 1.8                      |

| Differential SSTL25             | 2.5                      |

| Differential HSTL18             | 1.8                      |

<sup>1.</sup> MachXO2-640U, MachXO2-1200/U and larger devices have dedicated LVDS buffers.

# sysIO Buffer Banks

The numbers of banks vary between the devices of this family. MachXO2-1200U, MachXO2-2000/U and higher density devices have six I/O banks (one bank on the top, right and bottom side and three banks on the left side). The MachXO2-1200 and lower density devices have four banks (one bank per side). Figures 2-18 and 2-19 show the sysIO banks and their associated supplies for all devices.

<sup>2.</sup> These interfaces can be emulated with external resistors in all devices.

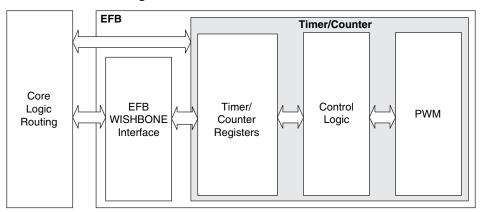

#### **Hardened Timer/Counter**

MachXO2 devices provide a hard Timer/Counter IP core. This Timer/Counter is a general purpose, bi-directional, 16-bit timer/counter module with independent output compare units and PWM support. The Timer/Counter supports the following functions:

- · Supports the following modes of operation:

- Watchdog timer

- Clear timer on compare match

- Fast PWM

- Phase and Frequency Correct PWM

- · Programmable clock input source

- Programmable input clock prescaler

- · One static interrupt output to routing

- One wake-up interrupt to on-chip standby mode controller.

- · Three independent interrupt sources: overflow, output compare match, and input capture

- · Auto reload

- · Time-stamping support on the input capture unit

- · Waveform generation on the output

- · Glitch-free PWM waveform generation with variable PWM period

- · Internal WISHBONE bus access to the control and status registers

- Stand-alone mode with preloaded control registers and direct reset input

Figure 2-23. Timer/Counter Block Diagram

Table 2-17. Timer/Counter Signal Description

| Port    | I/O | Description                                                                                                                                                                                                          |

|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tc_clki | I   | Timer/Counter input clock signal                                                                                                                                                                                     |

| tc_rstn | I   | Register tc_rstn_ena is preloaded by configuration to always keep this pin enabled                                                                                                                                   |

| tc_ic   | I   | Input capture trigger event, applicable for non-pwm modes with WISHBONE interface. If enabled, a rising edge of this signal will be detected and synchronized to capture tc_cnt value into tc_icr for time-stamping. |

| tc_int  | 0   | Without WISHBONE – Can be used as overflow flag With WISHBONE – Controlled by three IRQ registers                                                                                                                    |

| tc_oc   | 0   | Timer counter output signal                                                                                                                                                                                          |

# Programming and Erase Flash Supply Current – ZE Devices<sup>1, 2, 3, 4</sup>

| Symbol            | Symbol Parameter               |               | Typ.⁵ | Units |

|-------------------|--------------------------------|---------------|-------|-------|

|                   |                                | LCMXO2-256ZE  | 13    | mA    |

|                   |                                | LCMXO2-640ZE  | 14    | mA    |

| Icc               | Core Power Supply              | LCMXO2-1200ZE | 15    | mA    |

|                   |                                | LCMXO2-2000ZE | 17    | mA    |

|                   |                                | LCMXO2-4000ZE | 18    | mA    |

|                   |                                | LCMXO2-7000ZE | 20    | mA    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>6</sup> | All devices   | 0     | mA    |

- 1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

- 2. Assumes all inputs are held at  $\ensuremath{V_{\text{CCIO}}}$  or GND and all outputs are tri-stated.

- 3. Typical user pattern.

- 4. JTAG programming is at 25 MHz.

- 5. TJ = 25 °C, power supplies at nominal voltage.

- 6. Per bank.  $V_{CCIO} = 2.5 \text{ V}$ . Does not include pull-up/pull-down.

|                    |                                                                 |                                                       | _         | 3        | _        | 2      | -1      |          |                        |

|--------------------|-----------------------------------------------------------------|-------------------------------------------------------|-----------|----------|----------|--------|---------|----------|------------------------|

| Parameter          | Description                                                     | Device                                                | Min.      | Max.     | Min.     | Max.   | Min.    | Max.     | Units                  |

| Generic DDR        | Inputs with Clock and Data Cer                                  | ntered at Pin Using PC                                | LK Pin fo | or Clock | Input –  | GDDRX4 | _RX.EC  | LK.Cent  | ered <sup>9, 12</sup>  |

| t <sub>SU</sub>    | Input Data Setup Before ECLK                                    |                                                       | 0.434     | _        | 0.535    | _      | 0.630   | _        | ns                     |

| t <sub>HO</sub>    | Input Data Hold After ECLK                                      | MachXO2-640U.                                         | 0.385     | _        | 0.395    | _      | 0.463   | _        | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Input Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,                 | _         | 420      | _        | 352    | _       | 292      | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency                                            | bottom side only <sup>11</sup>                        | _         | 210      |          | 176    |         | 146      | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                  |                                                       | _         | 53       | _        | 44     | _       | 37       | MHz                    |

| 7:1 LVDS Inp       | uts - GDDR71_RX.ECLK.7.19,12                                    | 2                                                     |           |          |          |        |         |          |                        |

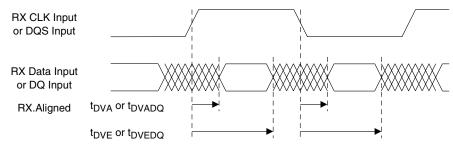

| t <sub>DVA</sub>   | Input Data Valid After ECLK                                     |                                                       | _         | 0.307    | _        | 0.316  | _       | 0.326    | UI                     |

| t <sub>DVE</sub>   | Input Data Hold After ECLK                                      |                                                       | 0.662     | _        | 0.650    | _      | 0.649   | _        | UI                     |

| f <sub>DATA</sub>  | DDR71 Serial Input Data<br>Speed                                | MachXO2-640U,<br>MachXO2-1200/U                       | _         | 420      | _        | 352    | _       | 292      | Mbps                   |

| f <sub>DDR71</sub> | DDR71 ECLK Frequency                                            | and larger devices,<br>bottom side only <sup>11</sup> | _         | 210      |          | 176    |         | 146      | MHz                    |

| f <sub>CLKIN</sub> | 7:1 Input Clock Frequency<br>(SCLK) (minimum limited by<br>PLL) | bottom side only                                      | _         | 60       | _        | 50     | _       | 42       | MHz                    |

| Generic DDR        | Outputs with Clock and Data A                                   | ligned at Pin Using PC                                | LK Pin 1  | or Clock | (Input – | GDDRX  | 1_TX.S  | CLK.Aliç | ned <sup>9, 12</sup>   |

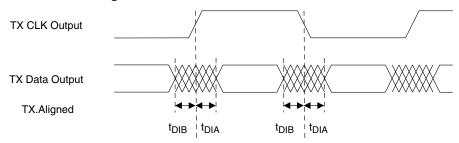

| t <sub>DIA</sub>   | Output Data Invalid After CLK Output                            |                                                       | _         | 0.850    | _        | 0.910  | _       | 0.970    | ns                     |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                        | All MachXO2<br>devices, all sides                     | _         | 0.850    | _        | 0.910  | _       | 0.970    | ns                     |

| f <sub>DATA</sub>  | DDRX1 Output Data Speed                                         | ,                                                     | _         | 140      | _        | 116    | _       | 98       | Mbps                   |

| f <sub>DDRX1</sub> | DDRX1 SCLK frequency                                            |                                                       | _         | 70       | _        | 58     |         | 49       | MHz                    |

| Generic DDR        | Outputs with Clock and Data Ce                                  | ntered at Pin Using PC                                | LK Pin f  | or Clock | Input –  | GDDRX  | 1_TX.SC | LK.Cen   | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>   | Output Data Valid Before CLK Output                             |                                                       | 2.720     | _        | 3.380    | _      | 4.140   | _        | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                           | All MachXO2                                           | 2.720     | _        | 3.380    | _      | 4.140   | _        | ns                     |

| f <sub>DATA</sub>  | DDRX1 Output Data Speed                                         | devices, all sides                                    | _         | 140      | _        | 116    |         | 98       | Mbps                   |

| f <sub>DDRX1</sub> | DDRX1 SCLK Frequency<br>(minimum limited by PLL)                |                                                       | _         | 70       | _        | 58     | _       | 49       | MHz                    |

| Generic DDR        | X2 Outputs with Clock and Data                                  | Aligned at Pin Using P                                | CLK Pin   | for Cloc | k Input  | - GDDR | X2_TX.E | CLK.Ali  | gned <sup>9, 12</sup>  |

| t <sub>DIA</sub>   | Output Data Invalid After CLK Output                            |                                                       | _         | 0.270    | _        | 0.300  | _       | 0.330    | ns                     |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                        | MachXO2-640U,<br>MachXO2-1200/U                       | _         | 0.270    | _        | 0.300  | _       | 0.330    | ns                     |

| f <sub>DATA</sub>  | DDRX2 Serial Output Data<br>Speed                               | and larger devices,<br>top side only                  | _         | 280      | _        | 234    | _       | 194      | Mbps                   |

| f <sub>DDRX2</sub> | DDRX2 ECLK frequency                                            |                                                       | _         | 140      | _        | 117    | _       | 97       | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                  |                                                       | _         | 70       | _        | 59     | _       | 49       | MHz                    |

|                     |                                                                  |                                                        |         | -3        | _         | 2      | -1      |         |                        |

|---------------------|------------------------------------------------------------------|--------------------------------------------------------|---------|-----------|-----------|--------|---------|---------|------------------------|

| Parameter           | Description                                                      | Device                                                 | Min.    | Max.      | Min.      | Max.   | Min.    | Max.    | Units                  |

| Generic DDR         | K2 Outputs with Clock and Data C                                 | entered at Pin Using P                                 | CLK Pin | for Cloc  | k Input – | GDDRX  | 2_TX.E0 | CLK.Cen | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>    | Output Data Valid Before CLK Output                              |                                                        | 1.445   | _         | 1.760     | _      | 2.140   | _       | ns                     |

| t <sub>DVA</sub>    | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                          | 1.445   | _         | 1.760     | _      | 2.140   | _       | ns                     |

| f <sub>DATA</sub>   | DDRX2 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,<br>top side only | _       | 280       | _         | 234    | _       | 194     | Mbps                   |

| f <sub>DDRX2</sub>  | DDRX2 ECLK Frequency<br>(minimum limited by PLL)                 | top oldo olliy                                         | _       | 140       | _         | 117    | _       | 97      | MHz                    |

| f <sub>SCLK</sub>   | SCLK Frequency                                                   |                                                        | _       | 70        | _         | 59     |         | 49      | MHz                    |

| Generic DDR         | X4 Outputs with Clock and Data                                   | Aligned at Pin Using P                                 | CLK Pin | for Cloc  | k Input   | - GDDR | X4_TX.E | CLK.Ali | gned <sup>9, 12</sup>  |

| t <sub>DIA</sub>    | Output Data Invalid After CLK Output                             |                                                        | _       | 0.270     | _         | 0.300  | _       | 0.330   | ns                     |

| t <sub>DIB</sub>    | Output Data Invalid Before<br>CLK Output                         | MachXO2-640U,<br>MachXO2-1200/U                        | _       | 0.270     | _         | 0.300  | _       | 0.330   | ns                     |

| f <sub>DATA</sub>   | DDRX4 Serial Output Data<br>Speed                                | and larger devices,<br>top side only                   | _       | 420       | _         | 352    | _       | 292     | Mbps                   |

| f <sub>DDRX4</sub>  | DDRX4 ECLK Frequency                                             |                                                        | _       | 210       | _         | 176    | _       | 146     | MHz                    |

| f <sub>SCLK</sub>   | SCLK Frequency                                                   |                                                        | _       | 53        | _         | 44     | _       | 37      | MHz                    |

| Generic DDR         | K4 Outputs with Clock and Data C                                 | entered at Pin Using P                                 | CLK Pin | for Clock | k Input – | GDDRX  | 4_TX.EC | CLK.Cen | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>    | Output Data Valid Before CLK Output                              |                                                        | 0.873   | _         | 1.067     | _      | 1.319   | _       | ns                     |

| t <sub>DVA</sub>    | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                          | 0.873   | _         | 1.067     | _      | 1.319   | _       | ns                     |

| f <sub>DATA</sub>   | DDRX4 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,<br>top side only | _       | 420       | _         | 352    | _       | 292     | Mbps                   |

| f <sub>DDRX4</sub>  | DDRX4 ECLK Frequency (minimum limited by PLL)                    | top oldo olliy                                         | _       | 210       | _         | 176    | _       | 146     | MHz                    |

| f <sub>SCLK</sub>   | SCLK Frequency                                                   |                                                        | _       | 53        | _         | 44     | _       | 37      | MHz                    |

| 7:1 LVDS Ou         | tputs - GDDR71_TX.ECLK.7:1 <sup>s</sup>                          | , 12                                                   | •       |           |           | •      | •       | •       |                        |

| t <sub>DIB</sub>    | Output Data Invalid Before<br>CLK Output                         |                                                        | _       | 0.240     | _         | 0.270  | _       | 0.300   | ns                     |

| t <sub>DIA</sub>    | Output Data Invalid After CLK Output                             | MachXO2-640U,                                          | _       | 0.240     | _         | 0.270  | _       | 0.300   | ns                     |

| f <sub>DATA</sub>   | DDR71 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,                  | _       | 420       | _         | 352    | _       | 292     | Mbps                   |

| f <sub>DDR71</sub>  | DDR71 ECLK Frequency                                             | top side only.                                         | _       | 210       | _         | 176    | _       | 146     | MHz                    |

| f <sub>CLKOUT</sub> | 7:1 Output Clock Frequency<br>(SCLK) (minimum limited by<br>PLL) |                                                        | _       | 60        | _         | 50     | _       | 42      | MHz                    |

Figure 3-5. Receiver RX.CLK.Aligned and MEM DDR Input Waveforms

Figure 3-6. Receiver RX.CLK.Centered Waveforms

Figure 3-7. Transmitter TX.CLK.Aligned Waveforms

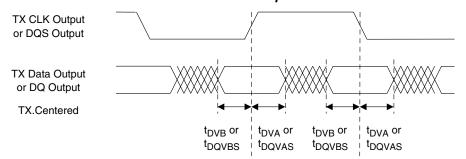

Figure 3-8. Transmitter TX.CLK.Centered and MEM DDR Output Waveforms

# **Signal Descriptions (Cont.)**

| Signal Name | I/O | Descriptions                                                                                                                                                                                                  |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INITN       | I/O | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, or when reserved as INITn in user mode, this pin has an active pull-up.                                                   |

| DONE        | I/O | Open Drain pin. Indicates that the configuration sequence is complete, and the start-up sequence is in progress. During configuration, or when reserved as DONE in user mode, this pin has an active pull-up. |

| MCLK/CCLK   | I/O | Input Configuration Clock for configuring an FPGA in Slave SPI mode. Output Configuration Clock for configuring an FPGA in SPI and SPIm configuration modes.                                                  |

| SN          | I   | Slave SPI active low chip select input.                                                                                                                                                                       |

| CSSPIN      | I/O | Master SPI active low chip select output.                                                                                                                                                                     |

| SI/SPISI    | I/O | Slave SPI serial data input and master SPI serial data output.                                                                                                                                                |

| SO/SPISO    | I/O | Slave SPI serial data output and master SPI serial data input.                                                                                                                                                |

| SCL         | I/O | Slave I <sup>2</sup> C clock input and master I <sup>2</sup> C clock output.                                                                                                                                  |

| SDA         | I/O | Slave I <sup>2</sup> C data input and master I <sup>2</sup> C data output.                                                                                                                                    |

# **Pinout Information Summary**

|                                                           | MachXO2-256            |                        |             |             | MachXO2-640  |                        |             | MachXO2-640U |          |

|-----------------------------------------------------------|------------------------|------------------------|-------------|-------------|--------------|------------------------|-------------|--------------|----------|

|                                                           | 32<br>QFN <sup>1</sup> | 48<br>QFN <sup>3</sup> | 64<br>ucBGA | 100<br>TQFP | 132<br>csBGA | 48<br>QFN <sup>3</sup> | 100<br>TQFP | 132<br>csBGA | 144 TQFP |

| General Purpose I/O per Bank                              | · II                   | I.                     |             |             |              |                        |             | •            | •        |

| Bank 0                                                    | 8                      | 10                     | 9           | 13          | 13           | 10                     | 18          | 19           | 27       |

| Bank 1                                                    | 2                      | 10                     | 12          | 14          | 14           | 10                     | 20          | 20           | 26       |

| Bank 2                                                    | 9                      | 10                     | 11          | 14          | 14           | 10                     | 20          | 20           | 28       |

| Bank 3                                                    | 2                      | 10                     | 12          | 14          | 14           | 10                     | 20          | 20           | 26       |

| Bank 4                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0        |

| Bank 5                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0        |

| Total General Purpose Single Ended I/O                    | 21                     | 40                     | 44          | 55          | 55           | 40                     | 78          | 79           | 107      |

| Differential I/O per Bank                                 |                        |                        |             |             |              |                        |             |              |          |

| Bank 0                                                    | 4                      | 5                      | 5           | 7           | 7            | 5                      | 9           | 10           | 14       |

| Bank 1                                                    | 1                      | 5                      | 6           | 7           | 7            | 5                      | 10          | 10           | 13       |

| Bank 2                                                    | 4                      | 5                      | 5           | 7           | 7            | 5                      | 10          | 10           | 14       |

| Bank 3                                                    | 1                      | 5                      | 6           | 7           | 7            | 5                      | 10          | 10           | 13       |

| Bank 4                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0        |

| Bank 5                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0        |

| Total General Purpose Differential I/O                    | 10                     | 20                     | 22          | 28          | 28           | 20                     | 39          | 40           | 54       |

| Dual Function I/O                                         | 22                     | 25                     | 27          | 29          | 29           | 25                     | 29          | 29           | 33       |

| High-speed Differential I/O                               |                        |                        | <u> </u>    |             | <u> </u>     |                        |             |              |          |

| Bank 0                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 7        |

| Gearboxes                                                 | 1                      | <u> </u>               | l           |             | l            |                        |             |              |          |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 7        |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 7        |

| DQS Groups                                                | I                      | I                      | 1           |             | 1            |                        |             | 1            | I        |

| Bank 1                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 2        |

| VCCIO Pins                                                |                        |                        |             |             |              |                        |             |              |          |

| Bank 0                                                    | 2                      | 2                      | 2           | 2           | 2            | 2                      | 2           | 2            | 3        |

| Bank 1                                                    | 1                      | 1                      | 2           | 2           | 2            | 1                      | 2           | 2            | 3        |

| Bank 2                                                    | 2                      | 2                      | 2           | 2           | 2            | 2                      | 2           | 2            | 3        |

| Bank 3                                                    | 1                      | 1                      | 2           | 2           | 2            | 1                      | 2           | 2            | 3        |

| Bank 4                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0        |

| Bank 5                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0        |

|                                                           | •                      | T                      | _           | Ī           | _            | Ī                      |             | 1            | T        |

| VCC                                                       | 2                      | 2                      | 2           | 2           | 2            | 2                      | 2           | 2            | 4        |

| GND <sup>2</sup>                                          | 2                      | 1                      | 8           | 8           | 8            | 1                      | 8           | 10           | 12       |

| NC                                                        | 0                      | 0                      | 1           | 26          | 58           | 0                      | 3           | 32           | 8        |

| Reserved for Configuration                                | 1                      | 1                      | 1           | 1           | 1            | 1                      | 1           | 1            | 1        |

| Total Count of Bonded Pins                                | 32                     | 49                     | 64          | 100         | 132          | 49                     | 100         | 132          | 144      |

Lattice recommends soldering the central thermal pad onto the top PCB ground for improved thermal resistance.

For 48 QFN package, exposed die pad is the device ground.

48-pin QFN information is 'Advanced'.

|                                                           |          |           | MachXO2-1200U |          |                     |           |

|-----------------------------------------------------------|----------|-----------|---------------|----------|---------------------|-----------|

|                                                           | 100 TQFP | 132 csBGA | 144 TQFP      | 25 WLCSP | 32 QFN <sup>1</sup> | 256 ftBGA |

| General Purpose I/O per Bank                              | 1        |           |               |          |                     | L         |

| Bank 0                                                    | 18       | 25        | 27            | 11       | 9                   | 50        |

| Bank 1                                                    | 21       | 26        | 26            | 0        | 2                   | 52        |

| Bank 2                                                    | 20       | 28        | 28            | 7        | 9                   | 52        |

| Bank 3                                                    | 20       | 25        | 26            | 0        | 2                   | 16        |

| Bank 4                                                    | 0        | 0         | 0             | 0        | 0                   | 16        |

| Bank 5                                                    | 0        | 0         | 0             | 0        | 0                   | 20        |

| Total General Purpose Single Ended I/O                    | 79       | 104       | 107           | 18       | 22                  | 206       |

| Differential I/O per Bank                                 |          |           |               |          |                     |           |

| Bank 0                                                    | 9        | 13        | 14            | 5        | 4                   | 25        |

| Bank 1                                                    | 10       | 13        | 13            | 0        | 1                   | 26        |

| Bank 2                                                    | 10       | 14        | 14            | 2        | 4                   | 26        |

| Bank 3                                                    | 10       | 12        | 13            | 0        | 1                   | 8         |

| Bank 4                                                    | 0        | 0         | 0             | 0        | 0                   | 8         |

| Bank 5                                                    | 0        | 0         | 0             | 0        | 0                   | 10        |

| Total General Purpose Differential I/O                    | 39       | 52        | 54            | 7        | 10                  | 103       |

| Dual Function I/O                                         | 31       | 33        | 33            | 18       | 22                  | 33        |

| High-speed Differential I/O                               |          |           |               |          |                     | l         |

| Bank 0                                                    | 4        | 7         | 7             | 0        | 0                   | 14        |

| Gearboxes                                                 | 1        | l         |               |          |                     | L         |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 4        | 7         | 7             | 0        | 0                   | 14        |

| Number of 7:1 or 8:1 Input Gearbox Available (Bank 2)     | 5        | 7         | 7             | 0        | 2                   | 14        |

| DQS Groups                                                |          |           |               |          |                     |           |

| Bank 1                                                    | 1        | 2         | 2             | 0        | 0                   | 2         |

| VCCIO Pins                                                |          |           |               |          |                     |           |

| Bank 0                                                    | 2        | 3         | 3             | 1        | 2                   | 4         |

| Bank 1                                                    | 2        | 3         | 3             | 0        | 1                   | 4         |

| Bank 2                                                    | 2        | 3         | 3             | 1        | 2                   | 4         |

| Bank 3                                                    | 3        | 3         | 3             | 0        | 1                   | 1         |

| Bank 4                                                    | 0        | 0         | 0             | 0        | 0                   | 2         |

| Bank 5                                                    | 0        | 0         | 0             | 0        | 0                   | 1         |

| VCC                                                       | 2        | 4         | 4             | 2        | 2                   | 8         |

| GND                                                       | 8        | 10        | 12            | 2        | 2                   | 24        |

| NC                                                        | 1        | 1         | 8             | 0        | 0                   | 1         |

| Reserved for Configuration                                | 1        | 1         | 1             | 1        | 1                   | 1         |

| Total Count of Bonded Pins                                | 100      | 132       | 144           | 25       | 32                  | 256       |

| 1 Lattice recommends coldering the centre                 |          | l .       |               |          |                     |           |

<sup>1.</sup> Lattice recommends soldering the central thermal pad onto the top PCB ground for improved thermal resistance.

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000ZE-1TG144C  | 6864 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000ZE-2TG144C  | 6864 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000ZE-3TG144C  | 6864 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000ZE-1BG256C  | 6864 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000ZE-2BG256C  | 6864 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000ZE-3BG256C  | 6864 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000ZE-1FTG256C | 6864 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000ZE-2FTG256C | 6864 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000ZE-3FTG256C | 6864 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000ZE-1BG332C  | 6864 | 1.2 V          | -1    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000ZE-2BG332C  | 6864 | 1.2 V          | -2    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000ZE-3BG332C  | 6864 | 1.2 V          | -3    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000ZE-1FG484C  | 6864 | 1.2 V          | -1    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000ZE-2FG484C  | 6864 | 1.2 V          | -2    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000ZE-3FG484C  | 6864 | 1.2 V          | -3    | Halogen-Free fpBGA | 484   | COM   |

| Part Number                          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|--------------------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200ZE-1TG100CR1 <sup>1</sup> | 1280 | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200ZE-2TG100CR1 <sup>1</sup> | 1280 | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200ZE-3TG100CR1 <sup>1</sup> | 1280 | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200ZE-1MG132CR1 <sup>1</sup> | 1280 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200ZE-2MG132CR1 <sup>1</sup> | 1280 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200ZE-3MG132CR1 <sup>1</sup> | 1280 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200ZE-1TG144CR1 <sup>1</sup> | 1280 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200ZE-2TG144CR1 <sup>1</sup> | 1280 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200ZE-3TG144CR1 <sup>1</sup> | 1280 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | COM   |

Specifications for the "LCMXO2-1200ZE-speed package CR1" are the same as the "LCMXO2-1200ZE-speed package C" devices respectively, except as specified in the R1 Device Specifications section of this data sheet.

| Part Number            | LUTs | Supply Voltage | Grade          | Package            | Leads | Temp. |

|------------------------|------|----------------|----------------|--------------------|-------|-------|

| LCMXO2-7000HC-4TG144C  | 6864 | 2.5 V / 3.3 V  | -4             | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-5TG144C  | 6864 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-6TG144C  | 6864 | 2.5 V / 3.3 V  | -6             | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-4BG256C  | 6864 | 2.5 V / 3.3 V  | -4             | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-5BG256C  | 6864 | 2.5 V / 3.3 V  | <del>-</del> 5 | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-6BG256C  | 6864 | 2.5 V / 3.3 V  | -6             | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-4FTG256C | 6864 | 2.5 V / 3.3 V  | -4             | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-5FTG256C | 6864 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-6FTG256C | 6864 | 2.5 V / 3.3 V  | -6             | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-4BG332C  | 6864 | 2.5 V / 3.3 V  | -4             | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-5BG332C  | 6864 | 2.5 V / 3.3 V  | <del>-</del> 5 | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-6BG332C  | 6864 | 2.5 V / 3.3 V  | -6             | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-4FG400C  | 6864 | 2.5 V / 3.3 V  | -4             | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-5FG400C  | 6864 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-6FG400C  | 6864 | 2.5 V / 3.3 V  | -6             | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-4FG484C  | 6864 | 2.5 V / 3.3 V  | -4             | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HC-5FG484C  | 6864 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HC-6FG484C  | 6864 | 2.5 V / 3.3 V  | -6             | Halogen-Free fpBGA | 484   | COM   |

| Part Number                          | LUTs | Supply Voltage | Grade          | Package            | Leads | Temp. |

|--------------------------------------|------|----------------|----------------|--------------------|-------|-------|

| LCMXO2-1200HC-4TG100CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -4             | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-5TG100CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | <del>-</del> 5 | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-6TG100CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6             | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-4MG132CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -4             | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-5MG132CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-6MG132CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6             | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-4TG144CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -4             | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200HC-5TG144CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5     | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200HC-6TG144CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6             | Halogen-Free TQFP  | 144   | COM   |

<sup>1.</sup> Specifications for the "LCMXO2-1200HC-speed package CR1" are the same as the "LCMXO2-1200HC-speed package C" devices respectively, except as specified in the R1 Device Specifications section of this data sheet.

| Part Number                          | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|--------------------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-1200HC-4TG100IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -4         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-5TG100IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-6TG100IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-4MG132IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -4         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-5MG132IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-6MG132IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-4TG144IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -4         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-5TG144IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | <b>-</b> 5 | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-6TG144IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6         | Halogen-Free TQFP  | 144   | IND   |

Specifications for the "LCMXO2-1200HC-speed package IR1" are the same as the "LCMXO2-1200ZE-speed package I" devices respectively, except as specified in the R1 Device Specifications section of this data sheet.

# High Performance Industrial Grade Devices Without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100I  | 2112 | 1.2 V          | -4         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-5TG100I  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-6TG100I  | 2112 | 1.2 V          | -6         | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-4MG132I  | 2112 | 1.2 V          | -4         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-5MG132I  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-6MG132I  | 2112 | 1.2 V          | -6         | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-4TG144I  | 2112 | 1.2 V          | -4         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-5TG144I  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-6TG144I  | 2112 | 1.2 V          | -6         | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-4BG256I  | 2112 | 1.2 V          | -4         | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-5BG256I  | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-6BG256I  | 2112 | 1.2 V          | -6         | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-4FTG256I | 2112 | 1.2 V          | -4         | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HE-5FTG256I | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HE-6FTG256I | 2112 | 1.2 V          | -6         | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade      | Package            | Leads | Temp. |

|------------------------|------|----------------|------------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484I | 2112 | 1.2 V          | -4         | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHE-5FG484I | 2112 | 1.2 V          | <b>-</b> 5 | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHE-6FG484I | 2112 | 1.2 V          | -6         | Halogen-Free fpBGA | 484   | IND   |

| Date          | Version | Section                                                                                                                                                                              | Change Summary                                                                                                                                                                         |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2012 | 01.7    | All                                                                                                                                                                                  | Updated document with new corporate logo.                                                                                                                                              |

|               | 01.6    |                                                                                                                                                                                      | Data sheet status changed from preliminary to final.                                                                                                                                   |

|               |         | Introduction                                                                                                                                                                         | MachXO2 Family Selection Guide table – Removed references to 49-ball WLCSP.                                                                                                            |

|               |         | DC and Switching<br>Characteristics                                                                                                                                                  | Updated Flash Download Time table.                                                                                                                                                     |

|               |         |                                                                                                                                                                                      | Modified Storage Temperature in the Absolute Maximum Ratings section.                                                                                                                  |

|               |         |                                                                                                                                                                                      | Updated I <sub>DK</sub> max in Hot Socket Specifications table.                                                                                                                        |

|               |         |                                                                                                                                                                                      | Modified Static Supply Current tables for ZE and HC/HE devices.                                                                                                                        |

|               |         |                                                                                                                                                                                      | Updated Power Supply Ramp Rates table.                                                                                                                                                 |

|               |         |                                                                                                                                                                                      | Updated Programming and Erase Supply Current tables.                                                                                                                                   |

|               |         |                                                                                                                                                                                      | Updated data in the External Switching Characteristics table.                                                                                                                          |

|               |         |                                                                                                                                                                                      | Corrected Absolute Maximum Ratings for Dedicated Input Voltage Applied for LCMXO2 HC.                                                                                                  |

|               |         |                                                                                                                                                                                      | DC Electrical Characteristics table – Minor corrections to conditions for $I_{IL},I_{IH.}$                                                                                             |

|               |         | Pinout Information                                                                                                                                                                   | Removed references to 49-ball WLCSP.                                                                                                                                                   |

|               |         |                                                                                                                                                                                      | Signal Descriptions table – Updated description for GND, VCC, and VCCIOx.                                                                                                              |

|               |         | Updated Pin Information Summary table – Number of VCCIOs, GNDs, VCCs, and Total Count of Bonded Pins for MachXO2-256, 640, and 640U and Dual Function I/O for MachXO2-4000 332caBGA. |                                                                                                                                                                                        |

|               |         | Ordering Information                                                                                                                                                                 | Removed references to 49-ball WLCSP                                                                                                                                                    |

| August 2011   | 01.5    | DC and Switching<br>Characteristics                                                                                                                                                  | Updated ESD information.                                                                                                                                                               |

|               |         | Ordering Information                                                                                                                                                                 | Updated footnote for ordering WLCSP devices.                                                                                                                                           |

|               | 01.4    | Architecture                                                                                                                                                                         | Updated information in Clock/Control Distribution Network and sys-<br>CLOCK Phase Locked Loops (PLLs).                                                                                 |

|               |         | DC and Switching<br>Characteristics                                                                                                                                                  | Updated $I_{\rm IL}$ and $I_{\rm IH}$ conditions in the DC Electrical Characteristics table.                                                                                           |

|               |         | Pinout Information                                                                                                                                                                   | Included number of 7:1 and 8:1 gearboxes (input and output) in the pin information summary tables.                                                                                     |

|               |         |                                                                                                                                                                                      | Updated Pin Information Summary table: Dual Function I/O, DQS Groups Bank 1, Total General Purpose Single-Ended I/O, Differential I/O Per Bank, Total Count of Bonded Pins, Gearboxes. |

|               |         |                                                                                                                                                                                      | Added column of data for MachXO2-2000 49 WLCSP.                                                                                                                                        |

|               |         | Ordering Information                                                                                                                                                                 | Updated R1 Device Specifications text section with information on migration from MachXO2-1200-R1 to Standard (non-R1) devices.                                                         |

|               |         |                                                                                                                                                                                      | Corrected Supply Voltage typo for part numbers: LCMX02-2000UHE-4FG484I, LCMX02-2000UHE-5FG484I, LCMX02-2000UHE-6FG484I.                                                                |

|               |         |                                                                                                                                                                                      | Added footnote for WLCSP package parts.                                                                                                                                                |

|               |         | Supplemental<br>Information                                                                                                                                                          | Removed reference to Stand-alone Power Calculator for MachXO2 Devices. Added reference to AN8086, Designing for Migration from MachXO2-1200-R1 to Standard (non-R1) Devices.           |