Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------|

| Product Status                 | Active                                                                          |

| Number of LABs/CLBs            | 32                                                                              |

| Number of Logic Elements/Cells | 256                                                                             |

| Total RAM Bits                 | -                                                                               |

| Number of I/O                  | 55                                                                              |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                   |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                 |

| Package / Case                 | 132-LFBGA, CSPBGA                                                               |

| Supplier Device Package        | 132-CSPBGA (8x8)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-256ze-1mg132c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## MachXO2 Family Data Sheet Architecture

### March 2016

Data Sheet DS1035

## **Architecture Overview**

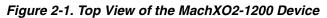

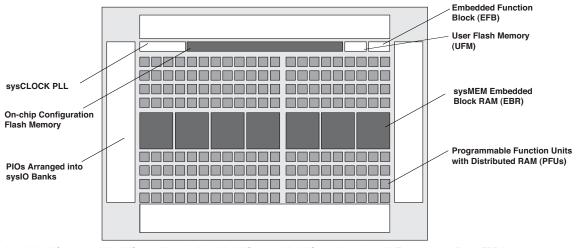

The MachXO2 family architecture contains an array of logic blocks surrounded by Programmable I/O (PIO). The larger logic density devices in this family have sysCLOCK<sup>™</sup> PLLs and blocks of sysMEM Embedded Block RAM (EBRs). Figure 2-1 and Figure 2-2 show the block diagrams of the various family members.

Note: MachXO2-256, and MachXO2-640/U are similar to MachXO2-1200. MachXO2-256 has a lower LUT count and no PLL or EBR blocks. MachXO2-640 has no PLL, a lower LUT count and two EBR blocks. MachXO2-640U has a lower LUT count, one PLL and seven EBR blocks.

Figure 2-2. Top View of the MachXO2-4000 Device

Note: MachXO2-1200U, MachXO2-2000/U and MachXO2-7000 are similar to MachXO2-4000. MachXO2-1200U and MachXO2-2000 have a lower LUT count, one PLL, and eight EBR blocks. MachXO2-2000U has a lower LUT count, two PLLs, and 10 EBR blocks. MachXO2-7000 has a higher LUT count, two PLLs, and 26 EBR blocks.

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In Ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/down counter with asynchronous clear

- Up/down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per-slice basis to allow fast arithmetic functions to be constructed by concatenating slices.

### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed by using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals.

MachXO2 devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in MachXO2 devices, please see TN1201, Memory Usage Guide for MachXO2 Devices.

### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                                                          | SPR 16x4 | PDPR 16x4 |  |  |  |

|----------------------------------------------------------|----------|-----------|--|--|--|

| Number of slices                                         | 3        | 3         |  |  |  |

| Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM |          |           |  |  |  |

ote: SPR = Single Port RAM, PDPR = Pseudo Dual

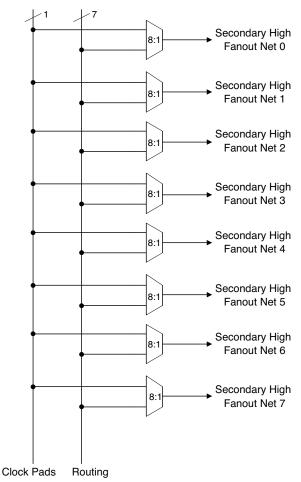

### Figure 2-6. Secondary High Fanout Nets for MachXO2 Devices

## sysCLOCK Phase Locked Loops (PLLs)

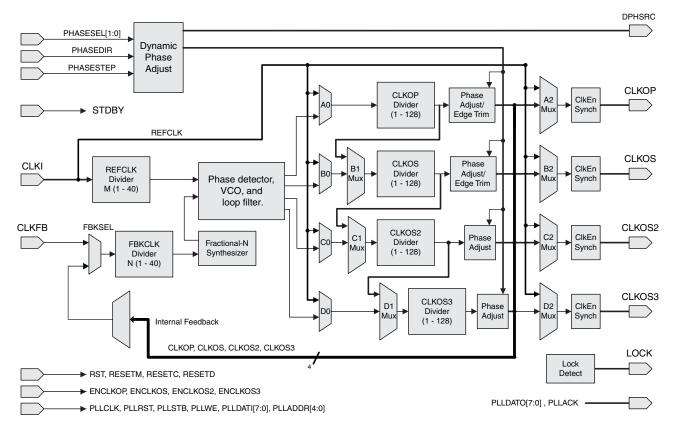

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The MachXO2-640U, MachXO2-1200/U and larger devices have one or more sysCLOCK PLL. CLKI is the reference frequency input to the PLL and its source can come from an external I/O pin or from internal routing. CLKFB is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The MachXO2 sysCLOCK PLLs support high resolution (16-bit) fractional-N synthesis. Fractional-N frequency synthesis allows the user to generate an output clock which is a non-integer multiple of the input frequency. For more information about using the PLL with Fractional-N synthesis, please see TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide.

Each output has its own output divider, thus allowing the PLL to generate different frequencies for each output. The output dividers can have a value from 1 to 128. The output dividers may also be cascaded together to generate low frequency clocks. The CLKOP, CLKOS, CLKOS2, and CLKOS3 outputs can all be used to drive the MachXO2 clock distribution network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 2-7.

The setup and hold times of the device can be improved by programming a phase shift into the CLKOS, CLKOS2, and CLKOS3 output clocks which will advance or delay the output clock with reference to the CLKOP output clock.

This phase shift can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after a phase adjustment on the output used as the feedback source and not relock until the  $t_{I,OCK}$  parameter has been satisfied.

The MachXO2 also has a feature that allows the user to select between two different reference clock sources dynamically. This feature is implemented using the PLLREFCS primitive. The timing parameters for the PLL are shown in the sysCLOCK PLL Timing table.

The MachXO2 PLL contains a WISHBONE port feature that allows the PLL settings, including divider values, to be dynamically changed from the user logic. When using this feature the EFB block must also be instantiated in the design to allow access to the WISHBONE ports. Similar to the dynamic phase adjustment, when PLL settings are updated through the WISHBONE port the PLL may lose lock and not relock until the t<sub>LOCK</sub> parameter has been satisfied. The timing parameters for the PLL are shown in the sysCLOCK PLL Timing table.

For more details on the PLL and the WISHBONE interface, see TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide.

### Figure 2-7. PLL Diagram

Table 2-4 provides signal descriptions of the PLL block.

| Table 2-4. PLL Signal | Descriptions |

|-----------------------|--------------|

|-----------------------|--------------|

| Port Name                                     | I/O | Description                                                       |

|-----------------------------------------------|-----|-------------------------------------------------------------------|

| CLKI                                          | I   | Input clock to PLL                                                |

| CLKFB                                         | I   | Feedback clock                                                    |

| PHASESEL[1:0]                                 | I   | Select which output is affected by Dynamic Phase adjustment ports |

| PHASEDIR I Dynamic Phase adjustment direction |     | Dynamic Phase adjustment direction                                |

| PHASESTEP                                     | I   | Dynamic Phase step – toggle shifts VCO phase adjust by one step.  |

## Programmable I/O Cells (PIC)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the MachXO2 devices, the PIO cells are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the MachXO2 devices, two adjacent PIOs can be combined to provide a complementary output driver pair.

The MachXO2-640U, MachXO2-1200/U and higher density devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. Half of the PIO pairs on the top edge of these devices can be configured as true LVDS transmit pairs. The PIO pairs on the bottom edge of these higher density devices have on-chip differential termination and also provide PCI support.

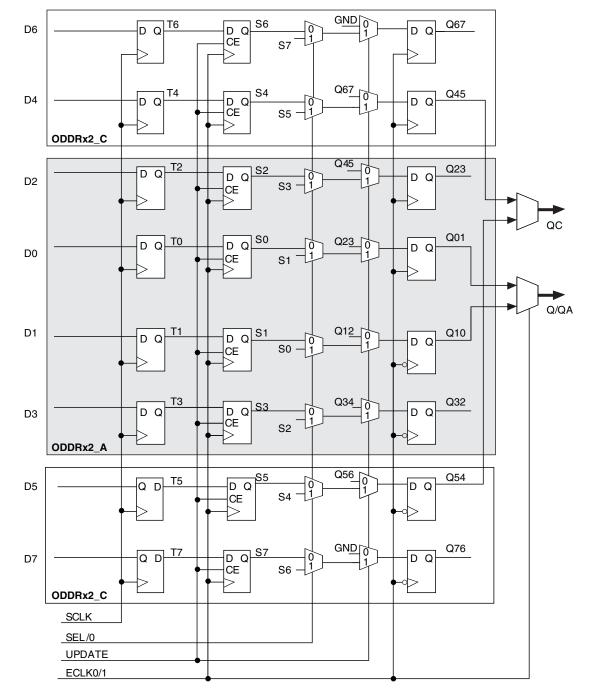

### Figure 2-17. Output Gearbox

More information on the output gearbox is available in TN1203, Implementing High-Speed Interfaces with MachXO2 Devices.

### Table 2-11. I/O Support Device by Device

|                                             | MachXO2-256,<br>MachXO2-640                                     | MachXO2-640U,<br>MachXO2-1200                                         | MachXO2-1200U<br>MachXO2-2000/U,<br>MachXO2-4000,<br>MachXO2-7000     |

|---------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|

| Number of I/O Banks                         | 4                                                               | 4                                                                     | 6                                                                     |

|                                             |                                                                 | Single-ended (all I/O banks)                                          | Single-ended (all I/O banks)                                          |

| Type of Input Buffers                       | Single-ended (all I/O banks)<br>Differential Receivers (all I/O | Differential Receivers (all I/O<br>banks)                             | Differential Receivers (all I/O<br>banks)                             |

|                                             | banks)                                                          | Differential input termination (bottom side)                          | Differential input termination (bottom side)                          |

|                                             | Single-ended buffers with                                       | Single-ended buffers with<br>complementary outputs (all I/O<br>banks) | Single-ended buffers with<br>complementary outputs (all I/O<br>banks) |

| Types of Output Buffers                     | complementary outputs (all I/O<br>banks)                        | Differential buffers with true<br>LVDS outputs (50% on top<br>side)   | Differential buffers with true<br>LVDS outputs (50% on top<br>side)   |

| Differential Output Emulation<br>Capability | All I/O banks                                                   | All I/O banks                                                         | All I/O banks                                                         |

| PCI Clamp Support                           | No                                                              | Clamp on bottom side only                                             | Clamp on bottom side only                                             |

### Table 2-12. Supported Input Standards

|                                 | VCCIO (Typ.)          |                       |                       |                       |                       |  |  |

|---------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|

| Input Standard                  | 3.3 V                 | 2.5 V                 | 1.8 V                 | 1.5                   | 1.2 V                 |  |  |

| Single-Ended Interfaces         |                       | •                     | •                     |                       |                       |  |  |

| LVTTL                           | ✓                     | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> |                       |  |  |

| LVCMOS33                        | ✓                     | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> |                       |  |  |

| LVCMOS25                        | <b>√</b> <sup>2</sup> | ✓                     | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> |                       |  |  |

| LVCMOS18                        | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | ✓                     | <b>√</b> <sup>2</sup> |                       |  |  |

| LVCMOS15                        | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | ~                     | <b>√</b> <sup>2</sup> |  |  |

| LVCMOS12                        | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | ✓                     |  |  |

| PCI <sup>1</sup>                | ✓                     |                       |                       |                       |                       |  |  |

| SSTL18 (Class I, Class II)      | 1                     | ✓                     | ✓                     |                       |                       |  |  |

| SSTL25 (Class I, Class II)      | 1                     | ✓                     |                       |                       |                       |  |  |

| HSTL18 (Class I, Class II)      | ✓                     | ✓                     | ✓                     |                       |                       |  |  |

| Differential Interfaces         | •                     | •                     |                       |                       |                       |  |  |

| LVDS                            | ✓                     | ✓                     |                       |                       |                       |  |  |

| BLVDS, MVDS, LVPECL, RSDS       | ✓                     | ✓                     |                       |                       |                       |  |  |

| MIPI <sup>3</sup>               | ✓                     | ✓                     |                       |                       |                       |  |  |

| Differential SSTL18 Class I, II | ✓                     | ✓                     | ✓                     |                       |                       |  |  |

| Differential SSTL25 Class I, II | ✓                     | ✓                     |                       |                       |                       |  |  |

| Differential HSTL18 Class I, II | ✓                     | ✓                     | ✓                     |                       |                       |  |  |

1. Bottom banks of MachXO2-640U, MachXO2-1200/U and higher density devices only.

2. Reduced functionality. Refer to TN1202, MachXO2 sysIO Usage Guide for more detail.

3. These interfaces can be emulated with external resistors in all devices.

| Device Subsystem                               | Feature Description                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bandgap                                        | The bandgap can be turned off in standby mode. When the Bandgap is turned off, ana-<br>log circuitry such as the POR, PLLs, on-chip oscillator, and referenced and differential<br>I/O buffers are also turned off. Bandgap can only be turned off for 1.2 V devices.                                                                        |

| Power-On-Reset (POR)                           | The POR can be turned off in standby mode. This monitors VCC levels. In the event of unsafe $V_{CC}$ drops, this circuit reconfigures the device. When the POR circuitry is turned off, limited power detector circuitry is still active. This option is only recommended for applications in which the power supply rails are reliable.     |

| On-Chip Oscillator                             | The on-chip oscillator has two power saving features. It may be switched off if it is not needed in your design. It can also be turned off in Standby mode.                                                                                                                                                                                  |

| PLL                                            | Similar to the on-chip oscillator, the PLL also has two power saving features. It can be statically switched off if it is not needed in a design. It can also be turned off in Standby mode. The PLL will wait until all output clocks from the PLL are driven low before powering off.                                                      |

| I/O Bank Controller                            | Referenced and differential I/O buffers (used to implement standards such as HSTL, SSTL and LVDS) consume more than ratioed single-ended I/Os such as LVCMOS and LVTTL. The I/O bank controller allows the user to turn these I/Os off dynamically on a per bank selection.                                                                  |

| Dynamic Clock Enable for Primary<br>Clock Nets | Each primary clock net can be dynamically disabled to save power.                                                                                                                                                                                                                                                                            |

| Power Guard                                    | Power Guard is a feature implemented in input buffers. This feature allows users to switch off the input buffer when it is not needed. This feature can be used in both clock and data paths. Its biggest impact is that in the standby mode it can be used to switch off clock inputs that are distributed using general routing resources. |

For more details on the standby mode refer to TN1198, Power Estimation and Management for MachXO2 Devices.

## Power On Reset

MachXO2 devices have power-on reset circuitry to monitor  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels during power-up and operation. At power-up, the POR circuitry monitors  $V_{CCINT}$  and  $V_{CCIO0}$  (controls configuration) voltage levels. It then triggers download from the on-chip configuration Flash memory after reaching the  $V_{PORUP}$  level specified in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. For devices without voltage regulators (ZE and HE devices),  $V_{CCINT}$  is the same as the  $V_{CC}$  supply voltage. For devices with voltage regulators (HC devices),  $V_{CCINT}$  is regulated from the  $V_{CC}$  supply voltage. From this voltage reference, the time taken for configuration and entry into user mode is specified as Flash Download Time (t<sub>REFRESH</sub>) in the DC and Switching Characteristics section of this data sheet. Before and during configuration, the I/Os are held in tristate. I/Os are released to user functionality once the device has finished configuration. Note that for HC devices, a separate POR circuit monitors external  $V_{CC}$  voltage in addition to the POR circuit that monitors the internal post-regulated power supply voltage level.

Once the device enters into user mode, the POR circuitry can optionally continue to monitor  $V_{CCINT}$  levels. If  $V_{CCINT}$  drops below  $V_{PORDNBG}$  level (with the bandgap circuitry switched on) or below  $V_{PORDNSRAM}$  level (with the bandgap circuitry switched off to conserve power) device functionality cannot be guaranteed. In such a situation the POR issues a reset and begins monitoring the  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels.  $V_{PORDNBG}$  and  $V_{PORDNSRAM}$  are both specified in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet.

Note that once a ZE or HE device enters user mode, users can switch off the bandgap to conserve power. When the bandgap circuitry is switched off, the POR circuitry also shuts down. The device is designed such that a minimal, low power POR circuit is still operational (this corresponds to the  $V_{PORDNSRAM}$  reset point described in the paragraph above). However this circuit is not as accurate as the one that operates when the bandgap is switched on. The low power POR circuit emulates an SRAM cell and is biased to trip before the vast majority of SRAM cells flip. If users are concerned about the  $V_{CC}$  supply dropping below  $V_{CC}$  (min) they should not shut down the bandgap or POR circuit.

# MachXO2 Family Data Sheet DC and Switching Characteristics

#### March 2017

### Data Sheet DS1035

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                               | MachXO2 ZE/HE (1.2 V) | MachXO2 HC (2.5 V / 3.3 V) |

|-----------------------------------------------|-----------------------|----------------------------|

| Supply Voltage V <sub>CC</sub>                | –0.5 V to 1.32 V      | –0.5 V to 3.75 V           |

| Output Supply Voltage V <sub>CCIO</sub>       | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| I/O Tri-state Voltage Applied <sup>4, 5</sup> | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| Dedicated Input Voltage Applied <sup>4</sup>  | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| Storage Temperature (Ambient)                 | –55 °C to 125 °C      | –55 °C to 125 °C           |

| Junction Temperature (T <sub>J</sub> )        | –40 °C to 125 °C      | –40 °C to 125 °C           |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

5. The dual function  $I^2C$  pins SCL and SDA are limited to -0.25 V to 3.75 V or to -0.3 V with a duration of <20 ns.

## **Recommended Operating Conditions**<sup>1</sup>

| Symbol                               | Parameter                                     | Min.  | Max. | Units |

|--------------------------------------|-----------------------------------------------|-------|------|-------|

| V <sub>CC</sub> <sup>1</sup>         | Core Supply Voltage for 1.2 V Devices         | 1.14  | 1.26 | V     |

|                                      | Core Supply Voltage for 2.5 V / 3.3 V Devices | 2.375 | 3.6  | V     |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup> | I/O Driver Supply Voltage                     | 1.14  | 3.6  | V     |

| t <sub>JCOM</sub>                    | Junction Temperature Commercial Operation     | 0     | 85   | °C    |

| t <sub>JIND</sub>                    | Junction Temperature Industrial Operation     | -40   | 100  | °C    |

1. Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both the same voltage, they must also be the same supply.

2. See recommended voltages by I/O standard in subsequent table.

3. V<sub>CCIO</sub> pins of unused I/O banks should be connected to the V<sub>CC</sub> power supply on boards.

## **Power Supply Ramp Rates**<sup>1</sup>

| Symbol            | Parameter                                       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------------------|------|------|------|-------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies. | 0.01 |      | 100  | V/ms  |

1. Assumes monotonic ramp rates.

<sup>© 2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Power-On-Reset Voltage Levels<sup>1, 2, 3, 4, 5</sup>

| Symbol                    | Parameter                                                                                            | Min. | Тур. | Max. | Units |

|---------------------------|------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>PORUP</sub>        | Power-On-Reset ramp up trip point (band gap based circuit monitoring $V_{CCINT}$ and $V_{CCIO0})$    | 0.9  | —    | 1.06 | V     |

| V <sub>PORUPEXT</sub>     | Power-On-Reset ramp up trip point (band gap based circuit monitoring external $V_{CC}$ power supply) | 1.5  | _    | 2.1  | V     |

| V <sub>PORDNBG</sub>      | Power-On-Reset ramp down trip point (band gap based circuit monitoring $V_{CCINT})$                  | 0.75 | _    | 0.93 | V     |

| V <sub>PORDNBGEXT</sub>   | Power-On-Reset ramp down trip point (band gap based circuit monitoring $\mathrm{V}_{\mathrm{CC}}$ )  | 0.98 | _    | 1.33 | V     |

| V <sub>PORDNSRAM</sub>    | Power-On-Reset ramp down trip point (SRAM based circuit monitoring $V_{CCINT})$                      | _    | 0.6  |      | V     |

| V <sub>PORDNSRAMEXT</sub> | Power-On-Reset ramp down trip point (SRAM based circuit monitoring $\mathrm{V}_{\mathrm{CC}}$ )      | _    | 0.96 | —    | V     |

1. These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

2. For devices without voltage regulators V<sub>CCINT</sub> is the same as the V<sub>CC</sub> supply voltage. For devices with voltage regulators, V<sub>CCINT</sub> is regulated from the V<sub>CC</sub> supply voltage.

3. Note that V<sub>PORUP</sub> (min.) and V<sub>PORDNBG</sub> (max.) are in different process corners. For any given process corner V<sub>PORDNBG</sub> (max.) is always 12.0 mV below V<sub>PORUP</sub> (min.).

4. V<sub>PORUPEXT</sub> is for HC devices only. In these devices a separate POR circuit monitors the external V<sub>CC</sub> power supply.

5. V<sub>CCIO0</sub> does not have a Power-On-Reset ramp down trip point. V<sub>CCIO0</sub> must remain within the Recommended Operating Conditions to ensure proper operation.

## **Programming/Erase Specifications**

| Symbol    | Parameter                                           | Min. | Max. <sup>1</sup> | Units  |  |

|-----------|-----------------------------------------------------|------|-------------------|--------|--|

| Nanagaya  | Flash Programming cycles per t <sub>RETENTION</sub> | —    | 10,000            | Cycles |  |

| NPROGCYC  | Flash functional programming cycles                 | —    | 100,000           | Cycles |  |

|           | Data retention at 100 °C junction temperature       | 10   | —                 | Years  |  |

| RETENTION | Data retention at 85 °C junction temperature        | 20   | _                 | Teals  |  |

1. Maximum Flash memory reads are limited to 7.5E13 cycles over the lifetime of the product.

## Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol          | Parameter                    | Condition                   | Max.    | Units |

|-----------------|------------------------------|-----------------------------|---------|-------|

| I <sub>DK</sub> | Input or I/O leakage Current | $0 < V_{IN} < V_{IH}$ (MAX) | +/-1000 | μΑ    |

1. Insensitive to sequence of  $V_{CC}$  and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$  and  $V_{CCIO}$ .

2.  $0 < V_{CC} < V_{CC}$  (MAX),  $0 < V_{CCIO} < V_{CCIO}$  (MAX).

3. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PD</sub> or I<sub>BH</sub>.

## **ESD** Performance

Please refer to the MachXO2 Product Family Qualification Summary for complete qualification data, including ESD performance.

## sysCLOCK PLL Timing

| Parameter                             | Descriptions                                   | Conditions                              | Min.   | Max.  | Units  |

|---------------------------------------|------------------------------------------------|-----------------------------------------|--------|-------|--------|

| f <sub>IN</sub>                       | Input Clock Frequency (CLKI, CLKFB)            |                                         | 7      | 400   | MHz    |

| fout                                  | Output Clock Frequency (CLKOP, CLKOS, CLKOS2)  |                                         | 1.5625 | 400   | MHz    |

| fout2                                 | Output Frequency (CLKOS3 cascaded from CLKOS2) |                                         | 0.0122 | 400   | MHz    |

| f <sub>VCO</sub>                      | PLL VCO Frequency                              |                                         | 200    | 800   | MHz    |

| f <sub>PFD</sub>                      | Phase Detector Input Frequency                 |                                         | 7      | 400   | MHz    |

| AC Characteri                         | stics                                          | •                                       |        |       |        |

| t <sub>DT</sub>                       | Output Clock Duty Cycle                        | Without duty trim selected <sup>3</sup> | 45     | 55    | %      |

| t <sub>DT_TRIM</sub> <sup>7</sup>     | Edge Duty Trim Accuracy                        |                                         | -75    | 75    | %      |

| t <sub>PH</sub> ⁴                     | Output Phase Accuracy                          |                                         | -6     | 6     | %      |

|                                       | Output Clock Pariad littar                     | f <sub>OUT</sub> > 100 MHz              | —      | 150   | ps p-p |

|                                       | Output Clock Period Jitter                     | f <sub>OUT</sub> < 100 MHz              | _      | 0.007 | UIPP   |

|                                       | Output Olaski Ousla ta susla littari           | f <sub>OUT</sub> > 100 MHz              | _      | 180   | ps p-p |

|                                       | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> < 100 MHz              | —      | 0.009 | UIPP   |

| . 18                                  |                                                | f <sub>PFD</sub> > 100 MHz              | —      | 160   | ps p-p |

| t <sub>OPJIT</sub> <sup>1, 8</sup> Ou | Output Clock Phase Jitter                      | f <sub>PFD</sub> < 100 MHz              | —      | 0.011 | UIPP   |

|                                       |                                                | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p |

|                                       | Output Clock Period Jitter (Fractional-N)      | f <sub>OUT</sub> < 100 MHz              | _      | 0.12  | UIPP   |

|                                       | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p |

|                                       | (Fractional-N)                                 | f <sub>OUT</sub> < 100 MHz              | _      | 0.12  | UIPP   |

| t <sub>SPO</sub>                      | Static Phase Offset                            | Divider ratio = integer                 | -120   | 120   | ps     |

| t <sub>W</sub>                        | Output Clock Pulse Width                       | At 90% or 10% <sup>3</sup>              | 0.9    | —     | ns     |

| tLOCK <sup>2, 5</sup>                 | PLL Lock-in Time                               |                                         | _      | 15    | ms     |

| t <sub>UNLOCK</sub>                   | PLL Unlock Time                                |                                         | _      | 50    | ns     |

| <b>.</b> 6                            | Innut Clask Daviad Littar                      | f <sub>PFD</sub> ≥ 20 MHz               | —      | 1,000 | ps p-p |

| t <sub>IPJIT</sub> <sup>6</sup>       | Input Clock Period Jitter                      | f <sub>PFD</sub> < 20 MHz               | —      | 0.02  | UIPP   |

| t <sub>HI</sub>                       | Input Clock High Time                          | 90% to 90%                              | 0.5    | —     | ns     |

| t <sub>LO</sub>                       | Input Clock Low Time                           | 10% to 10%                              | 0.5    | —     | ns     |

| t <sub>STABLE</sub> <sup>5</sup>      | STANDBY High to PLL Stable                     |                                         |        | 15    | ms     |

| t <sub>RST</sub>                      | RST/RESETM Pulse Width                         |                                         | 1      |       | ns     |

| t <sub>RSTREC</sub>                   | RST Recovery Time                              |                                         | 1      |       | ns     |

| t <sub>RST_DIV</sub>                  | RESETC/D Pulse Width                           |                                         | 10     |       | ns     |

| t <sub>RSTREC_DIV</sub>               | RESETC/D Recovery Time                         |                                         | 1      |       | ns     |

| t <sub>ROTATE-SETUP</sub>             | PHASESTEP Setup Time                           |                                         | 10     |       | ns     |

## **Over Recommended Operating Conditions**

## sysCLOCK PLL Timing (Continued)

### **Over Recommended Operating Conditions**

| Parameter              | Descriptions          | Conditions | Min. | Max. | Units      |

|------------------------|-----------------------|------------|------|------|------------|

| t <sub>ROTATE_WD</sub> | PHASESTEP Pulse Width |            | 4    | _    | VCO Cycles |

1. Period jitter sample is taken over 10,000 samples of the primary PLL output with a clean reference clock. Cycle-to-cycle jitter is taken over 1000 cycles. Phase jitter is taken over 2000 cycles. All values per JESD65B.

2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

3. Using LVDS output buffers.

4. CLKOS as compared to CLKOP output for one phase step at the maximum VCO frequency. See TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide for more details.

5. At minimum  $f_{PFD}$  As the  $f_{PFD}$  increases the time will decrease to approximately 60% the value listed.

6. Maximum allowed jitter on an input clock. PLL unlock may occur if the input jitter exceeds this specification. Jitter on the input clock may be transferred to the output clocks, resulting in jitter measurements outside the output specifications listed in this table.

7. Edge Duty Trim Accuracy is a percentage of the setting value. Settings available are 70 ps, 140 ps, and 280 ps in addition to the default value of none.

8. Jitter values measured with the internal oscillator operating. The jitter values will increase with loading of the PLD fabric and in the presence of SSO noise.

|                                                           | MachXO2-4000 |              |             |              |              |              |              |              |

|-----------------------------------------------------------|--------------|--------------|-------------|--------------|--------------|--------------|--------------|--------------|

|                                                           | 84<br>QFN    | 132<br>csBGA | 144<br>TQFP | 184<br>csBGA | 256<br>caBGA | 256<br>ftBGA | 332<br>caBGA | 484<br>fpBGA |

| General Purpose I/O per Bank                              |              |              |             |              |              |              |              |              |

| Bank 0                                                    | 27           | 25           | 27          | 37           | 50           | 50           | 68           | 70           |

| Bank 1                                                    | 10           | 26           | 29          | 37           | 52           | 52           | 68           | 68           |

| Bank 2                                                    | 22           | 28           | 29          | 39           | 52           | 52           | 70           | 72           |

| Bank 3                                                    | 0            | 7            | 9           | 10           | 16           | 16           | 24           | 24           |

| Bank 4                                                    | 9            | 8            | 10          | 12           | 16           | 16           | 16           | 16           |

| Bank 5                                                    | 0            | 10           | 10          | 15           | 20           | 20           | 28           | 28           |

| Total General Purpose Single Ended I/O                    | 68           | 104          | 114         | 150          | 206          | 206          | 274          | 278          |

| Differential I/O per Bank                                 |              |              |             |              |              |              |              |              |

| Bank 0                                                    | 13           | 13           | 14          | 18           | 25           | 25           | 34           | 35           |

| Bank 1                                                    | 4            | 13           | 14          | 18           | 26           | 26           | 34           | 34           |

| Bank 2                                                    | 11           | 14           | 14          | 19           | 26           | 26           | 35           | 36           |

| Bank 3                                                    | 0            | 3            | 4           | 4            | 8            | 8            | 12           | 12           |

| Bank 4                                                    | 4            | 4            | 5           | 6            | 8            | 8            | 8            | 8            |

| Bank 5                                                    | 0            | 5            | 5           | 7            | 10           | 10           | 14           | 14           |

| Total General Purpose Differential I/O                    | 32           | 52           | 56          | 72           | 103          | 103          | 137          | 139          |

| Dual Function I/O                                         | 28           | 37           | 37          | 37           | 37           | 37           | 37           | 37           |

| High-speed Differential I/O                               |              |              |             | •            |              |              |              |              |

| Bank 0                                                    | 8            | 8            | 9           | 8            | 18           | 18           | 18           | 18           |

| Gearboxes                                                 |              |              |             | •            |              |              |              |              |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 8            | 8            | 9           | 9            | 18           | 18           | 18           | 18           |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 11           | 14           | 14          | 12           | 18           | 18           | 18           | 18           |

| DQS Groups                                                | 1            | 1            |             |              |              |              |              |              |

| Bank 1                                                    | 1            | 2            | 2           | 2            | 2            | 2            | 2            | 2            |

| VCCIO Pins                                                |              |              |             |              |              |              |              |              |

| Bank 0                                                    | 3            | 3            | 3           | 3            | 4            | 4            | 4            | 10           |

| Bank 1                                                    | 1            | 3            | 3           | 3            | 4            | 4            | 4            | 10           |

| Bank 2                                                    | 2            | 3            | 3           | 3            | 4            | 4            | 4            | 10           |

| Bank 3                                                    | 1            | 1            | 1           | 1            | 1            | 1            | 2            | 3            |

| Bank 4                                                    | 1            | 1            | 1           | 1            | 2            | 2            | 1            | 4            |

| Bank 5                                                    | 1            | 1            | 1           | 1            | 1            | 1            | 2            | 3            |

| VCC                                                       | 4            | 4            | 4           | 4            | 8            | 8            | 8            | 12           |

| GND                                                       | 4            | 10           | 12          | 16           | 24           | 24           | 27           | 48           |

| NC                                                        | 1            | 1            | 1           | 1            | 1            | 1            | 5            | 105          |

| Reserved for configuration                                | 1            | 1            | 1           | 1            | 1            | 1            | 1            | 1            |

| liebel ved for bernigaration                              |              |              |             |              |              |              |              |              |

\_

|                                                           | MachXO2-7000 |           |           |           |           |           |

|-----------------------------------------------------------|--------------|-----------|-----------|-----------|-----------|-----------|

|                                                           | 144 TQFP     | 256 caBGA | 256 ftBGA | 332 caBGA | 400 caBGA | 484 fpBGA |

| General Purpose I/O per Bank                              |              | 1         | 1         |           |           | 1         |

| Bank 0                                                    | 27           | 50        | 50        | 68        | 83        | 82        |

| Bank 1                                                    | 29           | 52        | 52        | 70        | 84        | 84        |

| Bank 2                                                    | 29           | 52        | 52        | 70        | 84        | 84        |

| Bank 3                                                    | 9            | 16        | 16        | 24        | 28        | 28        |

| Bank 4                                                    | 10           | 16        | 16        | 16        | 24        | 24        |

| Bank 5                                                    | 10           | 20        | 20        | 30        | 32        | 32        |

| Total General Purpose Single Ended I/O                    | 114          | 206       | 206       | 278       | 335       | 334       |

| Differential I/O per Bank                                 |              |           |           |           |           |           |

| Bank 0                                                    | 14           | 25        | 25        | 34        | 42        | 41        |

| Bank 1                                                    | 14           | 26        | 26        | 35        | 42        | 42        |

| Bank 2                                                    | 14           | 26        | 26        | 35        | 42        | 42        |

| Bank 3                                                    | 4            | 8         | 8         | 12        | 14        | 14        |

| Bank 4                                                    | 5            | 8         | 8         | 8         | 12        | 12        |

| Bank 5                                                    | 5            | 10        | 10        | 15        | 16        | 16        |

| Total General Purpose Differential I/O                    | 56           | 103       | 103       | 139       | 168       | 167       |

| Dual Function I/O                                         | 37           | 37        | 37        | 37        | 37        | 37        |

| High-speed Differential I/O                               |              | -         | -         | -         | -         | -         |

| Bank 0                                                    | 9            | 20        | 20        | 21        | 21        | 21        |

| Gearboxes                                                 |              |           |           |           |           |           |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 9            | 20        | 20        | 21        | 21        | 21        |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 14           | 20        | 20        | 21        | 21        | 21        |

| DQS Groups                                                |              |           |           |           | •         | •         |

| Bank 1                                                    | 2            | 2         | 2         | 2         | 2         | 2         |

| VCCIO Pins                                                |              |           |           |           |           |           |

| Bank 0                                                    | 3            | 4         | 4         | 4         | 5         | 10        |

| Bank 1                                                    | 3            | 4         | 4         | 4         | 5         | 10        |

| Bank 2                                                    | 3            | 4         | 4         | 4         | 5         | 10        |

| Bank 3                                                    | 1            | 1         | 1         | 2         | 2         | 3         |

| Bank 4                                                    | 1            | 2         | 2         | 1         | 2         | 4         |

| Bank 5                                                    | 1            | 1         | 1         | 2         | 2         | 3         |

| 200                                                       |              |           |           |           |           | 4.0       |

| VCC                                                       | 4            | 8         | 8         | 8         | 10        | 12        |

| GND                                                       | 12           | 24        | 24        | 27        | 33        | 48        |

| NC                                                        | 1            | 1         | 1         | 1         | 0         | 49        |

| Reserved for Configuration                                | 1            | 1         | 1         | 1         | 1         | 1         |

| Total Count of Bonded Pins                                | 144          | 256       | 256       | 332       | 400       | 484       |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000ZE-1TG100C  | 2112 | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000ZE-2TG100C  | 2112 | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000ZE-3TG100C  | 2112 | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000ZE-1MG132C  | 2112 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000ZE-2MG132C  | 2112 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000ZE-3MG132C  | 2112 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000ZE-1TG144C  | 2112 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000ZE-2TG144C  | 2112 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000ZE-3TG144C  | 2112 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000ZE-1BG256C  | 2112 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000ZE-2BG256C  | 2112 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000ZE-3BG256C  | 2112 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000ZE-1FTG256C | 2112 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000ZE-2FTG256C | 2112 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000ZE-3FTG256C | 2112 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000ZE-1QN84C   | 4320 | 1.2 V          | -1    | Halogen-Free QFN   | 84    | COM   |

| LCMXO2-4000ZE-2QN84C   | 4320 | 1.2 V          | -2    | Halogen-Free QFN   | 84    | COM   |

| LCMXO2-4000ZE-3QN84C   | 4320 | 1.2 V          | -3    | Halogen-Free QFN   | 84    | COM   |

| LCMXO2-4000ZE-1MG132C  | 4320 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000ZE-2MG132C  | 4320 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000ZE-3MG132C  | 4320 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000ZE-1TG144C  | 4320 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000ZE-2TG144C  | 4320 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000ZE-3TG144C  | 4320 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000ZE-1BG256C  | 4320 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000ZE-2BG256C  | 4320 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000ZE-3BG256C  | 4320 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000ZE-1FTG256C | 4320 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000ZE-2FTG256C | 4320 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000ZE-3FTG256C | 4320 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000ZE-1BG332C  | 4320 | 1.2 V          | -1    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000ZE-2BG332C  | 4320 | 1.2 V          | -2    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000ZE-3BG332C  | 4320 | 1.2 V          | -3    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000ZE-1FG484C  | 4320 | 1.2 V          | -1    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-4000ZE-2FG484C  | 4320 | 1.2 V          | -2    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-4000ZE-3FG484C  | 4320 | 1.2 V          | -3    | Halogen-Free fpBGA | 484   | COM   |

## High-Performance Industrial Grade Devices with Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-256HC-4SG32I  | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256HC-5SG32I  | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256HC-6SG32I  | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256HC-4SG48I  | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-256HC-5SG48I  | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-256HC-6SG48I  | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-256HC-4UMG64I | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256HC-5UMG64I | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256HC-6UMG64I | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256HC-4TG100I | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256HC-5TG100I | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256HC-6TG100I | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256HC-4MG132I | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-256HC-5MG132I | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-256HC-6MG132I | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-640HC-4SG48I  | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-640HC-5SG48I  | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-640HC-6SG48I  | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-640HC-4TG100I | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640HC-5TG100I | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640HC-6TG100I | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640HC-4MG132I | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-640HC-5MG132I | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-640HC-6MG132I | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| Part Number           | LUTs | Supply Voltage | Grade | Package           | Leads | Temp. |

|-----------------------|------|----------------|-------|-------------------|-------|-------|

| LCMXO2-640UHC-4TG144I | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP | 144   | IND   |

| LCMXO2-640UHC-5TG144I | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP | 144   | IND   |

| LCMXO2-640UHC-6TG144I | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP | 144   | IND   |

| Part Number                          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|--------------------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200HC-4TG100IR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-5TG100IR11             | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-6TG100IR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-4MG132IR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-5MG132IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-6MG132IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-4TG144IR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-5TG144IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-6TG144IR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | IND   |

1. Specifications for the "LCMXO2-1200HC-speed package IR1" are the same as the "LCMXO2-1200ZE-speed package I" devices respectively, except as specified in the R1 Device Specifications section of this data sheet.

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HE-4MG132I  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-5MG132I  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-6MG132I  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-4TG144I  | 4320 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-5TG144I  | 4320 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-6TG144I  | 4320 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-4MG184I  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-5MG184I  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-6MG184I  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-4BG256I  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-5BG256I  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-6BG256I  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-4FTG256I | 4320 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-5FTG256I | 4320 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-6FTG256I | 4320 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-4BG332I  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-5BG332I  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-6BG332I  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-4FG484I  | 4320 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000HE-5FG484I  | 4320 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000HE-6FG484I  | 4320 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000HE-4TG144I  | 6864 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-5TG144I  | 6864 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-6TG144I  | 6864 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-4BG256I  | 6864 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-5BG256I  | 6864 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-6BG256I  | 6864 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-4FTG256I | 6864 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-5FTG256I | 6864 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-6FTG256I | 6864 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-4BG332I  | 6864 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-5BG332I  | 6864 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-6BG332I  | 6864 | 1.2 V          | -6    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-4FG484I  | 6864 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000HE-5FG484I  | 6864 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000HE-6FG484I  | 6864 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | IND   |

## MachXO2 Family Data Sheet Revision History

March 2017

Data Sheet DS1035

| Date           | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                              |

|----------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2017 3.3 |         | DC and Switching<br>Characteristics | Updated the Absolute Maximum Ratings section.<br>Added standards.                                                                                                                                                                                                                                           |

|                |         |                                     | Updated the sysIO Recommended Operating Conditions section.<br>Added standards.                                                                                                                                                                                                                             |

|                |         |                                     | Updated the sysIO Single-Ended DC Electrical Characteristics sec-<br>tion. Added standards.                                                                                                                                                                                                                 |

|                |         |                                     | Updated the MachXO2 External Switching Characteristics – HC/HE Devices section.<br>Under 7:1 LVDS Outputs – GDDR71_TX.ECLK.7:1, the $D_{VB}$ and the $D_{VA}$ parameters were changed to $D_{IB}$ and $D_{IA}$ . The parameter descriptions were also modified.                                             |

|                |         |                                     | Updated the MachXO2 External Switching Characteristics – ZE<br>Devices section.<br>Under 7:1 LVDS Outputs – GDDR71_TX.ECLK.7:1, the $D_{VB}$ and the<br>$D_{VA}$ parameters were changed to $D_{IB}$ and $D_{IA}$ . The parameter<br>descriptions were also modified.                                       |

|                |         |                                     | Updated the sysCONFIG Port Timing Specifications section. Corrected the $t_{\text{INITL}}$ units from ns to $\mu$ s.                                                                                                                                                                                        |

|                |         | Pinout Information                  | Updated the Signal Descriptions section. Revised the descriptions of the PROGRAMN, INITN, and DONE signals.                                                                                                                                                                                                 |

|                |         |                                     | Updated the Pinout Information Summary section. Added footnote to MachXO2-1200 32 QFN.                                                                                                                                                                                                                      |

|                |         | Ordering Information                | Updated the MachXO2 Part Number Description section. Corrected the MG184, BG256, FTG256 package information. Added "(0.8 mm Pitch)" to BG332.                                                                                                                                                               |

|                |         |                                     | Updated the Ultra Low Power Industrial Grade Devices, Halogen Free<br>(RoHS) Packaging section.<br>— Updated LCMXO2-1200ZE-1UWG25ITR50 footnote.<br>— Corrected footnote numbering typo.<br>— Added the LCMXO2-2000ZE-1UWG49ITR50 and LCMXO2-<br>2000ZE-1UWG49ITR1K part numbers. Updated/added footnote/s. |

<sup>© 2016</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Image: space with the second secon         | Date                | Version | Section              | Change Summary                                                                                     |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|----------------------|----------------------------------------------------------------------------------------------------|--|--|

| Guide table.     Architecture   Added information to Standby Mode and Power Saving Options section.     Pinout Information   Added the XO2-2000 49 WLCSP in the Pinout Information Summary table.     Ordering Information   Added the XO2-2000 2E in the Pinout Information Summary table.     Ordering Information   Added the XO2-2000ZE-1UWG49CTR in Ultra Low Power Commercial Grade Devices, Halogen Free (RoHS) Packaging section.     Added and LCMXO2-2000ZE-1UWG49ITR in Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging section.   Added and LCMXO2-2000ZE-1UWG49ITR in Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging section.     December 2013   02.3   Architecture   Updated Information on CLKOS output divider in sysCLOCK Phase Locked Loops (PLLs) section.     DC and Switching   Updated footnote 4 in sysIO Single-Ended DC Electrical Characteristics table; Updated V <sub>IL</sub> Max. (V) data for LVCMOS 25 and LVCMOS 28.     Updated V <sub>OS</sub> test condition in sysIO Differential Electrical Characteristics - LVDS table.   Updated Supported Input Standards table.     DC and Switching   Updated Power-On-Reset Voltage Levels table.   Updated Supported Input Standards table.     June 2013   02.1   Architecture   Architecture Overview – Added information on the state of the register on power up and after configuration.     June 2013   02.1   Architecture   Architec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | May 2014            | 2.5     | Architecture         | Updated TransFR description for PLL use during background Flash                                    |  |  |

| Image: section of the sectio | February 2014 02.4  |         | Introduction         |                                                                                                    |  |  |

| Image: series of the series         |                     |         | Architecture         |                                                                                                    |  |  |

| Added and LCMXO2-2000ZE-1UWG49CTR in Ultra Low Power<br>Commercial Grade Devices, Halogen Free (RoHS) Packaging section.     Added and LCMXO2-2000ZE-1UWG49ITR in Ultra Low Power<br>Industrial Grade Devices, Halogen Free (RoHS) Packaging section.     December 2013   02.3     Architecture   Updated information on CLKOS output divider in sysCLOCK Phase<br>Locked Loops (PLLs) section.     DC and Switching<br>Characteristics   Updated Static Supply Current – ZE Devices table.     Updated footnote 4 in sysIO Single-Ended DC Electrical Characteris<br>tics table; Updated V <sub>IL</sub> Max. (V) data for LVCMOS 25 and LVCMOS<br>28.     Updated Vos test condition in sysIO Differential Electrical Characteri-<br>istics - LVDS table.     September 2013   02.2     Oz and Switching<br>Characteristics   Removed I <sup>2</sup> C Clock-Stretching feature per PCN #10A-13.     Removed information on PDPR memory in RAM Mode section.   Updated Supported Input Standards table.     June 2013   02.1   Architecture   Architecture Overview – Added information on the state of the regis-<br>ter on power up and after configuration.     sysCLOCK Phase Locked Loops (PLLs) section – Added missing<br>cross reference to sysCLOC KPLL Timing table.   Added slew rate information to footnote 2 of the MachXO2 External<br>Switching Characteristics – HC/HE Devices and the MachXO2 External<br>Switching Characteristics – ZE Devices tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |         | Pinout Information   | Added the XO2-2000 49 WLCSP in the Pinout Information Summary table.                               |  |  |

| Image: bit is a series of the serie |                     |         | Ordering Information | Added UW49 package in MachXO2 Part Number Description.                                             |  |  |