Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------|

| Product Status                 | Active                                                                          |

| Number of LABs/CLBs            | 32                                                                              |

| Number of Logic Elements/Cells | 256                                                                             |

| Total RAM Bits                 | -                                                                               |

| Number of I/O                  | 55                                                                              |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                   |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                 |

| Package / Case                 | 132-LFBGA, CSPBGA                                                               |

| Supplier Device Package        | 132-CSPBGA (8x8)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-256ze-2mg132c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The logic blocks, Programmable Functional Unit (PFU) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each row has either the logic blocks or the EBR blocks. The PIO cells are located at the periphery of the device, arranged in banks. The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the MachXO2 family, the number of sysIO banks varies by device. There are different types of I/O buffers on the different banks. Refer to the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks; these blocks are found in MachXO2-640/U and larger devices. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT usage.

The MachXO2 registers in PFU and sysl/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

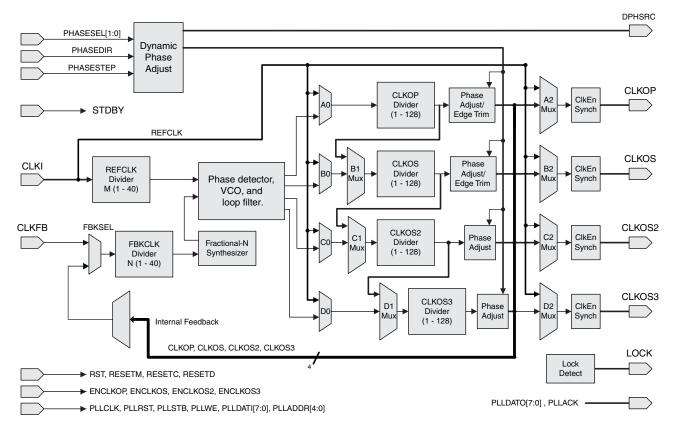

The MachXO2 architecture also provides up to two sysCLOCK Phase Locked Loop (PLL) blocks on MachXO2-640U, MachXO2-1200/U and larger devices. These blocks are located at the ends of the on-chip Flash block. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

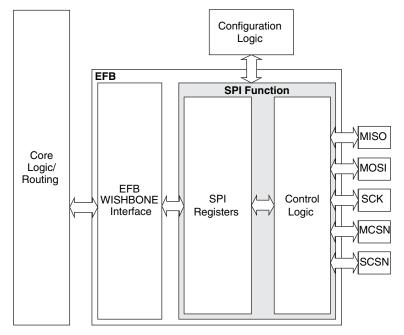

MachXO2 devices provide commonly used hardened functions such as SPI controller, I<sup>2</sup>C controller and timer/ counter. MachXO2-640/U and higher density devices also provide User Flash Memory (UFM). These hardened functions and the UFM interface to the core logic and routing through a WISHBONE interface. The UFM can also be accessed through the SPI, I<sup>2</sup>C and JTAG ports.

Every device in the family has a JTAG port that supports programming and configuration of the device as well as access to the user logic. The MachXO2 devices are available for operation from 3.3 V, 2.5 V and 1.2 V power supplies, providing easy integration into the overall system.

### **PFU Blocks**

The core of the MachXO2 device consists of PFU blocks, which can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. Each PFU block consists of four interconnected slices numbered 0 to 3 as shown in Figure 2-3. Each slice contains two LUTs and two registers. There are 53 inputs and 25 outputs associated with each PFU block.

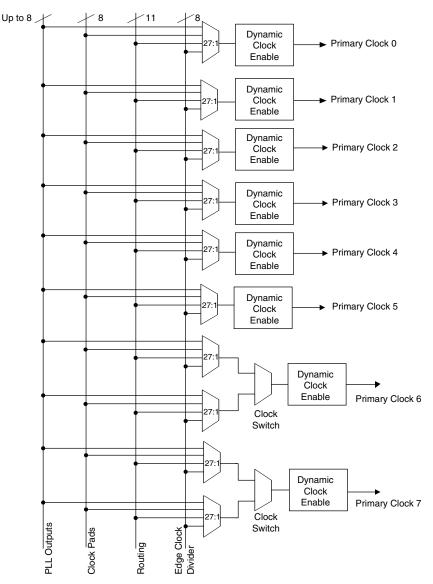

### Figure 2-5. Primary Clocks for MachXO2 Devices

Primary clocks for MachXO2-640U, MachXO2-1200/U and larger devices.

Note: MachXO2-640 and smaller devices do not have inputs from the Edge Clock Divider or PLL and fewer routing inputs. These devices have 17:1 muxes instead of 27:1 muxes.

Eight secondary high fanout nets are generated from eight 8:1 muxes as shown in Figure 2-6. One of the eight inputs to the secondary high fanout net input mux comes from dual function clock pins and the remaining seven come from internal routing. The maximum frequency for the secondary clock network is shown in MachXO2 External Switching Characteristics table.

This phase shift can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after a phase adjustment on the output used as the feedback source and not relock until the  $t_{I,OCK}$  parameter has been satisfied.

The MachXO2 also has a feature that allows the user to select between two different reference clock sources dynamically. This feature is implemented using the PLLREFCS primitive. The timing parameters for the PLL are shown in the sysCLOCK PLL Timing table.

The MachXO2 PLL contains a WISHBONE port feature that allows the PLL settings, including divider values, to be dynamically changed from the user logic. When using this feature the EFB block must also be instantiated in the design to allow access to the WISHBONE ports. Similar to the dynamic phase adjustment, when PLL settings are updated through the WISHBONE port the PLL may lose lock and not relock until the t<sub>LOCK</sub> parameter has been satisfied. The timing parameters for the PLL are shown in the sysCLOCK PLL Timing table.

For more details on the PLL and the WISHBONE interface, see TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide.

### Figure 2-7. PLL Diagram

Table 2-4 provides signal descriptions of the PLL block.

| Table 2-4. PLL Signal | Descriptions |

|-----------------------|--------------|

|-----------------------|--------------|

| Port Name     | I/O | Description                                                       |

|---------------|-----|-------------------------------------------------------------------|

| CLKI          | I   | Input clock to PLL                                                |

| CLKFB         | I   | Feedback clock                                                    |

| PHASESEL[1:0] | I   | Select which output is affected by Dynamic Phase adjustment ports |

| PHASEDIR      | I   | Dynamic Phase adjustment direction                                |

| PHASESTEP     | I   | Dynamic Phase step – toggle shifts VCO phase adjust by one step.  |

### Table 2-4. PLL Signal Descriptions (Continued)

| Port Name     | I/O | Description                                                                                            |

|---------------|-----|--------------------------------------------------------------------------------------------------------|

| CLKOP         | 0   | Primary PLL output clock (with phase shift adjustment)                                                 |

| CLKOS         | 0   | Secondary PLL output clock (with phase shift adjust)                                                   |

| CLKOS2        | 0   | Secondary PLL output clock2 (with phase shift adjust)                                                  |

| CLKOS3        | 0   | Secondary PLL output clock3 (with phase shift adjust)                                                  |

| LOCK          | 0   | PLL LOCK, asynchronous signal. Active high indicates PLL is locked to input and feed-<br>back signals. |

| DPHSRC        | 0   | Dynamic Phase source – ports or WISHBONE is active                                                     |

| STDBY         | I   | Standby signal to power down the PLL                                                                   |

| RST           | I   | PLL reset without resetting the M-divider. Active high reset.                                          |

| RESETM        | I   | PLL reset - includes resetting the M-divider. Active high reset.                                       |

| RESETC        | I   | Reset for CLKOS2 output divider only. Active high reset.                                               |

| RESETD        | I   | Reset for CLKOS3 output divider only. Active high reset.                                               |

| ENCLKOP       | I   | Enable PLL output CLKOP                                                                                |

| ENCLKOS       | I   | Enable PLL output CLKOS when port is active                                                            |

| ENCLKOS2      | I   | Enable PLL output CLKOS2 when port is active                                                           |

| ENCLKOS3      | I   | Enable PLL output CLKOS3 when port is active                                                           |

| PLLCLK        | I   | PLL data bus clock input signal                                                                        |

| PLLRST        | I   | PLL data bus reset. This resets only the data bus not any register values.                             |

| PLLSTB        | I   | PLL data bus strobe signal                                                                             |

| PLLWE         | I   | PLL data bus write enable signal                                                                       |

| PLLADDR [4:0] | I   | PLL data bus address                                                                                   |

| PLLDATI [7:0] | ļ   | PLL data bus data input                                                                                |

| PLLDATO [7:0] | 0   | PLL data bus data output                                                                               |

| PLLACK        | 0   | PLL data bus acknowledge signal                                                                        |

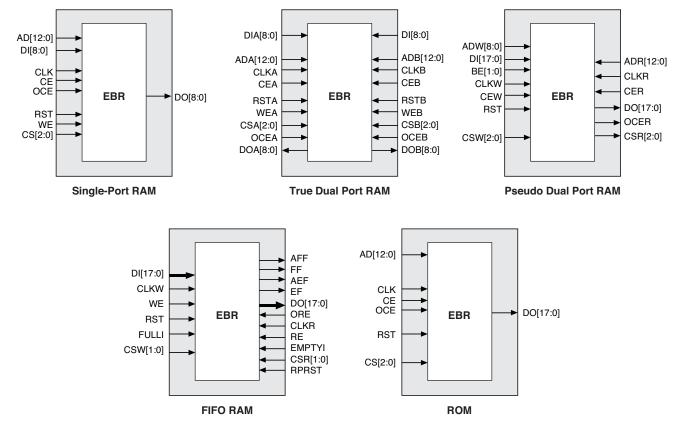

### sysMEM Embedded Block RAM Memory

The MachXO2-640/U and larger devices contain sysMEM Embedded Block RAMs (EBRs). The EBR consists of a 9-kbit RAM, with dedicated input and output registers. This memory can be used for a wide variety of purposes including data buffering, PROM for the soft processor and FIFO.

### sysMEM Memory Block

The sysMEM block can implement single port, dual port, pseudo dual port, or FIFO memories. Each block can be used in a variety of depths and widths as shown in Table 2-5.

#### Figure 2-8. sysMEM Memory Primitives

#### Table 2-6. EBR Signal Descriptions

| Port Name        | Description                 | Active State      |

|------------------|-----------------------------|-------------------|

| CLK              | Clock                       | Rising Clock Edge |

| CE               | Clock Enable                | Active High       |

| OCE <sup>1</sup> | Output Clock Enable         | Active High       |

| RST              | Reset                       | Active High       |

| BE <sup>1</sup>  | Byte Enable                 | Active High       |

| WE               | Write Enable                | Active High       |

| AD               | Address Bus                 | —                 |

| DI               | Data In                     | —                 |

| DO               | Data Out                    | —                 |

| CS               | Chip Select                 | Active High       |

| AFF              | FIFO RAM Almost Full Flag   | —                 |

| FF               | FIFO RAM Full Flag          | —                 |

| AEF              | FIFO RAM Almost Empty Flag  | —                 |

| EF               | FIFO RAM Empty Flag         | —                 |

| RPRST            | FIFO RAM Read Pointer Reset | —                 |

1. Optional signals.

2. For dual port EBR primitives a trailing 'A' or 'B' in the signal name specifies the EBR port A or port B respectively.

3. For FIFO RAM mode primitive, a trailing 'R' or 'W' in the signal name specifies the FIFO read port or write port respectively.

4. For FIFO RAM mode primitive FULLI has the same function as CSW(2) and EMPTYI has the same function as CSR(2).

5. In FIFO mode, CLKW is the write port clock, CSW is the write port chip select, CLKR is the read port clock, CSR is the read port chip select, ORE is the output read enable.

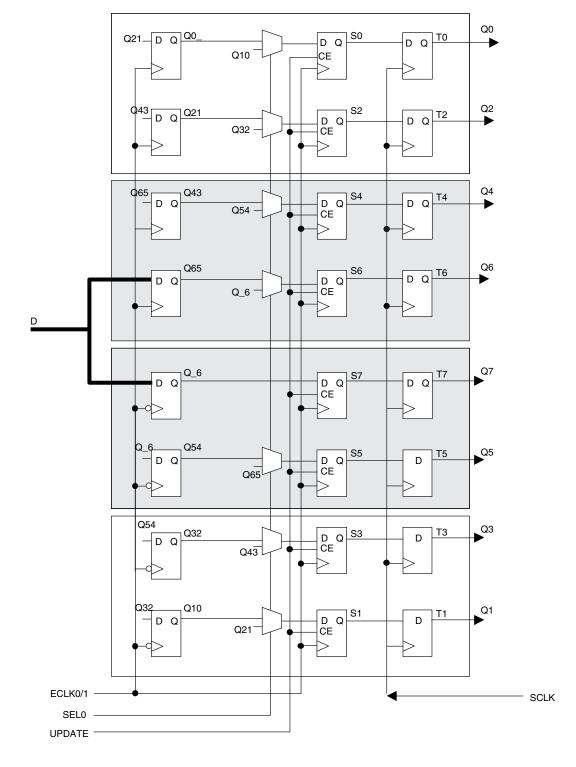

These gearboxes have three stage pipeline registers. The first stage registers sample the high-speed input data by the high-speed edge clock on its rising and falling edges. The second stage registers perform data alignment based on the control signals UPDATE and SEL0 from the control block. The third stage pipeline registers pass the data to the device core synchronized to the low-speed system clock. Figure 2-16 shows a block diagram of the input gearbox.

### Figure 2-16. Input Gearbox

More information on the input gearbox is available in TN1203, Implementing High-Speed Interfaces with MachXO2 Devices.

### **Output Gearbox**

Each PIC on the top edge has a built-in 8:1 output gearbox. Each of these output gearboxes may be programmed as a 7:1 serializer or as one ODDRX4 (8:1) gearbox or as two ODDRX2 (4:1) gearboxes. Table 2-10 shows the gearbox signals.

### Table 2-10. Output Gearbox Signal List

| Name                       | I/O Type | Description                     |

|----------------------------|----------|---------------------------------|

| Q                          | Output   | High-speed data output          |

| D[7:0]                     | Input    | Low-speed data from device core |

| Video TX(7:1): D[6:0]      |          |                                 |

| GDDRX4(8:1): D[7:0]        |          |                                 |

| GDDRX2(4:1)(IOL-A): D[3:0] |          |                                 |

| GDDRX2(4:1)(IOL-C): D[7:4] |          |                                 |

| SCLK                       | Input    | Slow-speed system clock         |

| ECLK [1:0]                 | Input    | High-speed edge clock           |

| RST                        | Input    | Reset                           |

The gearboxes have three stage pipeline registers. The first stage registers sample the low-speed input data on the low-speed system clock. The second stage registers transfer data from the low-speed clock registers to the high-speed clock registers. The third stage pipeline registers controlled by high-speed edge clock shift and mux the high-speed data out to the sysIO buffer. Figure 2-17 shows the output gearbox block diagram.

## **DDR Memory Support**

Certain PICs on the right edge of MachXO2-640U, MachXO2-1200/U and larger devices, have additional circuitry to allow the implementation of DDR memory interfaces. There are two groups of 14 or 12 PIOs each on the right edge with additional circuitry to implement DDR memory interfaces. This capability allows the implementation of up to 16-bit wide memory interfaces. One PIO from each group contains a control element, the DQS Read/Write Block, to facilitate the generation of clock and control signals (DQSR90, DQSW90, DDRCLKPOL and DATAVALID). These clock and control signals are distributed to the other PIO in the group through dedicated low skew routing.

## **DQS Read Write Block**

Source synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces a PLL is used for this adjustment. However, in DDR memories the clock (referred to as DQS) is not free-running so this approach cannot be used. The DQS Read Write block provides the required clock alignment for DDR memory interfaces. DQSR90 and DQSW90 signals are generated by the DQS Read Write block from the DQS input.

In a typical DDR memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the read cycle) is unknown. The MachXO2 family contains dedicated circuits to transfer data between these domains. To prevent set-up and hold violations, at the domain transfer between DQS (delayed) and the system clock, a clock polarity selector is used. This circuit changes the edge on which the data is registered in the synchronizing registers in the input register block. This requires evaluation at the start of each read cycle for the correct clock polarity. Prior to the read operation in DDR memories, DQS is in tri-state (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit in the DQS Read Write block detects the first DQS rising edge after the preamble state and generates the DDRCLKPOL signal. This signal is used to control the polarity of the clock to the synchronizing registers.

The temperature, voltage and process variations of the DQS delay block are compensated by a set of calibration signals (6-bit bus) from a DLL on the right edge of the device. The DLL loop is compensated for temperature, voltage and process variations by the system clock and feedback loop.

### sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement a wide variety of standards that are found in today's systems including LVCMOS, TTL, PCI, SSTL, HSTL, LVDS, BLVDS, MLVDS and LVPECL.

Each bank is capable of supporting multiple I/O standards. In the MachXO2 devices, single-ended output buffers, ratioed input buffers (LVTTL, LVCMOS and PCI), differential (LVDS) and referenced input buffers (SSTL and HSTL) are powered using I/O supply voltage ( $V_{CCIO}$ ). Each sysIO bank has its own  $V_{CCIO}$ . In addition, each bank has a voltage reference,  $V_{REF}$  which allows the use of referenced input buffers independent of the bank  $V_{CCIO}$ .

MachXO2-256 and MachXO2-640 devices contain single-ended ratioed input buffers and single-ended output buffers with complementary outputs on all the I/O banks. Note that the single-ended input buffers on these devices do not contain PCI clamps. In addition to the single-ended I/O buffers these two devices also have differential and referenced input buffers on all I/Os. The I/Os are arranged in pairs, the two pads in the pair are described as "T" and "C", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

There are some limitations on the use of the hardened user SPI. These are defined in the following technical notes:

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology (Appendix B)

- TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices

### Figure 2-22. SPI Core Block Diagram

Table 2-16 describes the signals interfacing with the SPI cores.

Table 2-16. SPI Core Signal Description

| Signal Name | I/O | Master/Slave | Description                                                                                                                                                                           |  |  |  |  |

|-------------|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| spi_csn[0]  | 0   | Master       | SPI master chip-select output                                                                                                                                                         |  |  |  |  |

| spi_csn[17] | 0   | Master       | Additional SPI chip-select outputs (total up to eight slaves)                                                                                                                         |  |  |  |  |

| spi_scsn    | I   | Slave        | SPI slave chip-select input                                                                                                                                                           |  |  |  |  |

| spi_irq     | 0   | Master/Slave | Interrupt request                                                                                                                                                                     |  |  |  |  |

| spi_clk     | I/O | Master/Slave | SPI clock. Output in master mode. Input in slave mode.                                                                                                                                |  |  |  |  |

| spi_miso    | I/O | Master/Slave | SPI data. Input in master mode. Output in slave mode.                                                                                                                                 |  |  |  |  |

| spi_mosi    | I/O | Master/Slave | SPI data. Output in master mode. Input in slave mode.                                                                                                                                 |  |  |  |  |

| ufm_sn      | I   | Slave        | Configuration Slave Chip Select (active low), dedicated for selecting the User Flash Memory (UFM).                                                                                    |  |  |  |  |

| cfg_stdby   | 0   | Master/Slave | Stand-by signal – To be connected only to the power module of the MachXO2 device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab. |  |  |  |  |

| cfg_wake    | 0   | Master/Slave | Wake-up signal – To be connected only to the power module of the MachXO2 device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab.  |  |  |  |  |

For more details on these embedded functions, please refer to TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices.

### **User Flash Memory (UFM)**

MachXO2-640/U and higher density devices provide a User Flash Memory block, which can be used for a variety of applications including storing a portion of the configuration image, initializing EBRs, to store PROM data or, as a general purpose user Flash memory. The UFM block connects to the device core through the embedded function block WISHBONE interface. Users can also access the UFM block through the JTAG, I<sup>2</sup>C and SPI interfaces of the device. The UFM block offers the following features:

- Non-volatile storage up to 256 kbits

- 100K write cycles

- Write access is performed page-wise; each page has 128 bits (16 bytes)

- Auto-increment addressing

- WISHBONE interface

For more information on the UFM, please refer to TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices.

### **Standby Mode and Power Saving Options**

MachXO2 devices are available in three options for maximum flexibility: ZE, HC and HE devices. The ZE devices have ultra low static and dynamic power consumption. These devices use a 1.2 V core voltage that further reduces power consumption. The HC and HE devices are designed to provide high performance. The HC devices have a built-in voltage regulator to allow for 2.5 V V<sub>CC</sub> and 3.3 V V<sub>CC</sub> while the HE devices operate at 1.2 V V<sub>CC</sub>.

MachXO2 devices have been designed with features that allow users to meet the static and dynamic power requirements of their applications by controlling various device subsystems such as the bandgap, power-on-reset circuitry, I/O bank controllers, power guard, on-chip oscillator, PLLs, etc. In order to maximize power savings, MachXO2 devices support an ultra low power Stand-by mode. While most of these features are available in all three device types, these features are mainly intended for use with MachXO2 ZE devices to manage power consumption.

In the stand-by mode the MachXO2 devices are powered on and configured. Internal logic, I/Os and memories are switched on and remain operational, as the user logic waits for an external input. The device enters this mode when the standby input of the standby controller is toggled or when an appropriate I<sup>2</sup>C or JTAG instruction is issued by an external master. Various subsystems in the device such as the band gap, power-on-reset circuitry etc can be configured such that they are automatically turned "off" or go into a low power consumption state to save power when the device enters this state. Note that the MachXO2 devices are powered on when in standby mode and all power supplies should remain in the Recommended Operating Conditions.

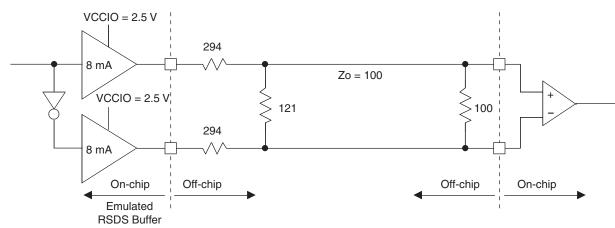

### RSDS

The MachXO2 family supports the differential RSDS standard. The output standard is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all the devices. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Use LVDS25E mode with suggested resistors for RSDS operation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

### Figure 3-4. RSDS (Reduced Swing Differential Standard)

#### Table 3-4. RSDS DC Conditions

| Parameter         | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20      | Ohms  |

| R <sub>S</sub>    | Driver series resistor      | 294     | Ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 121     | Ohms  |

| R <sub>T</sub>    | Receiver termination        | 100     | Ohms  |

| V <sub>OH</sub>   | Output high voltage         | 1.35    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.15    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.20    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25    | V     |

| Z <sub>BACK</sub> | Back impedance              | 101.5   | Ohms  |

| IDC               | DC output current           | 3.66    | mA    |

|                    |                                                                  |                                                                         | _       | -3       | _         | 2      | _       | -1      |                        |

|--------------------|------------------------------------------------------------------|-------------------------------------------------------------------------|---------|----------|-----------|--------|---------|---------|------------------------|

| Parameter          | Description                                                      | Device                                                                  | Min.    | Max.     | Min.      | Max.   | Min.    | Max.    | Units                  |

| Generic DDR        | 2 Outputs with Clock and Data C                                  | Centered at Pin Using P                                                 | CLK Pin | for Cloc | k Input – | GDDRX  | 2_TX.EC | CLK.Cen | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>   | Output Data Valid Before CLK<br>Output                           |                                                                         | 1.445   | _        | 1.760     | _      | 2.140   | _       | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                                           | 1.445   | _        | 1.760     | _      | 2.140   | _       | ns                     |

| f <sub>DATA</sub>  | DDRX2 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,<br>top side only                  | _       | 280      |           | 234    | _       | 194     | Mbps                   |

| f <sub>DDRX2</sub> | DDRX2 ECLK Frequency<br>(minimum limited by PLL)                 | _                                                                       | _       | 140      |           | 117    | _       | 97      | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                                         |         | 70       | _         | 59     | —       | 49      | MHz                    |

| Generic DDR        | X4 Outputs with Clock and Data                                   | Aligned at Pin Using P                                                  | CLK Pin | for Cloc | k Input   | - GDDR | X4_TX.E | CLK.Ali | gned <sup>9, 12</sup>  |

| t <sub>DIA</sub>   | Output Data Invalid After CLK<br>Output                          |                                                                         | _       | 0.270    | _         | 0.300  | _       | 0.330   | ns                     |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                         | MachXO2-640U,<br>MachXO2-1200/U<br>and larger devices,<br>top side only | _       | 0.270    |           | 0.300  | _       | 0.330   | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Output Data<br>Speed                                |                                                                         | _       | 420      |           | 352    | _       | 292     | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency                                             |                                                                         |         | 210      | _         | 176    |         | 146     | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                                         |         | 53       |           | 44     | —       | 37      | MHz                    |

| Generic DDR        | 4 Outputs with Clock and Data C                                  | entered at Pin Using P                                                  | CLK Pin | for Cloc | k Input – | GDDRX  | 4_TX.EC | LK.Cen  | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>   | Output Data Valid Before CLK<br>Output                           |                                                                         | 0.873   | _        | 1.067     | _      | 1.319   | _       | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                                           | 0.873   |          | 1.067     | _      | 1.319   | _       | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,<br>top side only                  | _       | 420      |           | 352    | _       | 292     | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency<br>(minimum limited by PLL)                 |                                                                         | _       | 210      |           | 176    | _       | 146     | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                                         |         | 53       | _         | 44     | —       | 37      | MHz                    |

| 7:1 LVDS Out       | tputs – GDDR71_TX.ECLK.7:1 <sup>s</sup>                          | , 12                                                                    |         |          |           |        |         | •       |                        |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                         |                                                                         | _       | 0.240    | _         | 0.270  | _       | 0.300   | ns                     |

| t <sub>DIA</sub>   | Output Data Invalid After CLK<br>Output                          | MachXO2-640U,                                                           | _       | 0.240    |           | 0.270  | _       | 0.300   | ns                     |

| f <sub>DATA</sub>  | DDR71 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,                                   | _       | 420      | _         | 352    | _       | 292     | Mbps                   |

| f <sub>DDR71</sub> | DDR71 ECLK Frequency                                             | top side only.                                                          |         | 210      | _         | 176    |         | 146     | MHz                    |

| fclkout            | 7:1 Output Clock Frequency<br>(SCLK) (minimum limited by<br>PLL) |                                                                         | _       | 60       | _         | 50     | _       | 42      | MHz                    |

|                        |                                          |                                                    | -     | -3 -2 |       | 2     | _     | ·1    |       |

|------------------------|------------------------------------------|----------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Parameter              | Description                              | Device                                             | Min.  | Max.  | Min.  | Max.  | Min.  | Max.  | Units |

| LPDDR <sup>9, 12</sup> |                                          | •                                                  |       |       |       |       |       |       | 1     |

| t <sub>DVADQ</sub>     | Input Data Valid After DQS<br>Input      |                                                    | _     | 0.349 | _     | 0.381 | _     | 0.396 | UI    |

| t <sub>DVEDQ</sub>     | Input Data Hold After DQS<br>Input       |                                                    | 0.665 | —     | 0.630 | _     | 0.613 | —     | UI    |

| t <sub>DQVBS</sub>     | Output Data Invalid Before<br>DQS Output | MachXO2-1200/U                                     | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| t <sub>DQVAS</sub>     | Output Data Invalid After DQS<br>Output  | and larger devices, right side only. <sup>13</sup> | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| f <sub>DATA</sub>      | MEM LPDDR Serial Data<br>Speed           |                                                    | _     | 120   | _     | 110   | _     | 96    | Mbps  |

| f <sub>SCLK</sub>      | SCLK Frequency                           |                                                    | —     | 60    | —     | 55    |       | 48    | MHz   |

| f <sub>LPDDR</sub>     | LPDDR Data Transfer Rate                 |                                                    | 0     | 120   | 0     | 110   | 0     | 96    | Mbps  |

| DDR <sup>9, 12</sup>   |                                          | ·                                                  |       |       | •     |       |       |       |       |

| t <sub>DVADQ</sub>     | Input Data Valid After DQS<br>Input      |                                                    | _     | 0.347 | _     | 0.374 | _     | 0.393 | UI    |

| t <sub>DVEDQ</sub>     | Input Data Hold After DQS<br>Input       |                                                    | 0.665 | _     | 0.637 | _     | 0.616 | —     | UI    |

| t <sub>DQVBS</sub>     | Output Data Invalid Before<br>DQS Output | MachXO2-1200/U<br>and larger devices,              | 0.25  | _     | 0.25  | _     | 0.25  | —     | UI    |

| t <sub>DQVAS</sub>     | Output Data Invalid After DQS<br>Output  | right side only. <sup>13</sup>                     | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| f <sub>DATA</sub>      | MEM DDR Serial Data Speed                |                                                    |       | 140   | _     | 116   |       | 98    | Mbps  |

| f <sub>SCLK</sub>      | SCLK Frequency                           |                                                    | —     | 70    |       | 58    | —     | 49    | MHz   |

| f <sub>MEM_DDR</sub>   | MEM DDR Data Transfer Rate               |                                                    | N/A   | 140   | N/A   | 116   | N/A   | 98    | Mbps  |

| DDR2 <sup>9, 12</sup>  |                                          | •                                                  |       |       |       |       |       |       |       |

| t <sub>DVADQ</sub>     | Input Data Valid After DQS<br>Input      |                                                    | _     | 0.372 | _     | 0.394 | _     | 0.410 | UI    |

| t <sub>DVEDQ</sub>     | Input Data Hold After DQS<br>Input       |                                                    | 0.690 | _     | 0.658 | _     | 0.618 | _     | UI    |

| t <sub>DQVBS</sub>     | Output Data Invalid Before<br>DQS Output | MachXO2-1200/U                                     | 0.25  | _     | 0.25  | _     | 0.25  | _     | UI    |

| t <sub>DQVAS</sub>     | Output Data Invalid After DQS<br>Output  | and larger devices, right side only. <sup>13</sup> | 0.25  | _     | 0.25  | _     | 0.25  |       | UI    |

| f <sub>DATA</sub>      | MEM DDR Serial Data Speed                | 1                                                  | —     | 140   | —     | 116   |       | 98    | Mbps  |

| f <sub>SCLK</sub>      | SCLK Frequency                           | 1                                                  | —     | 70    | —     | 58    |       | 49    | MHz   |

| f <sub>MEM_DDR2</sub>  | MEM DDR2 Data Transfer<br>Rate           |                                                    | N/A   | 140   | N/A   | 116   | N/A   | 98    | Mbps  |

1. Exact performance may vary with device and design implementation. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions, including industrial, can be extracted from the Diamond software.

2. General I/O timing numbers based on LVCMOS 2.5, 8 mA, 0 pf load, fast slew rate.

3. Generic DDR timing numbers based on LVDS I/O (for input, output, and clock ports).

4. DDR timing numbers based on SSTL25. DDR2 timing numbers based on SSTL18. LPDDR timing numbers based in LVCMOS18.

5. 7:1 LVDS (GDDR71) uses the LVDS I/O standard (for input, output, and clock ports).

6. For Generic DDRX1 mode  $t_{SU} = t_{HO} = (t_{DVE} - t_{DVA} - 0.03 \text{ ns})/2$ .

7. The  $t_{SU_{DEL}}$  and  $t_{H_{DEL}}$  values use the SCLK\_ZERHOLD default step size. Each step is 167 ps (-3), 182 ps (-2), 195 ps (-1).

8. This number for general purpose usage. Duty cycle tolerance is +/-10%.

9. Duty cycle is +/-5% for system usage.

10. The above timing numbers are generated using the Diamond design tool. Exact performance may vary with the device selected.

11. High-speed DDR and LVDS not supported in SG32 (32-Pin QFN) packages.

12. Advance information for MachXO2 devices in 48 QFN packages.

13. DDR memory interface not supported in QN84 (84 QFN) and SG32 (32 QFN) packages.

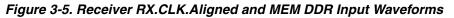

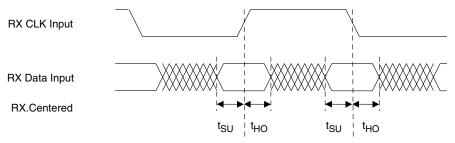

#### Figure 3-6. Receiver RX.CLK.Centered Waveforms

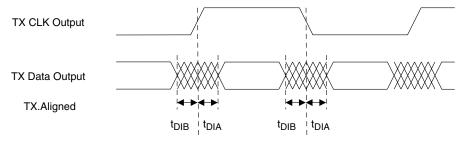

### Figure 3-7. Transmitter TX.CLK.Aligned Waveforms

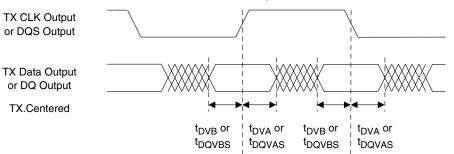

Figure 3-8. Transmitter TX.CLK.Centered and MEM DDR Output Waveforms

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000HC-4TG144C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-5TG144C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-6TG144C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-4BG256C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-5BG256C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-6BG256C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-4FTG256C | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-5FTG256C | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-6FTG256C | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-4BG332C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-5BG332C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-6BG332C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-4FG400C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-5FG400C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-6FG400C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-4FG484C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HC-5FG484C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HC-6FG484C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 484   | COM   |

| Part Number                          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|--------------------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200HC-4TG100CR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-5TG100CR11             | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-6TG100CR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-4MG132CR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-5MG132CR11             | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-6MG132CR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-4TG144CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200HC-5TG144CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200HC-6TG144CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | COM   |

1. Specifications for the "LCMXO2-1200HC-speed package CR1" are the same as the "LCMXO2-1200HC-speed package C" devices respectively, except as specified in the R1 Device Specifications section of this data sheet.

# High-Performance Commercial Grade Devices without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100C  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-5TG100C  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-6TG100C  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-4TG144C  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-5TG144C  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-6TG144C  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-4MG132C  | 2112 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-5MG132C  | 2112 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-6MG132C  | 2112 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-4BG256C  | 2112 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-5BG256C  | 2112 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-6BG256C  | 2112 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-4FTG256C | 2112 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-5FTG256C | 2112 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-6FTG256C | 2112 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484C | 2112 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-5FG484C | 2112 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-6FG484C | 2112 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HE-4TG144C  | 4320 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-5TG144C  | 4320 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-6TG144C  | 4320 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-4MG132C  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-5MG132C  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-6MG132C  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-4BG256C  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4MG184C  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5MG184C  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-6MG184C  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5BG256C  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-6BG256C  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4FTG256C | 4320 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-5FTG256C | 4320 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-6FTG256C | 4320 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-4BG332C  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HE-5BG332C  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | COM   |

| Part Number                            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000ZE-1UWG49ITR1               | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1UWG49ITR50 <sup>3</sup> | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1UWG49ITR1K <sup>2</sup> | 2112 | 1.2 V          | -1    | Halogen-Free WLCSP | 49    | IND   |

| LCMXO2-2000ZE-1TG100I                  | 2112 | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-2TG100I                  | 2112 | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-3TG100I                  | 2112 | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000ZE-1MG132I                  | 2112 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-2MG132I                  | 2112 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-3MG132I                  | 2112 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000ZE-1TG144I                  | 2112 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-2TG144I                  | 2112 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-3TG144I                  | 2112 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000ZE-1BG256I                  | 2112 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-2BG256I                  | 2112 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-3BG256I                  | 2112 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000ZE-1FTG256I                 | 2112 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000ZE-2FTG256I                 | 2112 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000ZE-3FTG256I                 | 2112 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | IND   |

1. This part number has a tape and reel quantity of 5,000 units with a minimum order quantity of 10,000 units. Order quantities must be in increments of 5,000 units. For example, a 10,000 unit order will be shipped in two reels with one reel containing 5,000 units and the other reel with less than 5,000 units (depending on test yields). Unserviced backlog will be canceled.

2. This part number has a tape and reel quantity of 1,000 units with a minimum order quantity of 1,000. Order quantities must be in increments of 1,000 units. For example, a 5,000 unit order will be shipped as 5 reels of 1000 units each.

3. This part number has a tape and reel quantity of 50 units with a minimum order quantity of 50. Order quantities must be in increments of 50 units. For example, a 1,000 unit order will be shipped as 20 reels of 50 units each.

| Part Number              | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|--------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200ZE-1TG100IR11 | 1280 | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200ZE-2TG100IR11 | 1280 | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200ZE-3TG100IR11 | 1280 | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200ZE-1MG132IR11 | 1280 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200ZE-2MG132IR11 | 1280 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200ZE-3MG132IR11 | 1280 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200ZE-1TG144IR11 | 1280 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200ZE-2TG144IR11 | 1280 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200ZE-3TG144IR11 | 1280 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | IND   |

1. Specifications for the "LCMXO2-1200ZE-speed package IR1" are the same as the "LCMXO2-1200ZE-speed package I" devices respectively, except as specified in the R1 Device Specifications section of this data sheet.

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HC-4QN84I   | 4320 | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000HC-5QN84I   | 4320 | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000HC-6QN84I   | 4320 | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000HC-4TG144I  | 4320 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HC-5TG144I  | 4320 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HC-6TG144I  | 4320 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HC-4MG132I  | 4320 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HC-5MG132I  | 4320 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HC-6MG132I  | 4320 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HC-4BG256I  | 4320 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HC-5BG256I  | 4320 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HC-6BG256I  | 4320 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HC-4FTG256I | 4320 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HC-5FTG256I | 4320 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HC-6FTG256I | 4320 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HC-4BG332I  | 4320 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HC-5BG332I  | 4320 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HC-6BG332I  | 4320 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HC-4FG484I  | 4320 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000HC-5FG484I  | 4320 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000HC-6FG484I  | 4320 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000HC-4TG144I  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HC-5TG144I  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HC-6TG144I  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HC-4BG256I  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HC-5BG256I  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HC-6BG256I  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HC-4FTG256I | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HC-5FTG256I | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HC-6FTG256I | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HC-4BG332I  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HC-5BG332I  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HC-6BG332I  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HC-4FG400I  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 400   | IND   |

| LCMXO2-7000HC-5FG400I  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 400   | IND   |

| LCMXO2-7000HC-6FG400I  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 400   | IND   |

| LCMXO2-7000HC-4FG484I  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000HC-5FG484I  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000HC-6FG484I  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 484   | IND   |

| Date          | Version           | Section                                                                                                                                                      | Change Summary                                                                                                                                                                                                  |

|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2014 | 2.9               | Introduction                                                                                                                                                 | Updated the Features section. Revised Table 1-1, MachXO2 Family<br>Selection Guide.<br>— Removed XO2-4000U data.<br>— Removed 400-ball ftBGA.<br>— Removed 25-ball WLCSP value for XO2-2000U.                   |

|               |                   | DC and Switching<br>Characteristics                                                                                                                          | Updated the Recommended Operating Conditions section. Adjusted Max. values for $V_{CC}$ and $V_{CCIO}$                                                                                                          |

|               |                   |                                                                                                                                                              | Updated the sysIO Recommended Operating Conditions section.<br>Adjusted Max. values for LVCMOS 3.3, LVTTL, PCI, LVDS33 and<br>LVPECL.                                                                           |

|               |                   | Pinout Information                                                                                                                                           | Updated the Pinout Information Summary section. Removed MachXO2-4000U.                                                                                                                                          |

|               |                   | Ordering Information                                                                                                                                         | Updated the MachXO2 Part Number Description section. Removed BG400 package.                                                                                                                                     |

|               |                   |                                                                                                                                                              | Updated the High-Performance Commercial Grade Devices with Volt-<br>age Regulator, Halogen Free (RoHS) Packaging section. Removed<br>LCMXO2-4000UHC part numbers.                                               |

|               |                   |                                                                                                                                                              | Updated the High-Performance Industrial Grade Devices with Voltage<br>Regulator, Halogen Free (RoHS) Packaging section. Removed<br>LCMXO2-4000UHC part numbers.                                                 |

| November 2014 | lovember 2014 2.8 | Introduction                                                                                                                                                 | Updated the Features section.<br>— Revised I/Os under Flexible Logic Architecture.<br>— Revised standby power under Ultra Low Power Devices.<br>— Revise input frequency range under Flexible On-Chip Clocking. |

|               |                   | Updated Table 1-1, MachXO2 Family Selection Guide.<br>— Added XO2-4000U data.<br>— Removed HE and ZE device options for XO2-4000.<br>— Added 400-ball ftBGA. |                                                                                                                                                                                                                 |

|               |                   | Pinout Information                                                                                                                                           | Updated the Pinout Information Summary section. Added MachXO2-4000U caBGA400 and MachXO2-7000 caBGA400.                                                                                                         |

|               |                   | Ordering Information                                                                                                                                         | Updated the MachXO2 Part Number Description section. Added BG400 package.                                                                                                                                       |

|               |                   |                                                                                                                                                              | Updated the Ordering Information section. Added MachXO2-4000U caBGA400 and MachXO2-7000 caBGA400 part numbers.                                                                                                  |

| October 2014  | 2.7               | Ordering Information                                                                                                                                         | Updated the Ultra Low Power Industrial Grade Devices, Halogen Free<br>(RoHS) Packaging section. Fixed typo in LCMXO2-2000ZE-<br>1UWG49ITR part number package.                                                  |

|               |                   | Architecture                                                                                                                                                 | Updated the Supported Standards section. Added MIPI information to Table 2-12. Supported Input Standards and Table 2-13. Supported Output Standards.                                                            |

|               |                   | DC and Switching<br>Characteristics                                                                                                                          | Updated the BLVDS section. Changed output impedance nominal values in Table 3-2, BLVDS DC Condition.                                                                                                            |

|               |                   |                                                                                                                                                              | Updated the LVPECL section. Changed output impedance nominal value in Table 3-3, LVPECL DC Condition.                                                                                                           |

|               |                   |                                                                                                                                                              | Updated the sysCONFIG Port Timing Specifications section.<br>Updated INITN low time values.                                                                                                                     |

| July 2014     | 2.6               | DC and Switching<br>Characteristics                                                                                                                          | Updated sysIO Single-Ended DC Electrical Characteristics <sup>1, 2</sup> section.<br>Updated footnote 4.                                                                                                        |

|               |                   |                                                                                                                                                              | Updated Register-to-Register Performance section. Updated foot-<br>note.                                                                                                                                        |

|               |                   | Ordering Information                                                                                                                                         | Updated UW49 package to UWG49 in MachXO2 Part Number Description.                                                                                                                                               |

|               |                   |                                                                                                                                                              | Updated LCMXO2-2000ZE-1UWG49CTR package in Ultra Low Power Commercial Grade Devices, Halogen Free (RoHS) Packaging.                                                                                             |