# Evit ce Semiconductor Corporation - <u>LCMXO2-4000HC-6FG484C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                           |

|--------------------------------|----------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 540                                                                              |

| Number of Logic Elements/Cells | 4320                                                                             |

| Total RAM Bits                 | 94208                                                                            |

| Number of I/O                  | 278                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 2.375V ~ 3.465V                                                                  |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                  |

| Package / Case                 | 484-BBGA                                                                         |

| Supplier Device Package        | 484-FBGA (23x23)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-4000hc-6fg484c |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

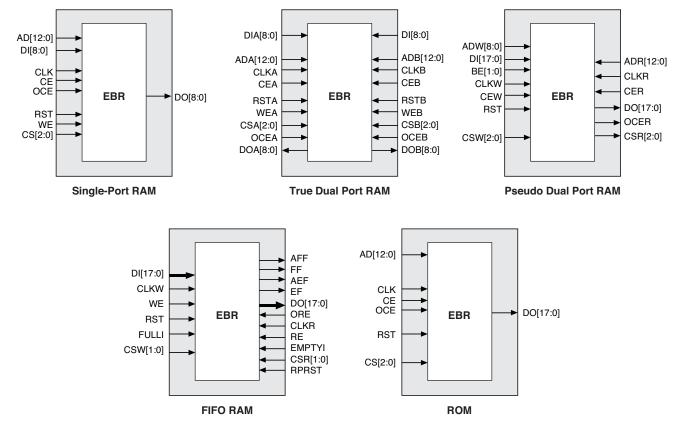

#### Figure 2-8. sysMEM Memory Primitives

#### Table 2-6. EBR Signal Descriptions

| Port Name        | Description                 | Active State      |

|------------------|-----------------------------|-------------------|

| CLK              | Clock                       | Rising Clock Edge |

| CE               | Clock Enable                | Active High       |

| OCE <sup>1</sup> | Output Clock Enable         | Active High       |

| RST              | Reset                       | Active High       |

| BE <sup>1</sup>  | Byte Enable                 | Active High       |

| WE               | Write Enable                | Active High       |

| AD               | Address Bus                 | —                 |

| DI               | Data In                     | —                 |

| DO               | Data Out                    | —                 |

| CS               | Chip Select                 | Active High       |

| AFF              | FIFO RAM Almost Full Flag   | —                 |

| FF               | FIFO RAM Full Flag          | —                 |

| AEF              | FIFO RAM Almost Empty Flag  | —                 |

| EF               | FIFO RAM Empty Flag         | —                 |

| RPRST            | FIFO RAM Read Pointer Reset | —                 |

1. Optional signals.

2. For dual port EBR primitives a trailing 'A' or 'B' in the signal name specifies the EBR port A or port B respectively.

3. For FIFO RAM mode primitive, a trailing 'R' or 'W' in the signal name specifies the FIFO read port or write port respectively.

4. For FIFO RAM mode primitive FULLI has the same function as CSW(2) and EMPTYI has the same function as CSR(2).

5. In FIFO mode, CLKW is the write port clock, CSW is the write port chip select, CLKR is the read port clock, CSR is the read port chip select, ORE is the output read enable.

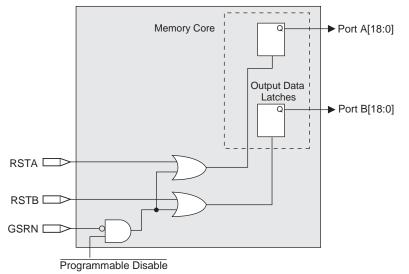

#### Figure 2-9. Memory Core Reset

For further information on the sysMEM EBR block, please refer to TN1201, Memory Usage Guide for MachXO2 Devices.

#### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-10. The GSR input to the EBR is always asynchronous.

#### Figure 2-10. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device wake up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-10. The reset timing rules apply to the RPReset input versus the RE input and the RST input versus the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs. For more details refer to TN1201, Memory Usage Guide for MachXO2 Devices.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

# Programmable I/O Cells (PIC)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the MachXO2 devices, the PIO cells are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the MachXO2 devices, two adjacent PIOs can be combined to provide a complementary output driver pair.

The MachXO2-640U, MachXO2-1200/U and higher density devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. Half of the PIO pairs on the top edge of these devices can be configured as true LVDS transmit pairs. The PIO pairs on the bottom edge of these higher density devices have on-chip differential termination and also provide PCI support.

### PIO

The PIO contains three blocks: an input register block, output register block and tri-state register block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

| Table 2-8 | . PIO | Signal | List |

|-----------|-------|--------|------|

|-----------|-------|--------|------|

| Pin Name               | I/О Туре | Description                                         |

|------------------------|----------|-----------------------------------------------------|

| CE                     | Input    | Clock Enable                                        |

| D                      | Input    | Pin input from sysIO buffer.                        |

| INDD                   | Output   | Register bypassed input.                            |

| INCK                   | Output   | Clock input                                         |

| Q0                     | Output   | DDR positive edge input                             |

| Q1                     | Output   | Registered input/DDR negative edge input            |

| D0                     | Input    | Output signal from the core (SDR and DDR)           |

| D1                     | Input    | Output signal from the core (DDR)                   |

| TD                     | Input    | Tri-state signal from the core                      |

| Q                      | Output   | Data output signals to sysIO Buffer                 |

| TQ                     | Output   | Tri-state output signals to sysIO Buffer            |

| DQSR90 <sup>1</sup>    | Input    | DQS shift 90-degree read clock                      |

| DQSW90 <sup>1</sup>    | Input    | DQS shift 90-degree write clock                     |

| DDRCLKPOL <sup>1</sup> | Input    | DDR input register polarity control signal from DQS |

| SCLK                   | Input    | System clock for input and output/tri-state blocks. |

| RST                    | Input    | Local set reset signal                              |

1. Available in PIO on right edge only.

#### Input Register Block

The input register blocks for the PIOs on all edges contain delay elements and registers that can be used to condition high-speed interface signals before they are passed to the device core. In addition to this functionality, the input register blocks for the PIOs on the right edge include built-in logic to interface to DDR memory.

Figure 2-12 shows the input register block for the PIOs located on the left, top and bottom edges. Figure 2-13 shows the input register block for the PIOs on the right edge.

#### Left, Top, Bottom Edges

Input signals are fed from the sysIO buffer to the input register block (as signal D). If desired, the input signal can bypass the register and delay elements and be used directly as a combinatorial signal (INDD), and a clock (INCK). If an input delay is desired, users can select a fixed delay. I/Os on the bottom edge also have a dynamic delay, DEL[4:0]. The delay, if selected, reduces input register hold time requirements when using a global clock. The input block allows two modes of operation. In single data rate (SDR) the data is registered with the system clock (SCLK) by one of the registers in the single data rate sync register block. In Generic DDR mode, two registers are used to sample the data on the positive and negative edges of the system clock (SCLK) signal, creating two data streams.

| Device Subsystem                               | Feature Description                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bandgap                                        | The bandgap can be turned off in standby mode. When the Bandgap is turned off, ana-<br>log circuitry such as the POR, PLLs, on-chip oscillator, and referenced and differential<br>I/O buffers are also turned off. Bandgap can only be turned off for 1.2 V devices.                                                                        |

| Power-On-Reset (POR)                           | The POR can be turned off in standby mode. This monitors VCC levels. In the event of unsafe $V_{CC}$ drops, this circuit reconfigures the device. When the POR circuitry is turned off, limited power detector circuitry is still active. This option is only recommended for applications in which the power supply rails are reliable.     |

| On-Chip Oscillator                             | The on-chip oscillator has two power saving features. It may be switched off if it is not needed in your design. It can also be turned off in Standby mode.                                                                                                                                                                                  |

| PLL                                            | Similar to the on-chip oscillator, the PLL also has two power saving features. It can be statically switched off if it is not needed in a design. It can also be turned off in Standby mode. The PLL will wait until all output clocks from the PLL are driven low before powering off.                                                      |

| I/O Bank Controller                            | Referenced and differential I/O buffers (used to implement standards such as HSTL, SSTL and LVDS) consume more than ratioed single-ended I/Os such as LVCMOS and LVTTL. The I/O bank controller allows the user to turn these I/Os off dynamically on a per bank selection.                                                                  |

| Dynamic Clock Enable for Primary<br>Clock Nets | Each primary clock net can be dynamically disabled to save power.                                                                                                                                                                                                                                                                            |

| Power Guard                                    | Power Guard is a feature implemented in input buffers. This feature allows users to switch off the input buffer when it is not needed. This feature can be used in both clock and data paths. Its biggest impact is that in the standby mode it can be used to switch off clock inputs that are distributed using general routing resources. |

For more details on the standby mode refer to TN1198, Power Estimation and Management for MachXO2 Devices.

## Power On Reset

MachXO2 devices have power-on reset circuitry to monitor  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels during power-up and operation. At power-up, the POR circuitry monitors  $V_{CCINT}$  and  $V_{CCIO0}$  (controls configuration) voltage levels. It then triggers download from the on-chip configuration Flash memory after reaching the  $V_{PORUP}$  level specified in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. For devices without voltage regulators (ZE and HE devices),  $V_{CCINT}$  is the same as the  $V_{CC}$  supply voltage. For devices with voltage regulators (HC devices),  $V_{CCINT}$  is regulated from the  $V_{CC}$  supply voltage. From this voltage reference, the time taken for configuration and entry into user mode is specified as Flash Download Time (t<sub>REFRESH</sub>) in the DC and Switching Characteristics section of this data sheet. Before and during configuration, the I/Os are held in tristate. I/Os are released to user functionality once the device has finished configuration. Note that for HC devices, a separate POR circuit monitors external  $V_{CC}$  voltage in addition to the POR circuit that monitors the internal post-regulated power supply voltage level.

Once the device enters into user mode, the POR circuitry can optionally continue to monitor  $V_{CCINT}$  levels. If  $V_{CCINT}$  drops below  $V_{PORDNBG}$  level (with the bandgap circuitry switched on) or below  $V_{PORDNSRAM}$  level (with the bandgap circuitry switched off to conserve power) device functionality cannot be guaranteed. In such a situation the POR issues a reset and begins monitoring the  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels.  $V_{PORDNBG}$  and  $V_{PORDNSRAM}$  are both specified in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet.

Note that once a ZE or HE device enters user mode, users can switch off the bandgap to conserve power. When the bandgap circuitry is switched off, the POR circuitry also shuts down. The device is designed such that a minimal, low power POR circuit is still operational (this corresponds to the  $V_{PORDNSRAM}$  reset point described in the paragraph above). However this circuit is not as accurate as the one that operates when the bandgap is switched on. The low power POR circuit emulates an SRAM cell and is biased to trip before the vast majority of SRAM cells flip. If users are concerned about the  $V_{CC}$  supply dropping below  $V_{CC}$  (min) they should not shut down the bandgap or POR circuit.

# **DC Electrical Characteristics**

| Symbol                                            | Parameter                                   | Condition                                                                                                                                          | Min.                     | Тур. | Max.                     | Units |

|---------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

|                                                   |                                             | Clamp OFF and $V_{CCIO} < V_{IN} < V_{IH}$ (MAX)                                                                                                   | _                        | _    | +175                     | μΑ    |

|                                                   |                                             | Clamp OFF and $V_{IN} = V_{CCIO}$                                                                                                                  | -10                      |      | 10                       | μA    |

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1, 4</sup> | Input or I/O Leakage                        | Clamp OFF and V <sub>CCIO</sub> –0.97 V < V <sub>IN</sub> < V <sub>CCIO</sub>                                                                      | -175                     | _    | —                        | μA    |

|                                                   |                                             | Clamp OFF and 0 V < V <sub>IN</sub> < V <sub>CCIO</sub> –0.97 V                                                                                    |                          |      | 10                       | μA    |

|                                                   |                                             | Clamp OFF and V <sub>IN</sub> = GND                                                                                                                | —                        | _    | 10                       | μΑ    |

|                                                   |                                             | Clamp ON and 0 V < $V_{IN}$ < $V_{CCIO}$                                                                                                           | _                        | _    | 10                       | μΑ    |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current                  | 0 < V <sub>IN</sub> < 0.7 V <sub>CCIO</sub>                                                                                                        | -30                      | _    | -309                     | μA    |

| I <sub>PD</sub>                                   | I/O Active Pull-down<br>Current             | $V_{IL}$ (MAX) < $V_{IN}$ < $V_{CCIO}$                                                                                                             | 30                       |      | 305                      | μA    |

| I <sub>BHLS</sub>                                 | Bus Hold Low sustaining<br>current          | $V_{IN} = V_{IL} (MAX)$                                                                                                                            | 30                       |      | _                        | μA    |

| I <sub>BHHS</sub>                                 | Bus Hold High sustaining<br>current         | $V_{IN} = 0.7 V_{CCIO}$                                                                                                                            | -30                      | _    | _                        | μA    |

| I <sub>BHLO</sub>                                 | Bus Hold Low Overdrive<br>current           | $0 \leq V_{IN} \leq V_{CCIO}$                                                                                                                      | _                        | _    | 305                      | μA    |

| I <sub>BHHO</sub>                                 | Bus Hold High Overdrive<br>current          | $0 \leq V_{IN} \leq V_{CCIO}$                                                                                                                      | _                        | _    | -309                     | μA    |

| V <sub>BHT</sub> <sup>3</sup>                     | Bus Hold Trip Points                        |                                                                                                                                                    | V <sub>IL</sub><br>(MAX) | _    | V <sub>IH</sub><br>(MIN) | V     |

| C1                                                | I/O Capacitance <sup>2</sup>                | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = Typ., V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | 3                        | 5    | 9                        | pF    |

| C2                                                | Dedicated Input<br>Capacitance <sup>2</sup> | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}, 1.5 \text{ V}, 1.2 \text{ V}, V_{CC} = Typ., V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | 3                        | 5.5  | 7                        | pF    |

|                                                   |                                             | V <sub>CCIO</sub> = 3.3 V, Hysteresis = Large                                                                                                      | _                        | 450  | —                        | mV    |

|                                                   |                                             | V <sub>CCIO</sub> = 2.5 V, Hysteresis = Large                                                                                                      | _                        | 250  | —                        | mV    |

| V <sub>HYST</sub>                                 |                                             | V <sub>CCIO</sub> = 1.8 V, Hysteresis = Large                                                                                                      | _                        | 125  | —                        | mV    |

|                                                   | Hysteresis for Schmitt                      | V <sub>CCIO</sub> = 1.5 V, Hysteresis = Large                                                                                                      | _                        | 100  | —                        | mV    |

|                                                   | Trigger Inputs <sup>5</sup>                 | V <sub>CCIO</sub> = 3.3 V, Hysteresis = Small                                                                                                      | —                        | 250  | —                        | mV    |

|                                                   |                                             | V <sub>CCIO</sub> = 2.5 V, Hysteresis = Small                                                                                                      | —                        | 150  | —                        | mV    |

|                                                   |                                             | V <sub>CCIO</sub> = 1.8 V, Hysteresis = Small                                                                                                      | —                        | 60   | —                        | mV    |

|                                                   |                                             | V <sub>CCIO</sub> = 1.5 V, Hysteresis = Small                                                                                                      | _                        | 40   | —                        | mV    |

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

3. Please refer to  $V_{IL}$  and  $V_{IH}$  in the sysIO Single-Ended DC Electrical Characteristics table of this document.

4. When V<sub>IH</sub> is higher than V<sub>CCIO</sub>, a transient current typically of 30 ns in duration or less with a peak current of 6 mA can occur on the high-to-low transition. For true LVDS output pins in MachXO2-640U, MachXO2-1200/U and larger devices, V<sub>IH</sub> must be less than or equal to V<sub>CCIO</sub>.

5. With bus keeper circuit turned on. For more details, refer to TN1202, MachXO2 sysIO Usage Guide.

# Static Supply Current – ZE Devices<sup>1, 2, 3, 6</sup>

| Symbol            | Parameter                                            | Device        | Typ. <sup>4</sup> | Units |

|-------------------|------------------------------------------------------|---------------|-------------------|-------|

| Icc               | Core Power Supply                                    | LCMXO2-256ZE  | 18                | μΑ    |

|                   |                                                      | LCMXO2-640ZE  | 28                | μΑ    |

|                   |                                                      | LCMXO2-1200ZE | 56                | μΑ    |

|                   |                                                      | LCMXO2-2000ZE | 80                | μA    |

|                   |                                                      | LCMXO2-4000ZE | 124               | μΑ    |

|                   |                                                      | LCMXO2-7000ZE | 189               | μΑ    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>5</sup><br>$V_{CCIO} = 2.5 V$ | All devices   | 1                 | μΑ    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip oscillator is off, on-chip PLL is off. To estimate the impact of turning each of these items on, please refer to the following table or for more detail with your specific design use the Power Calculator tool.

3. Frequency = 0 MHz.

4.  $T_J = 25$  °C, power supplies at nominal voltage.

5. Does not include pull-up/pull-down.

6. To determine the MachXO2 peak start-up current data, use the Power Calculator tool.

# Static Power Consumption Contribution of Different Components – ZE Devices

The table below can be used for approximating static power consumption. For a more accurate power analysis for your design please use the Power Calculator tool.

| Symbol Parameter    |                                               | Тур. | Units |

|---------------------|-----------------------------------------------|------|-------|

| I <sub>DCBG</sub>   | Bandgap DC power contribution                 | 101  | μΑ    |

| IDCPOR              | POR DC power contribution                     | 38   | μΑ    |

| IDCIOBANKCONTROLLER | DC power contribution per I/O bank controller | 143  | μΑ    |

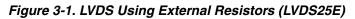

### LVDS Emulation

MachXO2 devices can support LVDS outputs via emulation (LVDS25E). The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all devices. The scheme shown in Figure 3-1 is one possible solution for LVDS standard implementation. Resistor values in Figure 3-1 are industry standard values for 1% resistors.

Note: All resistors are ±1%.

#### Table 3-1. LVDS25E DC Conditions

#### **Over Recommended Operating Conditions**

| Parameter         | Description                 | Тур.  | Units |  |

|-------------------|-----------------------------|-------|-------|--|

| Z <sub>OUT</sub>  | Output impedance            | 20    | Ohms  |  |

| R <sub>S</sub>    | Driver series resistor      | 158   | Ohms  |  |

| R <sub>P</sub>    | Driver parallel resistor    | 140   | Ohms  |  |

| R <sub>T</sub>    | Receiver termination        | 100   | Ohms  |  |

| V <sub>OH</sub>   | Output high voltage         | 1.43  | V     |  |

| V <sub>OL</sub>   | Output low voltage          | 1.07  | V     |  |

| V <sub>OD</sub>   | Output differential voltage | 0.35  | V     |  |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25  | V     |  |

| Z <sub>BACK</sub> | Back impedance              | 100.5 | Ohms  |  |

| I <sub>DC</sub>   | DC output current           | 6.03  | mA    |  |

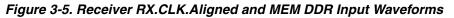

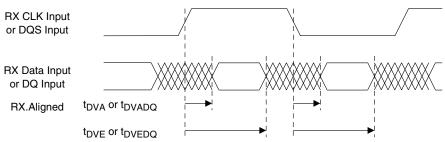

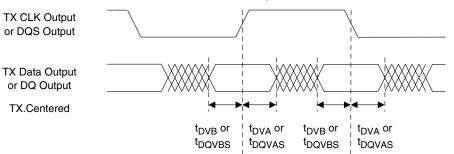

#### Figure 3-6. Receiver RX.CLK.Centered Waveforms

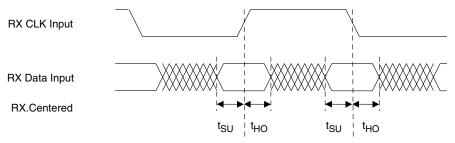

#### Figure 3-7. Transmitter TX.CLK.Aligned Waveforms

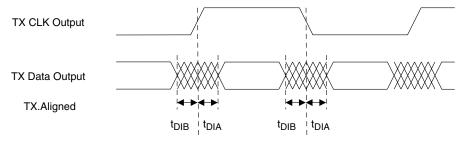

Figure 3-8. Transmitter TX.CLK.Centered and MEM DDR Output Waveforms

# MachXO2 Oscillator Output Frequency

| Symbol                 | Parameter                                                                   | Min.    | Тур.                   | Max     | Units |

|------------------------|-----------------------------------------------------------------------------|---------|------------------------|---------|-------|

| f                      | Oscillator Output Frequency (Commercial Grade Devices,<br>0 to 85°C)        | 125.685 | 133                    | 140.315 | MHz   |

| TMAX                   | Oscillator Output Frequency (Industrial Grade Devices,<br>–40 °C to 100 °C) | 124.355 | 124.355 133 141.645 MH |         | MHz   |

| t <sub>DT</sub>        | Output Clock Duty Cycle                                                     | 43      | 50                     | 57      | %     |

| t <sub>OPJIT</sub> 1   | Output Clock Period Jitter                                                  | 0.01    | 0.012                  | 0.02    | UIPP  |

| t <sub>STABLEOSC</sub> | STDBY Low to Oscillator Stable                                              | 0.01    | 0.05                   | 0.1     | μs    |

1. Output Clock Period Jitter specified at 133 MHz. The values for lower frequencies will be smaller UIPP. The typical value for 133 MHz is 95 ps and for 2.08 MHz the typical value is 1.54 ns.

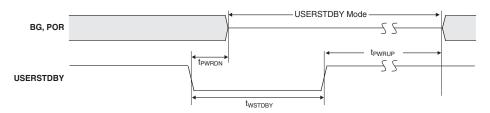

# MachXO2 Standby Mode Timing – HC/HE Devices

| Symbol              | Parameter                 | Device       | Min. | Тур. | Max | Units |

|---------------------|---------------------------|--------------|------|------|-----|-------|

| t <sub>PWRDN</sub>  | USERSTDBY High to Stop    | All          | _    | _    | 9   | ns    |

|                     |                           | LCMXO2-256   |      | _    |     | μs    |

|                     |                           | LCMXO2-640   |      | _    |     | μs    |

|                     |                           | LCMXO2-640U  |      | _    |     | μs    |

|                     |                           | LCMXO2-1200  | 20   | _    | 50  | μs    |

| t <sub>PWRUP</sub>  | USERSTDBY Low to Power Up | LCMXO2-1200U |      |      |     | μs    |

|                     |                           | LCMXO2-2000  |      | _    |     | μs    |

|                     |                           | LCMXO2-2000U |      | _    |     | μs    |

|                     |                           | LCMXO2-4000  |      | _    |     | μs    |

|                     |                           | LCMXO2-7000  |      | _    |     | μs    |

| t <sub>WSTDBY</sub> | USERSTDBY Pulse Width     | All          | 18   |      | —   | ns    |

## MachXO2 Standby Mode Timing – ZE Devices

| Symbol                  | Parameter                        | Device      | Min. | Тур. | Max | Units |

|-------------------------|----------------------------------|-------------|------|------|-----|-------|

| t <sub>PWRDN</sub>      | USERSTDBY High to Stop           | All         | _    | —    | 13  | ns    |

|                         |                                  | LCMXO2-256  |      | —    |     | μs    |

|                         |                                  | LCMXO2-640  |      | —    |     | μs    |

|                         | USERSTDBY Low to Power Up        | LCMXO2-1200 | 20   | —    | 50  | μs    |

| <sup>t</sup> PWRUP      |                                  | LCMXO2-2000 |      | —    |     | μs    |

|                         |                                  | LCMXO2-4000 |      | —    |     | μs    |

|                         |                                  | LCMXO2-7000 |      | _    |     | μs    |

| t <sub>WSTDBY</sub>     | USERSTDBY Pulse Width            | All         | 19   |      |     | ns    |

| t <sub>BNDGAPSTBL</sub> | USERSTDBY High to Bandgap Stable | All         |      | —    | 15  | ns    |

# MachXO2 Family Data Sheet Pinout Information

March 2017

Data Sheet DS1035

# **Signal Descriptions**

| Signal Name                              | I/O                         | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                          |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          |                             | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                          |                             | [Row/Column Number] indicates the PFU row or the column of the device on which the PIO Group exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                                                                                                                                                                                                                                                                                                                                                                |

|                                          |                             | [A/B/C/D] indicates the PIO within the group to which the pad is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P[Edge] [Row/Column<br>Number]_[A/B/C/D] | I/O                         | Some of these user-programmable pins are shared with special function pins. When not used as special function pins, these pins can be programmed as I/Os for user logic.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                          |                             | During configuration of the user-programmable I/Os, the user has an option to tri-state the I/Os and enable an internal pull-up, pull-down or buskeeper resistor. This option also applies to unused pins (or those not bonded to a package pin). The default during configuration is for user-programmable I/Os to be tri-stated with an internal pull-down resistor enabled. When the device is erased, I/Os will be tri-stated with an internal pull-down resistor enabled. Some pins, such as PROGRAMN and JTAG pins, default to tri-stated I/Os with pull-up resistors enabled when the device is erased. |

| NC                                       |                             | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND                                      |                             | GND – Ground. Dedicated pins. It is recommended that all GNDs are tied together.<br>For QFN 48 package, the exposed die pad is the device ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VCC                                      | _                           | $V_{CC}$ – The power supply pins for core logic. Dedicated pins. It is recommended that all VCCs are tied to the same supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCCIOx                                   |                             | VCCIO – The power supply pins for I/O Bank x. Dedicated pins. It is recommended that all VCCIOs located in the same bank are tied to the same supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PLL and Clock Function                   | ons (Us                     | ed as user-programmable I/O pins when not used for PLL or clock pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [LOC]_GPLL[T, C]_IN                      | _                           | Reference Clock (PLL) input pads: [LOC] indicates location. Valid designations are L (Left PLL) and R (Right PLL). T = true and C = complement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [LOC]_GPLL[T, C]_FB                      | _                           | Optional Feedback (PLL) input pads: [LOC] indicates location. Valid designations are L (Left PLL) and R (Right PLL). T = true and C = complement.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PCLK [n]_[2:0]                           | _                           | Primary Clock pads. One to three clock pads per side.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Test and Programming                     | <b>g</b> (Dual <sup>.</sup> | function pins used for test access port and during sysCONFIG™)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TMS                                      | I                           | Test Mode Select input pin, used to control the 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ТСК                                      | Ι                           | Test Clock input pin, used to clock the 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TDI                                      | Ι                           | Test Data input pin, used to load data into the device using an 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TDO                                      | 0                           | Output pin – Test Data output pin used to shift data out of the device using 1149.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                          |                             | Optionally controls behavior of TDI, TDO, TMS, TCK. If the device is configured to use the JTAG pins (TDI, TDO, TMS, TCK) as general purpose I/O, then:                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| JTAGENB                                  | Ι                           | If JTAGENB is low: TDI, TDO, TMS and TCK can function a general purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          |                             | If JTAGENB is high: TDI, TDO, TMS and TCK function as JTAG pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                          |                             | For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Configuration (Dual fu                   | nction p                    | ins used during sysCONFIG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PROGRAMN                                 | Ι                           | Initiates configuration sequence when asserted low. During configuration, or when reserved as PROGRAMN in user mode, this pin always has an active pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

|                                                            |          | M         | achXO2-120 | 00       |                     | MachXO2-1200U |

|------------------------------------------------------------|----------|-----------|------------|----------|---------------------|---------------|

|                                                            | 100 TQFP | 132 csBGA | 144 TQFP   | 25 WLCSP | 32 QFN <sup>1</sup> | 256 ftBGA     |

| General Purpose I/O per Bank                               | •        | •         |            |          |                     |               |

| Bank 0                                                     | 18       | 25        | 27         | 11       | 9                   | 50            |

| Bank 1                                                     | 21       | 26        | 26         | 0        | 2                   | 52            |

| Bank 2                                                     | 20       | 28        | 28         | 7        | 9                   | 52            |

| Bank 3                                                     | 20       | 25        | 26         | 0        | 2                   | 16            |

| Bank 4                                                     | 0        | 0         | 0          | 0        | 0                   | 16            |

| Bank 5                                                     | 0        | 0         | 0          | 0        | 0                   | 20            |

| Total General Purpose Single Ended I/O                     | 79       | 104       | 107        | 18       | 22                  | 206           |

| Differential I/O per Bank                                  |          |           |            |          |                     |               |

| Bank 0                                                     | 9        | 13        | 14         | 5        | 4                   | 25            |

| Bank 1                                                     | 10       | 13        | 13         | 0        | 1                   | 26            |

| Bank 2                                                     | 10       | 14        | 14         | 2        | 4                   | 26            |

| Bank 3                                                     | 10       | 12        | 13         | 0        | 1                   | 8             |

| Bank 4                                                     | 0        | 0         | 0          | 0        | 0                   | 8             |

| Bank 5                                                     | 0        | 0         | 0          | 0        | 0                   | 10            |

| Total General Purpose Differential I/O                     | 39       | 52        | 54         | 7        | 10                  | 103           |

| Dual Function I/O                                          | 31       | 33        | 33         | 18       | 22                  | 33            |

| High-speed Differential I/O                                |          |           |            |          |                     |               |

| Bank 0                                                     | 4        | 7         | 7          | 0        | 0                   | 14            |

| Gearboxes                                                  |          |           |            |          |                     |               |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0)  | 4        | 7         | 7          | 0        | 0                   | 14            |

| Number of 7:1 or 8:1 Input Gearbox Avail-<br>able (Bank 2) | 5        | 7         | 7          | 0        | 2                   | 14            |

| DQS Groups                                                 |          |           |            |          |                     |               |

| Bank 1                                                     | 1        | 2         | 2          | 0        | 0                   | 2             |

| VCCIO Pins                                                 |          |           |            |          |                     |               |

| Bank 0                                                     | 2        | 3         | 3          | 1        | 2                   | 4             |

| Bank 1                                                     | 2        | 3         | 3          | 0        | 1                   | 4             |

| Bank 2                                                     | 2        | 3         | 3          | 1        | 2                   | 4             |

| Bank 3                                                     | 3        | 3         | 3          | 0        | 1                   | 1             |

| Bank 4                                                     | 0        | 0         | 0          | 0        | 0                   | 2             |

| Bank 5                                                     | 0        | 0         | 0          | 0        | 0                   | 1             |

| VCC                                                        | 2        | 4         | 4          | 2        | 2                   | 8             |

| GND                                                        | 8        | 10        | 12         | 2        | 2                   | 24            |

| NC                                                         | 1        | 1         | 8          | 0        | 0                   | 1             |

| Reserved for Configuration                                 | 1        | 1         | 1          | 1        | 1                   | 1             |

| Total Count of Bonded Pins                                 | 100      | 132       | 144        | 25       | 32                  | 256           |

| 1. Lattice recommends soldering the centra                 |          |           |            |          |                     |               |

1. Lattice recommends soldering the central thermal pad onto the top PCB ground for improved thermal resistance.

|                                                           |             |             | MachX        | D2-2000     |              |              | MachXO2-2000U |

|-----------------------------------------------------------|-------------|-------------|--------------|-------------|--------------|--------------|---------------|

|                                                           | 49<br>WLCSP | 100<br>TQFP | 132<br>csBGA | 144<br>TQFP | 256<br>caBGA | 256<br>ftBGA | 484 ftBGA     |

| General Purpose I/O per Bank                              | •           |             | •            | •           | •            |              |               |

| Bank 0                                                    | 19          | 18          | 25           | 27          | 50           | 50           | 70            |

| Bank 1                                                    | 0           | 21          | 26           | 28          | 52           | 52           | 68            |

| Bank 2                                                    | 13          | 20          | 28           | 28          | 52           | 52           | 72            |

| Bank 3                                                    | 0           | 6           | 7            | 8           | 16           | 16           | 24            |

| Bank 4                                                    | 0           | 6           | 8            | 10          | 16           | 16           | 16            |

| Bank 5                                                    | 6           | 8           | 10           | 10          | 20           | 20           | 28            |

| Total General Purpose Single-Ended I/O                    | 38          | 79          | 104          | 111         | 206          | 206          | 278           |

| Differential I/O per Bank                                 |             |             |              |             |              |              |               |

| Bank 0                                                    | 7           | 9           | 13           | 14          | 25           | 25           | 35            |

| Bank 1                                                    | 0           | 10          | 13           | 14          | 26           | 26           | 34            |

| Bank 2                                                    | 6           | 10          | 14           | 14          | 26           | 26           | 36            |

| Bank 3                                                    | 0           | 3           | 3            | 4           | 8            | 8            | 12            |

| Bank 4                                                    | 0           | 3           | 4            | 5           | 8            | 8            | 8             |

| Bank 5                                                    | 3           | 4           | 5            | 5           | 10           | 10           | 14            |

| Total General Purpose Differential I/O                    | 16          | 39          | 52           | 56          | 103          | 103          | 139           |

| Dual Function I/O                                         | 24          | 31          | 33           | 33          | 33           | 33           | 37            |

| High-speed Differential I/O                               |             | -           |              |             |              |              | _             |

| Bank 0                                                    | 5           | 4           | 8            | 9           | 14           | 14           | 18            |

| Gearboxes                                                 | -           |             | _            | _           |              |              | -             |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 5           | 4           | 8            | 9           | 14           | 14           | 18            |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 6           | 10          | 14           | 14          | 14           | 14           | 18            |

| DQS Groups                                                |             |             |              |             |              |              |               |

| Bank 1                                                    | 0           | 1           | 2            | 2           | 2            | 2            | 2             |

| VCCIO Pins                                                |             |             |              |             |              |              |               |

| Bank 0                                                    | 2           | 2           | 3            | 3           | 4            | 4            | 10            |

| Bank 1                                                    | 0           | 2           | 3            | 3           | 4            | 4            | 10            |

| Bank 2                                                    | 1           | 2           | 3            | 3           | 4            | 4            | 10            |

| Bank 3                                                    | 0           | 1           | 1            | 1           | 1            | 1            | 3             |

| Bank 4                                                    | 0           | 1           | 1            | 1           | 2            | 2            | 4             |

| Bank 5                                                    | 1           | 1           | 1            | 1           | 1            | 1            | 3             |

|                                                           | 1           |             | I            | 1           | I            |              | T             |

| VCC                                                       | 2           | 2           | 4            | 4           | 8            | 8            | 12            |

| GND                                                       | 4           | 8           | 10           | 12          | 24           | 24           | 48            |

| NC                                                        | 0           | 1           | 1            | 4           | 1            | 1            | 105           |

| Reserved for Configuration                                | 1           | 1           | 1            | 1           | v            | 1            | 1             |

| Total Count of Bonded Pins                                | 39          | 100         | 132          | 144         | 256          | 256          | 484           |

## **For Further Information**

For further information regarding logic signal connections for various packages please refer to the MachXO2 Device Pinout Files.

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Users must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

### For Further Information

For further information regarding Thermal Management, refer to the following:

- Thermal Management document

- TN1198, Power Estimation and Management for MachXO2 Devices

- The Power Calculator tool is included with the Lattice design tools, or as a standalone download from www.latticesemi.com/software

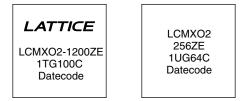

# **Ordering Information**

MachXO2 devices have top-side markings, for commercial and industrial grades, as shown below:

Notes:

- 1. Markings are abbreviated for small packages.

- 2. See PCN 05A-12 for information regarding a change to the top-side mark logo.

# Ultra Low Power Commercial Grade Devices, Halogen Free (RoHS) Packaging

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-256ZE-1SG32C  | 256  | 1.2 V          | -1    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256ZE-2SG32C  | 256  | 1.2 V          | -2    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256ZE-3SG32C  | 256  | 1.2 V          | -3    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256ZE-1UMG64C | 256  | 1.2 V          | -1    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256ZE-2UMG64C | 256  | 1.2 V          | -2    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256ZE-3UMG64C | 256  | 1.2 V          | -3    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256ZE-1TG100C | 256  | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256ZE-2TG100C | 256  | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256ZE-3TG100C | 256  | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256ZE-1MG132C | 256  | 1.2 V          | -1    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-256ZE-2MG132C | 256  | 1.2 V          | -2    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-256ZE-3MG132C | 256  | 1.2 V          | -3    | Halogen-Free csBGA | 132   | COM   |

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-640ZE-1TG100C | 640  | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640ZE-2TG100C | 640  | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640ZE-3TG100C | 640  | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640ZE-1MG132C | 640  | 1.2 V          | -1    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-640ZE-2MG132C | 640  | 1.2 V          | -2    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-640ZE-3MG132C | 640  | 1.2 V          | -3    | Halogen-Free csBGA | 132   | COM   |

| Part Number           | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|-----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200ZE-1SG32C  | 1280 | 1.2 V          | -1    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-1200ZE-2SG32C  | 1280 | 1.2 V          | -2    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-1200ZE-3SG32C  | 1280 | 1.2 V          | -3    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-1200ZE-1TG100C | 1280 | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200ZE-2TG100C | 1280 | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200ZE-3TG100C | 1280 | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200ZE-1MG132C | 1280 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200ZE-2MG132C | 1280 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200ZE-3MG132C | 1280 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200ZE-1TG144C | 1280 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200ZE-2TG144C | 1280 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200ZE-3TG144C | 1280 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | COM   |

# High-Performance Commercial Grade Devices without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100C  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-5TG100C  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-6TG100C  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-4TG144C  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-5TG144C  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-6TG144C  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-4MG132C  | 2112 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-5MG132C  | 2112 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-6MG132C  | 2112 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-4BG256C  | 2112 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-5BG256C  | 2112 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-6BG256C  | 2112 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-4FTG256C | 2112 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-5FTG256C | 2112 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-6FTG256C | 2112 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484C | 2112 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-5FG484C | 2112 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-6FG484C | 2112 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HE-4TG144C  | 4320 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-5TG144C  | 4320 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-6TG144C  | 4320 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-4MG132C  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-5MG132C  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-6MG132C  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-4BG256C  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4MG184C  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5MG184C  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-6MG184C  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5BG256C  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-6BG256C  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4FTG256C | 4320 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-5FTG256C | 4320 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-6FTG256C | 4320 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-4BG332C  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HE-5BG332C  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | COM   |

# High-Performance Industrial Grade Devices with Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-256HC-4SG32I  | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256HC-5SG32I  | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256HC-6SG32I  | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256HC-4SG48I  | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-256HC-5SG48I  | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-256HC-6SG48I  | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-256HC-4UMG64I | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256HC-5UMG64I | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256HC-6UMG64I | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256HC-4TG100I | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256HC-5TG100I | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256HC-6TG100I | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256HC-4MG132I | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-256HC-5MG132I | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-256HC-6MG132I | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-640HC-4SG48I  | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-640HC-5SG48I  | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-640HC-6SG48I  | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 48    | IND   |

| LCMXO2-640HC-4TG100I | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640HC-5TG100I | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640HC-6TG100I | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640HC-4MG132I | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-640HC-5MG132I | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-640HC-6MG132I | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| Part Number           | LUTs | Supply Voltage | Grade | Package           | Leads | Temp. |

|-----------------------|------|----------------|-------|-------------------|-------|-------|

| LCMXO2-640UHC-4TG144I | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP | 144   | IND   |

| LCMXO2-640UHC-5TG144I | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP | 144   | IND   |

| LCMXO2-640UHC-6TG144I | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP | 144   | IND   |

# MachXO2 Family Data Sheet Supplemental Information

#### April 2012

Data Sheet DS1035

### **For Further Information**

A variety of technical notes for the MachXO2 family are available on the Lattice web site.

- TN1198, Power Estimation and Management for MachXO2 Devices

- TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide

- TN1201, Memory Usage Guide for MachXO2 Devices

- TN1202, MachXO2 sysIO Usage Guide

- TN1203, Implementing High-Speed Interfaces with MachXO2 Devices

- TN1204, MachXO2 Programming and Configuration Usage Guide

- TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices

- TN1206, MachXO2 SRAM CRC Error Detection Usage Guide

- TN1207, Using TraceID in MachXO2 Devices

- TN1074, PCB Layout Recommendations for BGA Packages

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology

- AN8086, Designing for Migration from MachXO2-1200-R1 to Standard (non-R1) Devices