# E · / Fattice Semiconductor Corporation - <u>LCMX02-4000ZE-1BG256C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                           |

|--------------------------------|----------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 540                                                                              |

| Number of Logic Elements/Cells | 4320                                                                             |

| Total RAM Bits                 | 94208                                                                            |

| Number of I/O                  | 206                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                    |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                  |

| Package / Case                 | 256-LFBGA                                                                        |

| Supplier Device Package        | 256-CABGA (14x14)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-4000ze-1bg256c |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The logic blocks, Programmable Functional Unit (PFU) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each row has either the logic blocks or the EBR blocks. The PIO cells are located at the periphery of the device, arranged in banks. The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

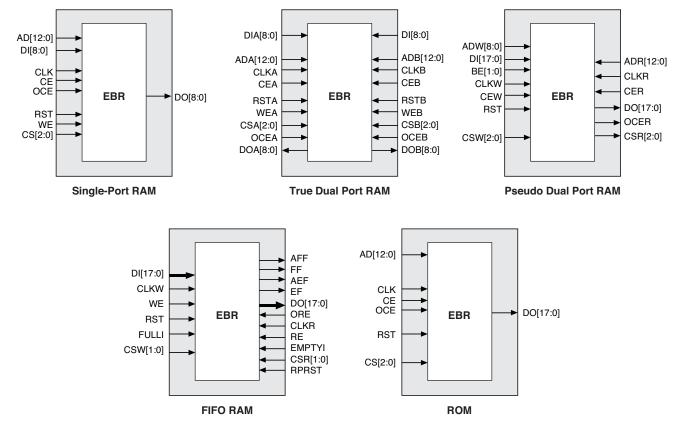

In the MachXO2 family, the number of sysIO banks varies by device. There are different types of I/O buffers on the different banks. Refer to the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks; these blocks are found in MachXO2-640/U and larger devices. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT usage.

The MachXO2 registers in PFU and sysl/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

The MachXO2 architecture also provides up to two sysCLOCK Phase Locked Loop (PLL) blocks on MachXO2-640U, MachXO2-1200/U and larger devices. These blocks are located at the ends of the on-chip Flash block. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

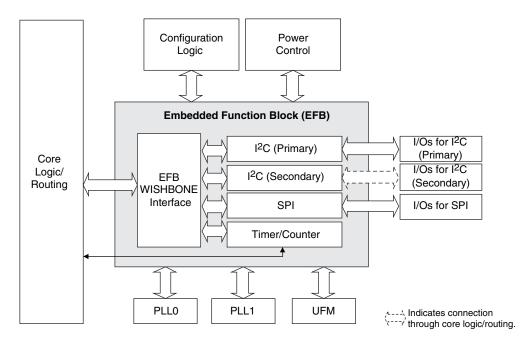

MachXO2 devices provide commonly used hardened functions such as SPI controller, I<sup>2</sup>C controller and timer/ counter. MachXO2-640/U and higher density devices also provide User Flash Memory (UFM). These hardened functions and the UFM interface to the core logic and routing through a WISHBONE interface. The UFM can also be accessed through the SPI, I<sup>2</sup>C and JTAG ports.

Every device in the family has a JTAG port that supports programming and configuration of the device as well as access to the user logic. The MachXO2 devices are available for operation from 3.3 V, 2.5 V and 1.2 V power supplies, providing easy integration into the overall system.

## **PFU Blocks**

The core of the MachXO2 device consists of PFU blocks, which can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. Each PFU block consists of four interconnected slices numbered 0 to 3 as shown in Figure 2-3. Each slice contains two LUTs and two registers. There are 53 inputs and 25 outputs associated with each PFU block.

## Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In Ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/down counter with asynchronous clear

- Up/down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per-slice basis to allow fast arithmetic functions to be constructed by concatenating slices.

## **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed by using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals.

MachXO2 devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in MachXO2 devices, please see TN1201, Memory Usage Guide for MachXO2 Devices.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                                                          | SPR 16x4 | PDPR 16x4 |  |  |  |  |  |

|----------------------------------------------------------|----------|-----------|--|--|--|--|--|

| Number of slices                                         | 3        | 3         |  |  |  |  |  |

| Note: SPB = Single Port BAM, PDPB = Pseudo Dual Port BAM |          |           |  |  |  |  |  |

ote: SPR = Single Port RAM, PDPR = Pseudo Dual

## **ROM Mode**

ROM mode uses the LUT logic; hence, slices 0-3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information on the RAM and ROM modes, please refer to TN1201, Memory Usage Guide for MachXO2 Devices.

## Routing

There are many resources provided in the MachXO2 devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with three different types of routing resources: x1 (spans two PFUs), x2 (spans three PFUs) and x6 (spans seven PFUs). The x1, x2, and x6 connections provide fast and efficient connections in the horizontal and vertical directions.

The design tools take the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock/Control Distribution Network**

Each MachXO2 device has eight clock inputs (PCLK [T, C] [Banknum]\_[2..0]) – three pins on the left side, two pins each on the bottom and top sides and one pin on the right side. These clock inputs drive the clock nets. These eight inputs can be differential or single-ended and may be used as general purpose I/O if they are not used to drive the clock nets. When using a single ended clock input, only the PCLKT input can drive the clock tree directly.

The MachXO2 architecture has three types of clocking resources: edge clocks, primary clocks and secondary high fanout nets. MachXO2-640U, MachXO2-1200/U and higher density devices have two edge clocks each on the top and bottom edges. Lower density devices have no edge clocks. Edge clocks are used to clock I/O registers and have low injection time and skew. Edge clock inputs are from PLL outputs, primary clock pads, edge clock bridge outputs and CIB sources.

The eight primary clock lines in the primary clock network drive throughout the entire device and can provide clocks for all resources within the device including PFUs, EBRs and PICs. In addition to the primary clock signals, MachXO2 devices also have eight secondary high fanout signals which can be used for global control signals, such as clock enables, synchronous or asynchronous clears, presets, output enables, etc. Internal logic can drive the global clock network for internally-generated global clocks and control signals.

The maximum frequency for the primary clock network is shown in the MachXO2 External Switching Characteristics table.

The primary clock signals for the MachXO2-256 and MachXO2-640 are generated from eight 17:1 muxes The available clock sources include eight I/O sources and 9 routing inputs. Primary clock signals for the MachXO2-640U, MachXO2-1200/U and larger devices are generated from eight 27:1 muxes The available clock sources include eight I/O sources, 11 routing inputs, eight clock divider inputs and up to eight sysCLOCK PLL outputs.

#### Figure 2-8. sysMEM Memory Primitives

#### Table 2-6. EBR Signal Descriptions

| Port Name        | Description                 | Active State      |

|------------------|-----------------------------|-------------------|

| CLK              | Clock                       | Rising Clock Edge |

| CE               | Clock Enable                | Active High       |

| OCE <sup>1</sup> | Output Clock Enable         | Active High       |

| RST              | Reset                       | Active High       |

| BE <sup>1</sup>  | Byte Enable                 | Active High       |

| WE               | Write Enable                | Active High       |

| AD               | Address Bus                 | —                 |

| DI               | Data In                     | —                 |

| DO               | Data Out                    | —                 |

| CS               | Chip Select                 | Active High       |

| AFF              | FIFO RAM Almost Full Flag   | —                 |

| FF               | FIFO RAM Full Flag          | —                 |

| AEF              | FIFO RAM Almost Empty Flag  | —                 |

| EF               | FIFO RAM Empty Flag         | —                 |

| RPRST            | FIFO RAM Read Pointer Reset | —                 |

1. Optional signals.

2. For dual port EBR primitives a trailing 'A' or 'B' in the signal name specifies the EBR port A or port B respectively.

3. For FIFO RAM mode primitive, a trailing 'R' or 'W' in the signal name specifies the FIFO read port or write port respectively.

4. For FIFO RAM mode primitive FULLI has the same function as CSW(2) and EMPTYI has the same function as CSR(2).

5. In FIFO mode, CLKW is the write port clock, CSW is the write port chip select, CLKR is the read port clock, CSR is the read port chip select, ORE is the output read enable.

### Figure 2-20. Embedded Function Block Interface

## Hardened I<sup>2</sup>C IP Core

Every MachXO2 device contains two I<sup>2</sup>C IP cores. These are the primary and secondary I<sup>2</sup>C IP cores. Either of the two cores can be configured either as an I<sup>2</sup>C master or as an I<sup>2</sup>C slave. The only difference between the two IP cores is that the primary core has pre-assigned I/O pins whereas users can assign I/O pins for the secondary core.

When the IP core is configured as a master it will be able to control other devices on the  $I^2C$  bus through the interface. When the core is configured as the slave, the device will be able to provide I/O expansion to an  $I^2C$  Master. The  $I^2C$  cores support the following functionality:

- Master and Slave operation

- 7-bit and 10-bit addressing

- Multi-master arbitration support

- Up to 400 kHz data transfer speed

- General call support

- Interface to custom logic through 8-bit WISHBONE interface

When implementing background programming of the on-chip Flash, care must be taken for the operation of the PLL. For devices that have two PLLs (XO2-2000U, -4000 and -7000), the system must put the RPLL (Right-side PLL) in reset state during the background Flash programming. More detailed description can be found in TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Security and One-Time Programmable Mode (OTP)

For applications where security is important, the lack of an external bitstream provides a solution that is inherently more secure than SRAM-based FPGAs. This is further enhanced by device locking. MachXO2 devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile Flash memory spaces. The device can be in one of two modes:

- 1. Unlocked Readback of the SRAM configuration and non-volatile Flash memory spaces is allowed.

- 2. Permanently Locked The device is permanently locked.

Once set, the only way to clear the security bits is to erase the device. To further complement the security of the device, a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the Flash and SRAM OTP portions of the device. For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Dual Boot

MachXO2 devices can optionally boot from two patterns, a primary bitstream and a golden bitstream. If the primary bitstream is found to be corrupt while being downloaded into the SRAM, the device shall then automatically re-boot from the golden bitstream. Note that the primary bitstream must reside in the on-chip Flash. The golden image MUST reside in an external SPI Flash. For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Soft Error Detection

The SED feature is a CRC check of the SRAM cells after the device is configured. This check ensures that the SRAM cells were configured successfully. This feature is enabled by a configuration bit option. The Soft Error Detection can also be initiated in user mode via an input to the fabric. The clock for the Soft Error Detection circuit is generated using a dedicated divider. The undivided clock from the on-chip oscillator is the input to this divider. For low power applications users can switch off the Soft Error Detection circuit. For more details, refer to TN1206, MachXO2 Soft Error Detection Usage Guide.

## TraceID

Each MachXO2 device contains a unique (per device), TraceID that can be used for tracking purposes or for IP security applications. The TraceID is 64 bits long. Eight out of 64 bits are user-programmable, the remaining 56 bits are factory-programmed. The TraceID is accessible through the EFB WISHBONE interface and can also be accessed through the SPI, I<sup>2</sup>C, or JTAG interfaces.

## **Density Shifting**

The MachXO2 family has been designed to enable density migration within the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case. When migrating from lower to higher density or higher to lower density, ensure to review all the power supplies and NC pins of the chosen devices. For more details refer to the MachXO2 migration files.

# sysIO Recommended Operating Conditions

|                        |       | V <sub>CCIO</sub> (V) |       |       | V <sub>REF</sub> (V) |       |

|------------------------|-------|-----------------------|-------|-------|----------------------|-------|

| Standard               | Min.  | Тур.                  | Max.  | Min.  | Тур.                 | Max.  |

| LVCMOS 3.3             | 3.135 | 3.3                   | 3.6   | —     | —                    | —     |

| LVCMOS 2.5             | 2.375 | 2.5                   | 2.625 | —     | —                    | —     |

| LVCMOS 1.8             | 1.71  | 1.8                   | 1.89  | —     | —                    | —     |

| LVCMOS 1.5             | 1.425 | 1.5                   | 1.575 | —     | —                    | —     |

| LVCMOS 1.2             | 1.14  | 1.2                   | 1.26  | —     | —                    | _     |

| LVTTL                  | 3.135 | 3.3                   | 3.6   | —     | —                    | —     |

| PCI <sup>3</sup>       | 3.135 | 3.3                   | 3.6   | —     | —                    | —     |

| SSTL25                 | 2.375 | 2.5                   | 2.625 | 1.15  | 1.25                 | 1.35  |

| SSTL18                 | 1.71  | 1.8                   | 1.89  | 0.833 | 0.9                  | 0.969 |

| HSTL18                 | 1.71  | 1.8                   | 1.89  | 0.816 | 0.9                  | 1.08  |

| LVCMOS25R33            | 3.135 | 3.3                   | 3.6   | 1.1   | 1.25                 | 1.4   |

| LVCMOS18R33            | 3.135 | 3.3                   | 3.6   | 0.75  | 0.9                  | 1.05  |

| LVCMOS18R25            | 2.375 | 2.5                   | 2.625 | 0.75  | 0.9                  | 1.05  |

| LVCMOS15R33            | 3.135 | 3.3                   | 3.6   | 0.6   | 0.75                 | 0.9   |

| LVCMOS15R25            | 2.375 | 2.5                   | 2.625 | 0.6   | 0.75                 | 0.9   |

| LVCMOS12R334           | 3.135 | 3.3                   | 3.6   | 0.45  | 0.6                  | 0.75  |

| LVCMOS12R254           | 2.375 | 2.5                   | 2.625 | 0.45  | 0.6                  | 0.75  |

| LVCMOS10R334           | 3.135 | 3.3                   | 3.6   | 0.35  | 0.5                  | 0.65  |

| LVCMOS10R254           | 2.375 | 2.5                   | 2.625 | 0.35  | 0.5                  | 0.65  |

| LVDS25 <sup>1, 2</sup> | 2.375 | 2.5                   | 2.625 | —     | —                    | _     |

| LVDS33 <sup>1, 2</sup> | 3.135 | 3.3                   | 3.6   | —     | —                    | —     |

| LVPECL <sup>1</sup>    | 3.135 | 3.3                   | 3.6   | —     | —                    | —     |

| BLVDS <sup>1</sup>     | 2.375 | 2.5                   | 2.625 | —     | —                    | —     |

| RSDS <sup>1</sup>      | 2.375 | 2.5                   | 2.625 | —     | —                    | —     |

| SSTL18D                | 1.71  | 1.8                   | 1.89  | —     | —                    | —     |

| SSTL25D                | 2.375 | 2.5                   | 2.625 | —     | —                    |       |

| HSTL18D                | 1.71  | 1.8                   | 1.89  | —     | —                    | —     |

1. Inputs on-chip. Outputs are implemented with the addition of external resistors.

2. MachXO2-640U, MachXO2-1200/U and larger devices have dedicated LVDS buffers.

3. Input on the bottom bank of the MachXO2-640U, MachXO2-1200/U and larger devices only.

4. Supported only for inputs and BIDIs for all ZE devices, and -6 speed grade for HE and HC devices.

# sysIO Single-Ended DC Electrical Characteristics<sup>1, 2</sup>

| Input/Output    | V                     | / <sub>IL</sub>          | V <sub>I</sub>           | н        | V <sub>OL</sub> Max. | V <sub>OH</sub> Min.     | l <sub>OL</sub> Max.⁴ | I <sub>OH</sub> Max.⁴ |

|-----------------|-----------------------|--------------------------|--------------------------|----------|----------------------|--------------------------|-----------------------|-----------------------|

| Standard        | Min. (V) <sup>3</sup> | Max. (V)                 | Min. (V)                 | Max. (V) | (V)                  | (V)                      | (mA)                  | (mA)                  |

|                 |                       |                          |                          |          |                      |                          | 4                     | -4                    |

|                 |                       |                          |                          |          |                      |                          | 8                     | -8                    |

| LVCMOS 3.3      | -0.3                  | 0.8                      | 2.0                      | 3.6      | 0.4                  | $V_{CCIO} - 0.4$         | 12                    | -12                   |

| LVTTL           | 0.0                   | 0.0                      | 2.0                      | 0.0      |                      |                          | 16                    | -16                   |

|                 |                       |                          |                          |          |                      |                          | 24                    | -24                   |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> – 0.2  | 0.1                   | -0.1                  |

|                 |                       |                          |                          |          |                      |                          | 4                     | -4                    |

|                 |                       |                          |                          |          | 0.4                  | V <sub>CCIO</sub> – 0.4  | 8                     | -8                    |

| LVCMOS 2.5      | -0.3                  | 0.7                      | 1.7                      | 3.6      | 0.4                  | VCCIO 0.4                | 12                    | -12                   |

|                 |                       |                          |                          |          |                      |                          | 16                    | -16                   |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> – 0.2  | 0.1                   | -0.1                  |

|                 |                       |                          |                          |          |                      |                          | 4                     | -4                    |

| LVCMOS 1.8      | -0.3                  | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | $V_{CCIO} - 0.4$         | 8                     | -8                    |

|                 | -0.3                  | 0.33 v CCIO              | 0.03 v CCIO              | 5.0      |                      |                          | 12                    | -12                   |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> – 0.2  | 0.1                   | -0.1                  |

|                 |                       |                          | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | V <sub>CCIO</sub> – 0.4  | 4                     | -4                    |

| LVCMOS 1.5      | -0.3                  | 0.35V <sub>CCIO</sub>    |                          |          |                      | VCCIO - 0.4              | 8                     | -8                    |

|                 |                       |                          |                          |          | 0.2                  | V <sub>CCIO</sub> – 0.2  | 0.1                   | -0.1                  |

|                 | -0.3                  | 0.35V <sub>CCIO</sub>    | 0.65V <sub>CCIO</sub>    | 3.6      | 0.4                  | V <sub>CCIO</sub> – 0.4  | 4                     | -2                    |

| LVCMOS 1.2      |                       |                          |                          |          | 0.1                  |                          | 8                     | -6                    |

|                 |                       |                          |                          |          | 0.2                  | $V_{CCIO} - 0.2$         | 0.1                   | -0.1                  |

| PCI             | -0.3                  | 0.3V <sub>CCIO</sub>     | 0.5V <sub>CCIO</sub>     | 3.6      | 0.1V <sub>CCIO</sub> | 0.9V <sub>CCIO</sub>     | 1.5                   | -0.5                  |

| SSTL25 Class I  | -0.3                  | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | 0.54                 | V <sub>CCIO</sub> - 0.62 | 8                     | 8                     |

| SSTL25 Class II | -0.3                  | V <sub>REF</sub> - 0.18  | V <sub>REF</sub> + 0.18  | 3.6      | NA                   | NA                       | NA                    | NA                    |

| SSTL18 Class I  | -0.3                  | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | 0.40                 | V <sub>CCIO</sub> - 0.40 | 8                     | 8                     |

| SSTL18 Class II | -0.3                  | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | 3.6      | NA                   | NA                       | NA                    | NA                    |

| HSTL18 Class I  | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.40                 | V <sub>CCIO</sub> - 0.40 | 8                     | 8                     |

| HSTL18 Class II | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                    | NA                    |

| LVCMOS25R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                    | NA                    |

| LVCMOS18R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                    | NA                    |

| LVCMOS18R25     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                    | NA                    |

| LVCMOS15R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                    | NA                    |

| LVCMOS15R25     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | NA                   | NA                       | NA                    | NA                    |

| LVCMOS12R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.40                 | NA Open<br>Drain         | 24, 16, 12,<br>8, 4   | NA Open<br>Drain      |

| LVCMOS12R25     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.40                 | NA Open<br>Drain         | 16, 12, 8, 4          | NA Open<br>Drain      |

| LVCMOS10R33     | -0.3                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | 3.6      | 0.40                 | NA Open<br>Drain         | 24, 16, 12,<br>8, 4   | NA Open<br>Drain      |

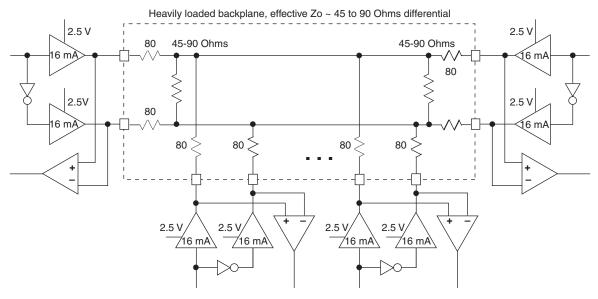

## BLVDS

The MachXO2 family supports the BLVDS standard through emulation. The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs. The input standard is supported by the LVDS differential input buffer. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

## Figure 3-2. BLVDS Multi-point Output Example

#### Table 3-2. BLVDS DC Conditions<sup>1</sup>

| <b>Over Recommended</b> | Operating | Conditions  |

|-------------------------|-----------|-------------|

|                         | oporating | 00110110110 |

|                     |                             | No      |         |       |  |

|---------------------|-----------------------------|---------|---------|-------|--|

| Symbol              | Description                 | Zo = 45 | Zo = 90 | Units |  |

| Z <sub>OUT</sub>    | Output impedance            | 20      | 20      | Ohms  |  |

| R <sub>S</sub>      | Driver series resistance    | 80      | 80      | Ohms  |  |

| R <sub>TLEFT</sub>  | Left end termination        | 45      | 90      | Ohms  |  |

| R <sub>TRIGHT</sub> | Right end termination       | 45      | 90      | Ohms  |  |

| V <sub>OH</sub>     | Output high voltage         | 1.376   | 1.480   | V     |  |

| V <sub>OL</sub>     | Output low voltage          | 1.124   | 1.020   | V     |  |

| V <sub>OD</sub>     | Output differential voltage | 0.253   | 0.459   | V     |  |

| V <sub>CM</sub>     | Output common mode voltage  | 1.250   | 1.250   | V     |  |

| I <sub>DC</sub>     | DC output current           | 11.236  | 10.204  | mA    |  |

1. For input buffer, see LVDS table.

## RSDS

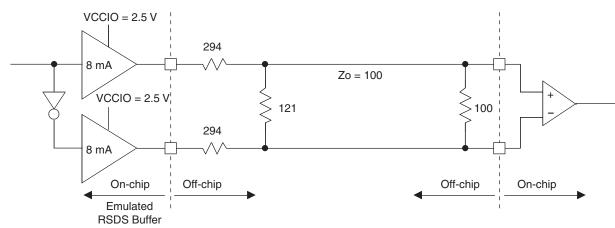

The MachXO2 family supports the differential RSDS standard. The output standard is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all the devices. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Use LVDS25E mode with suggested resistors for RSDS operation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

## Figure 3-4. RSDS (Reduced Swing Differential Standard)

#### Table 3-4. RSDS DC Conditions

| Parameter         | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20      | Ohms  |

| R <sub>S</sub>    | Driver series resistor      | 294     | Ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 121     | Ohms  |

| R <sub>T</sub>    | Receiver termination        | 100     | Ohms  |

| V <sub>OH</sub>   | Output high voltage         | 1.35    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.15    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.20    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25    | V     |

| Z <sub>BACK</sub> | Back impedance              | 101.5   | Ohms  |

| IDC               | DC output current           | 3.66    | mA    |

## Maximum sysIO Buffer Performance

| I/O Standard | Max. Speed | Units |

|--------------|------------|-------|

| LVDS25       | 400        | MHz   |

| LVDS25E      | 150        | MHz   |

| RSDS25       | 150        | MHz   |

| RSDS25E      | 150        | MHz   |

| BLVDS25      | 150        | MHz   |

| BLVDS25E     | 150        | MHz   |

| MLVDS25      | 150        | MHz   |

| MLVDS25E     | 150        | MHz   |

| LVPECL33     | 150        | MHz   |

| LVPECL33E    | 150        | MHz   |

| SSTL25_I     | 150        | MHz   |

| SSTL25_II    | 150        | MHz   |

| SSTL25D_I    | 150        | MHz   |

| SSTL25D_II   | 150        | MHz   |

| SSTL18_I     | 150        | MHz   |

| SSTL18_II    | 150        | MHz   |

| SSTL18D_I    | 150        | MHz   |

| SSTL18D_II   | 150        | MHz   |

| HSTL18_I     | 150        | MHz   |

| HSTL18_II    | 150        | MHz   |

| HSTL18D_I    | 150        | MHz   |

| HSTL18D_II   | 150        | MHz   |

| PCI33        | 134        | MHz   |

| LVTTL33      | 150        | MHz   |

| LVTTL33D     | 150        | MHz   |

| LVCMOS33     | 150        | MHz   |

| LVCMOS33D    | 150        | MHz   |

| LVCMOS25     | 150        | MHz   |

| LVCMOS25D    | 150        | MHz   |

| LVCMOS25R33  | 150        | MHz   |

| LVCMOS18     | 150        | MHz   |

| LVCMOS18D    | 150        | MHz   |

| LVCMOS18R33  | 150        | MHz   |

| LVCMOS18R25  | 150        | MHz   |

| LVCMOS15     | 150        | MHz   |

| LVCMOS15D    | 150        | MHz   |

| LVCMOS15R33  | 150        | MHz   |

| LVCMOS15R25  | 150        | MHz   |

| LVCMOS12     | 91         | MHz   |

| LVCMOS12D    | 91         | MHz   |

# MachXO2 External Switching Characteristics – HC/HE Devices<sup>1, 2, 3, 4, 5, 6, 7</sup>

|                                    |                                               |                                    | -     | 6    | _     | 5    | -4    |      | 7     |

|------------------------------------|-----------------------------------------------|------------------------------------|-------|------|-------|------|-------|------|-------|

| Parameter                          | Description                                   | Device                             | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| Clocks                             |                                               |                                    |       |      |       |      |       |      |       |

| Primary Clo                        | ocks                                          |                                    |       |      |       |      |       |      |       |

| f <sub>MAX_PRI</sub> <sup>8</sup>  | Frequency for Primary Clock<br>Tree           | All MachXO2 devices                |       | 388  | _     | 323  |       | 269  | MHz   |

| t <sub>W_PRI</sub>                 | Clock Pulse Width for Primary<br>Clock        | All MachXO2 devices                | 0.5   |      | 0.6   |      | 0.7   |      | ns    |

|                                    |                                               | MachXO2-256HC-HE                   | _     | 912  | —     | 939  | —     | 975  | ps    |

|                                    |                                               | MachXO2-640HC-HE                   |       | 844  |       | 871  |       | 908  | ps    |

|                                    | Primary Clock Skew Within a                   | MachXO2-1200HC-HE                  |       | 868  |       | 902  |       | 951  | ps    |

| <sup>t</sup> SKEW_PRI              | Device                                        | MachXO2-2000HC-HE                  |       | 867  |       | 897  |       | 941  | ps    |

|                                    |                                               | MachXO2-4000HC-HE                  |       | 865  | —     | 892  |       | 931  | ps    |

|                                    |                                               | MachXO2-7000HC-HE                  | —     | 902  | —     | 942  | —     | 989  | ps    |

| Edge Clock                         | 1                                             | 1                                  |       |      | I.    |      | 1     |      | L     |

| f <sub>MAX_EDGE</sub> <sup>8</sup> | Frequency for Edge Clock                      | MachXO2-1200 and<br>larger devices | _     | 400  | _     | 333  | _     | 278  | MHz   |

| Pin-LUT-Pin                        | Propagation Delay                             |                                    |       |      |       |      |       |      |       |

| t <sub>PD</sub>                    | Best case propagation delay through one LUT-4 | All MachXO2 devices                | _     | 6.72 | _     | 6.96 | _     | 7.24 | ns    |

| General I/O                        | Pin Parameters (Using Primar                  | y Clock without PLL)               |       |      |       |      | 1     |      |       |

|                                    |                                               | MachXO2-256HC-HE                   | _     | 7.13 | —     | 7.30 |       | 7.57 | ns    |

|                                    |                                               | MachXO2-640HC-HE                   |       | 7.15 | —     | 7.30 |       | 7.57 | ns    |

|                                    | Clock to Output – PIO Output                  | MachXO2-1200HC-HE                  | _     | 7.44 | —     | 7.64 | —     | 7.94 | ns    |

| t <sub>CO</sub>                    | Register                                      | MachXO2-2000HC-HE                  | _     | 7.46 | —     | 7.66 | —     | 7.96 | ns    |

|                                    |                                               | MachXO2-4000HC-HE                  |       | 7.51 | —     | 7.71 |       | 8.01 | ns    |

|                                    |                                               | MachXO2-7000HC-HE                  | _     | 7.54 | —     | 7.75 | —     | 8.06 | ns    |

|                                    |                                               | MachXO2-256HC-HE                   | -0.06 | _    | -0.06 |      | -0.06 |      | ns    |

|                                    |                                               | MachXO2-640HC-HE                   | -0.06 | _    | -0.06 | _    | -0.06 | _    | ns    |

|                                    | Clock to Data Setup – PIO                     | MachXO2-1200HC-HE                  | -0.17 | _    | -0.17 |      | -0.17 |      | ns    |

| t <sub>SU</sub>                    | Input Register                                | MachXO2-2000HC-HE                  | -0.20 | _    | -0.20 |      | -0.20 |      | ns    |

|                                    |                                               | MachXO2-4000HC-HE                  | -0.23 | _    | -0.23 | _    | -0.23 | _    | ns    |

|                                    |                                               | MachXO2-7000HC-HE                  | -0.23 | —    | -0.23 | _    | -0.23 | —    | ns    |

|                                    |                                               | MachXO2-256HC-HE                   | 1.75  | _    | 1.95  | _    | 2.16  | —    | ns    |

|                                    |                                               | MachXO2-640HC-HE                   | 1.75  | —    | 1.95  | —    | 2.16  | _    | ns    |

|                                    | Clock to Data Hold – PIO Input                | MachXO2-1200HC-HE                  | 1.88  | _    | 2.12  |      | 2.36  | _    | ns    |

| t <sub>H</sub>                     | Register                                      | MachXO2-2000HC-HE                  | 1.89  | _    | 2.13  | _    | 2.37  | _    | ns    |

|                                    |                                               | MachXO2-4000HC-HE                  | 1.94  | —    | 2.18  | _    | 2.43  | _    | ns    |

|                                    |                                               | MachXO2-7000HC-HE                  | 1.98  | _    | 2.23  | —    | 2.49  | —    | ns    |

**Over Recommended Operating Conditions**

|                    |                                                                  |                                                         | _       | -3       | _         | 2      | _       | -1      |                        |

|--------------------|------------------------------------------------------------------|---------------------------------------------------------|---------|----------|-----------|--------|---------|---------|------------------------|

| Parameter          | Description                                                      | Device                                                  | Min.    | Max.     | Min.      | Max.   | Min.    | Max.    | Units                  |

| Generic DDR        | 2 Outputs with Clock and Data C                                  | Centered at Pin Using P                                 | CLK Pin | for Cloc | k Input – | GDDRX  | 2_TX.EC | CLK.Cen | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>   | Output Data Valid Before CLK<br>Output                           |                                                         | 1.445   | _        | 1.760     | _      | 2.140   | _       | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                           | 1.445   | _        | 1.760     | _      | 2.140   | _       | ns                     |

| f <sub>DATA</sub>  | DDRX2 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,<br>top side only  | _       | 280      |           | 234    | _       | 194     | Mbps                   |

| f <sub>DDRX2</sub> | DDRX2 ECLK Frequency<br>(minimum limited by PLL)                 |                                                         | _       | 140      |           | 117    | _       | 97      | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                         |         | 70       | _         | 59     | —       | 49      | MHz                    |

| Generic DDR        | X4 Outputs with Clock and Data                                   | Aligned at Pin Using P                                  | CLK Pin | for Cloc | k Input   | - GDDR | X4_TX.E | CLK.Ali | gned <sup>9, 12</sup>  |

| t <sub>DIA</sub>   | Output Data Invalid After CLK<br>Output                          |                                                         | _       | 0.270    | _         | 0.300  | _       | 0.330   | ns                     |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                         | MachXO2-640U,<br>MachXO2-1200/U                         | _       | 0.270    |           | 0.300  | _       | 0.330   | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Output Data<br>Speed                                | and larger devices,<br>top side only                    | _       | 420      |           | 352    | _       | 292     | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency                                             |                                                         |         | 210      | _         | 176    |         | 146     | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                         |         | 53       |           | 44     | —       | 37      | MHz                    |

| Generic DDR        | 4 Outputs with Clock and Data C                                  | entered at Pin Using P                                  | CLK Pin | for Cloc | k Input – | GDDRX  | 4_TX.EC | LK.Cen  | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>   | Output Data Valid Before CLK<br>Output                           |                                                         | 0.873   | _        | 1.067     | _      | 1.319   | _       | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                           | 0.873   |          | 1.067     | _      | 1.319   | _       | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,<br>top side only  | _       | 420      |           | 352    | _       | 292     | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency<br>(minimum limited by PLL)                 |                                                         | _       | 210      |           | 176    | _       | 146     | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                         |         | 53       | _         | 44     | —       | 37      | MHz                    |

| 7:1 LVDS Out       | tputs – GDDR71_TX.ECLK.7:1 <sup>s</sup>                          | , 12                                                    |         |          |           |        |         |         |                        |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                         |                                                         | _       | 0.240    | _         | 0.270  | _       | 0.300   | ns                     |

| t <sub>DIA</sub>   | Output Data Invalid After CLK<br>Output                          | MachXO2-640U,                                           | _       | 0.240    |           | 0.270  | _       | 0.300   | ns                     |

| f <sub>DATA</sub>  | DDR71 Serial Output Data<br>Speed                                | MachXO2-1200/U<br>and larger devices,<br>top side only. | _       | 420      | _         | 352    | _       | 292     | Mbps                   |

| f <sub>DDR71</sub> | DDR71 ECLK Frequency                                             |                                                         |         | 210      | _         | 176    |         | 146     | MHz                    |

| fclkout            | 7:1 Output Clock Frequency<br>(SCLK) (minimum limited by<br>PLL) |                                                         | _       | 60       | _         | 50     | _       | 42      | MHz                    |

# sysCLOCK PLL Timing

| Parameter                         | Descriptions                                   | Conditions                              | Min.   | Max.  | Units  |

|-----------------------------------|------------------------------------------------|-----------------------------------------|--------|-------|--------|

| f <sub>IN</sub>                   | Input Clock Frequency (CLKI, CLKFB)            |                                         | 7      | 400   | MHz    |

| fout                              | Output Clock Frequency (CLKOP, CLKOS, CLKOS2)  |                                         | 1.5625 | 400   | MHz    |

| fout2                             | Output Frequency (CLKOS3 cascaded from CLKOS2) |                                         | 0.0122 | 400   | MHz    |

| f <sub>VCO</sub>                  | PLL VCO Frequency                              |                                         | 200    | 800   | MHz    |

| f <sub>PFD</sub>                  | Phase Detector Input Frequency                 |                                         | 7      | 400   | MHz    |

| AC Characteri                     | stics                                          | •                                       |        |       |        |

| t <sub>DT</sub>                   | Output Clock Duty Cycle                        | Without duty trim selected <sup>3</sup> | 45     | 55    | %      |

| t <sub>DT_TRIM</sub> <sup>7</sup> | Edge Duty Trim Accuracy                        |                                         | -75    | 75    | %      |

| t <sub>PH</sub> ⁴                 | Output Phase Accuracy                          |                                         | -6     | 6     | %      |

|                                   | Output Clock Pariad littar                     | f <sub>OUT</sub> > 100 MHz              | —      | 150   | ps p-p |

|                                   | Output Clock Period Jitter                     | f <sub>OUT</sub> < 100 MHz              | _      | 0.007 | UIPP   |

|                                   | Output Olaski Ousla ta susla littari           | f <sub>OUT</sub> > 100 MHz              | _      | 180   | ps p-p |

|                                   | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> < 100 MHz              | —      | 0.009 | UIPP   |

| . 18                              | Outrast Olaska Dhasan Jittari                  | f <sub>PFD</sub> > 100 MHz              | —      | 160   | ps p-p |

| t <sub>OPJIT</sub> <sup>1,8</sup> | Output Clock Phase Jitter                      | f <sub>PFD</sub> < 100 MHz              | —      | 0.011 | UIPP   |

|                                   | Output Cleak Daviad Littar (Eractional N)      | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p |

|                                   | Output Clock Period Jitter (Fractional-N)      | f <sub>OUT</sub> < 100 MHz              | _      | 0.12  | UIPP   |

|                                   | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p |

|                                   | (Fractional-N)                                 | f <sub>OUT</sub> < 100 MHz              | _      | 0.12  | UIPP   |

| t <sub>SPO</sub>                  | Static Phase Offset                            | Divider ratio = integer                 | -120   | 120   | ps     |

| t <sub>W</sub>                    | Output Clock Pulse Width                       | At 90% or 10% <sup>3</sup>              | 0.9    | —     | ns     |

| tLOCK <sup>2, 5</sup>             | PLL Lock-in Time                               |                                         | _      | 15    | ms     |

| t <sub>UNLOCK</sub>               | PLL Unlock Time                                |                                         | _      | 50    | ns     |

| <b>•</b> 6                        | Innut Clask Daviad Littar                      | f <sub>PFD</sub> ≥ 20 MHz               | —      | 1,000 | ps p-p |

| t <sub>IPJIT</sub> <sup>6</sup>   | Input Clock Period Jitter                      | f <sub>PFD</sub> < 20 MHz               | —      | 0.02  | UIPP   |

| t <sub>HI</sub>                   | Input Clock High Time                          | 90% to 90%                              | 0.5    | —     | ns     |

| t <sub>LO</sub>                   | Input Clock Low Time                           | 10% to 10%                              | 0.5    | —     | ns     |

| t <sub>STABLE</sub> <sup>5</sup>  | STANDBY High to PLL Stable                     |                                         |        | 15    | ms     |

| t <sub>RST</sub>                  | RST/RESETM Pulse Width                         |                                         | 1      |       | ns     |

| t <sub>RSTREC</sub>               | RST Recovery Time                              |                                         | 1      |       | ns     |

| t <sub>RST_DIV</sub>              | RESETC/D Pulse Width                           |                                         | 10     |       | ns     |

| t <sub>RSTREC_DIV</sub>           | RESETC/D Recovery Time                         |                                         | 1      |       | ns     |

| t <sub>ROTATE-SETUP</sub>         | PHASESTEP Setup Time                           |                                         | 10     |       | ns     |

## **Over Recommended Operating Conditions**

## Flash Download Time<sup>1, 2</sup>

| Symbol               | Parameter                | Device       | Тур. | Units |

|----------------------|--------------------------|--------------|------|-------|

|                      |                          | LCMXO2-256   | 0.6  | ms    |

|                      |                          | LCMXO2-640   | 1.0  | ms    |

|                      |                          | LCMXO2-640U  | 1.9  | ms    |

|                      |                          | LCMXO2-1200  | 1.9  | ms    |

| t <sub>REFRESH</sub> | POR to Device I/O Active | LCMXO2-1200U | 1.4  | ms    |

|                      |                          | LCMXO2-2000  | 1.4  | ms    |

|                      |                          | LCMXO2-2000U | 2.4  | ms    |

|                      |                          | LCMXO2-4000  | 2.4  | ms    |

|                      |                          | LCMXO2-7000  | 3.8  | ms    |

1. Assumes sysMEM EBR initialized to an all zero pattern if they are used.

2. The Flash download time is measured starting from the maximum voltage of POR trip point.

## **JTAG Port Timing Specifications**

| Symbol               | Parameter                                                          | Min. | Max. | Units |

|----------------------|--------------------------------------------------------------------|------|------|-------|

| f <sub>MAX</sub>     | TCK clock frequency                                                |      | 25   | MHz   |

| t <sub>BTCPH</sub>   | TCK [BSCAN] clock pulse width high                                 | 20   | —    | ns    |

| t <sub>BTCPL</sub>   | TCK [BSCAN] clock pulse width low                                  | 20   | —    | ns    |

| t <sub>BTS</sub>     | TCK [BSCAN] setup time                                             | 10   | —    | ns    |

| t <sub>BTH</sub>     | TCK [BSCAN] hold time                                              | 8    | —    | ns    |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to valid output               | _    | 10   | ns    |

| t <sub>BTCODIS</sub> | TAP controller falling edge of clock to valid disable              | _    | 10   | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to valid enable               | _    | 10   | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                             | 8    | —    | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                              | 20   | —    | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to valid output  | _    | 25   | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to valid disable | _    | 25   | ns    |

| t <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  |      | 25   | ns    |

## **Ordering Information**

MachXO2 devices have top-side markings, for commercial and industrial grades, as shown below:

Notes:

- 1. Markings are abbreviated for small packages.

- 2. See PCN 05A-12 for information regarding a change to the top-side mark logo.

# High-Performance Commercial Grade Devices without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100C  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-5TG100C  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-6TG100C  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-4TG144C  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-5TG144C  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-6TG144C  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-4MG132C  | 2112 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-5MG132C  | 2112 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-6MG132C  | 2112 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-4BG256C  | 2112 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-5BG256C  | 2112 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-6BG256C  | 2112 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-4FTG256C | 2112 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-5FTG256C | 2112 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-6FTG256C | 2112 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484C | 2112 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-5FG484C | 2112 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-6FG484C | 2112 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HE-4TG144C  | 4320 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-5TG144C  | 4320 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-6TG144C  | 4320 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-4MG132C  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-5MG132C  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-6MG132C  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-4BG256C  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4MG184C  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5MG184C  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-6MG184C  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5BG256C  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-6BG256C  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4FTG256C | 4320 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-5FTG256C | 4320 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-6FTG256C | 4320 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-4BG332C  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HE-5BG332C  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | COM   |

| Part Number           | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|-----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200HC-4SG32I  | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-5SG32I  | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-6SG32I  | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200HC-4TG100I | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-5TG100I | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-6TG100I | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-4MG132I | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-5MG132I | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-6MG132I | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-4TG144I | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-5TG144I | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-6TG144I | 1280 | 2.5 V/ 3.3 V   | -6    | Halogen-Free TQFP  | 144   | IND   |

| Part Number             | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|-------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200UHC-4FTG256I | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-1200UHC-5FTG256I | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-1200UHC-6FTG256I | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HC-4TG100I  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-5TG100I  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-6TG100I  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HC-4MG132I  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-5MG132I  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-6MG132I  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HC-4TG144I  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-5TG144I  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-6TG144I  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HC-4BG256I  | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-5BG256I  | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-6BG256I  | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HC-4FTG256I | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HC-5FTG256I | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HC-6FTG256I | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000UHC-4FG484I | 2112 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHC-5FG484I | 2112 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHC-6FG484I | 2112 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 484   | IND   |

| Part Number                          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|--------------------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200HC-4TG100IR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-5TG100IR11             | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-6TG100IR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200HC-4MG132IR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-5MG132IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-6MG132IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200HC-4TG144IR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-5TG144IR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200HC-6TG144IR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | IND   |

1. Specifications for the "LCMXO2-1200HC-speed package IR1" are the same as the "LCMXO2-1200ZE-speed package I" devices respectively, except as specified in the R1 Device Specifications section of this data sheet.

| Date         | Version | Section                             | Change Summary                                                                                                                                                                      |

|--------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2013 | 02.0    | Introduction                        | Updated the total number IOs to include JTAGENB.                                                                                                                                    |

|              |         | Architecture                        | Supported Output Standards table – Added 3.3 $V_{CCIO}$ (Typ.) to LVDS row.                                                                                                         |

|              |         |                                     | Changed SRAM CRC Error Detection to Soft Error Detection.                                                                                                                           |

|              |         | DC and Switching<br>Characteristics | Power Supply Ramp Rates table – Updated Units column for t <sub>RAMP</sub> symbol.                                                                                                  |

|              |         |                                     | Added new Maximum sysIO Buffer Performance table.                                                                                                                                   |

|              |         |                                     | sysCLOCK PLL Timing table – Updated Min. column values for $f_{\rm IN}, f_{\rm OUT}, f_{\rm OUT2}$ and $f_{\rm PFD}$ parameters. Added $t_{\rm SPO}$ parameter. Updated footnote 6. |

|              |         |                                     | MachXO2 Oscillator Output Frequency table – Updated symbol name                                                                                                                     |

|              |         |                                     | for t <sub>STABLEOSC</sub> .                                                                                                                                                        |

|              |         |                                     | DC Electrical Characteristics table – Updated conditions for ${\rm I}_{\rm IL,}~{\rm I}_{\rm IH}$ symbols.                                                                          |

|              |         |                                     | Corrected parameters tDQVBS and tDQVAS                                                                                                                                              |

|              |         |                                     | Corrected MachXO2 ZE parameters tDVADQ and tDVEDQ                                                                                                                                   |

|              |         | Pinout Information                  | Included the MachXO2-4000HE 184 csBGA package.                                                                                                                                      |

|              |         | Ordering Information                | Updated part number.                                                                                                                                                                |

| April 2012   | 01.9    | Architecture                        | Removed references to TN1200.                                                                                                                                                       |

|              |         | Ordering Information                | Updated the Device Status portion of the MachXO2 Part Number Description to include the 50 parts per reel for the WLCSP package.                                                    |

|              |         |                                     | Added new part number and footnote 2 for LCMXO2-1200ZE-<br>1UWG25ITR50.                                                                                                             |

|              |         |                                     | Updated footnote 1 for LCMXO2-1200ZE-1UWG25ITR.                                                                                                                                     |

|              |         | Supplemental<br>Information         | Removed references to TN1200.                                                                                                                                                       |

| March 2012   | 01.8    | Introduction                        | Added 32 QFN packaging information to Features bullets and MachXO2 Family Selection Guide table.                                                                                    |

|              |         | DC and Switching<br>Characteristics | Changed 'STANDBY' to 'USERSTDBY' in Standby Mode timing dia-<br>gram.                                                                                                               |

|              |         | Pinout Information                  | Removed footnote from Pin Information Summary tables.                                                                                                                               |

|              |         |                                     | Added 32 QFN package to Pin Information Summary table.                                                                                                                              |

|              |         | Ordering Information                | Updated Part Number Description and Ordering Information tables for 32 QFN package.                                                                                                 |

|              |         |                                     | Updated topside mark diagram in the Ordering Information section.                                                                                                                   |