# E · / Fattice Semiconductor Corporation - <u>LCMX02-4000ZE-1BG332C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                           |

|--------------------------------|----------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 540                                                                              |

| Number of Logic Elements/Cells | 4320                                                                             |

| Total RAM Bits                 | 94208                                                                            |

| Number of I/O                  | 274                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                    |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                  |

| Package / Case                 | 332-FBGA                                                                         |

| Supplier Device Package        | 332-CABGA (17x17)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-4000ze-1bg332c |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MachXO2 Family Data Sheet Introduction

May 2016

## **Features**

- Flexible Logic Architecture

- Six devices with 256 to 6864 LUT4s and 18 to 334 I/Os

- Ultra Low Power Devices

- Advanced 65 nm low power process

- As low as 22  $\mu$ W standby power

- Programmable low swing differential I/Os

- · Stand-by mode and other power saving options

## Embedded and Distributed Memory

- Up to 240 kbits sysMEM™ Embedded Block RAM

- Up to 54 kbits Distributed RAM

- Dedicated FIFO control logic

- On-Chip User Flash Memory

- Up to 256 kbits of User Flash Memory

- 100,000 write cycles

- Accessible through WISHBONE, SPI, I<sup>2</sup>C and JTAG interfaces

- Can be used as soft processor PROM or as Flash memory

## Pre-Engineered Source Synchronous I/O

- DDR registers in I/O cells

- Dedicated gearing logic

- 7:1 Gearing for Display I/Os

- Generic DDR, DDRX2, DDRX4

- Dedicated DDR/DDR2/LPDDR memory with DQS support

## ■ High Performance, Flexible I/O Buffer

- Programmable syslO<sup>™</sup> buffer supports wide range of interfaces:

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- PCI

- LVDS, Bus-LVDS, MLVDS, RSDS, LVPECL

- SSTL 25/18

- HSTL 18

- Schmitt trigger inputs, up to 0.5 V hysteresis

- I/Os support hot socketing

- On-chip differential termination

- · Programmable pull-up or pull-down mode

- Flexible On-Chip Clocking

- · Eight primary clocks

- Up to two edge clocks for high-speed I/O interfaces (top and bottom sides only)

- Up to two analog PLLs per device with fractional-n frequency synthesis

- Wide input frequency range (7 MHz to 400 MHz)

Data Sheet DS1035

- Non-volatile, Infinitely Reconfigurable

- Instant-on powers up in microseconds

- Single-chip, secure solution

- Programmable through JTAG, SPI or I<sup>2</sup>C

- Supports background programming of non-volatile memory

- Optional dual boot with external SPI memory

- TransFR<sup>™</sup> Reconfiguration

- In-field logic update while system operates

## Enhanced System Level Support

- On-chip hardened functions: SPI, I<sup>2</sup>C, timer/ counter

- On-chip oscillator with 5.5% accuracy

- Unique TraceID for system tracking

- One Time Programmable (OTP) mode

- Single power supply with extended operating range

- IEEE Standard 1149.1 boundary scan

- IEEE 1532 compliant in-system programming

- Broad Range of Package Options

- TQFP, WLCSP, ucBGA, csBGA, caBGA, ftBGA, fpBGA, QFN package options

- Small footprint package options

As small as 2.5 mm x 2.5 mm

- · Density migration supported

- Advanced halogen-free packaging

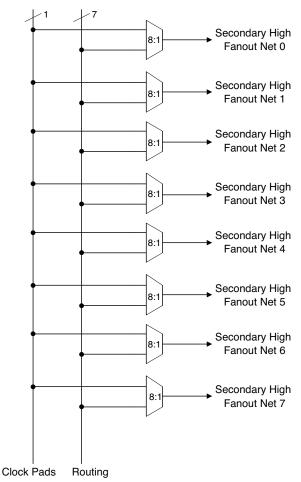

#### Figure 2-6. Secondary High Fanout Nets for MachXO2 Devices

## sysCLOCK Phase Locked Loops (PLLs)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The MachXO2-640U, MachXO2-1200/U and larger devices have one or more sysCLOCK PLL. CLKI is the reference frequency input to the PLL and its source can come from an external I/O pin or from internal routing. CLKFB is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The MachXO2 sysCLOCK PLLs support high resolution (16-bit) fractional-N synthesis. Fractional-N frequency synthesis allows the user to generate an output clock which is a non-integer multiple of the input frequency. For more information about using the PLL with Fractional-N synthesis, please see TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide.

Each output has its own output divider, thus allowing the PLL to generate different frequencies for each output. The output dividers can have a value from 1 to 128. The output dividers may also be cascaded together to generate low frequency clocks. The CLKOP, CLKOS, CLKOS2, and CLKOS3 outputs can all be used to drive the MachXO2 clock distribution network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 2-7.

The setup and hold times of the device can be improved by programming a phase shift into the CLKOS, CLKOS2, and CLKOS3 output clocks which will advance or delay the output clock with reference to the CLKOP output clock.

Table 2-5. sysMEM Block Configurations

| Memory Mode      | Configurations                                               |

|------------------|--------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

#### Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

#### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. EBR initialization data can be loaded from the UFM. To maximize the number of UFM bits, initialize the EBRs used in your design to an all-zero pattern. Initializing to an all-zero pattern does not use up UFM bits. MachXO2 devices have been designed such that multiple EBRs share the same initialization memory space if they are initialized to the same pattern.

By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

#### Memory Cascading

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

### Single, Dual, Pseudo-Dual Port and FIFO Modes

Figure 2-8 shows the five basic memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and addresses for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the memory array output.

## Programmable I/O Cells (PIC)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the MachXO2 devices, the PIO cells are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the MachXO2 devices, two adjacent PIOs can be combined to provide a complementary output driver pair.

The MachXO2-640U, MachXO2-1200/U and higher density devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. Half of the PIO pairs on the top edge of these devices can be configured as true LVDS transmit pairs. The PIO pairs on the bottom edge of these higher density devices have on-chip differential termination and also provide PCI support.

## PIO

The PIO contains three blocks: an input register block, output register block and tri-state register block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

| Table 2-8 | . PIO | Signal | List |

|-----------|-------|--------|------|

|-----------|-------|--------|------|

| Pin Name               | I/О Туре | Description                                         |

|------------------------|----------|-----------------------------------------------------|

| CE                     | Input    | Clock Enable                                        |

| D                      | Input    | Pin input from sysIO buffer.                        |

| INDD                   | Output   | Register bypassed input.                            |

| INCK                   | Output   | Clock input                                         |

| Q0                     | Output   | DDR positive edge input                             |

| Q1                     | Output   | Registered input/DDR negative edge input            |

| D0                     | Input    | Output signal from the core (SDR and DDR)           |

| D1                     | Input    | Output signal from the core (DDR)                   |

| TD                     | Input    | Tri-state signal from the core                      |

| Q                      | Output   | Data output signals to sysIO Buffer                 |

| TQ                     | Output   | Tri-state output signals to sysIO Buffer            |

| DQSR90 <sup>1</sup>    | Input    | DQS shift 90-degree read clock                      |

| DQSW90 <sup>1</sup>    | Input    | DQS shift 90-degree write clock                     |

| DDRCLKPOL <sup>1</sup> | Input    | DDR input register polarity control signal from DQS |

| SCLK                   | Input    | System clock for input and output/tri-state blocks. |

| RST                    | Input    | Local set reset signal                              |

1. Available in PIO on right edge only.

## Input Register Block

The input register blocks for the PIOs on all edges contain delay elements and registers that can be used to condition high-speed interface signals before they are passed to the device core. In addition to this functionality, the input register blocks for the PIOs on the right edge include built-in logic to interface to DDR memory.

Figure 2-12 shows the input register block for the PIOs located on the left, top and bottom edges. Figure 2-13 shows the input register block for the PIOs on the right edge.

### Left, Top, Bottom Edges

Input signals are fed from the sysIO buffer to the input register block (as signal D). If desired, the input signal can bypass the register and delay elements and be used directly as a combinatorial signal (INDD), and a clock (INCK). If an input delay is desired, users can select a fixed delay. I/Os on the bottom edge also have a dynamic delay, DEL[4:0]. The delay, if selected, reduces input register hold time requirements when using a global clock. The input block allows two modes of operation. In single data rate (SDR) the data is registered with the system clock (SCLK) by one of the registers in the single data rate sync register block. In Generic DDR mode, two registers are used to sample the data on the positive and negative edges of the system clock (SCLK) signal, creating two data streams.

More information on the input gearbox is available in TN1203, Implementing High-Speed Interfaces with MachXO2 Devices.

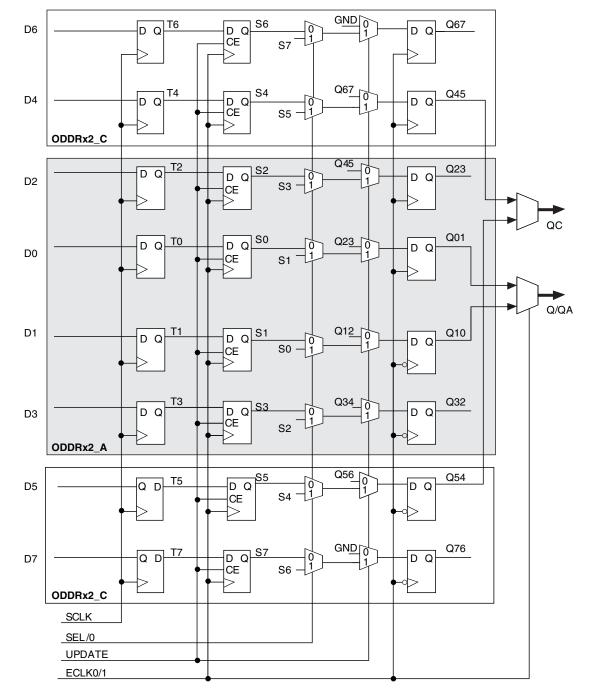

## **Output Gearbox**

Each PIC on the top edge has a built-in 8:1 output gearbox. Each of these output gearboxes may be programmed as a 7:1 serializer or as one ODDRX4 (8:1) gearbox or as two ODDRX2 (4:1) gearboxes. Table 2-10 shows the gearbox signals.

## Table 2-10. Output Gearbox Signal List

| Name                       | I/O Type | Description                     |

|----------------------------|----------|---------------------------------|

| Q                          | Output   | High-speed data output          |

| D[7:0]                     | Input    | Low-speed data from device core |

| Video TX(7:1): D[6:0]      |          |                                 |

| GDDRX4(8:1): D[7:0]        |          |                                 |

| GDDRX2(4:1)(IOL-A): D[3:0] |          |                                 |

| GDDRX2(4:1)(IOL-C): D[7:4] |          |                                 |

| SCLK                       | Input    | Slow-speed system clock         |

| ECLK [1:0]                 | Input    | High-speed edge clock           |

| RST                        | Input    | Reset                           |

The gearboxes have three stage pipeline registers. The first stage registers sample the low-speed input data on the low-speed system clock. The second stage registers transfer data from the low-speed clock registers to the high-speed clock registers. The third stage pipeline registers controlled by high-speed edge clock shift and mux the high-speed data out to the sysIO buffer. Figure 2-17 shows the output gearbox block diagram.

## Figure 2-17. Output Gearbox

More information on the output gearbox is available in TN1203, Implementing High-Speed Interfaces with MachXO2 Devices.

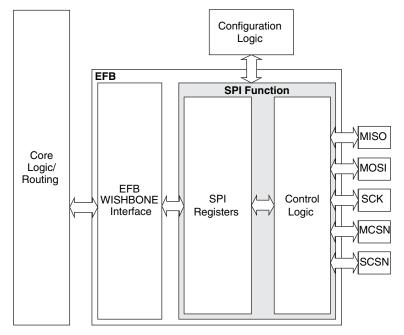

There are some limitations on the use of the hardened user SPI. These are defined in the following technical notes:

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology (Appendix B)

- TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices

## Figure 2-22. SPI Core Block Diagram

Table 2-16 describes the signals interfacing with the SPI cores.

Table 2-16. SPI Core Signal Description

| Signal Name | I/O | Master/Slave | Description                                                                                                                                                                           |

|-------------|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| spi_csn[0]  | 0   | Master       | SPI master chip-select output                                                                                                                                                         |

| spi_csn[17] | 0   | Master       | Additional SPI chip-select outputs (total up to eight slaves)                                                                                                                         |

| spi_scsn    | I   | Slave        | SPI slave chip-select input                                                                                                                                                           |

| spi_irq     | 0   | Master/Slave | Interrupt request                                                                                                                                                                     |

| spi_clk     | I/O | Master/Slave | SPI clock. Output in master mode. Input in slave mode.                                                                                                                                |

| spi_miso    | I/O | Master/Slave | SPI data. Input in master mode. Output in slave mode.                                                                                                                                 |

| spi_mosi    | I/O | Master/Slave | SPI data. Output in master mode. Input in slave mode.                                                                                                                                 |

| ufm_sn      | I   | Slave        | Configuration Slave Chip Select (active low), dedicated for selecting the User Flash Memory (UFM).                                                                                    |

| cfg_stdby   | 0   | Master/Slave | Stand-by signal – To be connected only to the power module of the MachXO2 device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab. |

| cfg_wake    | 0   | Master/Slave | Wake-up signal – To be connected only to the power module of the MachXO2 device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab.  |

When implementing background programming of the on-chip Flash, care must be taken for the operation of the PLL. For devices that have two PLLs (XO2-2000U, -4000 and -7000), the system must put the RPLL (Right-side PLL) in reset state during the background Flash programming. More detailed description can be found in TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Security and One-Time Programmable Mode (OTP)

For applications where security is important, the lack of an external bitstream provides a solution that is inherently more secure than SRAM-based FPGAs. This is further enhanced by device locking. MachXO2 devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile Flash memory spaces. The device can be in one of two modes:

- 1. Unlocked Readback of the SRAM configuration and non-volatile Flash memory spaces is allowed.

- 2. Permanently Locked The device is permanently locked.

Once set, the only way to clear the security bits is to erase the device. To further complement the security of the device, a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the Flash and SRAM OTP portions of the device. For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Dual Boot

MachXO2 devices can optionally boot from two patterns, a primary bitstream and a golden bitstream. If the primary bitstream is found to be corrupt while being downloaded into the SRAM, the device shall then automatically re-boot from the golden bitstream. Note that the primary bitstream must reside in the on-chip Flash. The golden image MUST reside in an external SPI Flash. For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Soft Error Detection

The SED feature is a CRC check of the SRAM cells after the device is configured. This check ensures that the SRAM cells were configured successfully. This feature is enabled by a configuration bit option. The Soft Error Detection can also be initiated in user mode via an input to the fabric. The clock for the Soft Error Detection circuit is generated using a dedicated divider. The undivided clock from the on-chip oscillator is the input to this divider. For low power applications users can switch off the Soft Error Detection circuit. For more details, refer to TN1206, MachXO2 Soft Error Detection Usage Guide.

## TraceID

Each MachXO2 device contains a unique (per device), TraceID that can be used for tracking purposes or for IP security applications. The TraceID is 64 bits long. Eight out of 64 bits are user-programmable, the remaining 56 bits are factory-programmed. The TraceID is accessible through the EFB WISHBONE interface and can also be accessed through the SPI, I<sup>2</sup>C, or JTAG interfaces.

## **Density Shifting**

The MachXO2 family has been designed to enable density migration within the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case. When migrating from lower to higher density or higher to lower density, ensure to review all the power supplies and NC pins of the chosen devices. For more details refer to the MachXO2 migration files.

## Static Supply Current – HC/HE Devices<sup>1, 2, 3, 6</sup>

| Symbol | Parameter                                       | Device         | Typ.⁴ | Units |

|--------|-------------------------------------------------|----------------|-------|-------|

|        |                                                 | LCMXO2-256HC   | 1.15  | mA    |

|        |                                                 | LCMXO2-640HC   | 1.84  | mA    |

|        |                                                 | LCMXO2-640UHC  | 3.48  | mA    |

|        |                                                 | LCMXO2-1200HC  | 3.49  | mA    |

|        |                                                 | LCMXO2-1200UHC | 4.80  | mA    |

| 1      | Core Power Supply                               | LCMXO2-2000HC  | 4.80  | mA    |

| ICC    |                                                 | LCMXO2-2000UHC | 8.44  | mA    |

|        |                                                 | LCMXO2-4000HC  | 8.45  | mA    |

|        |                                                 | LCMXO2-7000HC  | 12.87 | mA    |

|        |                                                 | LCMXO2-2000HE  | 1.39  | mA    |

|        |                                                 | LCMXO2-4000HE  | 2.55  | mA    |

|        |                                                 | LCMXO2-7000HE  | 4.06  | mA    |

| Іссю   | Bank Power Supply⁵<br>V <sub>CCIO</sub> = 2.5 V | All devices    | 0     | mA    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

2. Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip oscillator is off, on-chip PLL is off.

3. Frequency = 0 MHz.

4.  $T_J = 25$  °C, power supplies at nominal voltage.

5. Does not include pull-up/pull-down.

6. To determine the MachXO2 peak start-up current data, use the Power Calculator tool.

# Programming and Erase Flash Supply Current – HC/HE Devices<sup>1, 2, 3, 4</sup>

| Symbol            | Parameter                      | Device         | Typ.⁵ | Units |

|-------------------|--------------------------------|----------------|-------|-------|

|                   |                                | LCMXO2-256HC   | 14.6  | mA    |

|                   |                                | LCMXO2-640HC   | 16.1  | mA    |

|                   |                                | LCMXO2-640UHC  | 18.8  | mA    |

|                   |                                | LCMXO2-1200HC  | 18.8  | mA    |

|                   |                                | LCMXO2-1200UHC | 22.1  | mA    |

|                   |                                | LCMXO2-2000HC  | 22.1  | mA    |

| I <sub>CC</sub>   | Core Power Supply              | LCMXO2-2000UHC | 26.8  | mA    |

|                   |                                | LCMXO2-4000HC  | 26.8  | mA    |

|                   |                                | LCMXO2-7000HC  | 33.2  | mA    |

|                   |                                | LCMXO2-2000HE  | 18.3  | mA    |

|                   |                                | LCMXO2-2000UHE | 20.4  | mA    |

|                   |                                | LCMXO2-4000HE  | 20.4  | mA    |

|                   |                                | LCMXO2-7000HE  | 23.9  | mA    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>6</sup> | All devices    | 0     | mA    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

2. Assumes all inputs are held at  $V_{CCIO}$  or GND and all outputs are tri-stated.

3. Typical user pattern.

4. JTAG programming is at 25 MHz.

5.  $T_J = 25$  °C, power supplies at nominal voltage.

6. Per bank.  $V_{CCIO} = 2.5$  V. Does not include pull-up/pull-down.

# Programming and Erase Flash Supply Current – ZE Devices<sup>1, 2, 3, 4</sup>

| Symbol          | Parameter                      | Device        | Typ.⁵ | Units |

|-----------------|--------------------------------|---------------|-------|-------|

|                 |                                | LCMXO2-256ZE  | 13    | mA    |

|                 |                                | LCMXO2-640ZE  | 14    | mA    |

| I <sub>CC</sub> | Core Power Supply              | LCMXO2-1200ZE | 15    | mA    |

|                 | Core Fower Supply              | LCMXO2-2000ZE | 17    | mA    |

|                 |                                | LCMXO2-4000ZE | 18    | mA    |

|                 |                                | LCMXO2-7000ZE | 20    | mA    |

| ICCIO           | Bank Power Supply <sup>6</sup> | All devices   | 0     | mA    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

2. Assumes all inputs are held at  $V_{\mbox{CCIO}}$  or GND and all outputs are tri-stated.

3. Typical user pattern.

4. JTAG programming is at 25 MHz.

5. TJ = 25 °C, power supplies at nominal voltage.

6. Per bank.  $V_{CCIO}$  = 2.5 V. Does not include pull-up/pull-down.

|                    |                                                                  |                                                                          | _                                                   | -6       | _         | 5      | _       | 4                      |                        |

|--------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|----------|-----------|--------|---------|------------------------|------------------------|

| Parameter          | Description                                                      | Device                                                                   | Min.                                                | Max.     | Min.      | Max.   | Min.    | Max.                   | Units                  |

| Generic DDR        | X2 Outputs with Clock and Data                                   | Centered at Pin Using P                                                  | CLK Pin                                             | for Cloc | k Input – | GDDRX  | 2_TX.EC | LK.Cen                 | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>   | Output Data Valid Before CLK<br>Output                           |                                                                          | 0.535                                               | _        | 0.670     | _      | 0.830   | _                      | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                                            | 0.535                                               | _        | 0.670     | _      | 0.830   | _                      | ns                     |

| f <sub>DATA</sub>  | DDRX2 Serial Output Data<br>Speed                                | MachXO2-1200/U and larger devices, top side only.                        |                                                     | 664      | _         | 554    | _       | 462                    | Mbps                   |

| f <sub>DDRX2</sub> | DDRX2 ECLK Frequency<br>(minimum limited by PLL)                 |                                                                          |                                                     | 332      | _         | 277    | _       | 231                    | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   | -                                                                        |                                                     | 166      | —         | 139    |         | 116                    | MHz                    |

| Generic DDF        | X4 Outputs with Clock and Data                                   | Aligned at Pin Using P                                                   | CLK Pin                                             | for Cloc | k Input   | - GDDR | X4_TX.E | CLK.Ali                | gned <sup>9, 12</sup>  |

| t <sub>DIA</sub>   | Output Data Invalid After CLK<br>Output                          |                                                                          | _                                                   | 0.200    | _         | 0.215  | _       | 0.230                  | ns                     |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                         | MachXO2-640U,<br>MachXO2-1200/U and                                      |                                                     | 0.200    | _         | 0.215  | _       | 0.230                  | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Output Data<br>Speed                                | larger devices, top side<br>only.                                        |                                                     | 756      | _         | 630    | _       | 524                    | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency                                             |                                                                          | _                                                   | 378      | —         | 315    | —       | 262                    | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                                          | _                                                   | 95       | —         | 79     |         | 66                     | MHz                    |

| Generic DDF        | X4 Outputs with Clock and Data                                   | Centered at Pin Using Po                                                 | CLK Pin for Clock Input – GDDRX4_TX.ECLK.Centered9, |          |           |        |         | tered <sup>9, 12</sup> |                        |

| t <sub>DVB</sub>   | Output Data Valid Before CLK<br>Output                           |                                                                          | 0.455                                               | _        | 0.570     |        | 0.710   | —                      | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                                            | 0.455                                               | _        | 0.570     |        | 0.710   | _                      | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Output Data<br>Speed                                | MachXO2-1200/U and larger devices, top side only.                        |                                                     | 756      | _         | 630    | _       | 524                    | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency<br>(minimum limited by PLL)                 | ony.                                                                     |                                                     | 378      | _         | 315    | _       | 262                    | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                                          | _                                                   | 95       | —         | 79     | —       | 66                     | MHz                    |

| 7:1 LVDS Ou        | utputs - GDDR71_TX.ECLK.7:1                                      | 9, 12                                                                    |                                                     |          |           |        |         |                        |                        |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                         |                                                                          | _                                                   | 0.160    | _         | 0.180  |         | 0.200                  | ns                     |

| t <sub>DIA</sub>   | Output Data Invalid After CLK<br>Output                          | MachXO2-640U,<br>MachXO2-1200/U and<br>larger devices, top side<br>only. |                                                     | 0.160    | _         | 0.180  | _       | 0.200                  | ns                     |

| f <sub>DATA</sub>  | DDR71 Serial Output Data<br>Speed                                |                                                                          | _                                                   | 756      | _         | 630    | _       | 524                    | Mbps                   |

| f <sub>DDR71</sub> | DDR71 ECLK Frequency                                             |                                                                          | _                                                   | 378      | _         | 315    | _       | 262                    | MHz                    |

| fclkout            | 7:1 Output Clock Frequency<br>(SCLK) (minimum limited by<br>PLL) |                                                                          | _                                                   | 108      | _         | 90     | _       | 75                     | MHz                    |

|                        |                                         | -3                                                     |          |           | -         | -2      | - 1     | 1       |                        |

|------------------------|-----------------------------------------|--------------------------------------------------------|----------|-----------|-----------|---------|---------|---------|------------------------|

| Parameter              | Description                             | Device                                                 | Min.     | Max.      | Min.      | Max.    | Min.    | Max.    | Units                  |

|                        |                                         | MachXO2-1200ZE                                         | 0.66     |           | 0.68      |         | 0.80    |         | ns                     |

|                        | Clock to Data Hold – PIO Input          | MachXO2-2000ZE                                         | 0.68     | —         | 0.70      | —       | 0.83    | —       | ns                     |

| t <sub>HPLL</sub>      | Register                                | MachXO2-4000ZE                                         | 0.68     | —         | 0.71      | —       | 0.84    | —       | ns                     |

|                        |                                         | MachXO2-7000ZE                                         | 0.73     | —         | 0.74      | —       | 0.87    | —       | ns                     |

| -                      |                                         | MachXO2-1200ZE                                         | 5.14     | —         | 5.69      | —       | 6.20    | —       | ns                     |

|                        | Clock to Data Setup – PIO               | MachXO2-2000ZE                                         | 5.11     | —         | 5.67      | —       | 6.17    | —       | ns                     |

| <sup>t</sup> SU_DELPLL | Input Register with Data Input Delay    | MachXO2-4000ZE                                         | 5.27     | —         | 5.84      |         | 6.35    | —       | ns                     |

|                        |                                         | MachXO2-7000ZE                                         | 5.15     | —         | 5.71      | —       | 6.23    | —       | ns                     |

| -                      |                                         | MachXO2-1200ZE                                         | -1.36    | —         | -1.36     | —       | -1.36   | —       | ns                     |

|                        | Clock to Data Hold – PIO Input          | MachXO2-2000ZE                                         | -1.35    |           | -1.35     |         | -1.35   |         | ns                     |

| <sup>t</sup> H_DELPLL  | H_DELPLL Register with Input Data Delay | MachXO2-4000ZE                                         | -1.43    |           | -1.43     |         | -1.43   |         | ns                     |

|                        |                                         | MachXO2-7000ZE                                         | -1.41    |           | -1.41     |         | -1.41   |         | ns                     |

| Generic DDR            | X1 Inputs with Clock and Data A         | ligned at Pin Using P                                  | CLK Pin  | for Cloc  | k Input - | - GDDR) | (1_RX.S | CLK.Ali | gned <sup>9, 12</sup>  |

| t <sub>DVA</sub>       | Input Data Valid After CLK              |                                                        | —        | 0.382     |           | 0.401   | —       | 0.417   | UI                     |

| t <sub>DVE</sub>       | Input Data Hold After CLK               | All MachXO2<br>devices, all sides                      | 0.670    | —         | 0.684     |         | 0.693   | —       | UI                     |

| f <sub>DATA</sub>      | DDRX1 Input Data Speed                  |                                                        | _        | 140       |           | 116     | —       | 98      | Mbps                   |

| f <sub>DDRX1</sub>     | DDRX1 SCLK Frequency                    |                                                        | _        | 70        |           | 58      | —       | 49      | MHz                    |

|                        | X1 Inputs with Clock and Data Ce        | entered at Pin Using PO                                | LK Pin f | for Clock | Input –   | GDDRX   | 1_RX.SC | LK.Cen  | tered <sup>9, 12</sup> |

| t <sub>SU</sub>        | Input Data Setup Before CLK             |                                                        | 1.319    |           | 1.412     |         | 1.462   |         | ns                     |

| t <sub>HO</sub>        | Input Data Hold After CLK               | All MachXO2<br>devices, all sides                      | 0.717    | _         | 1.010     |         | 1.340   |         | ns                     |

| f <sub>DATA</sub>      | DDRX1 Input Data Speed                  |                                                        | _        | 140       |           | 116     | —       | 98      | Mbps                   |

| f <sub>DDRX1</sub>     | DDRX1 SCLK Frequency                    |                                                        | _        | 70        |           | 58      | —       | 49      | MHz                    |

|                        | X2 Inputs with Clock and Data A         | ligned at Pin Using P                                  | LK Pin   | for Cloc  | k Input - | GDDR    | 2_RX.E  | CLK.Ali | gned <sup>9, 12</sup>  |

| t <sub>DVA</sub>       | Input Data Valid After CLK              |                                                        | —        | 0.361     |           | 0.346   | —       | 0.334   | UI                     |

| t <sub>DVE</sub>       | Input Data Hold After CLK               | MachXO2-640U,                                          | 0.602    |           | 0.625     |         | 0.648   |         | UI                     |

| f <sub>DATA</sub>      | DDRX2 Serial Input Data<br>Speed        | MachXO2-1200/U<br>and larger devices,                  | _        | 280       | _         | 234     | _       | 194     | Mbps                   |

| f <sub>DDRX2</sub>     | DDRX2 ECLK Frequency                    | bottom side only <sup>11</sup>                         | _        | 140       |           | 117     | —       | 97      | MHz                    |

| f <sub>SCLK</sub>      | SCLK Frequency                          |                                                        | _        | 70        |           | 59      | —       | 49      | MHz                    |

|                        | X2 Inputs with Clock and Data Ce        | entered at Pin Using P                                 | LK Pin f | for Clock | Input –   | GDDRX   | 2_RX.EC | LK.Cen  | tered <sup>9, 12</sup> |

| t <sub>SU</sub>        | Input Data Setup Before CLK             |                                                        | 0.472    |           | 0.672     |         | 0.865   |         | ns                     |

| t <sub>HO</sub>        | Input Data Hold After CLK               | MachXO2-640U,                                          | 0.363    | _         | 0.501     |         | 0.743   |         | ns                     |

| f <sub>DATA</sub>      | DDRX2 Serial Input Data<br>Speed        | MachXO2-0400,<br>MachXO2-1200/U<br>and larger devices, |          | 280       | _         | 234     | _       | 194     | Mbps                   |

| f <sub>DDRX2</sub>     | DDRX2 ECLK Frequency                    | bottom side only <sup>11</sup>                         |          | 140       |           | 117     | _       | 97      | MHz                    |

| f <sub>SCLK</sub>      | SCLK Frequency                          |                                                        |          | 70        |           | 59      | _       | 49      | MHz                    |

|                        | 4 Inputs with Clock and Data A          | ligned at Pin Using PC                                 | LK Pin   | for Cloc  | k Input - | GDDRX   | 4_RX.E  | CLK.Ali | gned <sup>9, 12</sup>  |

| t <sub>DVA</sub>       | Input Data Valid After ECLK             |                                                        | _        | 0.307     |           | 0.316   | _       | 0.326   | UI                     |

| t <sub>DVE</sub>       | Input Data Hold After ECLK              | MachXO2-640U,<br>MachXO2-1200/U<br>and larger devices, | 0.662    |           | 0.650     |         | 0.649   | _       | UI                     |

| f <sub>DATA</sub>      | DDRX4 Serial Input Data<br>Speed        |                                                        | —        | 420       | _         | 352     | _       | 292     | Mbps                   |

| f <sub>DDRX4</sub>     | DDRX4 ECLK Frequency                    | bottom side only <sup>11</sup>                         | <b>—</b> | 210       |           | 176     | _       | 146     | MHz                    |

| f <sub>SCLK</sub>      | SCLK Frequency                          |                                                        | <u> </u> | 53        | _         | 44      | —       | 37      | MHz                    |

| JULIN                  |                                         | I                                                      | 1        |           |           |         | I       |         |                        |

## sysCLOCK PLL Timing

| Parameter                         | Descriptions                                   | Conditions                              | Min.   | Max.  | Units  |

|-----------------------------------|------------------------------------------------|-----------------------------------------|--------|-------|--------|

| f <sub>IN</sub>                   | Input Clock Frequency (CLKI, CLKFB)            |                                         | 7      | 400   | MHz    |

| fout                              | Output Clock Frequency (CLKOP, CLKOS, CLKOS2)  |                                         | 1.5625 | 400   | MHz    |

| fout2                             | Output Frequency (CLKOS3 cascaded from CLKOS2) |                                         | 0.0122 | 400   | MHz    |

| f <sub>VCO</sub>                  | PLL VCO Frequency                              |                                         | 200    | 800   | MHz    |

| f <sub>PFD</sub>                  | Phase Detector Input Frequency                 |                                         | 7      | 400   | MHz    |

| AC Characteri                     | stics                                          | •                                       |        |       |        |

| t <sub>DT</sub>                   | Output Clock Duty Cycle                        | Without duty trim selected <sup>3</sup> | 45     | 55    | %      |

| t <sub>DT_TRIM</sub> <sup>7</sup> | Edge Duty Trim Accuracy                        |                                         | -75    | 75    | %      |

| t <sub>PH</sub> ⁴                 | Output Phase Accuracy                          |                                         | -6     | 6     | %      |

|                                   | Output Clock Pariad littar                     | f <sub>OUT</sub> > 100 MHz              | —      | 150   | ps p-p |

|                                   | Output Clock Period Jitter                     | f <sub>OUT</sub> < 100 MHz              | _      | 0.007 | UIPP   |

|                                   | Output Olaski Ousla ta susla littari           | f <sub>OUT</sub> > 100 MHz              | _      | 180   | ps p-p |

| t <sub>opjit</sub> 1,8            | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> < 100 MHz              | —      | 0.009 | UIPP   |

|                                   | Outrast Olaska Dhasan Jittari                  | f <sub>PFD</sub> > 100 MHz              | —      | 160   | ps p-p |

|                                   | Output Clock Phase Jitter                      | f <sub>PFD</sub> < 100 MHz              | —      | 0.011 | UIPP   |

|                                   |                                                | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p |

|                                   | Output Clock Period Jitter (Fractional-N)      | f <sub>OUT</sub> < 100 MHz              | _      | 0.12  | UIPP   |

|                                   | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p |

|                                   | (Fractional-N)                                 | f <sub>OUT</sub> < 100 MHz              | _      | 0.12  | UIPP   |

| t <sub>SPO</sub>                  | Static Phase Offset                            | Divider ratio = integer                 | -120   | 120   | ps     |

| t <sub>W</sub>                    | Output Clock Pulse Width                       | At 90% or 10% <sup>3</sup>              | 0.9    | —     | ns     |

| tLOCK <sup>2, 5</sup>             | PLL Lock-in Time                               |                                         | _      | 15    | ms     |

| t <sub>UNLOCK</sub>               | PLL Unlock Time                                |                                         | _      | 50    | ns     |

| <b>•</b> 6                        | Innut Clask Daviad Littar                      | f <sub>PFD</sub> ≥ 20 MHz               | —      | 1,000 | ps p-p |

| t <sub>IPJIT</sub> <sup>6</sup>   | Input Clock Period Jitter                      | f <sub>PFD</sub> < 20 MHz               | —      | 0.02  | UIPP   |

| t <sub>HI</sub>                   | Input Clock High Time                          | 90% to 90%                              | 0.5    | —     | ns     |

| t <sub>LO</sub>                   | Input Clock Low Time                           | 10% to 10%                              | 0.5    | —     | ns     |

| t <sub>STABLE</sub> <sup>5</sup>  | STANDBY High to PLL Stable                     |                                         |        | 15    | ms     |

| t <sub>RST</sub>                  | RST/RESETM Pulse Width                         |                                         | 1      |       | ns     |

| t <sub>RSTREC</sub>               | RST Recovery Time                              |                                         | 1      |       | ns     |

| t <sub>RST_DIV</sub>              | RESETC/D Pulse Width                           |                                         | 10     |       | ns     |

| t <sub>RSTREC_DIV</sub>           | RESETC/D Recovery Time                         |                                         | 1      |       | ns     |

| t <sub>ROTATE-SETUP</sub>         | PHASESTEP Setup Time                           |                                         | 10     |       | ns     |

## **Over Recommended Operating Conditions**

|                                                           | MachXO2-2000 |             |              |             |              | MachXO2-2000U |           |

|-----------------------------------------------------------|--------------|-------------|--------------|-------------|--------------|---------------|-----------|

|                                                           | 49<br>WLCSP  | 100<br>TQFP | 132<br>csBGA | 144<br>TQFP | 256<br>caBGA | 256<br>ftBGA  | 484 ftBGA |

| General Purpose I/O per Bank                              | •            |             |              |             | •            |               |           |

| Bank 0                                                    | 19           | 18          | 25           | 27          | 50           | 50            | 70        |

| Bank 1                                                    | 0            | 21          | 26           | 28          | 52           | 52            | 68        |

| Bank 2                                                    | 13           | 20          | 28           | 28          | 52           | 52            | 72        |

| Bank 3                                                    | 0            | 6           | 7            | 8           | 16           | 16            | 24        |

| Bank 4                                                    | 0            | 6           | 8            | 10          | 16           | 16            | 16        |

| Bank 5                                                    | 6            | 8           | 10           | 10          | 20           | 20            | 28        |

| Total General Purpose Single-Ended I/O                    | 38           | 79          | 104          | 111         | 206          | 206           | 278       |

| Differential I/O per Bank                                 |              |             |              |             |              |               |           |

| Bank 0                                                    | 7            | 9           | 13           | 14          | 25           | 25            | 35        |

| Bank 1                                                    | 0            | 10          | 13           | 14          | 26           | 26            | 34        |

| Bank 2                                                    | 6            | 10          | 14           | 14          | 26           | 26            | 36        |

| Bank 3                                                    | 0            | 3           | 3            | 4           | 8            | 8             | 12        |

| Bank 4                                                    | 0            | 3           | 4            | 5           | 8            | 8             | 8         |

| Bank 5                                                    | 3            | 4           | 5            | 5           | 10           | 10            | 14        |

| Total General Purpose Differential I/O                    | 16           | 39          | 52           | 56          | 103          | 103           | 139       |

| Dual Function I/O                                         | 24           | 31          | 33           | 33          | 33           | 33            | 37        |

| High-speed Differential I/O                               |              | -           |              |             |              |               | _         |

| Bank 0                                                    | 5            | 4           | 8            | 9           | 14           | 14            | 18        |

| Gearboxes                                                 | -            |             | -            | _           |              |               | -         |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 5            | 4           | 8            | 9           | 14           | 14            | 18        |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 6            | 10          | 14           | 14          | 14           | 14            | 18        |

| DQS Groups                                                |              |             |              |             |              |               |           |

| Bank 1                                                    | 0            | 1           | 2            | 2           | 2            | 2             | 2         |

| VCCIO Pins                                                |              |             |              |             |              |               |           |

| Bank 0                                                    | 2            | 2           | 3            | 3           | 4            | 4             | 10        |

| Bank 1                                                    | 0            | 2           | 3            | 3           | 4            | 4             | 10        |

| Bank 2                                                    | 1            | 2           | 3            | 3           | 4            | 4             | 10        |

| Bank 3                                                    | 0            | 1           | 1            | 1           | 1            | 1             | 3         |

| Bank 4                                                    | 0            | 1           | 1            | 1           | 2            | 2             | 4         |

| Bank 5                                                    | 1            | 1           | 1            | 1           | 1            | 1             | 3         |

|                                                           |              |             | •            |             | 1            | r             | T         |

| VCC                                                       | 2            | 2           | 4            | 4           | 8            | 8             | 12        |

| GND                                                       | 4            | 8           | 10           | 12          | 24           | 24            | 48        |

| NC                                                        | 0            | 1           | 1            | 4           | 1            | 1             | 105       |

| Reserved for Configuration                                | 1            | 1           | 1            | 1           | v            | 1             | 1         |

| Total Count of Bonded Pins                                | 39           | 100         | 132          | 144         | 256          | 256           | 484       |

\_

|                                                           | MachXO2-7000 |           |           |           |           |           |

|-----------------------------------------------------------|--------------|-----------|-----------|-----------|-----------|-----------|

|                                                           | 144 TQFP     | 256 caBGA | 256 ftBGA | 332 caBGA | 400 caBGA | 484 fpBGA |

| General Purpose I/O per Bank                              |              | 1         | 1         |           |           | 1         |

| Bank 0                                                    | 27           | 50        | 50        | 68        | 83        | 82        |

| Bank 1                                                    | 29           | 52        | 52        | 70        | 84        | 84        |

| Bank 2                                                    | 29           | 52        | 52        | 70        | 84        | 84        |

| Bank 3                                                    | 9            | 16        | 16        | 24        | 28        | 28        |

| Bank 4                                                    | 10           | 16        | 16        | 16        | 24        | 24        |

| Bank 5                                                    | 10           | 20        | 20        | 30        | 32        | 32        |

| Total General Purpose Single Ended I/O                    | 114          | 206       | 206       | 278       | 335       | 334       |

| Differential I/O per Bank                                 |              |           |           |           |           |           |

| Bank 0                                                    | 14           | 25        | 25        | 34        | 42        | 41        |

| Bank 1                                                    | 14           | 26        | 26        | 35        | 42        | 42        |

| Bank 2                                                    | 14           | 26        | 26        | 35        | 42        | 42        |

| Bank 3                                                    | 4            | 8         | 8         | 12        | 14        | 14        |

| Bank 4                                                    | 5            | 8         | 8         | 8         | 12        | 12        |

| Bank 5                                                    | 5            | 10        | 10        | 15        | 16        | 16        |

| Total General Purpose Differential I/O                    | 56           | 103       | 103       | 139       | 168       | 167       |

| Dual Function I/O                                         | 37           | 37        | 37        | 37        | 37        | 37        |

| High-speed Differential I/O                               |              | -         | -         | -         | -         | -         |

| Bank 0                                                    | 9            | 20        | 20        | 21        | 21        | 21        |

| Gearboxes                                                 |              |           |           |           |           |           |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 9            | 20        | 20        | 21        | 21        | 21        |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 14           | 20        | 20        | 21        | 21        | 21        |

| DQS Groups                                                |              |           | •         |           | •         | •         |

| Bank 1                                                    | 2            | 2         | 2         | 2         | 2         | 2         |

| VCCIO Pins                                                |              |           |           |           |           |           |

| Bank 0                                                    | 3            | 4         | 4         | 4         | 5         | 10        |

| Bank 1                                                    | 3            | 4         | 4         | 4         | 5         | 10        |

| Bank 2                                                    | 3            | 4         | 4         | 4         | 5         | 10        |

| Bank 3                                                    | 1            | 1         | 1         | 2         | 2         | 3         |

| Bank 4                                                    | 1            | 2         | 2         | 1         | 2         | 4         |

| Bank 5                                                    | 1            | 1         | 1         | 2         | 2         | 3         |

|                                                           |              | -         | -         | -         |           |           |

| VCC                                                       | 4            | 8         | 8         | 8         | 10        | 12        |

| GND                                                       | 12           | 24        | 24        | 27        | 33        | 48        |

| NC                                                        | 1            | 1         | 1         | 1         | 0         | 49        |

| Reserved for Configuration                                | 1            | 1         | 1         | 1         | 1         | 1         |

| Total Count of Bonded Pins                                | 144          | 256       | 256       | 332       | 400       | 484       |

## **For Further Information**

For further information regarding logic signal connections for various packages please refer to the MachXO2 Device Pinout Files.

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Users must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

## For Further Information

For further information regarding Thermal Management, refer to the following:

- Thermal Management document

- TN1198, Power Estimation and Management for MachXO2 Devices

- The Power Calculator tool is included with the Lattice design tools, or as a standalone download from www.latticesemi.com/software

# High-Performance Commercial Grade Devices with Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-256HC-4SG32C  | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256HC-5SG32C  | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256HC-6SG32C  | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256HC-4SG48C  | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-256HC-5SG48C  | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-256HC-6SG48C  | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-256HC-4UMG64C | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256HC-5UMG64C | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256HC-6UMG64C | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256HC-4TG100C | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256HC-5TG100C | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256HC-6TG100C | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256HC-4MG132C | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-256HC-5MG132C | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-256HC-6MG132C | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | COM   |

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-640HC-4SG48C  | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-640HC-5SG48C  | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-640HC-6SG48C  | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-640HC-4TG100C | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640HC-5TG100C | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640HC-6TG100C | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640HC-4MG132C | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-640HC-5MG132C | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-640HC-6MG132C | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | COM   |

| Part Number           | LUTs | Supply Voltage | Grade | Package           | Leads | Temp. |

|-----------------------|------|----------------|-------|-------------------|-------|-------|

| LCMXO2-640UHC-4TG144C | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP | 144   | COM   |

| LCMXO2-640UHC-5TG144C | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP | 144   | COM   |

| LCMXO2-640UHC-6TG144C | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP | 144   | COM   |

| Date              | Version              | Section                                                                                                                                                                                                         | Change Summary                                                                                                                                                    |

|-------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2014 2.9 | Introduction         | Updated the Features section. Revised Table 1-1, MachXO2 Family<br>Selection Guide.<br>— Removed XO2-4000U data.<br>— Removed 400-ball ftBGA.<br>— Removed 25-ball WLCSP value for XO2-2000U.                   |                                                                                                                                                                   |

|                   |                      | DC and Switching<br>Characteristics                                                                                                                                                                             | Updated the Recommended Operating Conditions section. Adjusted Max. values for $V_{CC}$ and $V_{CCIO}$                                                            |

|                   |                      |                                                                                                                                                                                                                 | Updated the sysIO Recommended Operating Conditions section.<br>Adjusted Max. values for LVCMOS 3.3, LVTTL, PCI, LVDS33 and<br>LVPECL.                             |

|                   |                      | Pinout Information                                                                                                                                                                                              | Updated the Pinout Information Summary section. Removed MachXO2-4000U.                                                                                            |

|                   |                      | Ordering Information                                                                                                                                                                                            | Updated the MachXO2 Part Number Description section. Removed BG400 package.                                                                                       |

|                   |                      |                                                                                                                                                                                                                 | Updated the High-Performance Commercial Grade Devices with Volt-<br>age Regulator, Halogen Free (RoHS) Packaging section. Removed<br>LCMXO2-4000UHC part numbers. |

|                   |                      |                                                                                                                                                                                                                 | Updated the High-Performance Industrial Grade Devices with Voltage<br>Regulator, Halogen Free (RoHS) Packaging section. Removed<br>LCMXO2-4000UHC part numbers.   |

| November 2014 2.8 | Introduction         | Updated the Features section.<br>— Revised I/Os under Flexible Logic Architecture.<br>— Revised standby power under Ultra Low Power Devices.<br>— Revise input frequency range under Flexible On-Chip Clocking. |                                                                                                                                                                   |

|                   |                      | Updated Table 1-1, MachXO2 Family Selection Guide.<br>— Added XO2-4000U data.<br>— Removed HE and ZE device options for XO2-4000.<br>— Added 400-ball ftBGA.                                                    |                                                                                                                                                                   |

|                   |                      | Pinout Information                                                                                                                                                                                              | Updated the Pinout Information Summary section. Added MachXO2-4000U caBGA400 and MachXO2-7000 caBGA400.                                                           |

|                   | Ordering Information | Updated the MachXO2 Part Number Description section. Added BG400 package.                                                                                                                                       |                                                                                                                                                                   |

|                   |                      | Updated the Ordering Information section. Added MachXO2-4000U caBGA400 and MachXO2-7000 caBGA400 part numbers.                                                                                                  |                                                                                                                                                                   |

| October 2014      | 2.7                  | Ordering Information                                                                                                                                                                                            | Updated the Ultra Low Power Industrial Grade Devices, Halogen Free<br>(RoHS) Packaging section. Fixed typo in LCMXO2-2000ZE-<br>1UWG49ITR part number package.    |

|                   |                      | Architecture                                                                                                                                                                                                    | Updated the Supported Standards section. Added MIPI information to Table 2-12. Supported Input Standards and Table 2-13. Supported Output Standards.              |

|                   |                      | DC and Switching<br>Characteristics                                                                                                                                                                             | Updated the BLVDS section. Changed output impedance nominal values in Table 3-2, BLVDS DC Condition.                                                              |

|                   |                      |                                                                                                                                                                                                                 | Updated the LVPECL section. Changed output impedance nominal value in Table 3-3, LVPECL DC Condition.                                                             |

|                   |                      | Updated the sysCONFIG Port Timing Specifications section.<br>Updated INITN low time values.                                                                                                                     |                                                                                                                                                                   |

| July 2014 2.6     | 2.6                  | DC and Switching<br>Characteristics                                                                                                                                                                             | Updated sysIO Single-Ended DC Electrical Characteristics <sup>1, 2</sup> section.<br>Updated footnote 4.                                                          |

|                   |                      |                                                                                                                                                                                                                 | Updated Register-to-Register Performance section. Updated foot-<br>note.                                                                                          |

|                   |                      | Ordering Information                                                                                                                                                                                            | Updated UW49 package to UWG49 in MachXO2 Part Number Description.                                                                                                 |

|                   |                      |                                                                                                                                                                                                                 | Updated LCMXO2-2000ZE-1UWG49CTR package in Ultra Low Power Commercial Grade Devices, Halogen Free (RoHS) Packaging.                                               |