## E. Kentice Semiconductor Corporation - <u>LCMX02-4000ZE-1QN84C Datasheet</u>

Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2014                           |                                                                                 |

|--------------------------------|---------------------------------------------------------------------------------|

| Product Status                 | Active                                                                          |

| Number of LABs/CLBs            | 540                                                                             |

| Number of Logic Elements/Cells | 4320                                                                            |

| Total RAM Bits                 | 94208                                                                           |

| Number of I/O                  | 68                                                                              |

| Number of Gates                | -                                                                               |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                   |

| Mounting Type                  | Surface Mount                                                                   |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                 |

| Package / Case                 | 84-VFQFN Dual Rows, Exposed Pad                                                 |

| Supplier Device Package        | 84-QFN (7x7)                                                                    |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-4000ze-1qn84c |

|                                |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Introduction

The MachXO2 family of ultra low power, instant-on, non-volatile PLDs has six devices with densities ranging from 256 to 6864 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, User Flash Memory (UFM), Phase Locked Loops (PLLs), preengineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and timer/counter. These features allow these devices to be used in low cost, high volume consumer and system applications.

The MachXO2 devices are designed on a 65 nm non-volatile low power process. The device architecture has several features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs and oscillators dynamically. These features help manage static and dynamic power consumption resulting in low static power for all members of the family.

The MachXO2 devices are available in two versions – ultra low power (ZE) and high performance (HC and HE) devices. The ultra low power devices are offered in three speed grades –1, –2 and –3, with –3 being the fastest. Similarly, the high-performance devices are offered in three speed grades: –4, –5 and –6, with –6 being the fastest. HC devices have an internal linear voltage regulator which supports external V<sub>CC</sub> supply voltages of 3.3 V or 2.5 V. ZE and HE devices only accept 1.2 V as the external V<sub>CC</sub> supply voltage. With the exception of power supply voltage all three types of devices (ZE, HC and HE) are functionally compatible and pin compatible with each other.

The MachXO2 PLDs are available in a broad range of advanced halogen-free packages ranging from the space saving 2.5 mm x 2.5 mm WLCSP to the 23 mm x 23 mm fpBGA. MachXO2 devices support density migration within the same package. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters.

The pre-engineered source synchronous logic implemented in the MachXO2 device family supports a broad range of interface standards, including LPDDR, DDR, DDR2 and 7:1 gearing for display I/Os.

The MachXO2 devices offer enhanced I/O features such as drive strength control, slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a "per-pin" basis.

A user-programmable internal oscillator is included in MachXO2 devices. The clock output from this oscillator may be divided by the timer/counter for use as clock input in functions such as LED control, key-board scanner and similar state machines.

The MachXO2 devices also provide flexible, reliable and secure configuration from on-chip Flash memory. These devices can also configure themselves from external SPI Flash or be configured by an external master through the JTAG test access port or through the I<sup>2</sup>C port. Additionally, MachXO2 devices support dual-boot capability (using external Flash memory) and remote field upgrade (TransFR) capability.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the MachXO2 family of devices. Popular logic synthesis tools provide synthesis library support for MachXO2. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the MachXO2 device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) LatticeCORE<sup>™</sup> modules, including a number of reference designs licensed free of charge, optimized for the MachXO2 PLD family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increasing their productivity.

The logic blocks, Programmable Functional Unit (PFU) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each row has either the logic blocks or the EBR blocks. The PIO cells are located at the periphery of the device, arranged in banks. The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the MachXO2 family, the number of sysIO banks varies by device. There are different types of I/O buffers on the different banks. Refer to the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks; these blocks are found in MachXO2-640/U and larger devices. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT usage.

The MachXO2 registers in PFU and sysl/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

The MachXO2 architecture also provides up to two sysCLOCK Phase Locked Loop (PLL) blocks on MachXO2-640U, MachXO2-1200/U and larger devices. These blocks are located at the ends of the on-chip Flash block. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

MachXO2 devices provide commonly used hardened functions such as SPI controller, I<sup>2</sup>C controller and timer/ counter. MachXO2-640/U and higher density devices also provide User Flash Memory (UFM). These hardened functions and the UFM interface to the core logic and routing through a WISHBONE interface. The UFM can also be accessed through the SPI, I<sup>2</sup>C and JTAG ports.

Every device in the family has a JTAG port that supports programming and configuration of the device as well as access to the user logic. The MachXO2 devices are available for operation from 3.3 V, 2.5 V and 1.2 V power supplies, providing easy integration into the overall system.

## **PFU Blocks**

The core of the MachXO2 device consists of PFU blocks, which can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. Each PFU block consists of four interconnected slices numbered 0 to 3 as shown in Figure 2-3. Each slice contains two LUTs and two registers. There are 53 inputs and 25 outputs associated with each PFU block.

### Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In Ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/down counter with asynchronous clear

- Up/down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per-slice basis to allow fast arithmetic functions to be constructed by concatenating slices.

### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed by using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals.

MachXO2 devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in MachXO2 devices, please see TN1201, Memory Usage Guide for MachXO2 Devices.

### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                                                          | SPR 16x4 | PDPR 16x4 |  |  |  |  |

|----------------------------------------------------------|----------|-----------|--|--|--|--|

| Number of slices                                         | 3        | 3         |  |  |  |  |

| Note: SPB = Single Port RAM, PDPB = Pseudo Dual Port RAM |          |           |  |  |  |  |

ote: SPR = Single Port RAM, PDPR = Pseudo Dual

Table 2-5. sysMEM Block Configurations

| Memory Mode      | Configurations                                               |

|------------------|--------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

### Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. EBR initialization data can be loaded from the UFM. To maximize the number of UFM bits, initialize the EBRs used in your design to an all-zero pattern. Initializing to an all-zero pattern does not use up UFM bits. MachXO2 devices have been designed such that multiple EBRs share the same initialization memory space if they are initialized to the same pattern.

By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

### Memory Cascading

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

### Single, Dual, Pseudo-Dual Port and FIFO Modes

Figure 2-8 shows the five basic memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and addresses for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the memory array output.

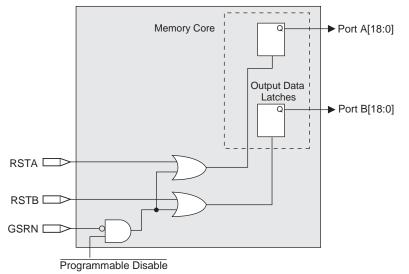

### Figure 2-9. Memory Core Reset

For further information on the sysMEM EBR block, please refer to TN1201, Memory Usage Guide for MachXO2 Devices.

### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-10. The GSR input to the EBR is always asynchronous.

### Figure 2-10. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device wake up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-10. The reset timing rules apply to the RPReset input versus the RE input and the RST input versus the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs. For more details refer to TN1201, Memory Usage Guide for MachXO2 Devices.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

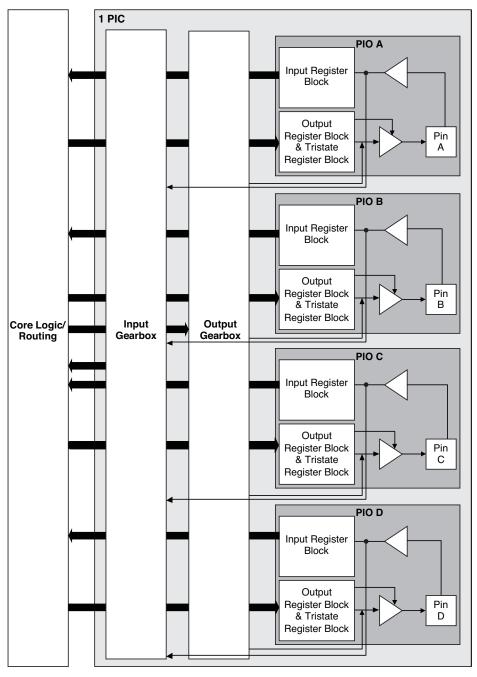

Figure 2-11. Group of Four Programmable I/O Cells

Notes:

1. Input gearbox is available only in PIC on the bottom edge of MachXO2-640U, MachXO2-1200/U and larger devices. 2. Output gearbox is available only in PIC on the top edge of MachXO2-640U, MachXO2-1200/U and larger devices.

### Table 2-13. Supported Output Standards

| Output Standard                 | V <sub>CCIO</sub> (Typ.) |

|---------------------------------|--------------------------|

| Single-Ended Interfaces         |                          |

| LVTTL                           | 3.3                      |

| LVCMOS33                        | 3.3                      |

| LVCMOS25                        | 2.5                      |

| LVCMOS18                        | 1.8                      |

| LVCMOS15                        | 1.5                      |

| LVCMOS12                        | 1.2                      |

| LVCMOS33, Open Drain            |                          |

| LVCMOS25, Open Drain            |                          |

| LVCMOS18, Open Drain            |                          |

| LVCMOS15, Open Drain            |                          |

| LVCMOS12, Open Drain            |                          |

| PCI33                           | 3.3                      |

| SSTL25 (Class I)                | 2.5                      |

| SSTL18 (Class I)                | 1.8                      |

| HSTL18(Class I)                 | 1.8                      |

| Differential Interfaces         |                          |

| LVDS <sup>1, 2</sup>            | 2.5, 3.3                 |

| BLVDS, MLVDS, RSDS <sup>2</sup> | 2.5                      |

| LVPECL <sup>2</sup>             | 3.3                      |

| MIPI <sup>2</sup>               | 2.5                      |

| Differential SSTL18             | 1.8                      |

| Differential SSTL25             | 2.5                      |

| Differential HSTL18             | 1.8                      |

1. MachXO2-640U, MachXO2-1200/U and larger devices have dedicated LVDS buffers. 2. These interfaces can be emulated with external resistors in all devices.

### sysIO Buffer Banks

The numbers of banks vary between the devices of this family. MachXO2-1200U, MachXO2-2000/U and higher density devices have six I/O banks (one bank on the top, right and bottom side and three banks on the left side). The MachXO2-1200 and lower density devices have four banks (one bank per side). Figures 2-18 and 2-19 show the sysIO banks and their associated supplies for all devices.

# MachXO2 Family Data Sheet DC and Switching Characteristics

### March 2017

### Data Sheet DS1035

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                               | MachXO2 ZE/HE (1.2 V) | MachXO2 HC (2.5 V / 3.3 V) |

|-----------------------------------------------|-----------------------|----------------------------|

| Supply Voltage V <sub>CC</sub>                | –0.5 V to 1.32 V      | –0.5 V to 3.75 V           |

| Output Supply Voltage V <sub>CCIO</sub>       | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| I/O Tri-state Voltage Applied <sup>4, 5</sup> | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| Dedicated Input Voltage Applied <sup>4</sup>  | –0.5 V to 3.75 V      | –0.5 V to 3.75 V           |

| Storage Temperature (Ambient)                 | –55 °C to 125 °C      | –55 °C to 125 °C           |

| Junction Temperature (T <sub>J</sub> )        | –40 °C to 125 °C      | –40 °C to 125 °C           |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

5. The dual function  $I^2C$  pins SCL and SDA are limited to -0.25 V to 3.75 V or to -0.3 V with a duration of <20 ns.

## **Recommended Operating Conditions**<sup>1</sup>

| Symbol                                                             | Parameter                                     | Min.  | Max. | Units |

|--------------------------------------------------------------------|-----------------------------------------------|-------|------|-------|

| V <sub>CC</sub> <sup>1</sup> Core Supply Voltage for 1.2 V Devices |                                               | 1.14  | 1.26 | V     |

| VCC                                                                | Core Supply Voltage for 2.5 V / 3.3 V Devices | 2.375 | 3.6  | V     |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup>                               | I/O Driver Supply Voltage                     | 1.14  | 3.6  | V     |

| t <sub>JCOM</sub>                                                  | Junction Temperature Commercial Operation     | 0     | 85   | °C    |

| t <sub>JIND</sub>                                                  | Junction Temperature Industrial Operation     | -40   | 100  | °C    |

1. Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both the same voltage, they must also be the same supply.

2. See recommended voltages by I/O standard in subsequent table.

3. V<sub>CCIO</sub> pins of unused I/O banks should be connected to the V<sub>CC</sub> power supply on boards.

## **Power Supply Ramp Rates**<sup>1</sup>

| Symbol            | Parameter                                       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------------------|------|------|------|-------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies. | 0.01 |      | 100  | V/ms  |

1. Assumes monotonic ramp rates.

<sup>© 2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Static Supply Current – HC/HE Devices<sup>1, 2, 3, 6</sup>

| Symbol | Parameter                                       | Device         | Typ.⁴ | Units |

|--------|-------------------------------------------------|----------------|-------|-------|

|        |                                                 | LCMXO2-256HC   | 1.15  | mA    |

|        |                                                 | LCMXO2-640HC   | 1.84  | mA    |

|        |                                                 | LCMXO2-640UHC  | 3.48  | mA    |

|        |                                                 | LCMXO2-1200HC  | 3.49  | mA    |

|        |                                                 | LCMXO2-1200UHC | 4.80  | mA    |

|        | Core Power Supply                               | LCMXO2-2000HC  | 4.80  | mA    |

| ICC    |                                                 | LCMXO2-2000UHC | 8.44  | mA    |

|        |                                                 | LCMXO2-4000HC  | 8.45  | mA    |

|        |                                                 | LCMXO2-7000HC  | 12.87 | mA    |

|        |                                                 | LCMXO2-2000HE  | 1.39  | mA    |

|        |                                                 | LCMXO2-4000HE  | 2.55  | mA    |

|        |                                                 | LCMXO2-7000HE  | 4.06  | mA    |

| Іссю   | Bank Power Supply⁵<br>V <sub>CCIO</sub> = 2.5 V | All devices    | 0     | mA    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

2. Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip oscillator is off, on-chip PLL is off.

3. Frequency = 0 MHz.

4.  $T_J = 25$  °C, power supplies at nominal voltage.

5. Does not include pull-up/pull-down.

6. To determine the MachXO2 peak start-up current data, use the Power Calculator tool.

## Programming and Erase Flash Supply Current – HC/HE Devices<sup>1, 2, 3, 4</sup>

| Symbol            | Parameter                      | Device                          | Typ.⁵          | Units |    |

|-------------------|--------------------------------|---------------------------------|----------------|-------|----|

|                   |                                | LCMXO2-256HC                    | 14.6           | mA    |    |

|                   |                                | LCMXO2-640HC                    | 16.1           | mA    |    |

|                   |                                | LCMXO2-640UHC                   | 18.8           | mA    |    |

|                   |                                | LCMXO2-1200HC                   | 18.8           | mA    |    |

|                   |                                | LCMXO2-1200UHC                  | 22.1           | mA    |    |

|                   |                                | LCMXO2-2000HC                   | 22.1           | mA    |    |

| I <sub>CC</sub>   | Core Power Supply              | LCMXO2-2000UHC                  | 26.8           | mA    |    |

|                   |                                | LCMXO2-4000HC                   | 26.8           | mA    |    |

|                   | LCMXO2-7000HC                  | 33.2                            | mA             |       |    |

|                   |                                | LCMXO2-2000HE                   | 18.3           | mA    |    |

|                   |                                | LCMXO2-2000UHE<br>LCMXO2-4000HE | LCMXO2-2000UHE | 20.4  | mA |

|                   |                                |                                 | LCMXO2-4000HE  | 20.4  | mA |

|                   |                                | LCMXO2-7000HE                   | 23.9           | mA    |    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>6</sup> | All devices                     | 0              | mA    |    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

2. Assumes all inputs are held at  $V_{CCIO}$  or GND and all outputs are tri-stated.

3. Typical user pattern.

4. JTAG programming is at 25 MHz.

5.  $T_J = 25$  °C, power supplies at nominal voltage.

6. Per bank.  $V_{CCIO} = 2.5$  V. Does not include pull-up/pull-down.

## MachXO2 External Switching Characteristics – HC/HE Devices<sup>1, 2, 3, 4, 5, 6, 7</sup>

|                                    |                                               |                                    | -     | 6    | -     | 5    | -     | 4    |       |

|------------------------------------|-----------------------------------------------|------------------------------------|-------|------|-------|------|-------|------|-------|

| Parameter                          | Description                                   | Device                             | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| Clocks                             |                                               |                                    |       |      |       |      |       |      |       |

| Primary Clo                        | cks                                           |                                    |       |      |       |      |       |      |       |

| f <sub>MAX_PRI</sub> <sup>8</sup>  | Frequency for Primary Clock<br>Tree           | All MachXO2 devices                | _     | 388  |       | 323  | _     | 269  | MHz   |

| t <sub>W_PRI</sub>                 | Clock Pulse Width for Primary Clock           | All MachXO2 devices                | 0.5   | _    | 0.6   | _    | 0.7   | _    | ns    |

|                                    |                                               | MachXO2-256HC-HE                   |       | 912  |       | 939  | —     | 975  | ps    |

|                                    |                                               | MachXO2-640HC-HE                   |       | 844  |       | 871  | —     | 908  | ps    |

|                                    | Primary Clock Skew Within a                   | MachXO2-1200HC-HE                  |       | 868  |       | 902  | —     | 951  | ps    |

| t <sub>SKEW_PRI</sub>              | Device                                        | MachXO2-2000HC-HE                  |       | 867  |       | 897  | —     | 941  | ps    |

|                                    |                                               | MachXO2-4000HC-HE                  |       | 865  |       | 892  | —     | 931  | ps    |

|                                    |                                               | MachXO2-7000HC-HE                  |       | 902  |       | 942  | —     | 989  | ps    |

| Edge Clock                         |                                               |                                    |       |      |       |      |       |      | I     |

| f <sub>MAX_EDGE</sub> <sup>8</sup> | Frequency for Edge Clock                      | MachXO2-1200 and<br>larger devices | _     | 400  | _     | 333  | _     | 278  | MHz   |

| Pin-LUT-Pin                        | Propagation Delay                             | I                                  |       |      | 1     |      |       |      |       |

| t <sub>PD</sub>                    | Best case propagation delay through one LUT-4 | All MachXO2 devices                | _     | 6.72 | _     | 6.96 | _     | 7.24 | ns    |

| General I/O                        | Pin Parameters (Using Primary                 | y Clock without PLL)               |       |      | 1     |      |       |      |       |

|                                    |                                               | MachXO2-256HC-HE                   |       | 7.13 |       | 7.30 |       | 7.57 | ns    |

|                                    |                                               | MachXO2-640HC-HE                   |       | 7.15 |       | 7.30 | —     | 7.57 | ns    |

|                                    | Clock to Output – PIO Output                  | MachXO2-1200HC-HE                  |       | 7.44 |       | 7.64 |       | 7.94 | ns    |

| t <sub>co</sub>                    | Register                                      | MachXO2-2000HC-HE                  |       | 7.46 |       | 7.66 |       | 7.96 | ns    |

|                                    |                                               | MachXO2-4000HC-HE                  |       | 7.51 |       | 7.71 | —     | 8.01 | ns    |

|                                    |                                               | MachXO2-7000HC-HE                  |       | 7.54 |       | 7.75 |       | 8.06 | ns    |

|                                    |                                               | MachXO2-256HC-HE                   | -0.06 |      | -0.06 |      | -0.06 | _    | ns    |

|                                    |                                               | MachXO2-640HC-HE                   | -0.06 |      | -0.06 | _    | -0.06 | _    | ns    |

|                                    | Clock to Data Setup – PIO                     | MachXO2-1200HC-HE                  | -0.17 |      | -0.17 | _    | -0.17 | _    | ns    |

| t <sub>SU</sub>                    | Input Register                                | MachXO2-2000HC-HE                  | -0.20 |      | -0.20 | _    | -0.20 | _    | ns    |

|                                    |                                               | MachXO2-4000HC-HE                  | -0.23 | _    | -0.23 | _    | -0.23 | _    | ns    |

|                                    |                                               | MachXO2-7000HC-HE                  | -0.23 | _    | -0.23 | _    | -0.23 | _    | ns    |

|                                    |                                               | MachXO2-256HC-HE                   | 1.75  | —    | 1.95  | —    | 2.16  | —    | ns    |

|                                    |                                               | MachXO2-640HC-HE                   | 1.75  | _    | 1.95  | _    | 2.16  | _    | ns    |

|                                    | Clock to Data Hold – PIO Input                | MachXO2-1200HC-HE                  | 1.88  | _    | 2.12  | _    | 2.36  | _    | ns    |

| t <sub>H</sub>                     | Register                                      | MachXO2-2000HC-HE                  | 1.89  | _    | 2.13  | _    | 2.37  | _    | ns    |

|                                    |                                               | MachXO2-4000HC-HE                  | 1.94  |      | 2.18  |      | 2.43  | _    | ns    |

|                                    |                                               | MachXO2-7000HC-HE                  | 1.98  | _    | 2.23  | _    | 2.49  | _    | ns    |

**Over Recommended Operating Conditions**

## MachXO2 External Switching Characteristics – ZE Devices<sup>1, 2, 3, 4, 5, 6, 7</sup>

| MAX_PRI Tree                                                                                    | Description                       | Device<br>All MachXO2 devices      | Min.  | Max.  | Min.  | Max.  | Min.  | Max.  | Units |

|-------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Frimary Clocks       f <sub>MAX_PRI</sub> <sup>®</sup> Frequer<br>Tree       turner     Clock P |                                   | All MachXO2 devices                |       |       |       |       |       |       |       |

| f <sub>MAX_PRI</sub> <sup>8</sup> Frequer<br>Tree<br>Clock P                                    |                                   | All MachXO2 devices                |       |       |       |       |       |       |       |

| Tree Clock P                                                                                    |                                   | All MachXO2 devices                |       |       |       |       |       |       |       |

|                                                                                                 | ulse Width for Primary            |                                    | _     | 150   | _     | 125   | _     | 104   | MHz   |

|                                                                                                 |                                   | All MachXO2 devices                | 1.00  | _     | 1.20  | _     | 1.40  | _     | ns    |

|                                                                                                 |                                   | MachXO2-256ZE                      | _     | 1250  | _     | 1272  | _     | 1296  | ps    |

|                                                                                                 |                                   | MachXO2-640ZE                      |       | 1161  | _     | 1183  | _     | 1206  | ps    |

| . Primarv                                                                                       | Clock Skew Within a               | MachXO2-1200ZE                     | _     | 1213  | _     | 1267  | _     | 1322  | ps    |

| t <sub>SKEW_PRI</sub> Device                                                                    |                                   | MachXO2-2000ZE                     | _     | 1204  | _     | 1250  | —     | 1296  | ps    |

|                                                                                                 |                                   | MachXO2-4000ZE                     |       | 1195  |       | 1233  | _     | 1269  | ps    |

|                                                                                                 |                                   | MachXO2-7000ZE                     | _     | 1243  | _     | 1268  | —     | 1296  | ps    |

| Edge Clock                                                                                      |                                   | 1                                  | I     | L     |       | L     |       | L     |       |

| f <sub>MAX_EDGE<sup>8</sup> Frequer</sub>                                                       | ncy for Edge Clock                | MachXO2-1200 and<br>larger devices | _     | 210   | _     | 175   | _     | 146   | MHz   |

| Pin-LUT-Pin Propaga                                                                             | tion Delay                        |                                    |       |       |       |       |       |       |       |

| t <sub>PD</sub> Best ca<br>through                                                              | se propagation delay<br>one LUT-4 | All MachXO2 devices                | _     | 9.35  | _     | 9.78  | _     | 10.21 | ns    |

| General I/O Pin Parar                                                                           | meters (Using Primary             | Clock without PLL)                 |       |       |       |       |       |       |       |

|                                                                                                 |                                   | MachXO2-256ZE                      |       | 10.46 |       | 10.86 |       | 11.25 | ns    |

|                                                                                                 |                                   | MachXO2-640ZE                      |       | 10.52 |       | 10.92 |       | 11.32 | ns    |

| L Clock to                                                                                      | o Output – PIO Output             | MachXO2-1200ZE                     | _     | 11.24 | _     | 11.68 | _     | 12.12 | ns    |

| t <sub>CO</sub> Registe                                                                         |                                   | MachXO2-2000ZE                     | _     | 11.27 |       | 11.71 |       | 12.16 | ns    |

|                                                                                                 |                                   | MachXO2-4000ZE                     | _     | 11.28 |       | 11.78 |       | 12.28 | ns    |

|                                                                                                 |                                   | MachXO2-7000ZE                     | _     | 11.22 | _     | 11.76 | _     | 12.30 | ns    |

|                                                                                                 |                                   | MachXO2-256ZE                      | -0.21 |       | -0.21 |       | -0.21 | _     | ns    |

|                                                                                                 |                                   | MachXO2-640ZE                      | -0.22 |       | -0.22 |       | -0.22 | _     | ns    |

| L Clock to                                                                                      | Data Setup – PIO                  | MachXO2-1200ZE                     | -0.25 |       | -0.25 |       | -0.25 |       | ns    |

| t <sub>SU</sub> Input Re                                                                        |                                   | MachXO2-2000ZE                     | -0.27 |       | -0.27 |       | -0.27 |       | ns    |

|                                                                                                 |                                   | MachXO2-4000ZE                     | -0.31 |       | -0.31 |       | -0.31 |       | ns    |

|                                                                                                 |                                   | MachXO2-7000ZE                     | -0.33 |       | -0.33 |       | -0.33 | _     | ns    |

|                                                                                                 |                                   | MachXO2-256ZE                      | 3.96  | —     | 4.25  | _     | 4.65  | _     | ns    |

|                                                                                                 |                                   | MachXO2-640ZE                      | 4.01  | _     | 4.31  | _     | 4.71  | _     | ns    |

| Lock to                                                                                         | Data Hold – PIO Input             | MachXO2-1200ZE                     | 3.95  | _     | 4.29  | _     | 4.73  | _     | ns    |

| t <sub>H</sub> Registe                                                                          |                                   | MachXO2-2000ZE                     | 3.94  | _     | 4.29  | _     | 4.74  | _     | ns    |

|                                                                                                 |                                   | MachXO2-4000ZE                     | 3.96  | _     | 4.36  | _     | 4.87  | _     | ns    |

|                                                                                                 |                                   | MachXO2-7000ZE                     | 3.93  | _     | 4.37  |       | 4.91  | _     | ns    |

**Over Recommended Operating Conditions**

## sysCLOCK PLL Timing

| Parameter                          | Descriptions                                   | Conditions                              | Min.   | Max.  | Units  |  |

|------------------------------------|------------------------------------------------|-----------------------------------------|--------|-------|--------|--|

| f <sub>IN</sub>                    | Input Clock Frequency (CLKI, CLKFB)            |                                         | 7      | 400   | MHz    |  |

| fout                               | Output Clock Frequency (CLKOP, CLKOS, CLKOS2)  |                                         | 1.5625 | 400   | MHz    |  |

| fout2                              | Output Frequency (CLKOS3 cascaded from CLKOS2) |                                         | 0.0122 | 400   | MHz    |  |

| f <sub>VCO</sub>                   | PLL VCO Frequency                              |                                         | 200    | 800   | MHz    |  |

| f <sub>PFD</sub>                   | Phase Detector Input Frequency                 |                                         | 7      | 400   | MHz    |  |

| AC Characteri                      | stics                                          | •                                       |        |       |        |  |

| t <sub>DT</sub>                    | Output Clock Duty Cycle                        | Without duty trim selected <sup>3</sup> | 45     | 55    | %      |  |

| t <sub>DT_TRIM</sub> <sup>7</sup>  | Edge Duty Trim Accuracy                        |                                         | -75    | 75    | %      |  |

| t <sub>PH</sub> ⁴                  | Output Phase Accuracy                          |                                         | -6     | 6     | %      |  |

|                                    | Output Clask Daviad Litter                     | f <sub>OUT</sub> > 100 MHz              | —      | 150   | ps p-p |  |

|                                    | Output Clock Period Jitter                     | f <sub>OUT</sub> < 100 MHz              | —      | 0.007 | UIPP   |  |

|                                    | Output Olaski Ousla ta susla littari           | f <sub>OUT</sub> > 100 MHz              | —      | 180   | ps p-p |  |

|                                    | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> < 100 MHz              | _      | 0.009 | UIPP   |  |

| . 18                               | Output Cleak Dhoose litter                     | f <sub>PFD</sub> > 100 MHz              | _      | 160   | ps p-p |  |

| t <sub>OPJIT</sub> <sup>1, 8</sup> | Output Clock Phase Jitter                      | f <sub>PFD</sub> < 100 MHz              | _      | 0.011 | UIPP   |  |

|                                    |                                                | f <sub>OUT</sub> > 100 MHz              | _      | 230   | ps p-p |  |

|                                    | Output Clock Period Jitter (Fractional-N)      | f <sub>OUT</sub> < 100 MHz              | —      | 0.12  | UIPP   |  |

|                                    | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p |  |

|                                    | (Fractional-N)                                 | f <sub>OUT</sub> < 100 MHz              | —      | 0.12  | UIPP   |  |

| t <sub>SPO</sub>                   | Static Phase Offset                            | Divider ratio = integer                 | -120   | 120   | ps     |  |

| t <sub>W</sub>                     | Output Clock Pulse Width                       | At 90% or 10% <sup>3</sup>              | 0.9    | —     | ns     |  |

| tLOCK <sup>2, 5</sup>              | PLL Lock-in Time                               |                                         | —      | 15    | ms     |  |

| t <sub>UNLOCK</sub>                | PLL Unlock Time                                |                                         | —      | 50    | ns     |  |

| <b>•</b> 6                         | Innut Clask Daviad Littar                      | f <sub>PFD</sub> ≥ 20 MHz               | —      | 1,000 | ps p-p |  |

| t <sub>IPJIT</sub> <sup>6</sup>    | Input Clock Period Jitter                      | f <sub>PFD</sub> < 20 MHz               | —      | 0.02  | UIPP   |  |

| t <sub>HI</sub>                    | Input Clock High Time                          | 90% to 90%                              | 0.5    | —     | ns     |  |

| t <sub>LO</sub>                    | Input Clock Low Time                           | 10% to 10%                              | 0.5    | —     | ns     |  |

| t <sub>STABLE</sub> <sup>5</sup>   | STANDBY High to PLL Stable                     |                                         | _      | 15    | ms     |  |

| t <sub>RST</sub>                   | RST/RESETM Pulse Width                         |                                         | 1      |       | ns     |  |

| t <sub>RSTREC</sub>                | RST Recovery Time                              |                                         | 1      |       | ns     |  |

| t <sub>RST_DIV</sub>               | RESETC/D Pulse Width                           |                                         | 10     |       | ns     |  |

| t <sub>RSTREC_DIV</sub>            | RESETC/D Recovery Time                         |                                         | 1      |       | ns     |  |

|                                    | PHASESTEP Setup Time                           |                                         | 10     |       | ns     |  |

### **Over Recommended Operating Conditions**

## Signal Descriptions (Cont.)

| Signal Name | I/O | Descriptions                                                                                                                                                                                                  |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INITN       | I/O | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, or when reserved as INITn in user mode, this pin has an active pull-up.                                                   |

| DONE        | I/O | Open Drain pin. Indicates that the configuration sequence is complete, and the start-up sequence is in progress. During configuration, or when reserved as DONE in user mode, this pin has an active pull-up. |

| MCLK/CCLK   | I/O | Input Configuration Clock for configuring an FPGA in Slave SPI mode. Output Configuration Clock for configuring an FPGA in SPI and SPIm configuration modes.                                                  |

| SN          | I   | Slave SPI active low chip select input.                                                                                                                                                                       |

| CSSPIN      | I/O | Master SPI active low chip select output.                                                                                                                                                                     |

| SI/SPISI    | I/O | Slave SPI serial data input and master SPI serial data output.                                                                                                                                                |

| SO/SPISO    | I/O | Slave SPI serial data output and master SPI serial data input.                                                                                                                                                |

| SCL         | I/O | Slave I <sup>2</sup> C clock input and master I <sup>2</sup> C clock output.                                                                                                                                  |

| SDA         | I/O | Slave I <sup>2</sup> C data input and master I <sup>2</sup> C data output.                                                                                                                                    |

## **Pinout Information Summary**

|                                                           |                        | Ма                     | achXO2-2    | 256         |              | MachXO2-640            |             |              | MachXO2-640L |  |

|-----------------------------------------------------------|------------------------|------------------------|-------------|-------------|--------------|------------------------|-------------|--------------|--------------|--|

|                                                           | 32<br>QFN <sup>1</sup> | 48<br>QFN <sup>3</sup> | 64<br>ucBGA | 100<br>TQFP | 132<br>csBGA | 48<br>QFN <sup>3</sup> | 100<br>TQFP | 132<br>csBGA | 144 TQFP     |  |

| General Purpose I/O per Bank                              |                        |                        |             |             |              |                        |             | •            | •            |  |

| Bank 0                                                    | 8                      | 10                     | 9           | 13          | 13           | 10                     | 18          | 19           | 27           |  |

| Bank 1                                                    | 2                      | 10                     | 12          | 14          | 14           | 10                     | 20          | 20           | 26           |  |

| Bank 2                                                    | 9                      | 10                     | 11          | 14          | 14           | 10                     | 20          | 20           | 28           |  |

| Bank 3                                                    | 2                      | 10                     | 12          | 14          | 14           | 10                     | 20          | 20           | 26           |  |

| Bank 4                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0            |  |

| Bank 5                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0            |  |

| Total General Purpose Single Ended I/O                    | 21                     | 40                     | 44          | 55          | 55           | 40                     | 78          | 79           | 107          |  |

| Differential I/O per Bank                                 |                        |                        |             |             |              |                        |             |              |              |  |

| Bank 0                                                    | 4                      | 5                      | 5           | 7           | 7            | 5                      | 9           | 10           | 14           |  |

| Bank 1                                                    | 1                      | 5                      | 6           | 7           | 7            | 5                      | 10          | 10           | 13           |  |

| Bank 2                                                    | 4                      | 5                      | 5           | 7           | 7            | 5                      | 10          | 10           | 14           |  |

| Bank 3                                                    | 1                      | 5                      | 6           | 7           | 7            | 5                      | 10          | 10           | 13           |  |

| Bank 4                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0            |  |

| Bank 5                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0            |  |

| Total General Purpose Differential I/O                    | 10                     | 20                     | 22          | 28          | 28           | 20                     | 39          | 40           | 54           |  |

| Dual Function I/O                                         | 22                     | 25                     | 27          | 29          | 29           | 25                     | 29          | 29           | 33           |  |

| High-speed Differential I/O                               |                        | 1                      |             |             |              |                        |             | 1            |              |  |

| Bank 0                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 7            |  |

| Gearboxes                                                 |                        |                        |             |             |              |                        |             |              | •            |  |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 7            |  |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 7            |  |

| DQS Groups                                                |                        |                        |             |             |              |                        |             |              |              |  |

| Bank 1                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 2            |  |

| VCCIO Pins                                                |                        |                        |             |             |              |                        |             |              |              |  |

| Bank 0                                                    | 2                      | 2                      | 2           | 2           | 2            | 2                      | 2           | 2            | 3            |  |

| Bank 1                                                    | 1                      | 1                      | 2           | 2           | 2            | 1                      | 2           | 2            | 3            |  |

| Bank 2                                                    | 2                      | 2                      | 2           | 2           | 2            | 2                      | 2           | 2            | 3            |  |

| Bank 3                                                    | 1                      | 1                      | 2           | 2           | 2            | 1                      | 2           | 2            | 3            |  |

| Bank 4                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0            |  |

| Bank 5                                                    | 0                      | 0                      | 0           | 0           | 0            | 0                      | 0           | 0            | 0            |  |

| VCC                                                       | 2                      | 2                      | 2           | 2           | 2            | 2                      | 2           | 2            | 4            |  |

| GND <sup>2</sup>                                          | 2                      | 1                      | 8           | 8           | 8            | 1                      | 8           | 10           | 12           |  |

| NC                                                        | 0                      | 0                      | 1           | 26          | 58           | 0                      | 3           | 32           | 8            |  |

| Reserved for Configuration                                | 1                      | 1                      | 1           | 1           | 1            | 1                      | 1           | 1            | 1            |  |

|                                                           |                        |                        |             |             |              |                        |             |              |              |  |

1. Lattice recommends soldering the central thermal pad onto the top PCB ground for improved thermal resistance.

2. For 48 QFN package, exposed die pad is the device ground.

3. 48-pin QFN information is 'Advanced'.

|                                                            |          | MachXO2-1200U |          |          |                     |           |

|------------------------------------------------------------|----------|---------------|----------|----------|---------------------|-----------|

|                                                            | 100 TQFP | 132 csBGA     | 144 TQFP | 25 WLCSP | 32 QFN <sup>1</sup> | 256 ftBGA |

| General Purpose I/O per Bank                               | •        |               |          |          |                     |           |

| Bank 0                                                     | 18       | 25            | 27       | 11       | 9                   | 50        |

| Bank 1                                                     | 21       | 26            | 26       | 0        | 2                   | 52        |

| Bank 2                                                     | 20       | 28            | 28       | 7        | 9                   | 52        |

| Bank 3                                                     | 20       | 25            | 26       | 0        | 2                   | 16        |

| Bank 4                                                     | 0        | 0             | 0        | 0        | 0                   | 16        |

| Bank 5                                                     | 0        | 0             | 0        | 0        | 0                   | 20        |

| Total General Purpose Single Ended I/O                     | 79       | 104           | 107      | 18       | 22                  | 206       |

| Differential I/O per Bank                                  |          |               |          |          |                     |           |

| Bank 0                                                     | 9        | 13            | 14       | 5        | 4                   | 25        |

| Bank 1                                                     | 10       | 13            | 13       | 0        | 1                   | 26        |

| Bank 2                                                     | 10       | 14            | 14       | 2        | 4                   | 26        |

| Bank 3                                                     | 10       | 12            | 13       | 0        | 1                   | 8         |

| Bank 4                                                     | 0        | 0             | 0        | 0        | 0                   | 8         |

| Bank 5                                                     | 0        | 0             | 0        | 0        | 0                   | 10        |

| Total General Purpose Differential I/O                     | 39       | 52            | 54       | 7        | 10                  | 103       |

| Dual Function I/O                                          | 31       | 33            | 33       | 18       | 22                  | 33        |

| High-speed Differential I/O                                |          |               |          |          |                     |           |

| Bank 0                                                     | 4        | 7             | 7        | 0        | 0                   | 14        |

| Gearboxes                                                  |          |               |          |          |                     |           |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0)  | 4        | 7             | 7        | 0        | 0                   | 14        |

| Number of 7:1 or 8:1 Input Gearbox Avail-<br>able (Bank 2) | 5        | 7             | 7        | 0        | 2                   | 14        |

| DQS Groups                                                 |          |               |          |          |                     |           |

| Bank 1                                                     | 1        | 2             | 2        | 0        | 0                   | 2         |

| VCCIO Pins                                                 |          |               |          |          |                     |           |

| Bank 0                                                     | 2        | 3             | 3        | 1        | 2                   | 4         |

| Bank 1                                                     | 2        | 3             | 3        | 0        | 1                   | 4         |

| Bank 2                                                     | 2        | 3             | 3        | 1        | 2                   | 4         |

| Bank 3                                                     | 3        | 3             | 3        | 0        | 1                   | 1         |

| Bank 4                                                     | 0        | 0             | 0        | 0        | 0                   | 2         |

| Bank 5                                                     | 0        | 0             | 0        | 0        | 0                   | 1         |

| VCC                                                        | 2        | 4             | 4        | 2        | 2                   | 8         |

| GND                                                        | 8        | 10            | 12       | 2        | 2                   | 24        |

| NC                                                         | 1        | 1             | 8        | 0        | 0                   | 1         |

| Reserved for Configuration                                 | 1        | 1             | 1        | 1        | 1                   | 1         |

| Total Count of Bonded Pins                                 | 100      | 132           | 144      | 25       | 32                  | 256       |

| 1. Lattice recommends soldering the centra                 |          |               |          |          |                     |           |

1. Lattice recommends soldering the central thermal pad onto the top PCB ground for improved thermal resistance.

|                                                           | MachXO2-4000 |              |             |              |              |              |              |              |

|-----------------------------------------------------------|--------------|--------------|-------------|--------------|--------------|--------------|--------------|--------------|

|                                                           | 84<br>QFN    | 132<br>csBGA | 144<br>TQFP | 184<br>csBGA | 256<br>caBGA | 256<br>ftBGA | 332<br>caBGA | 484<br>fpBGA |

| General Purpose I/O per Bank                              |              |              |             |              |              |              |              |              |

| Bank 0                                                    | 27           | 25           | 27          | 37           | 50           | 50           | 68           | 70           |

| Bank 1                                                    | 10           | 26           | 29          | 37           | 52           | 52           | 68           | 68           |

| Bank 2                                                    | 22           | 28           | 29          | 39           | 52           | 52           | 70           | 72           |

| Bank 3                                                    | 0            | 7            | 9           | 10           | 16           | 16           | 24           | 24           |

| Bank 4                                                    | 9            | 8            | 10          | 12           | 16           | 16           | 16           | 16           |

| Bank 5                                                    | 0            | 10           | 10          | 15           | 20           | 20           | 28           | 28           |

| Total General Purpose Single Ended I/O                    | 68           | 104          | 114         | 150          | 206          | 206          | 274          | 278          |

| Differential I/O per Bank                                 |              |              |             |              |              |              |              |              |

| Bank 0                                                    | 13           | 13           | 14          | 18           | 25           | 25           | 34           | 35           |

| Bank 1                                                    | 4            | 13           | 14          | 18           | 26           | 26           | 34           | 34           |

| Bank 2                                                    | 11           | 14           | 14          | 19           | 26           | 26           | 35           | 36           |

| Bank 3                                                    | 0            | 3            | 4           | 4            | 8            | 8            | 12           | 12           |

| Bank 4                                                    | 4            | 4            | 5           | 6            | 8            | 8            | 8            | 8            |

| Bank 5                                                    | 0            | 5            | 5           | 7            | 10           | 10           | 14           | 14           |

| Total General Purpose Differential I/O                    | 32           | 52           | 56          | 72           | 103          | 103          | 137          | 139          |

| Dual Function I/O                                         | 28           | 37           | 37          | 37           | 37           | 37           | 37           | 37           |

| High-speed Differential I/O                               | •            |              |             | •            |              |              | 1            |              |

| Bank 0                                                    | 8            | 8            | 9           | 8            | 18           | 18           | 18           | 18           |

| Gearboxes                                                 | T            | 1            |             | T            | 1            | (            | 1            | n            |

| Number of 7:1 or 8:1 Output Gearbox<br>Available (Bank 0) | 8            | 8            | 9           | 9            | 18           | 18           | 18           | 18           |

| Number of 7:1 or 8:1 Input Gearbox<br>Available (Bank 2)  | 11           | 14           | 14          | 12           | 18           | 18           | 18           | 18           |

| DQS Groups                                                |              |              |             |              |              |              |              |              |

| Bank 1                                                    | 1            | 2            | 2           | 2            | 2            | 2            | 2            | 2            |

| VCCIO Pins                                                |              |              |             |              |              |              |              |              |

| Bank 0                                                    | 3            | 3            | 3           | 3            | 4            | 4            | 4            | 10           |

| Bank 1                                                    | 1            | 3            | 3           | 3            | 4            | 4            | 4            | 10           |

| Bank 2                                                    | 2            | 3            | 3           | 3            | 4            | 4            | 4            | 10           |

| Bank 3                                                    | 1            | 1            | 1           | 1            | 1            | 1            | 2            | 3            |

| Bank 4                                                    | 1            | 1            | 1           | 1            | 2            | 2            | 1            | 4            |

| Bank 5                                                    | 1            | 1            | 1           | 1            | 1            | 1            | 2            | 3            |

| VCC                                                       | 4            | 4            | 4           | 4            | 8            | 8            | 8            | 12           |

| GND                                                       | 4            | 10           | 12          | 16           | 24           | 24           | 27           | 48           |

| NC                                                        | 1            | 1            | 1           | 1            | 1            | 1            | 5            | 105          |

| Reserved for configuration                                | 1            | 1            | 1           | 1            | 1            | 1            | 1            | 1            |

| Total Count of Bonded Pins                                | 84           | 132          | 144         | 184          | 256          | 256          | 332          | 484          |

## **For Further Information**

For further information regarding logic signal connections for various packages please refer to the MachXO2 Device Pinout Files.

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Users must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Thermal Management document to find the device/package specific thermal values.

### For Further Information

For further information regarding Thermal Management, refer to the following:

- Thermal Management document

- TN1198, Power Estimation and Management for MachXO2 Devices

- The Power Calculator tool is included with the Lattice design tools, or as a standalone download from www.latticesemi.com/software

# High Performance Industrial Grade Devices Without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100I  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-5TG100I  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-6TG100I  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-4MG132I  | 2112 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-5MG132I  | 2112 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-6MG132I  | 2112 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-4TG144I  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-5TG144I  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-6TG144I  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-4BG256I  | 2112 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-5BG256I  | 2112 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-6BG256I  | 2112 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-4FTG256I | 2112 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HE-5FTG256I | 2112 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HE-6FTG256I | 2112 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484I | 2112 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHE-5FG484I | 2112 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHE-6FG484I | 2112 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HE-4MG132I  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-5MG132I  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-6MG132I  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-4TG144I  | 4320 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-5TG144I  | 4320 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-6TG144I  | 4320 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-4MG184I  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-5MG184I  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-6MG184I  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-4BG256I  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-5BG256I  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-6BG256I  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-4FTG256I | 4320 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-5FTG256I | 4320 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-6FTG256I | 4320 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-4BG332I  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-5BG332I  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-6BG332I  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-4FG484I  | 4320 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | IND   |