# E. Kentlice Semiconductor Corporation - <u>LCMXO2-640UHC-4TG144I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2 0 0 0 0                      |                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------|

| Product Status                 | Active                                                                           |

| Number of LABs/CLBs            | 80                                                                               |

| Number of Logic Elements/Cells | 640                                                                              |

| Total RAM Bits                 | 65536                                                                            |

| Number of I/O                  | 107                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 2.375V ~ 3.465V                                                                  |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                               |

| Package / Case                 | 144-LQFP                                                                         |

| Supplier Device Package        | 144-TQFP (20x20)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-640uhc-4tg144i |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

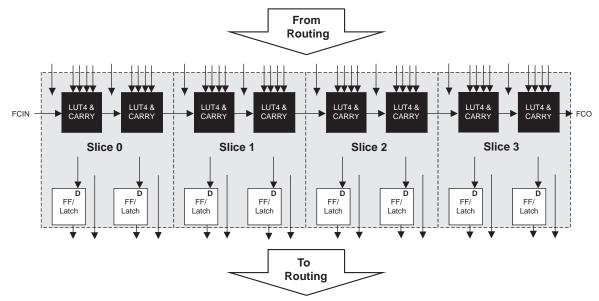

#### Figure 2-3. PFU Block Diagram

#### Slices

Slices 0-3 contain two LUT4s feeding two registers. Slices 0-2 can be configured as distributed memory. Table 2-1 shows the capability of the slices in PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. The control logic performs set/reset functions (programmable as synchronous/ asynchronous), clock select, chip-select and wider RAM/ROM functions.

|         | PFU Block                                       |                         |  |  |

|---------|-------------------------------------------------|-------------------------|--|--|

| Slice   | Resources                                       | Modes                   |  |  |

| Slice 0 | 2 LUT4s and 2 Registers                         | Logic, Ripple, RAM, ROM |  |  |

| Slice 1 | 2 LUT4s and 2 Registers Logic, Ripple, RAM, ROM |                         |  |  |

| Slice 2 | 2 LUT4s and 2 Registers                         | Logic, Ripple, RAM, ROM |  |  |

| Slice 3 | 2 LUT4s and 2 Registers                         | Logic, Ripple, ROM      |  |  |

Table 2-1. Resources and Modes Available per Slice

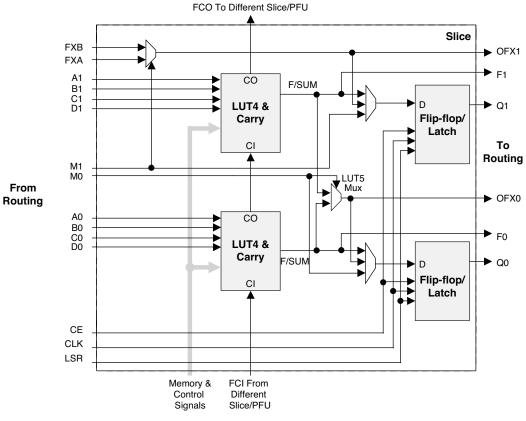

Figure 2-4 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks. All slices have 15 inputs from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six for routing and one to carry-chain (to the adjacent PFU). Table 2-2 lists the signals associated with Slices 0-3.

#### Figure 2-4. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

- WCK is CLK

WRE is from LSR

- DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2

- WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре             | Signal Names   | Description                                                          |

|----------|------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose    | M0/M1          | Multi-purpose input                                                  |

| Input    | Control signal   | CE             | Clock enable                                                         |

| Input    | Control signal   | LSR            | Local set/reset                                                      |

| Input    | Control signal   | CLK            | System clock                                                         |

| Input    | Inter-PFU signal | FCIN           | Fast carry in <sup>1</sup>                                           |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals     | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal | FCO            | Fast carry out <sup>1</sup>                                          |

1. See Figure 2-3 for connection details.

2. Requires two PFUs.

The EBR memory supports three forms of write behavior for single or dual port operation:

- 1. **Normal** Data on the output appears only during the read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port. This mode is supported for all data widths.

- 3. Read-Before-Write When new data is being written, the old contents of the address appears at the output.

#### **FIFO Configuration**

The FIFO has a write port with data-in, CEW, WE and CLKW signals. There is a separate read port with data-out, RCE, RE and CLKR signals. The FIFO internally generates Almost Full, Full, Almost Empty and Empty Flags. The Full and Almost Full flags are registered with CLKW. The Empty and Almost Empty flags are registered with CLKR. Table 2-7 shows the range of programming values for these flags.

#### Table 2-7. Programmable FIFO Flag Ranges

| Flag Name         | Programming Range           |

|-------------------|-----------------------------|

| Full (FF)         | 1 to max (up to $2^{N}$ -1) |

| Almost Full (AF)  | 1 to Full-1                 |

| Almost Empty (AE) | 1 to Full-1                 |

| Empty (EF)        | 0                           |

N = Address bit width.

The FIFO state machine supports two types of reset signals: RST and RPRST. The RST signal is a global reset that clears the contents of the FIFO by resetting the read/write pointer and puts the FIFO flags in their initial reset state. The RPRST signal is used to reset the read pointer. The purpose of this reset is to retransmit the data that is in the FIFO. In these applications it is important to keep careful track of when a packet is written into or read from the FIFO.

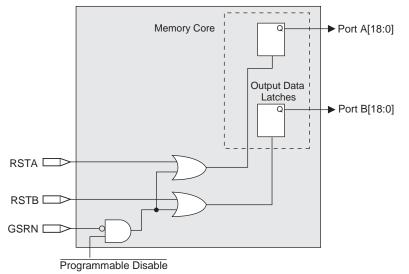

#### **Memory Core Reset**

The memory core contains data output latches for ports A and B. These are simple latches that can be reset synchronously or asynchronously. RSTA and RSTB are local signals, which reset the output latches associated with port A and port B respectively. The Global Reset (GSRN) signal resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-9.

#### Figure 2-9. Memory Core Reset

For further information on the sysMEM EBR block, please refer to TN1201, Memory Usage Guide for MachXO2 Devices.

#### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-10. The GSR input to the EBR is always asynchronous.

#### Figure 2-10. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device wake up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-10. The reset timing rules apply to the RPReset input versus the RE input and the RST input versus the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs. For more details refer to TN1201, Memory Usage Guide for MachXO2 Devices.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

## Programmable I/O Cells (PIC)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the MachXO2 devices, the PIO cells are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the MachXO2 devices, two adjacent PIOs can be combined to provide a complementary output driver pair.

The MachXO2-640U, MachXO2-1200/U and higher density devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. Half of the PIO pairs on the top edge of these devices can be configured as true LVDS transmit pairs. The PIO pairs on the bottom edge of these higher density devices have on-chip differential termination and also provide PCI support.

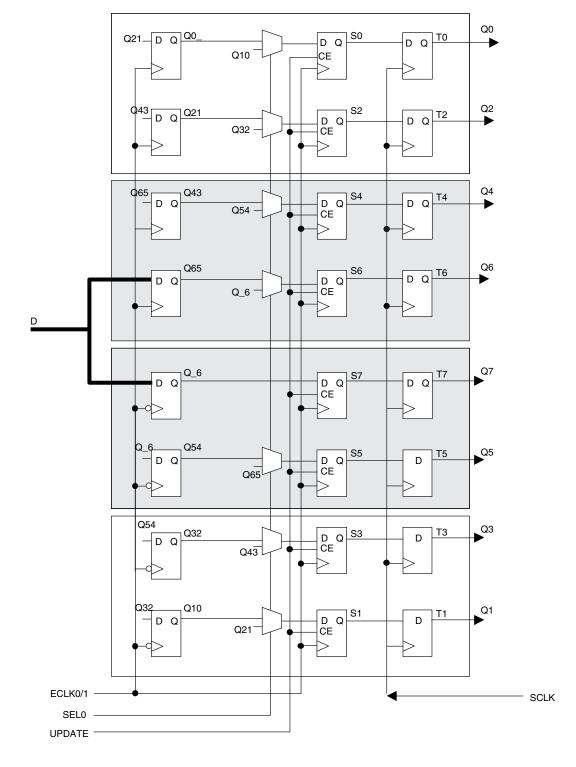

These gearboxes have three stage pipeline registers. The first stage registers sample the high-speed input data by the high-speed edge clock on its rising and falling edges. The second stage registers perform data alignment based on the control signals UPDATE and SEL0 from the control block. The third stage pipeline registers pass the data to the device core synchronized to the low-speed system clock. Figure 2-16 shows a block diagram of the input gearbox.

#### Figure 2-16. Input Gearbox

#### Table 2-13. Supported Output Standards

| Output Standard                 | V <sub>CCIO</sub> (Typ.) |

|---------------------------------|--------------------------|

| Single-Ended Interfaces         |                          |

| LVTTL                           | 3.3                      |

| LVCMOS33                        | 3.3                      |

| LVCMOS25                        | 2.5                      |

| LVCMOS18                        | 1.8                      |

| LVCMOS15                        | 1.5                      |

| LVCMOS12                        | 1.2                      |

| LVCMOS33, Open Drain            |                          |

| LVCMOS25, Open Drain            |                          |

| LVCMOS18, Open Drain            |                          |

| LVCMOS15, Open Drain            |                          |

| LVCMOS12, Open Drain            |                          |

| PCI33                           | 3.3                      |

| SSTL25 (Class I)                | 2.5                      |

| SSTL18 (Class I)                | 1.8                      |

| HSTL18(Class I)                 | 1.8                      |

| Differential Interfaces         |                          |

| LVDS <sup>1, 2</sup>            | 2.5, 3.3                 |

| BLVDS, MLVDS, RSDS <sup>2</sup> | 2.5                      |

| LVPECL <sup>2</sup>             | 3.3                      |

| MIPI <sup>2</sup>               | 2.5                      |

| Differential SSTL18             | 1.8                      |

| Differential SSTL25             | 2.5                      |

| Differential HSTL18             | 1.8                      |

1. MachXO2-640U, MachXO2-1200/U and larger devices have dedicated LVDS buffers. 2. These interfaces can be emulated with external resistors in all devices.

#### sysIO Buffer Banks

The numbers of banks vary between the devices of this family. MachXO2-1200U, MachXO2-2000/U and higher density devices have six I/O banks (one bank on the top, right and bottom side and three banks on the left side). The MachXO2-1200 and lower density devices have four banks (one bank per side). Figures 2-18 and 2-19 show the sysIO banks and their associated supplies for all devices.

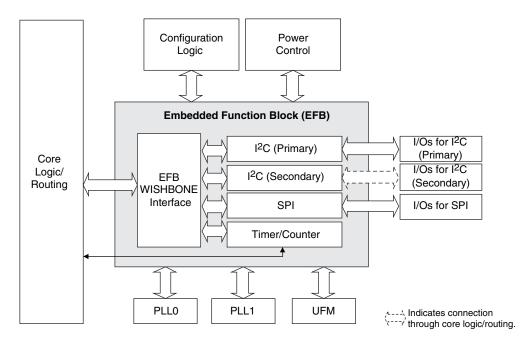

#### Figure 2-20. Embedded Function Block Interface

#### Hardened I<sup>2</sup>C IP Core

Every MachXO2 device contains two I<sup>2</sup>C IP cores. These are the primary and secondary I<sup>2</sup>C IP cores. Either of the two cores can be configured either as an I<sup>2</sup>C master or as an I<sup>2</sup>C slave. The only difference between the two IP cores is that the primary core has pre-assigned I/O pins whereas users can assign I/O pins for the secondary core.

When the IP core is configured as a master it will be able to control other devices on the  $I^2C$  bus through the interface. When the core is configured as the slave, the device will be able to provide I/O expansion to an  $I^2C$  Master. The  $I^2C$  cores support the following functionality:

- Master and Slave operation

- 7-bit and 10-bit addressing

- Multi-master arbitration support

- Up to 400 kHz data transfer speed

- General call support

- Interface to custom logic through 8-bit WISHBONE interface

There are some limitations on the use of the hardened user SPI. These are defined in the following technical notes:

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology (Appendix B)

- TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices

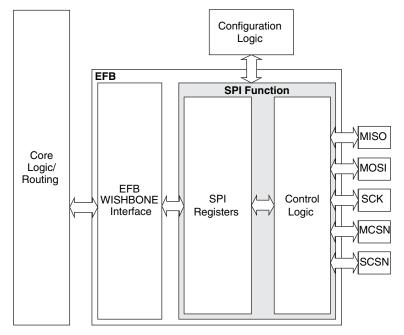

#### Figure 2-22. SPI Core Block Diagram

Table 2-16 describes the signals interfacing with the SPI cores.

Table 2-16. SPI Core Signal Description

| Signal Name | I/O | Master/Slave | Description                                                                                                                                                                           |  |  |  |

|-------------|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| spi_csn[0]  | 0   | Master       | SPI master chip-select output                                                                                                                                                         |  |  |  |

| spi_csn[17] | 0   | Master       | Additional SPI chip-select outputs (total up to eight slaves)                                                                                                                         |  |  |  |

| spi_scsn    | I   | Slave        | SPI slave chip-select input                                                                                                                                                           |  |  |  |

| spi_irq     | 0   | Master/Slave | nterrupt request                                                                                                                                                                      |  |  |  |

| spi_clk     | I/O | Master/Slave | PI clock. Output in master mode. Input in slave mode.                                                                                                                                 |  |  |  |

| spi_miso    | I/O | Master/Slave | SPI data. Input in master mode. Output in slave mode.                                                                                                                                 |  |  |  |

| spi_mosi    | I/O | Master/Slave | SPI data. Output in master mode. Input in slave mode.                                                                                                                                 |  |  |  |

| ufm_sn      | I   | Slave        | Configuration Slave Chip Select (active low), dedicated for selecting the User Flash Memory (UFM).                                                                                    |  |  |  |

| cfg_stdby   | 0   | Master/Slave | Stand-by signal – To be connected only to the power module of the MachXO2 device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab. |  |  |  |

| cfg_wake    | 0   | Master/Slave | Wake-up signal – To be connected only to the power module of the MachXO2 device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab.  |  |  |  |

When implementing background programming of the on-chip Flash, care must be taken for the operation of the PLL. For devices that have two PLLs (XO2-2000U, -4000 and -7000), the system must put the RPLL (Right-side PLL) in reset state during the background Flash programming. More detailed description can be found in TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Security and One-Time Programmable Mode (OTP)

For applications where security is important, the lack of an external bitstream provides a solution that is inherently more secure than SRAM-based FPGAs. This is further enhanced by device locking. MachXO2 devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile Flash memory spaces. The device can be in one of two modes:

- 1. Unlocked Readback of the SRAM configuration and non-volatile Flash memory spaces is allowed.

- 2. Permanently Locked The device is permanently locked.

Once set, the only way to clear the security bits is to erase the device. To further complement the security of the device, a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the Flash and SRAM OTP portions of the device. For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Dual Boot

MachXO2 devices can optionally boot from two patterns, a primary bitstream and a golden bitstream. If the primary bitstream is found to be corrupt while being downloaded into the SRAM, the device shall then automatically re-boot from the golden bitstream. Note that the primary bitstream must reside in the on-chip Flash. The golden image MUST reside in an external SPI Flash. For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.

#### Soft Error Detection

The SED feature is a CRC check of the SRAM cells after the device is configured. This check ensures that the SRAM cells were configured successfully. This feature is enabled by a configuration bit option. The Soft Error Detection can also be initiated in user mode via an input to the fabric. The clock for the Soft Error Detection circuit is generated using a dedicated divider. The undivided clock from the on-chip oscillator is the input to this divider. For low power applications users can switch off the Soft Error Detection circuit. For more details, refer to TN1206, MachXO2 Soft Error Detection Usage Guide.

### TraceID

Each MachXO2 device contains a unique (per device), TraceID that can be used for tracking purposes or for IP security applications. The TraceID is 64 bits long. Eight out of 64 bits are user-programmable, the remaining 56 bits are factory-programmed. The TraceID is accessible through the EFB WISHBONE interface and can also be accessed through the SPI, I<sup>2</sup>C, or JTAG interfaces.

## **Density Shifting**

The MachXO2 family has been designed to enable density migration within the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case. When migrating from lower to higher density or higher to lower density, ensure to review all the power supplies and NC pins of the chosen devices. For more details refer to the MachXO2 migration files.

## Typical Building Block Function Performance – ZE Devices<sup>1</sup>

#### Pin-to-Pin Performance (LVCMOS25 12 mA Drive)

| Function        | –3 Timing | Units |  |

|-----------------|-----------|-------|--|

| Basic Functions |           |       |  |

| 16-bit decoder  | 13.9      | ns    |  |

| 4:1 MUX         | 10.9      | ns    |  |

| 16:1 MUX        | 12.0      | ns    |  |

#### **Register-to-Register Performance**

| –3 Timing | Units                         |

|-----------|-------------------------------|

|           |                               |

| 191       | MHz                           |

| 134       | MHz                           |

| 148       | MHz                           |

| 77        | MHz                           |

|           |                               |

| 90        | MHz                           |

|           |                               |

| 214       | MHz                           |

|           | 191<br>134<br>148<br>77<br>90 |

1. The above timing numbers are generated using the Diamond design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

## **Derating Logic Timing**

Logic timing provided in the following sections of the data sheet and the Lattice design tools are worst case numbers in the operating range. Actual delays may be much faster. Lattice design tools can provide logic timing numbers at a particular temperature and voltage.

## MachXO2 External Switching Characteristics – ZE Devices<sup>1, 2, 3, 4, 5, 6, 7</sup>

|                                                                                            |                                               |                                    | -     | -3    | -     | 2     | -1    |       | -     |

|--------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Parameter                                                                                  | Description                                   | Device                             | Min.  | Max.  | Min.  | Max.  | Min.  | Max.  | Units |

| Clocks                                                                                     |                                               |                                    |       |       |       |       |       |       |       |

| Primary Cloo                                                                               | cks                                           |                                    |       |       |       |       |       |       |       |

| f <sub>MAX_PRI</sub> <sup>8</sup>                                                          | Frequency for Primary Clock<br>Tree           | All MachXO2 devices                | _     | 150   | _     | 125   | —     | 104   | MHz   |

| t <sub>W_PRI</sub>                                                                         | Clock Pulse Width for Primary<br>Clock        | All MachXO2 devices                | 1.00  | _     | 1.20  | _     | 1.40  | _     | ns    |

|                                                                                            |                                               | MachXO2-256ZE                      | —     | 1250  |       | 1272  | —     | 1296  | ps    |

|                                                                                            |                                               | MachXO2-640ZE                      |       | 1161  |       | 1183  | —     | 1206  | ps    |

|                                                                                            | Primary Clock Skew Within a                   | MachXO2-1200ZE                     |       | 1213  |       | 1267  | —     | 1322  | ps    |

| <sup>I</sup> SKEW_PRI                                                                      | Device                                        | MachXO2-2000ZE                     |       | 1204  |       | 1250  | —     | 1296  | ps    |

|                                                                                            |                                               | MachXO2-4000ZE                     |       | 1195  |       | 1233  | —     | 1269  | ps    |

|                                                                                            |                                               | MachXO2-7000ZE                     |       | 1243  |       | 1268  | —     | 1296  | ps    |

| Edge Clock                                                                                 |                                               |                                    |       |       |       |       |       |       |       |

| f <sub>MAX_EDGE<sup>8</sup></sub>                                                          | Frequency for Edge Clock                      | MachXO2-1200 and<br>larger devices | _     | 210   | _     | 175   | _     | 146   | MHz   |

| Pin-LUT-Pin                                                                                | Propagation Delay                             |                                    |       | 1     | 1     |       |       |       | 1     |

| t <sub>PD</sub>                                                                            | Best case propagation delay through one LUT-4 | All MachXO2 devices                | _     | 9.35  | _     | 9.78  | _     | 10.21 | ns    |

| General I/O I                                                                              | Pin Parameters (Using Primary                 | Clock without PLL)                 | 1     |       |       | 1     |       | 1     |       |

|                                                                                            |                                               | MachXO2-256ZE                      |       | 10.46 | —     | 10.86 | —     | 11.25 | ns    |

|                                                                                            | Clock to Output – PIO Output<br>Register      | MachXO2-640ZE                      |       | 10.52 |       | 10.92 | —     | 11.32 | ns    |

|                                                                                            |                                               | MachXO2-1200ZE                     |       | 11.24 |       | 11.68 | —     | 12.12 | ns    |

| t <sub>SKEW_PRI</sub><br>Edge Clock<br>f <sub>MAX_EDGE</sub> <sup>8</sup><br>Pin-LUT-Pin I |                                               | MachXO2-2000ZE                     |       | 11.27 |       | 11.71 | —     | 12.16 | ns    |

|                                                                                            |                                               | MachXO2-4000ZE                     |       | 11.28 |       | 11.78 | —     | 12.28 | ns    |

|                                                                                            |                                               | MachXO2-7000ZE                     | —     | 11.22 |       | 11.76 | —     | 12.30 | ns    |

|                                                                                            |                                               | MachXO2-256ZE                      | -0.21 |       | -0.21 | —     | -0.21 | —     | ns    |

|                                                                                            |                                               | MachXO2-640ZE                      | -0.22 | —     | -0.22 | —     | -0.22 | —     | ns    |

|                                                                                            | Clock to Data Setup – PIO                     | MachXO2-1200ZE                     | -0.25 | —     | -0.25 | —     | -0.25 | —     | ns    |

| ISU                                                                                        | Input Register                                | MachXO2-2000ZE                     | -0.27 | —     | -0.27 | —     | -0.27 | —     | ns    |

|                                                                                            |                                               | MachXO2-4000ZE                     | -0.31 | —     | -0.31 |       | -0.31 |       | ns    |

|                                                                                            |                                               | MachXO2-7000ZE                     | -0.33 | —     | -0.33 |       | -0.33 |       | ns    |

|                                                                                            |                                               | MachXO2-256ZE                      | 3.96  |       | 4.25  | _     | 4.65  | _     | ns    |

|                                                                                            |                                               | MachXO2-640ZE                      | 4.01  |       | 4.31  | —     | 4.71  | —     | ns    |

| +                                                                                          | Clock to Data Hold – PIO Input                | MachXO2-1200ZE                     | 3.95  |       | 4.29  | _     | 4.73  | _     | ns    |

| Ч                                                                                          | Register                                      | MachXO2-2000ZE                     | 3.94  | —     | 4.29  | —     | 4.74  | —     | ns    |

|                                                                                            |                                               | MachXO2-4000ZE                     | 3.96  |       | 4.36  | —     | 4.87  | —     | ns    |

|                                                                                            |                                               | MachXO2-7000ZE                     | 3.93  |       | 4.37  | —     | 4.91  |       | ns    |

|                                                                                            |                                               | IVIACHAU2-7000ZE                   | 3.93  | —     | 4.37  |       | 4.91  |       |       |

**Over Recommended Operating Conditions**

## I<sup>2</sup>C Port Timing Specifications<sup>1, 2</sup>

| Symbol           | Parameter                   | Min. | Max. | Units |

|------------------|-----------------------------|------|------|-------|

| f <sub>MAX</sub> | Maximum SCL clock frequency | _    | 400  | kHz   |

1. MachXO2 supports the following modes:

• Standard-mode (Sm), with a bit rate up to 100 kbit/s (user and configuration mode)

• Fast-mode (Fm), with a bit rate up to 400 kbit/s (user and configuration mode)

2. Refer to the I<sup>2</sup>C specification for timing requirements.

## SPI Port Timing Specifications<sup>1</sup>

| Symbol           | Parameter                   | Min. | Max. | Units |

|------------------|-----------------------------|------|------|-------|

| f <sub>MAX</sub> | Maximum SCK clock frequency | _    | 45   | MHz   |

1. Applies to user mode only. For configuration mode timing specifications, refer to sysCONFIG Port Timing Specifications table in this data sheet.

## **Switching Test Conditions**

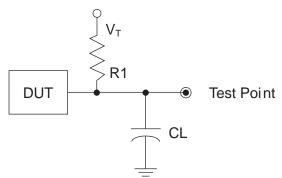

Figure 3-13 shows the output test load used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-5.

#### Figure 3-13. Output Test Load, LVTTL and LVCMOS Standards

| Table 3-5. Test Fixture Required Components, | Non-Terminated Interfaces |

|----------------------------------------------|---------------------------|

|----------------------------------------------|---------------------------|

| Test Condition                             | R1       | CL                        | Timing Ref.               | VT              |  |

|--------------------------------------------|----------|---------------------------|---------------------------|-----------------|--|

|                                            |          |                           | LVTTL, LVCMOS 3.3 = 1.5 V | —               |  |

|                                            |          |                           | LVCMOS 2.5 = $V_{CCIO}/2$ | —               |  |

| LVTTL and LVCMOS settings (L -> H, H -> L) | $\infty$ | 0pF                       | LVCMOS 1.8 = $V_{CCIO}/2$ | —               |  |

|                                            |          | LVCMOS 1.5 = $V_{CCIO}/2$ |                           |                 |  |

|                                            |          |                           | LVCMOS 1.2 = $V_{CCIO}/2$ | —               |  |

| LVTTL and LVCMOS 3.3 (Z -> H)              |          |                           | 1.5 V                     | V <sub>OL</sub> |  |

| LVTTL and LVCMOS 3.3 (Z -> L)              |          |                           | 1.5 V                     | V <sub>OH</sub> |  |

| Other LVCMOS (Z -> H)                      | 188      | 0pF                       | V <sub>CCIO</sub> /2      | V <sub>OL</sub> |  |

| Other LVCMOS (Z -> L)                      | 100      | opi                       | V <sub>CCIO</sub> /2      | V <sub>OH</sub> |  |

| LVTTL + LVCMOS (H -> Z)                    |          |                           | V <sub>OH</sub> – 0.15 V  | V <sub>OL</sub> |  |

| LVTTL + LVCMOS (L -> Z)                    | ]        |                           | V <sub>OL</sub> – 0.15 V  | V <sub>OH</sub> |  |

Note: Output test conditions for all other interfaces are determined by the respective standards.

# MachXO2 Family Data Sheet Pinout Information

March 2017

Data Sheet DS1035

## **Signal Descriptions**

| Signal Name                              | I/O       | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                          |           | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                          |           | [Row/Column Number] indicates the PFU row or the column of the device on which the PIO Group exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                                                                                                                                                                                                                                                                                                                                                                |

|                                          |           | [A/B/C/D] indicates the PIO within the group to which the pad is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P[Edge] [Row/Column<br>Number]_[A/B/C/D] | I/O       | Some of these user-programmable pins are shared with special function pins. When not used as special function pins, these pins can be programmed as I/Os for user logic.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                          |           | During configuration of the user-programmable I/Os, the user has an option to tri-state the I/Os and enable an internal pull-up, pull-down or buskeeper resistor. This option also applies to unused pins (or those not bonded to a package pin). The default during configuration is for user-programmable I/Os to be tri-stated with an internal pull-down resistor enabled. When the device is erased, I/Os will be tri-stated with an internal pull-down resistor enabled. Some pins, such as PROGRAMN and JTAG pins, default to tri-stated I/Os with pull-up resistors enabled when the device is erased. |

| NC                                       | —         | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND                                      | _         | GND – Ground. Dedicated pins. It is recommended that all GNDs are tied together.<br>For QFN 48 package, the exposed die pad is the device ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VCC                                      | _         | $V_{CC}$ – The power supply pins for core logic. Dedicated pins. It is recommended that all VCCs are tied to the same supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCCIOx                                   | _         | VCCIO – The power supply pins for I/O Bank x. Dedicated pins. It is recommended that all VCCIOs located in the same bank are tied to the same supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PLL and Clock Function                   | ons (Us   | ed as user-programmable I/O pins when not used for PLL or clock pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [LOC]_GPLL[T, C]_IN                      | _         | Reference Clock (PLL) input pads: [LOC] indicates location. Valid designations are L (Left PLL) and R (Right PLL). T = true and C = complement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [LOC]_GPLL[T, C]_FB                      | _         | Optional Feedback (PLL) input pads: [LOC] indicates location. Valid designations are L (Left PLL) and R (Right PLL). T = true and C = complement.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PCLK [n]_[2:0]                           | —         | Primary Clock pads. One to three clock pads per side.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Test and Programming                     | g (Dual f | function pins used for test access port and during sysCONFIG™)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TMS                                      | I         | Test Mode Select input pin, used to control the 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ТСК                                      | I         | Test Clock input pin, used to clock the 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TDI                                      | I         | Test Data input pin, used to load data into the device using an 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TDO                                      | 0         | Output pin – Test Data output pin used to shift data out of the device using 1149.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                          |           | Optionally controls behavior of TDI, TDO, TMS, TCK. If the device is configured to use the JTAG pins (TDI, TDO, TMS, TCK) as general purpose I/O, then:                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| JTAGENB                                  | I         | If JTAGENB is low: TDI, TDO, TMS and TCK can function a general purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                          |           | If JTAGENB is high: TDI, TDO, TMS and TCK function as JTAG pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                          |           | For more details, refer to TN1204, MachXO2 Programming and Configuration Usage Guide.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Configuration (Dual fu                   | nction p  | ins used during sysCONFIG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PROGRAMN                                 | I         | Initiates configuration sequence when asserted low. During configuration, or when reserved as PROGRAMN in user mode, this pin always has an active pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

<sup>© 2016</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# High-Performance Commercial Grade Devices with Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-256HC-4SG32C  | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256HC-5SG32C  | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256HC-6SG32C  | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 32    | COM   |

| LCMXO2-256HC-4SG48C  | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-256HC-5SG48C  | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-256HC-6SG48C  | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-256HC-4UMG64C | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256HC-5UMG64C | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256HC-6UMG64C | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free ucBGA | 64    | COM   |

| LCMXO2-256HC-4TG100C | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256HC-5TG100C | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256HC-6TG100C | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-256HC-4MG132C | 256  | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-256HC-5MG132C | 256  | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-256HC-6MG132C | 256  | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | COM   |

| Part Number          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-640HC-4SG48C  | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-640HC-5SG48C  | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-640HC-6SG48C  | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free QFN   | 48    | COM   |

| LCMXO2-640HC-4TG100C | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640HC-5TG100C | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640HC-6TG100C | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-640HC-4MG132C | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-640HC-5MG132C | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-640HC-6MG132C | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | COM   |

| Part Number           | LUTs | Supply Voltage | Grade | Package           | Leads | Temp. |

|-----------------------|------|----------------|-------|-------------------|-------|-------|

| LCMXO2-640UHC-4TG144C | 640  | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP | 144   | COM   |

| LCMXO2-640UHC-5TG144C | 640  | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP | 144   | COM   |

| LCMXO2-640UHC-6TG144C | 640  | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP | 144   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000HC-4TG144C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-5TG144C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-6TG144C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HC-4BG256C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-5BG256C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-6BG256C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HC-4FTG256C | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-5FTG256C | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-6FTG256C | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HC-4BG332C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-5BG332C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-6BG332C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HC-4FG400C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-5FG400C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-6FG400C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 400   | COM   |

| LCMXO2-7000HC-4FG484C  | 6864 | 2.5 V / 3.3 V  | -4    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HC-5FG484C  | 6864 | 2.5 V / 3.3 V  | -5    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HC-6FG484C  | 6864 | 2.5 V / 3.3 V  | -6    | Halogen-Free fpBGA | 484   | COM   |

| Part Number                          | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|--------------------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-1200HC-4TG100CR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-5TG100CR11             | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-6TG100CR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-1200HC-4MG132CR11             | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-5MG132CR11             | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-6MG132CR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-1200HC-4TG144CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200HC-5TG144CR1 <sup>1</sup> | 1280 | 2.5 V / 3.3 V  | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-1200HC-6TG144CR11             | 1280 | 2.5 V / 3.3 V  | -6    | Halogen-Free TQFP  | 144   | COM   |

1. Specifications for the "LCMXO2-1200HC-speed package CR1" are the same as the "LCMXO2-1200HC-speed package C" devices respectively, except as specified in the R1 Device Specifications section of this data sheet.

# High-Performance Commercial Grade Devices without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100C  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-5TG100C  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-6TG100C  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 100   | COM   |

| LCMXO2-2000HE-4TG144C  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-5TG144C  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-6TG144C  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-2000HE-4MG132C  | 2112 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-5MG132C  | 2112 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-6MG132C  | 2112 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-2000HE-4BG256C  | 2112 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-5BG256C  | 2112 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-6BG256C  | 2112 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-2000HE-4FTG256C | 2112 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-5FTG256C | 2112 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-2000HE-6FTG256C | 2112 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484C | 2112 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-5FG484C | 2112 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-2000UHE-6FG484C | 2112 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HE-4TG144C  | 4320 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-5TG144C  | 4320 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-6TG144C  | 4320 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-4000HE-4MG132C  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-5MG132C  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-6MG132C  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | COM   |

| LCMXO2-4000HE-4BG256C  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4MG184C  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5MG184C  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-6MG184C  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 184   | COM   |

| LCMXO2-4000HE-5BG256C  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-6BG256C  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-4000HE-4FTG256C | 4320 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-5FTG256C | 4320 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-6FTG256C | 4320 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-4000HE-4BG332C  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HE-5BG332C  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | COM   |

| Part Number           | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|-----------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HE-6BG332C | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-4000HE-4FG484C | 4320 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-4000HE-5FG484C | 4320 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-4000HE-6FG484C | 4320 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | COM   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000HE-4TG144C  | 6864 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HE-5TG144C  | 6864 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HE-6TG144C  | 6864 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | COM   |

| LCMXO2-7000HE-4BG256C  | 6864 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HE-5BG256C  | 6864 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HE-6BG256C  | 6864 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | COM   |

| LCMXO2-7000HE-4FTG256C | 6864 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HE-5FTG256C | 6864 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HE-6FTG256C | 6864 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | COM   |

| LCMXO2-7000HE-4BG332C  | 6864 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HE-5BG332C  | 6864 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HE-6BG332C  | 6864 | 1.2 V          | -6    | Halogen-Free caBGA | 332   | COM   |

| LCMXO2-7000HE-4FG484C  | 6864 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HE-5FG484C  | 6864 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | COM   |

| LCMXO2-7000HE-6FG484C  | 6864 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | COM   |

# MachXO2 Family Data Sheet Supplemental Information

#### April 2012

Data Sheet DS1035

### **For Further Information**

A variety of technical notes for the MachXO2 family are available on the Lattice web site.

- TN1198, Power Estimation and Management for MachXO2 Devices

- TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide

- TN1201, Memory Usage Guide for MachXO2 Devices

- TN1202, MachXO2 sysIO Usage Guide

- TN1203, Implementing High-Speed Interfaces with MachXO2 Devices

- TN1204, MachXO2 Programming and Configuration Usage Guide

- TN1205, Using User Flash Memory and Hardened Control Functions in MachXO2 Devices

- TN1206, MachXO2 SRAM CRC Error Detection Usage Guide

- TN1207, Using TraceID in MachXO2 Devices

- TN1074, PCB Layout Recommendations for BGA Packages

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology

- AN8086, Designing for Migration from MachXO2-1200-R1 to Standard (non-R1) Devices

- AN8066, Boundary Scan Testability with Lattice sysIO Capability

- MachXO2 Device Pinout Files

- Thermal Management document

- · Lattice design tools

For further information on interface standards, refer to the following web sites:

- JEDEC Standards (LVTTL, LVCMOS, LVDS, DDR, DDR2, LPDDR): www.jedec.org

- PCI: www.pcisig.com

<sup>© 2012</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Date            | Version                             | Section                                                                                                                                                                                                                                              | Change Summary                                                                                     |  |  |  |

|-----------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| May 2011 01.3   |                                     | Multiple                                                                                                                                                                                                                                             | Replaced "SED" with "SRAM CRC Error Detection" throughout the document.                            |  |  |  |

|                 |                                     | DC and Switching<br>Characteristics                                                                                                                                                                                                                  | Added footnote 1 to Program Erase Specifications table.                                            |  |  |  |

|                 |                                     | Pinout Information                                                                                                                                                                                                                                   | Updated Pin Information Summary tables.                                                            |  |  |  |

|                 |                                     |                                                                                                                                                                                                                                                      | Signal name SO/SISPISO changed to SO/SPISO in the Signal Descriptions table.                       |  |  |  |

| April 2011 01.2 |                                     | _                                                                                                                                                                                                                                                    | Data sheet status changed from Advance to Preliminary.                                             |  |  |  |

|                 | Introduction                        | Updated MachXO2 Family Selection Guide table.                                                                                                                                                                                                        |                                                                                                    |  |  |  |

|                 |                                     | Architecture                                                                                                                                                                                                                                         | Updated Supported Input Standards table.                                                           |  |  |  |

|                 |                                     | Updated sysMEM Memory Primitives diagram.                                                                                                                                                                                                            |                                                                                                    |  |  |  |

|                 |                                     |                                                                                                                                                                                                                                                      | Added differential SSTL and HSTL IO standards.                                                     |  |  |  |

|                 | DC and Switching<br>Characteristics | Updates following parameters: POR voltage levels, DC electrical characteristics, static supply current for ZE/HE/HC devices, static power consumption contribution of different components – ZE devices, programming and erase Flash supply current. |                                                                                                    |  |  |  |

|                 |                                     | Added VREF specifications to sysIO recommended operating condi-<br>tions.                                                                                                                                                                            |                                                                                                    |  |  |  |

|                 |                                     | Updating timing information based on characterization.                                                                                                                                                                                               |                                                                                                    |  |  |  |

|                 |                                     | Added differential SSTL and HSTL IO standards.                                                                                                                                                                                                       |                                                                                                    |  |  |  |

|                 |                                     | Ordering Information                                                                                                                                                                                                                                 | Added Ordering Part Numbers for R1 devices, and devices in WLCSP packages.                         |  |  |  |

|                 |                                     |                                                                                                                                                                                                                                                      | Added R1 device specifications.                                                                    |  |  |  |

| January 2011    | January 2011 01.1                   | All                                                                                                                                                                                                                                                  | Included ultra-high I/O devices.                                                                   |  |  |  |

|                 |                                     | DC and Switching<br>Characteristics                                                                                                                                                                                                                  | Recommended Operating Conditions table – Added footnote 3.                                         |  |  |  |

|                 |                                     | DC Electrical Characteristics table – Updated data for $\rm I_{IL},  I_{IH},  V_{HYST}$ typical values updated.                                                                                                                                      |                                                                                                    |  |  |  |

|                 |                                     | Generic DDRX2 Outputs with Clock and Data Aligned at Pin (GDDRX2_TX.ECLK.Aligned) Using PCLK Pin for Clock Input tables – Updated data for $T_{DIA}$ and $T_{DIB}$ .                                                                                 |                                                                                                    |  |  |  |

|                 |                                     | Generic DDRX4 Outputs with Clock and Data Aligned at Pin (GDDRX4_TX.ECLK.Aligned) Using PCLK Pin for Clock Input tables – Updated data for $T_{DIA}$ and $T_{DIB}$ .                                                                                 |                                                                                                    |  |  |  |