# E · K Fattice Semiconductor Corporation - <u>LCMX02-7000ZE-2FG484I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                           |

|--------------------------------|----------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 858                                                                              |

| Number of Logic Elements/Cells | 6864                                                                             |

| Total RAM Bits                 | 245760                                                                           |

| Number of I/O                  | 334                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                    |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                               |

| Package / Case                 | 484-BBGA                                                                         |

| Supplier Device Package        | 484-FBGA (23x23)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2-7000ze-2fg484i |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The logic blocks, Programmable Functional Unit (PFU) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each row has either the logic blocks or the EBR blocks. The PIO cells are located at the periphery of the device, arranged in banks. The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the MachXO2 family, the number of sysIO banks varies by device. There are different types of I/O buffers on the different banks. Refer to the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks; these blocks are found in MachXO2-640/U and larger devices. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT usage.

The MachXO2 registers in PFU and sysl/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

The MachXO2 architecture also provides up to two sysCLOCK Phase Locked Loop (PLL) blocks on MachXO2-640U, MachXO2-1200/U and larger devices. These blocks are located at the ends of the on-chip Flash block. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

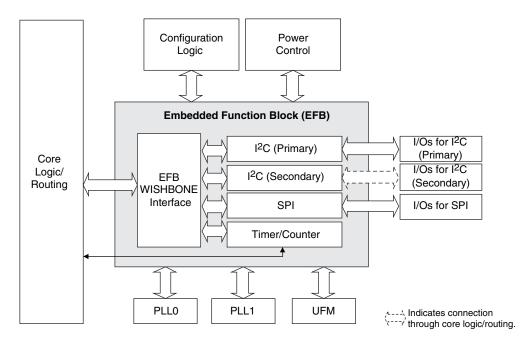

MachXO2 devices provide commonly used hardened functions such as SPI controller, I<sup>2</sup>C controller and timer/ counter. MachXO2-640/U and higher density devices also provide User Flash Memory (UFM). These hardened functions and the UFM interface to the core logic and routing through a WISHBONE interface. The UFM can also be accessed through the SPI, I<sup>2</sup>C and JTAG ports.

Every device in the family has a JTAG port that supports programming and configuration of the device as well as access to the user logic. The MachXO2 devices are available for operation from 3.3 V, 2.5 V and 1.2 V power supplies, providing easy integration into the overall system.

# **PFU Blocks**

The core of the MachXO2 device consists of PFU blocks, which can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. Each PFU block consists of four interconnected slices numbered 0 to 3 as shown in Figure 2-3. Each slice contains two LUTs and two registers. There are 53 inputs and 25 outputs associated with each PFU block.

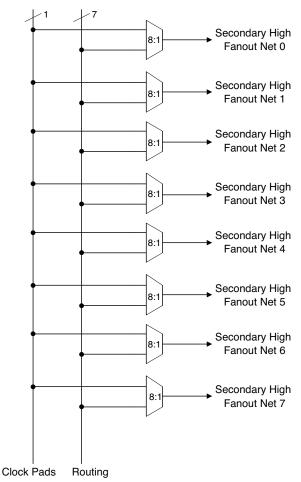

#### Figure 2-6. Secondary High Fanout Nets for MachXO2 Devices

# sysCLOCK Phase Locked Loops (PLLs)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The MachXO2-640U, MachXO2-1200/U and larger devices have one or more sysCLOCK PLL. CLKI is the reference frequency input to the PLL and its source can come from an external I/O pin or from internal routing. CLKFB is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The MachXO2 sysCLOCK PLLs support high resolution (16-bit) fractional-N synthesis. Fractional-N frequency synthesis allows the user to generate an output clock which is a non-integer multiple of the input frequency. For more information about using the PLL with Fractional-N synthesis, please see TN1199, MachXO2 sysCLOCK PLL Design and Usage Guide.

Each output has its own output divider, thus allowing the PLL to generate different frequencies for each output. The output dividers can have a value from 1 to 128. The output dividers may also be cascaded together to generate low frequency clocks. The CLKOP, CLKOS, CLKOS2, and CLKOS3 outputs can all be used to drive the MachXO2 clock distribution network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 2-7.

The setup and hold times of the device can be improved by programming a phase shift into the CLKOS, CLKOS2, and CLKOS3 output clocks which will advance or delay the output clock with reference to the CLKOP output clock.

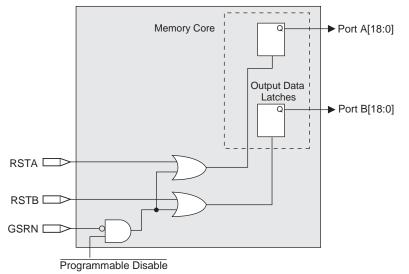

#### Figure 2-9. Memory Core Reset

For further information on the sysMEM EBR block, please refer to TN1201, Memory Usage Guide for MachXO2 Devices.

#### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-10. The GSR input to the EBR is always asynchronous.

#### Figure 2-10. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device wake up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-10. The reset timing rules apply to the RPReset input versus the RE input and the RST input versus the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs. For more details refer to TN1201, Memory Usage Guide for MachXO2 Devices.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

MachXO2-640U, MachXO2-1200/U, MachXO2-2000/U, MachXO2-4000 and MachXO2-7000 devices contain three types of sysIO buffer pairs.

## 1. Left and Right sysIO Buffer Pairs

The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers and two single-ended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the left and right of the devices also have differential and referenced input buffers.

## 2. Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the bottom bank of the device consist of two single-ended output drivers and two single-ended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the bottom also have differential and referenced input buffers. Only the I/Os on the bottom banks have programmable PCI clamps and differential input termination. The PCI clamp is enabled after  $V_{CC}$  and  $V_{CCIO}$  are at valid operating levels and the device has been configured.

## 3. Top sysIO Buffer Pairs

The sysIO buffer pairs in the top bank of the device consist of two single-ended output drivers and two singleended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the top also have differential and referenced I/O buffers. Half of the sysIO buffer pairs on the top edge have true differential outputs. The sysIO buffer pair comprising of the A and B PIOs in every PIC on the top edge have a differential output driver. The referenced input buffer can also be configured as a differential input buffer.

# Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$  and  $V_{CCIO0}$  have reached  $V_{PORUP}$  level defined in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a blank device is tri-state with a weak pulldown to GND (some pins such as PROGRAMN and the JTAG pins have weak pull-up to  $V_{CCIO}$  as the default functionality). The I/O pins will maintain the blank configuration until  $V_{CC}$  and  $V_{CCIO}$  (for I/O banks containing configuration I/Os) have reached  $V_{PORUP}$  levels at which time the I/Os will take on the user-configured settings only after a proper download/configuration.

# **Supported Standards**

The MachXO2 sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL, and PCI. The buffer supports the LVTTL, PCI, LVCMOS 1.2, 1.5, 1.8, 2.5, and 3.3 V standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, bus maintenance (weak pull-up, weak pull-down, bus-keeper latch or none) and open drain. BLVDS, MLVDS and LVPECL output emulation is supported on all devices. The MachXO2-640U, MachXO2-1200/U and higher devices support on-chip LVDS output buffers on approximately 50% of the I/Os on the top bank. Differential receivers for LVDS, BLVDS, MLVDS and LVPECL are supported on all banks of MachXO2 devices. PCI support is provided in the bottom bank of theMachXO2-640U, MachXO2-1200/U and higher density devices. Table 2-11 summarizes the I/O characteristics of the MachXO2 PLDs.

Tables 2-11 and 2-12 show the I/O standards (together with their supply and reference voltages) supported by the MachXO2 devices. For further information on utilizing the sysIO buffer to support a variety of standards please see TN1202, MachXO2 sysIO Usage Guide.

## Table 2-11. I/O Support Device by Device

|                                             | MachXO2-256,<br>MachXO2-640                                     | MachXO2-640U,<br>MachXO2-1200                                         | MachXO2-1200U<br>MachXO2-2000/U,<br>MachXO2-4000,<br>MachXO2-7000     |

|---------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|

| Number of I/O Banks                         | 4                                                               | 4                                                                     | 6                                                                     |

|                                             |                                                                 | Single-ended (all I/O banks)                                          | Single-ended (all I/O banks)                                          |

| Type of Input Buffers                       | Single-ended (all I/O banks)<br>Differential Receivers (all I/O | Differential Receivers (all I/O<br>banks)                             | Differential Receivers (all I/O<br>banks)                             |

|                                             | banks)                                                          | Differential input termination (bottom side)                          | Differential input termination (bottom side)                          |

|                                             | Single-ended buffers with                                       | Single-ended buffers with<br>complementary outputs (all I/O<br>banks) | Single-ended buffers with<br>complementary outputs (all I/O<br>banks) |

| Types of Output Buffers                     | complementary outputs (all I/O<br>banks)                        | Differential buffers with true<br>LVDS outputs (50% on top<br>side)   | Differential buffers with true<br>LVDS outputs (50% on top<br>side)   |

| Differential Output Emulation<br>Capability | All I/O banks                                                   | All I/O banks                                                         | All I/O banks                                                         |

| PCI Clamp Support                           | No                                                              | Clamp on bottom side only                                             | Clamp on bottom side only                                             |

## Table 2-12. Supported Input Standards

|                                 |                       | VCCIO (Typ.)          |                       |                       |                       |  |

|---------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|

| Input Standard                  | 3.3 V                 | 2.5 V                 | 1.8 V                 | 1.5                   | 1.2 V                 |  |

| Single-Ended Interfaces         |                       | •                     | •                     |                       |                       |  |

| LVTTL                           | ✓                     | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> |                       |  |

| LVCMOS33                        | ✓                     | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> |                       |  |

| LVCMOS25                        | <b>√</b> <sup>2</sup> | ✓                     | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> |                       |  |

| LVCMOS18                        | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | ✓                     | <b>√</b> <sup>2</sup> |                       |  |

| LVCMOS15                        | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | ~                     | <b>√</b> <sup>2</sup> |  |

| LVCMOS12                        | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | <b>√</b> <sup>2</sup> | ✓                     |  |

| PCI <sup>1</sup>                | ✓                     |                       |                       |                       |                       |  |

| SSTL18 (Class I, Class II)      | 1                     | ✓                     | ✓                     |                       |                       |  |

| SSTL25 (Class I, Class II)      | 1                     | ✓                     |                       |                       |                       |  |

| HSTL18 (Class I, Class II)      | ✓                     | ✓                     | ✓                     |                       |                       |  |

| Differential Interfaces         |                       | •                     |                       |                       |                       |  |

| LVDS                            | ✓                     | ✓                     |                       |                       |                       |  |

| BLVDS, MVDS, LVPECL, RSDS       | ✓                     | ✓                     |                       |                       |                       |  |

| MIPI <sup>3</sup>               | ✓                     | ✓                     |                       |                       |                       |  |

| Differential SSTL18 Class I, II | ✓                     | ✓                     | ✓                     |                       |                       |  |

| Differential SSTL25 Class I, II | ✓                     | ✓                     |                       |                       |                       |  |

| Differential HSTL18 Class I, II | ✓                     | ✓                     | ✓                     |                       |                       |  |

1. Bottom banks of MachXO2-640U, MachXO2-1200/U and higher density devices only.

2. Reduced functionality. Refer to TN1202, MachXO2 sysIO Usage Guide for more detail.

3. These interfaces can be emulated with external resistors in all devices.

#### Table 2-13. Supported Output Standards

| Output Standard                 | V <sub>CCIO</sub> (Typ.) |

|---------------------------------|--------------------------|

| Single-Ended Interfaces         |                          |

| LVTTL                           | 3.3                      |

| LVCMOS33                        | 3.3                      |

| LVCMOS25                        | 2.5                      |

| LVCMOS18                        | 1.8                      |

| LVCMOS15                        | 1.5                      |

| LVCMOS12                        | 1.2                      |

| LVCMOS33, Open Drain            |                          |

| LVCMOS25, Open Drain            |                          |

| LVCMOS18, Open Drain            |                          |

| LVCMOS15, Open Drain            |                          |

| LVCMOS12, Open Drain            |                          |

| PCI33                           | 3.3                      |

| SSTL25 (Class I)                | 2.5                      |

| SSTL18 (Class I)                | 1.8                      |

| HSTL18(Class I)                 | 1.8                      |

| Differential Interfaces         |                          |

| LVDS <sup>1, 2</sup>            | 2.5, 3.3                 |

| BLVDS, MLVDS, RSDS <sup>2</sup> | 2.5                      |

| LVPECL <sup>2</sup>             | 3.3                      |

| MIPI <sup>2</sup>               | 2.5                      |

| Differential SSTL18             | 1.8                      |

| Differential SSTL25             | 2.5                      |

| Differential HSTL18             | 1.8                      |

1. MachXO2-640U, MachXO2-1200/U and larger devices have dedicated LVDS buffers. 2. These interfaces can be emulated with external resistors in all devices.

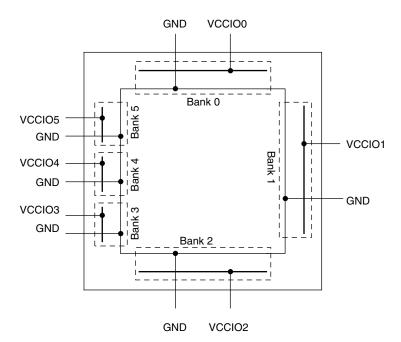

# sysIO Buffer Banks

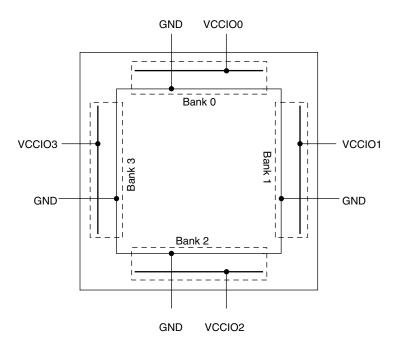

The numbers of banks vary between the devices of this family. MachXO2-1200U, MachXO2-2000/U and higher density devices have six I/O banks (one bank on the top, right and bottom side and three banks on the left side). The MachXO2-1200 and lower density devices have four banks (one bank per side). Figures 2-18 and 2-19 show the sysIO banks and their associated supplies for all devices.

Figure 2-18. MachXO2-1200U, MachXO2-2000/U, MachXO2-4000 and MachXO2-7000 Banks

Figure 2-19. MachXO2-256, MachXO2-640/U and MachXO2-1200 Banks

## Figure 2-20. Embedded Function Block Interface

# Hardened I<sup>2</sup>C IP Core

Every MachXO2 device contains two I<sup>2</sup>C IP cores. These are the primary and secondary I<sup>2</sup>C IP cores. Either of the two cores can be configured either as an I<sup>2</sup>C master or as an I<sup>2</sup>C slave. The only difference between the two IP cores is that the primary core has pre-assigned I/O pins whereas users can assign I/O pins for the secondary core.

When the IP core is configured as a master it will be able to control other devices on the  $I^2C$  bus through the interface. When the core is configured as the slave, the device will be able to provide I/O expansion to an  $I^2C$  Master. The  $I^2C$  cores support the following functionality:

- Master and Slave operation

- 7-bit and 10-bit addressing

- Multi-master arbitration support

- Up to 400 kHz data transfer speed

- General call support

- Interface to custom logic through 8-bit WISHBONE interface

# Power-On-Reset Voltage Levels<sup>1, 2, 3, 4, 5</sup>

| Symbol                    | Parameter                                                                                            | Min. | Тур. | Max. | Units |

|---------------------------|------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>PORUP</sub>        | Power-On-Reset ramp up trip point (band gap based circuit monitoring $V_{CCINT}$ and $V_{CCIO0})$    | 0.9  | _    | 1.06 | V     |

| V <sub>PORUPEXT</sub>     | Power-On-Reset ramp up trip point (band gap based circuit monitoring external $V_{CC}$ power supply) | 1.5  | _    | 2.1  | V     |

| V <sub>PORDNBG</sub>      | Power-On-Reset ramp down trip point (band gap based circuit monitoring $V_{CCINT})$                  | 0.75 | _    | 0.93 | V     |

| V <sub>PORDNBGEXT</sub>   | Power-On-Reset ramp down trip point (band gap based circuit monitoring $\mathrm{V}_{\mathrm{CC}}$ )  | 0.98 | _    | 1.33 | V     |

| V <sub>PORDNSRAM</sub>    | Power-On-Reset ramp down trip point (SRAM based circuit monitoring $V_{CCINT})$                      | _    | 0.6  |      | V     |

| V <sub>PORDNSRAMEXT</sub> | Power-On-Reset ramp down trip point (SRAM based circuit monitoring $\mathrm{V}_{\mathrm{CC}}$ )      | —    | 0.96 | —    | V     |

1. These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

2. For devices without voltage regulators V<sub>CCINT</sub> is the same as the V<sub>CC</sub> supply voltage. For devices with voltage regulators, V<sub>CCINT</sub> is regulated from the V<sub>CC</sub> supply voltage.

3. Note that V<sub>PORUP</sub> (min.) and V<sub>PORDNBG</sub> (max.) are in different process corners. For any given process corner V<sub>PORDNBG</sub> (max.) is always 12.0 mV below V<sub>PORUP</sub> (min.).

4. V<sub>PORUPEXT</sub> is for HC devices only. In these devices a separate POR circuit monitors the external V<sub>CC</sub> power supply.

5. V<sub>CCIO0</sub> does not have a Power-On-Reset ramp down trip point. V<sub>CCIO0</sub> must remain within the Recommended Operating Conditions to ensure proper operation.

# **Programming/Erase Specifications**

| Symbol    | Parameter Mir                                       |    | Max. <sup>1</sup> | Units  |

|-----------|-----------------------------------------------------|----|-------------------|--------|

| Nanagaya  | Flash Programming cycles per t <sub>RETENTION</sub> | —  | 10,000            | Cycles |

| NPROGCYC  | Flash functional programming cycles —               |    | 100,000           | Cycles |

|           | Data retention at 100 °C junction temperature       | 10 | —                 | Years  |

| RETENTION | Data retention at 85 °C junction temperature        | 20 | _                 | Teals  |

1. Maximum Flash memory reads are limited to 7.5E13 cycles over the lifetime of the product.

# Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol          | Parameter                    | Condition                   | Max.    | Units |

|-----------------|------------------------------|-----------------------------|---------|-------|

| I <sub>DK</sub> | Input or I/O leakage Current | $0 < V_{IN} < V_{IH}$ (MAX) | +/-1000 | μΑ    |

1. Insensitive to sequence of  $V_{CC}$  and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$  and  $V_{CCIO}$ .

2.  $0 < V_{CC} < V_{CC}$  (MAX),  $0 < V_{CCIO} < V_{CCIO}$  (MAX).

3. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PD</sub> or I<sub>BH</sub>.

# **ESD** Performance

Please refer to the MachXO2 Product Family Qualification Summary for complete qualification data, including ESD performance.

# Static Supply Current – HC/HE Devices<sup>1, 2, 3, 6</sup>

| Symbol | Parameter                                       | Device         | Typ.⁴ | Units |

|--------|-------------------------------------------------|----------------|-------|-------|

|        |                                                 | LCMXO2-256HC   | 1.15  | mA    |

|        |                                                 | LCMXO2-640HC   | 1.84  | mA    |

|        |                                                 | LCMXO2-640UHC  | 3.48  | mA    |

|        |                                                 | LCMXO2-1200HC  | 3.49  | mA    |

|        |                                                 | LCMXO2-1200UHC | 4.80  | mA    |

| 1      | Core Power Supply                               | LCMXO2-2000HC  | 4.80  | mA    |

| ICC    |                                                 | LCMXO2-2000UHC | 8.44  | mA    |

|        |                                                 | LCMXO2-4000HC  | 8.45  | mA    |

|        |                                                 | LCMXO2-7000HC  | 12.87 | mA    |

|        |                                                 | LCMXO2-2000HE  | 1.39  | mA    |

|        |                                                 | LCMXO2-4000HE  | 2.55  | mA    |

|        |                                                 | LCMXO2-7000HE  | 4.06  | mA    |

| Іссю   | Bank Power Supply⁵<br>V <sub>CCIO</sub> = 2.5 V | All devices    | 0     | mA    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

2. Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip oscillator is off, on-chip PLL is off.

3. Frequency = 0 MHz.

4.  $T_J = 25$  °C, power supplies at nominal voltage.

5. Does not include pull-up/pull-down.

6. To determine the MachXO2 peak start-up current data, use the Power Calculator tool.

# Programming and Erase Flash Supply Current – HC/HE Devices<sup>1, 2, 3, 4</sup>

| Symbol            | Parameter                      | Device         | Typ.⁵ | Units |

|-------------------|--------------------------------|----------------|-------|-------|

|                   |                                | LCMXO2-256HC   | 14.6  | mA    |

|                   |                                | LCMXO2-640HC   | 16.1  | mA    |

|                   |                                | LCMXO2-640UHC  | 18.8  | mA    |

|                   |                                | LCMXO2-1200HC  | 18.8  | mA    |

|                   |                                | LCMXO2-1200UHC | 22.1  | mA    |

|                   |                                | LCMXO2-2000HC  | 22.1  | mA    |

| I <sub>CC</sub>   | Core Power Supply              | LCMXO2-2000UHC | 26.8  | mA    |

|                   |                                | LCMXO2-4000HC  | 26.8  | mA    |

|                   |                                | LCMXO2-7000HC  | 33.2  | mA    |

|                   |                                | LCMXO2-2000HE  | 18.3  | mA    |

|                   |                                | LCMXO2-2000UHE | 20.4  | mA    |

|                   |                                | LCMXO2-4000HE  | 20.4  | mA    |

|                   |                                | LCMXO2-7000HE  | 23.9  | mA    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>6</sup> | All devices    | 0     | mA    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

2. Assumes all inputs are held at  $V_{CCIO}$  or GND and all outputs are tri-stated.

3. Typical user pattern.

4. JTAG programming is at 25 MHz.

5.  $T_J = 25$  °C, power supplies at nominal voltage.

6. Per bank.  $V_{CCIO} = 2.5$  V. Does not include pull-up/pull-down.

# Programming and Erase Flash Supply Current – ZE Devices<sup>1, 2, 3, 4</sup>

| Symbol                       | Parameter                      | Device        | Typ.⁵ | Units |

|------------------------------|--------------------------------|---------------|-------|-------|

|                              |                                | LCMXO2-256ZE  | 13    | mA    |

|                              |                                | LCMXO2-640ZE  | 14    | mA    |

| I <sub>CC</sub> Core Power S | Coro Bower Supply              | LCMXO2-1200ZE | 15    | mA    |

|                              | Core Fower Supply              | LCMXO2-2000ZE | 17    | mA    |

|                              |                                | LCMXO2-4000ZE | 18    | mA    |

|                              |                                | LCMXO2-7000ZE | 20    | mA    |

| ICCIO                        | Bank Power Supply <sup>6</sup> | All devices   | 0     | mA    |

1. For further information on supply current, please refer to TN1198, Power Estimation and Management for MachXO2 Devices.

2. Assumes all inputs are held at  $V_{\mbox{CCIO}}$  or GND and all outputs are tri-stated.

3. Typical user pattern.

4. JTAG programming is at 25 MHz.

5. TJ = 25 °C, power supplies at nominal voltage.

6. Per bank.  $V_{CCIO}$  = 2.5 V. Does not include pull-up/pull-down.

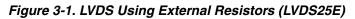

# LVDS Emulation

MachXO2 devices can support LVDS outputs via emulation (LVDS25E). The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all devices. The scheme shown in Figure 3-1 is one possible solution for LVDS standard implementation. Resistor values in Figure 3-1 are industry standard values for 1% resistors.

Note: All resistors are ±1%.

## Table 3-1. LVDS25E DC Conditions

#### **Over Recommended Operating Conditions**

| Parameter         | Description                 | Тур.  | Units |

|-------------------|-----------------------------|-------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20    | Ohms  |

| R <sub>S</sub>    | Driver series resistor      | 158   | Ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 140   | Ohms  |

| R <sub>T</sub>    | Receiver termination        | 100   | Ohms  |

| V <sub>OH</sub>   | Output high voltage         | 1.43  | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.07  | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.35  | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25  | V     |

| Z <sub>BACK</sub> | Back impedance              | 100.5 | Ohms  |

| I <sub>DC</sub>   | DC output current           | 6.03  | mA    |

|                      |                                                             |                     | -     | 6     | -     | -5    | -4    |      |       |

|----------------------|-------------------------------------------------------------|---------------------|-------|-------|-------|-------|-------|------|-------|

| Parameter            | Description                                                 | Device              | Min.  | Max.  | Min.  | Max.  | Min.  | Max. | Units |

|                      |                                                             | MachXO2-256HC-HE    | 1.42  | —     | 1.59  |       | 1.96  | —    | ns    |

|                      |                                                             | MachXO2-640HC-HE    | 1.41  | —     | 1.58  |       | 1.96  | —    | ns    |

| •                    | Clock to Data Setup – PIO<br>Input Register with Data Input | MachXO2-1200HC-HE   | 1.63  |       | 1.79  |       | 2.17  |      | ns    |

| <sup>t</sup> SU_DEL  | Delay                                                       | MachXO2-2000HC-HE   | 1.61  |       | 1.76  |       | 2.13  |      | ns    |

|                      |                                                             | MachXO2-4000HC-HE   | 1.66  |       | 1.81  | —     | 2.19  | —    | ns    |

|                      |                                                             | MachXO2-7000HC-HE   | 1.53  |       | 1.67  | —     | 2.03  | —    | ns    |

|                      |                                                             | MachXO2-256HC-HE    | -0.24 | —     | -0.24 | —     | -0.24 | —    | ns    |

|                      |                                                             | MachXO2-640HC-HE    | -0.23 | —     | -0.23 | —     | -0.23 | —    | ns    |

|                      | Clock to Data Hold – PIO Input                              | MachXO2-1200HC-HE   | -0.24 |       | -0.24 | —     | -0.24 | —    | ns    |

| t <sub>H_DEL</sub>   | Register with Input Data Delay                              | MachXO2-2000HC-HE   | -0.23 | —     | -0.23 | —     | -0.23 | —    | ns    |

|                      |                                                             | MachXO2-4000HC-HE   | -0.25 | —     | -0.25 | —     | -0.25 | —    | ns    |

|                      |                                                             | MachXO2-7000HC-HE   | -0.21 | —     | -0.21 |       | -0.21 | —    | ns    |

| f <sub>MAX_IO</sub>  | Clock Frequency of I/O and PFU Register                     | All MachXO2 devices | _     | 388   | _     | 323   | _     | 269  | MHz   |

| General I/O          | Pin Parameters (Using Edge C                                | lock without PLL)   |       |       |       | l     |       |      |       |

|                      |                                                             | MachXO2-1200HC-HE   | —     | 7.53  |       | 7.76  |       | 8.10 | ns    |

|                      |                                                             | MachXO2-2000HC-HE   | _     | 7.53  |       | 7.76  |       | 8.10 | ns    |

| t <sub>COE</sub>     |                                                             | MachXO2-4000HC-HE   | _     | 7.45  |       | 7.68  |       | 8.00 | ns    |

|                      |                                                             | MachXO2-7000HC-HE   | _     | 7.53  |       | 7.76  |       | 8.10 | ns    |

|                      |                                                             | MachXO2-1200HC-HE   | -0.19 |       | -0.19 | _     | -0.19 |      | ns    |

|                      | Clock to Data Setup – PIO                                   | MachXO2-2000HC-HE   | -0.19 | —     | -0.19 |       | -0.19 |      | ns    |

| SUE Input Register   | MachXO2-4000HC-HE                                           | -0.16               | —     | -0.16 |       | -0.16 |       | ns   |       |

|                      |                                                             | MachXO2-7000HC-HE   | -0.19 | —     | -0.19 |       | -0.19 |      | ns    |

|                      |                                                             | MachXO2-1200HC-HE   | 1.97  |       | 2.24  |       | 2.52  |      | ns    |

|                      | Clock to Data Hold – PIO Input                              | MachXO2-2000HC-HE   | 1.97  |       | 2.24  |       | 2.52  |      | ns    |

| t <sub>HE</sub>      | Register                                                    | MachXO2-4000HC-HE   | 1.89  |       | 2.16  |       | 2.43  |      | ns    |

|                      |                                                             | MachXO2-7000HC-HE   | 1.97  |       | 2.24  |       | 2.52  |      | ns    |

|                      |                                                             | MachXO2-1200HC-HE   | 1.56  |       | 1.69  |       | 2.05  |      | ns    |

|                      | Clock to Data Setup – PIO                                   | MachXO2-2000HC-HE   | 1.56  |       | 1.69  |       | 2.05  |      | ns    |

| <sup>t</sup> SU_DELE | Input Register with Data Input Delay                        | MachXO2-4000HC-HE   | 1.74  |       | 1.88  |       | 2.25  |      | ns    |

|                      | Delay                                                       | MachXO2-7000HC-HE   | 1.66  |       | 1.81  |       | 2.17  |      | ns    |

|                      |                                                             | MachXO2-1200HC-HE   | -0.23 |       | -0.23 |       | -0.23 |      | ns    |

|                      | Clock to Data Hold – PIO Input                              | MachXO2-2000HC-HE   | -0.23 |       | -0.23 |       | -0.23 |      | ns    |

| t <sub>H_DELE</sub>  | Register with Input Data Delay                              | MachXO2-4000HC-HE   | -0.34 |       | -0.34 |       | -0.34 |      | ns    |

|                      |                                                             | MachXO2-7000HC-HE   | -0.29 | _     | -0.29 |       | -0.29 |      | ns    |

| General I/O          | Pin Parameters (Using Primar                                |                     | 0.20  |       | 0.20  |       | 0.20  |      | 110   |

|                      |                                                             | MachXO2-1200HC-HE   | _     | 5.97  | _     | 6.00  | _     | 6.13 | ns    |

|                      | Clock to Output – PIO Output                                | MachXO2-2000HC-HE   | _     | 5.98  | _     | 6.01  | _     | 6.14 | ns    |

| t <sub>COPLL</sub>   |                                                             | MachXO2-4000HC-HE   |       | 5.99  |       | 6.02  |       | 6.16 | ns    |

|                      | -                                                           | MachXO2-7000HC-HE   |       | 6.02  |       | 6.06  |       | 6.20 | ns    |

|                      |                                                             | MachXO2-1200HC-HE   | 0.36  |       | 0.36  | 0.00  | 0.65  |      | ns    |

|                      | Cleak to Data Satura DIC                                    | MachXO2-2000HC-HE   | 0.36  |       | 0.36  |       | 0.63  | _    | ns    |

| t <sub>SUPLL</sub>   | Clock to Data Setup – PIO<br>Input Register                 | MachXO2-2000HC-HE   | 0.30  |       | 0.30  |       | 0.62  |      | ns    |

|                      |                                                             | MachXO2-7000HC-HE   | 0.35  |       | 0.35  |       | 0.62  |      |       |

|                      |                                                             |                     | 0.34  |       | 0.04  |       | 0.09  |      | ns    |

|                    |                                                                  |                                                                          | _       | -6       | _         | 5      | _       | 4       |                        |

|--------------------|------------------------------------------------------------------|--------------------------------------------------------------------------|---------|----------|-----------|--------|---------|---------|------------------------|

| Parameter          | Description                                                      | Device                                                                   | Min.    | Max.     | Min.      | Max.   | Min.    | Max.    | Units                  |

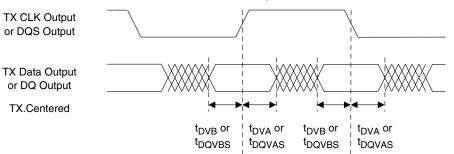

| Generic DDR        | X2 Outputs with Clock and Data                                   | Centered at Pin Using P                                                  | CLK Pin | for Cloc | k Input – | GDDRX  | 2_TX.EC | LK.Cen  | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>   | Output Data Valid Before CLK<br>Output                           |                                                                          | 0.535   | _        | 0.670     | _      | 0.830   | _       | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                                            | 0.535   | _        | 0.670     | _      | 0.830   | _       | ns                     |

| f <sub>DATA</sub>  | DDRX2 Serial Output Data<br>Speed                                | MachXO2-1200/U and larger devices, top side only.                        |         | 664      |           | 554    | _       | 462     | Mbps                   |

| f <sub>DDRX2</sub> | DDRX2 ECLK Frequency<br>(minimum limited by PLL)                 |                                                                          |         | 332      |           | 277    | _       | 231     | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                                          | _       | 166      | _         | 139    |         | 116     | MHz                    |

| Generic DDF        | X4 Outputs with Clock and Data                                   | Aligned at Pin Using P                                                   | CLK Pin | for Cloc | k Input   | - GDDR | X4_TX.E | CLK.Ali | gned <sup>9, 12</sup>  |

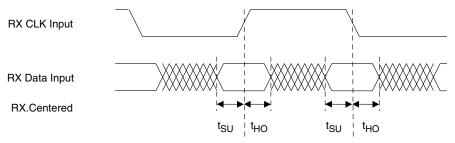

| t <sub>DIA</sub>   | Output Data Invalid After CLK<br>Output                          |                                                                          | _       | 0.200    | _         | 0.215  | _       | 0.230   | ns                     |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                         | MachXO2-640U,<br>MachXO2-1200/U and<br>larger devices, top side<br>only. |         | 0.200    | _         | 0.215  | _       | 0.230   | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Output Data<br>Speed                                |                                                                          |         | 756      |           | 630    | _       | 524     | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency                                             |                                                                          | _       | 378      |           | 315    | —       | 262     | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                                          | _       | 95       | _         | 79     |         | 66      | MHz                    |

| Generic DDF        | X4 Outputs with Clock and Data                                   | Centered at Pin Using Po                                                 | CLK Pin | for Cloc | k Input – | GDDRX  | 4_TX.EC | LK.Cen  | tered <sup>9, 12</sup> |

| t <sub>DVB</sub>   | Output Data Valid Before CLK<br>Output                           |                                                                          | 0.455   | _        | 0.570     |        | 0.710   | —       | ns                     |

| t <sub>DVA</sub>   | Output Data Valid After CLK<br>Output                            | MachXO2-640U,                                                            | 0.455   | _        | 0.570     |        | 0.710   | _       | ns                     |

| f <sub>DATA</sub>  | DDRX4 Serial Output Data<br>Speed                                | MachXO2-1200/U and larger devices, top side only.                        |         | 756      |           | 630    | _       | 524     | Mbps                   |

| f <sub>DDRX4</sub> | DDRX4 ECLK Frequency<br>(minimum limited by PLL)                 | ony.                                                                     |         | 378      |           | 315    | _       | 262     | MHz                    |

| f <sub>SCLK</sub>  | SCLK Frequency                                                   |                                                                          | _       | 95       | _         | 79     | —       | 66      | MHz                    |

| 7:1 LVDS Ou        | utputs - GDDR71_TX.ECLK.7:1                                      | 9, 12                                                                    |         |          |           |        |         |         |                        |

| t <sub>DIB</sub>   | Output Data Invalid Before<br>CLK Output                         |                                                                          | _       | 0.160    | _         | 0.180  |         | 0.200   | ns                     |

| t <sub>DIA</sub>   | Output Data Invalid After CLK<br>Output                          | MachXO2-640U,                                                            |         | 0.160    |           | 0.180  | _       | 0.200   | ns                     |

| f <sub>DATA</sub>  | DDR71 Serial Output Data<br>Speed                                | MachXO2-6400,<br>MachXO2-1200/U and<br>larger devices, top side<br>only. | _       | 756      | _         | 630    | _       | 524     | Mbps                   |

| f <sub>DDR71</sub> | DDR71 ECLK Frequency                                             |                                                                          | _       | 378      | _         | 315    | _       | 262     | MHz                    |

| fclkout            | 7:1 Output Clock Frequency<br>(SCLK) (minimum limited by<br>PLL) |                                                                          | _       | 108      | _         | 90     | _       | 75      | MHz                    |

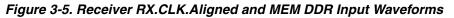

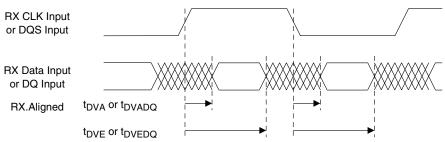

#### Figure 3-6. Receiver RX.CLK.Centered Waveforms

## Figure 3-7. Transmitter TX.CLK.Aligned Waveforms

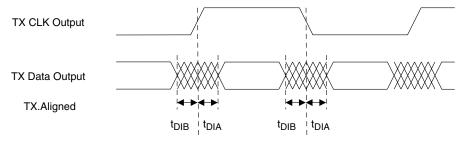

Figure 3-8. Transmitter TX.CLK.Centered and MEM DDR Output Waveforms

# Flash Download Time<sup>1, 2</sup>

| Symbol               | Parameter                | Device       | Тур. | Units |

|----------------------|--------------------------|--------------|------|-------|

|                      |                          | LCMXO2-256   | 0.6  | ms    |

|                      |                          | LCMXO2-640   | 1.0  | ms    |

|                      |                          | LCMXO2-640U  | 1.9  | ms    |

|                      |                          | LCMXO2-1200  | 1.9  | ms    |

| t <sub>REFRESH</sub> | POR to Device I/O Active | LCMXO2-1200U | 1.4  | ms    |

|                      |                          | LCMXO2-2000  | 1.4  | ms    |

|                      |                          | LCMXO2-2000U | 2.4  | ms    |

|                      |                          | LCMXO2-4000  | 2.4  | ms    |

|                      |                          | LCMXO2-7000  | 3.8  | ms    |

1. Assumes sysMEM EBR initialized to an all zero pattern if they are used.

2. The Flash download time is measured starting from the maximum voltage of POR trip point.

# **JTAG Port Timing Specifications**

| Symbol               | Parameter                                                          | Min. | Max. | Units |

|----------------------|--------------------------------------------------------------------|------|------|-------|

| f <sub>MAX</sub>     | TCK clock frequency                                                |      | 25   | MHz   |

| t <sub>BTCPH</sub>   | TCK [BSCAN] clock pulse width high                                 | 20   | —    | ns    |

| t <sub>BTCPL</sub>   | TCK [BSCAN] clock pulse width low                                  | 20   | —    | ns    |

| t <sub>BTS</sub>     | TCK [BSCAN] setup time                                             | 10   | —    | ns    |

| t <sub>BTH</sub>     | TCK [BSCAN] hold time                                              | 8    | —    | ns    |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to valid output               | _    | 10   | ns    |

| t <sub>BTCODIS</sub> | TAP controller falling edge of clock to valid disable              | _    | 10   | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to valid enable               | _    | 10   | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                             | 8    | —    | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                              | 20   | —    | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to valid output  | _    | 25   | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to valid disable | _    | 25   | ns    |

| t <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  |      | 25   | ns    |

# Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging

| Part Number                            | LUTs              | Supply Voltage | Grade | Package            | Leads | Temp. |

|----------------------------------------|-------------------|----------------|-------|--------------------|-------|-------|

| LCMXO2-256ZE-1SG32I                    | 256               | 1.2 V          | -1    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256ZE-2SG32I                    | 256               | 1.2 V          | -2    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256ZE-3SG32I                    | 256               | 1.2 V          | -3    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-256ZE-1UMG64I                   | 256               | 1.2 V          | -1    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256ZE-2UMG64I                   | 256               | 1.2 V          | -2    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256ZE-3UMG64I                   | 256               | 1.2 V          | -3    | Halogen-Free ucBGA | 64    | IND   |

| LCMXO2-256ZE-1TG100I                   | 256               | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256ZE-2TG100I                   | 256               | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256ZE-3TG100I                   | 256               | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-256ZE-1MG132I                   | 256               | 1.2 V          | -1    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-256ZE-2MG132I                   | 256               | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-256ZE-3MG132I                   | 256               | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

| Part Number                            | LUTs              | Supply Voltage | Grade | Package            | Leads | Temp. |

| LCMXO2-640ZE-1TG100I                   | 640               | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640ZE-2TG100I                   | 640               | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640ZE-3TG100I                   | 640               | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-640ZE-1MG132I                   | 640               | 1.2 V          |       | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-640ZE-2MG132I                   | 640               | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-640ZE-3MG132I                   | 640               | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

|                                        | 0.0               |                |       |                    |       |       |

| Part Number                            | LUTs              | Supply Voltage | Grade | Package            | Leads | Temp. |

| LCMXO2-1200ZE-1UWG25ITR1               | 1280              | 1.2 V          | -1    | Halogen-Free WLCSP | 25    | IND   |

| LCMXO2-1200ZE-1UWG25ITR50 <sup>3</sup> | <sup>3</sup> 1280 | 1.2 V          | -1    | Halogen-Free WLCSP | 25    | IND   |

| LCMXO2-1200ZE-1UWG25ITR1K              | <sup>2</sup> 1280 | 1.2 V          | -1    | Halogen-Free WLCSP | 25    | IND   |

| LCMXO2-1200ZE-1SG32I                   | 1280              | 1.2 V          | -1    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200ZE-2SG32I                   | 1280              | 1.2 V          | -2    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200ZE-3SG32I                   | 1280              | 1.2 V          | -3    | Halogen-Free QFN   | 32    | IND   |

| LCMXO2-1200ZE-1TG100I                  | 1280              | 1.2 V          | -1    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200ZE-2TG100I                  | 1280              | 1.2 V          | -2    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200ZE-3TG100I                  | 1280              | 1.2 V          | -3    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-1200ZE-1MG132I                  | 1280              | 1.2 V          | -1    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200ZE-2MG132I                  | 1280              | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200ZE-3MG132I                  | 1280              | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-1200ZE-1TG144I                  | 1280              | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-1200ZE-2TG144I                  | 1280              | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

|                                        |                   |                |       |                    |       |       |

1. This part number has a tape and reel quantity of 5,000 units with a minimum order quantity of 10,000 units. Order quantities must be in increments of 5,000 units. For example, a 10,000 unit order will be shipped in two reels with one reel containing 5,000 units and the other reel with less than 5,000 units (depending on test yields). Unserviced backlog will be canceled.

2. This part number has a tape and reel quantity of 1,000 units with a minimum order quantity of 1,000. Order quantities must be in increments of 1,000 units. For example, a 5,000 unit order will be shipped as 5 reels of 1000 units each.

3. This part number has a tape and reel quantity of 50 units with a minimum order quantity of 50. Order quantities must be in increments of 50 units. For example, a 1,000 unit order will be shipped as 20 reels of 50 units each.

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000ZE-1QN84I   | 4320 | 1.2 V          | -1    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000ZE-2QN84I   | 4320 | 1.2 V          | -2    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000ZE-3QN84I   | 4320 | 1.2 V          | -3    | Halogen-Free QFN   | 84    | IND   |

| LCMXO2-4000ZE-1MG132I  | 4320 | 1.2 V          | -1    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000ZE-2MG132I  | 4320 | 1.2 V          | -2    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000ZE-3MG132I  | 4320 | 1.2 V          | -3    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000ZE-1TG144I  | 4320 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000ZE-2TG144I  | 4320 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000ZE-3TG144I  | 4320 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000ZE-1BG256I  | 4320 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000ZE-2BG256I  | 4320 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000ZE-3BG256I  | 4320 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000ZE-1FTG256I | 4320 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000ZE-2FTG256I | 4320 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000ZE-3FTG256I | 4320 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000ZE-1BG332I  | 4320 | 1.2 V          | -1    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000ZE-2BG332I  | 4320 | 1.2 V          | -2    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000ZE-3BG332I  | 4320 | 1.2 V          | -3    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000ZE-1FG484I  | 4320 | 1.2 V          | -1    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000ZE-2FG484I  | 4320 | 1.2 V          | -2    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000ZE-3FG484I  | 4320 | 1.2 V          | -3    | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000ZE-1TG144I  | 6864 | 1.2 V          | -1    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000ZE-2TG144I  | 6864 | 1.2 V          | -2    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000ZE-3TG144I  | 6864 | 1.2 V          | -3    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000ZE-1BG256I  | 6864 | 1.2 V          | -1    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000ZE-2BG256I  | 6864 | 1.2 V          | -2    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000ZE-3BG256I  | 6864 | 1.2 V          | -3    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000ZE-1FTG256I | 6864 | 1.2 V          | -1    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000ZE-2FTG256I | 6864 | 1.2 V          | -2    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000ZE-3FTG256I | 6864 | 1.2 V          | -3    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000ZE-1BG332I  | 6864 | 1.2 V          | -1    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000ZE-2BG332I  | 6864 | 1.2 V          | -2    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000ZE-3BG332I  | 6864 | 1.2 V          | -3    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000ZE-1FG484I  | 6864 | 1.2 V          | -1    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000ZE-2FG484I  | 6864 | 1.2 V          | -2    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000ZE-3FG484I  | 6864 | 1.2 V          | -3    | Halogen-Free fpBGA | 484   | IND   |

# High Performance Industrial Grade Devices Without Voltage Regulator, Halogen Free (RoHS) Packaging

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000HE-4TG100I  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-5TG100I  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-6TG100I  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 100   | IND   |

| LCMXO2-2000HE-4MG132I  | 2112 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-5MG132I  | 2112 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-6MG132I  | 2112 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-2000HE-4TG144I  | 2112 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-5TG144I  | 2112 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-6TG144I  | 2112 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-2000HE-4BG256I  | 2112 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-5BG256I  | 2112 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-6BG256I  | 2112 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-2000HE-4FTG256I | 2112 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HE-5FTG256I | 2112 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-2000HE-6FTG256I | 2112 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-2000UHE-4FG484I | 2112 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHE-5FG484I | 2112 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-2000UHE-6FG484I | 2112 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-4000HE-4MG132I  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-5MG132I  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-6MG132I  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 132   | IND   |

| LCMXO2-4000HE-4TG144I  | 4320 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-5TG144I  | 4320 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-6TG144I  | 4320 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-4000HE-4MG184I  | 4320 | 1.2 V          | -4    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-5MG184I  | 4320 | 1.2 V          | -5    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-6MG184I  | 4320 | 1.2 V          | -6    | Halogen-Free csBGA | 184   | IND   |

| LCMXO2-4000HE-4BG256I  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-5BG256I  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-6BG256I  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-4000HE-4FTG256I | 4320 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-5FTG256I | 4320 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-6FTG256I | 4320 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-4000HE-4BG332I  | 4320 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-5BG332I  | 4320 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-6BG332I  | 4320 | 1.2 V          | -6    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-4000HE-4FG484I  | 4320 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000HE-5FG484I  | 4320 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-4000HE-6FG484I  | 4320 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | IND   |

| Part Number            | LUTs | Supply Voltage | Grade | Package            | Leads | Temp. |

|------------------------|------|----------------|-------|--------------------|-------|-------|

| LCMXO2-7000HE-4TG144I  | 6864 | 1.2 V          | -4    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-5TG144I  | 6864 | 1.2 V          | -5    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-6TG144I  | 6864 | 1.2 V          | -6    | Halogen-Free TQFP  | 144   | IND   |

| LCMXO2-7000HE-4BG256I  | 6864 | 1.2 V          | -4    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-5BG256I  | 6864 | 1.2 V          | -5    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-6BG256I  | 6864 | 1.2 V          | -6    | Halogen-Free caBGA | 256   | IND   |

| LCMXO2-7000HE-4FTG256I | 6864 | 1.2 V          | -4    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-5FTG256I | 6864 | 1.2 V          | -5    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-6FTG256I | 6864 | 1.2 V          | -6    | Halogen-Free ftBGA | 256   | IND   |

| LCMXO2-7000HE-4BG332I  | 6864 | 1.2 V          | -4    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-5BG332I  | 6864 | 1.2 V          | -5    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-6BG332I  | 6864 | 1.2 V          | -6    | Halogen-Free caBGA | 332   | IND   |

| LCMXO2-7000HE-4FG484I  | 6864 | 1.2 V          | -4    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000HE-5FG484I  | 6864 | 1.2 V          | -5    | Halogen-Free fpBGA | 484   | IND   |

| LCMXO2-7000HE-6FG484I  | 6864 | 1.2 V          | -6    | Halogen-Free fpBGA | 484   | IND   |