## Microchip Technology - PIC24F04KL100-E/P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 4KB (1.375K x 24)                                                           |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 14-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04kl100-e-p |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and bussing. This architecture also allows the direct access of program memory from the data space during code execution.

## 4.1 **Program Address Space**

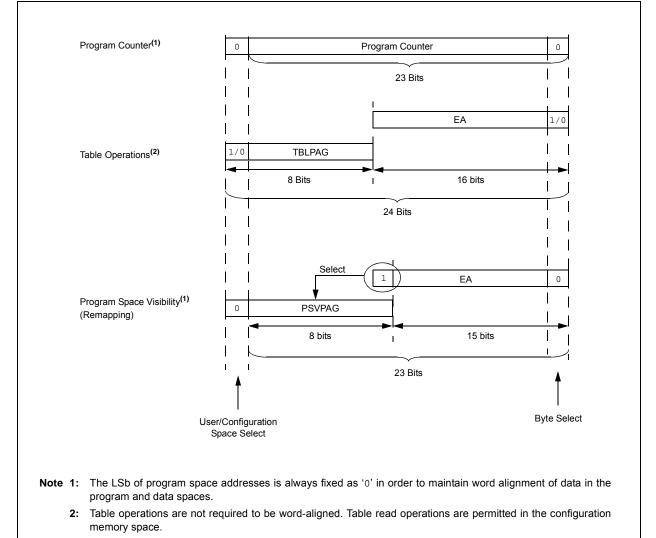

The program address memory space of the PIC24F16KL402 family is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24F16KL402 family of devices are shown in Figure 4-1.

## FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24F16KL402 FAMILY DEVICES

|                            | PIC24F04KLXXX                                                                                                                                       | PIC24F08KL2XX                                                                                              | PIC24F08KL3XX                                                                                              |       | PIC24F08KL4XX                                                                                              | PIC24F16KLXXX                                                                                     |                                                                                    |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                            | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash<br>Program Memory<br>(1408 instructions) | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash |       | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table<br>Flash | GOTO Instruction<br>Reset Address<br>Interrupt Vector Table<br>Reserved<br>Alternate Vector Table | 000000h<br>00002h<br>00004h<br>0000FEh<br>000100h<br>000104h<br>0001FEh<br>000200h |

| User Memory Space          |                                                                                                                                                     | Program Memory<br>(2816 instructions)                                                                      | <br>Program Memory<br>(2816 instructions)                                                                  | -     | Program Memory<br>(2816 instructions)                                                                      | <br>Flash<br>Program Memory<br>(5632 instructions)                                                | - 000AFEh                                                                          |

| User Me                    | Unimplemented<br>Read '0'                                                                                                                           | Unimplemented<br>Read '0'                                                                                  | Unimplemented<br>Read '0'                                                                                  |       | Unimplemented<br>Read '0'                                                                                  | Unimplemented                                                                                     | 002BFEh                                                                            |

|                            |                                                                                                                                                     |                                                                                                            | <br>Data EEPROM<br>(256 bytes)                                                                             | -<br> | Data EEPROM<br>(512 bytes)                                                                                 | <br>Read '0'<br>Data EEPROM<br>(512 bytes)                                                        | <ul> <li>7FFE00h</li> <li>7FFF00h</li> <li>7FFFFFh</li> <li>800000h</li> </ul>     |

| Ī                          | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 800800h                                                                            |

| ace                        | Unique ID                                                                                                                                           | Unique ID                                                                                                  | Unique ID                                                                                                  |       | Unique ID                                                                                                  | Unique ID                                                                                         | 800802h<br>800808h                                                                 |

| lory Sp                    | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | 80080Ah                                                                            |

| Mem                        | Device Config Registers                                                                                                                             | Device Config Registers                                                                                    | Device Config Registers                                                                                    |       | Device Config Registers                                                                                    | Device Config Registers                                                                           | F80000h<br>F8000Eh                                                                 |

| Configuration Memory Space | Reserved                                                                                                                                            | Reserved                                                                                                   | Reserved                                                                                                   |       | Reserved                                                                                                   | Reserved                                                                                          | F80010h<br>FEFFFEh                                                                 |

|                            | DEVID (2)                                                                                                                                           | DEVID (2)                                                                                                  | DEVID (2)                                                                                                  |       | DEVID (2)                                                                                                  | DEVID (2)                                                                                         | FF0000h<br>FFFFFFh                                                                 |

Note: Memory areas are not displayed to scale.

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address, as shown in Figure 4-2.

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h, with the actual address for the start of code at 000002h.

PIC24F devices also have two Interrupt Vector Tables (IVT), located from 000004h to 0000FFh and 000104h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. A more detailed discussion of the Interrupt Vector Tables is provided in **Section 8.1** "Interrupt Vector Table (IVT)".

## 4.1.3 DATA EEPROM

In the PIC24F16KL402 family, the data EEPROM is mapped to the top of the user program memory space, starting at address, 7FFE00, and expanding up to address, 7FFFF.

The data EEPROM is organized as 16-bit wide memory and 256 words deep. This memory is accessed using Table Read and Table Write operations, similar to the user code memory.

## 4.1.4 DEVICE CONFIGURATION WORDS

Table 4-1 provides the addresses of the device Configuration Words for the PIC24F16KL402 family. Their location in the memory map is shown in Figure 4-1.

For more information on device Configuration Words, see **Section 23.0 "Special Features"**.

### TABLE 4-1: DEVICE CONFIGURATION WORDS FOR PIC24F16KL402 FAMILY DEVICES

| Configuration Words | Configuration Word<br>Addresses |

|---------------------|---------------------------------|

| FBS                 | F80000                          |

| FGS                 | F80004                          |

| FOSCSEL             | F80006                          |

| FOSC                | F80008                          |

| FWDT                | F8000A                          |

| FPOR                | F8000C                          |

| FICD                | F8000E                          |

## FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| msw<br>Address | most significant wo                               | ord I   | east significant wo | rd | PC Address<br>(Isw Address) |

|----------------|---------------------------------------------------|---------|---------------------|----|-----------------------------|

|                | 23                                                | 16      | 8                   | 0  |                             |

| 000001h        | 0000000                                           |         |                     |    | 000000h                     |

| 000003h        | 0000000                                           |         |                     |    | 000002h                     |

| 000005h        | 0000000                                           |         |                     |    | 000004h                     |

| 000007h        | 0000000                                           |         |                     |    | 000006h                     |

|                |                                                   |         | $\sim$              |    |                             |

|                | Program Memory<br>'Phantom' Byte<br>(read as '0') | Instruc | tion Width          |    |                             |

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

|              | чυ.  |        |                      | 1 001                |                      |                     |            |                       |            |       |            |            |            |         |                       |                       |          |               |

|--------------|------|--------|----------------------|----------------------|----------------------|---------------------|------------|-----------------------|------------|-------|------------|------------|------------|---------|-----------------------|-----------------------|----------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14               | Bit 13               | Bit 12               | Bit 11              | Bit 10     | Bit 9                 | Bit 8      | Bit 7 | Bit 6      | Bit 5      | Bit 4      | Bit 3   | Bit 2                 | Bit 1                 | Bit 0    | All<br>Resets |

| INTCON1      | 0080 | NSTDIS | —                    | —                    | —                    | —                   | —          | —                     | —          | _     | —          | —          | MATHERR    | ADDRERR | STKERR                | OSCFAIL               | —        | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI                 | _                    | —                    | —                   | _          | _                     | —          | —     | _          | —          | _          | _       | INT2EP                | INT1EP                | INT0EP   | 0000          |

| IFS0         | 0084 | NVMIF  | _                    | AD1IF                | U1TXIF               | U1RXIF              | _          | _                     | T3IF       | T2IF  | CCP2IF     | _          | _          | T1IF    | CCP1IF                | _                     | INT0IF   | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF               | INT2IF               | _                    | T4IF <sup>(1)</sup> | _          | CCP3IF <sup>(1)</sup> | _          | _     | _          | _          | INT1IF     | CNIF    | CMIF                  | BCL1IF                | SSP1IF   | 0000          |

| IFS2         | 8800 |        | _                    | _                    | _                    |                     | _          | _                     | _          | _     | _          | T3GIF      | _          | _       | _                     | _                     | _        | 0000          |

| IFS3         | 008A | —      | _                    | _                    | —                    | —                   | _          | _                     | —          | —     | _          | —          | _          | _       | BCL2IF <sup>(1)</sup> | SSP2IF <sup>(1)</sup> | —        | 0000          |

| IFS4         | 008C | —      | _                    | _                    | —                    | _                   | _          | _                     | HLVDIF     | _     | _          | _          | _          | _       | U2ERIF                | U1ERIF                | _        | 0000          |

| IFS5         | 008E | —      | _                    | _                    | —                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | _                     | _                     | ULPWUIF  | 0000          |

| IEC0         | 0094 | NVMIE  | _                    | AD1IE                | U1TXIE               | U1RXIE              | _          | _                     | T3IE       | T2IE  | CCP2IE     | _          | _          | T1IE    | CCP1IE                | _                     | INT0IE   | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE               | INT2IE               | —                    | T4IE <sup>(1)</sup> | _          | CCP3IE <sup>(1)</sup> | _          | _     | _          | _          | INT1IE     | CNIE    | CMIE                  | BCL1IE                | SSP1IE   | 0000          |

| IEC2         | 0098 | _      | _                    | -                    | —                    | _                   | _          | _                     | _          |       | _          | T3GIE      | _          | _       | _                     | _                     | -        | 0000          |

| IEC3         | 009A | _      | _                    |                      | —                    | _                   | _          | _                     | _          |       | _          | _          | -          | _       | BCL2IE <sup>(1)</sup> | SSP2IE <sup>(1)</sup> |          | 0000          |

| IEC4         | 009C | _      | _                    |                      | —                    | _                   | _          | _                     | HLVDIE     |       | _          | _          | -          | _       | U2ERIE                | U1ERIE                |          | 0000          |

| IEC5         | 009E | _      | _                    |                      | —                    | _                   | _          | _                     | _          |       | _          | _          | -          | _       | _                     | _                     | ULPWUIE  | 0000          |

| IPC0         | 00A4 | —      | T1IP2                | T1IP1                | T1IP0                | _                   | CCP1IP2    | CCP1IP1               | CCP1IP0    | _     | _          | _          | _          | _       | INT0IP2               | INT0IP1               | INT0IP0  | 4404          |

| IPC1         | 00A6 | _      | T2IP2                | T2IP1                | T2IP0                | _                   | CCP2IP2    | CCP2IP1               | CCP2IP0    |       | _          | _          | -          | _       | _                     | _                     | -        | 4400          |

| IPC2         | 00A8 | _      | U1RXIP2              | U1RXIP1              | U1RXIP0              | _                   | _          | _                     | _          |       | _          | _          | -          | _       | T3IP2                 | T3IP1                 | T3IP0    | 4004          |

| IPC3         | 00AA | _      | NVMIP2               | NVMIP1               | NVMIP0               | _                   | _          | _                     | _          |       | AD1IP2     | AD1IP1     | AD1IP0     | _       | U1TXIP2               | U1TXIP1               | U1TXIP0  | 4044          |

| IPC4         | 00AC | _      | CNIP2                | CNIP1                | CNIP0                | _                   | CMIP2      | CMIP1                 | CMIP0      |       | BCL1IP2    | BCL1IP1    | BCL1IP0    | _       | SSP1IP2               | SSP1IP1               | SS1IP0   | 4444          |

| IPC5         | 00AE | _      | _                    | -                    | —                    | _                   | _          | _                     | _          |       | _          | _          | _          | _       | INT1IP2               | INT1IP1               | INT1IP0  | 0004          |

| IPC6         | 00B0 | _      | T4IP2 <sup>(1)</sup> | T4IP1 <sup>(1)</sup> | T4IP0 <sup>(1)</sup> | _                   | _          | _                     | _          |       | CCP3IP2(1) | CCP3IP1(1) | CCP3IP0(1) | _       | —                     | —                     |          | 4040          |

| IPC7         | 00B2 | _      | U2TXIP2              | U2TXIP1              | U2TXIP0              | _                   | U2RXIP2    | U2RXIP1               | U2RXIP0    |       | INT2IP2    | INT2IP1    | INT2IP0    | _       | _                     | _                     |          | 4440          |

| IPC9         | 00B6 | _      | _                    | -                    | —                    | _                   | _          | —                     | _          |       | T3GIP2     | T3GIP1     | T3GIP0     | _       | _                     | _                     |          | 0040          |

| IPC12        | 00BC | _      | _                    | _                    | —                    | _                   | BCL2IP2(1) | BCL2IP1(1)            | BCL2IP0(1) |       | SSP2IP2(1) | SSP2IP1(1) | SSP2IP0(1) | _       | _                     | _                     |          | 0440          |

| IPC16        | 00C4 | _      | _                    | _                    | _                    | _                   | U2ERIP2    | U2ERIP1               | U2ERIP0    | _     | U1ERIP2    | U1ERIP1    | U1ERIP0    | _       | _                     | —                     | _        | 0440          |

| IPC18        | 00C8 | _      | _                    | _                    | _                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | HLVDIP2               | HLVDIP1               | HLVDIP0  | 0004          |

| IPC20        | 00CC | _      | _                    | _                    | _                    | _                   | _          | _                     | _          | _     | _          | _          | _          | _       | ULPWUIP2              | ULPWUIP1              | ULPWUIP0 | 0004          |

| INTTREG      | 00E0 | CPUIRQ | r                    | VHOLD                | _                    | ILR3                | ILR2       | ILR1                  | ILR0       | _     | VECNUM6    | VECNUM5    | VECNUM4    | VECNUM3 | VECNUM2               | VECNUM1               | VECNUM0  | 0000          |

Legend: Note 1:

Legend: — = unimplemented, read as '0', r = reserved. Reset values are shown in hexadecimal.

Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X family devices; read as '0'.

| A                                     | Access        | Program Space Address |            |                        |                      |     |  |  |  |  |

|---------------------------------------|---------------|-----------------------|------------|------------------------|----------------------|-----|--|--|--|--|

| Access Type                           | Space         | <23>                  | <22:16>    | <15>                   | <14:1>               | <0> |  |  |  |  |

| Instruction Access                    | User          | 0 PC<22:1>            |            |                        | 0                    |     |  |  |  |  |

| (Code Execution)                      |               |                       | 0xx xxxx x | xxx xxxx               | x xxxx xxx0          |     |  |  |  |  |

| TBLRD/TBLWT<br>(Byte/Word Read/Write) | User          | TBI                   | _PAG<7:0>  |                        | Data EA<15:0>        |     |  |  |  |  |

|                                       |               | د0                    | xxx xxxx   | XXXX XXXX XXXX XXXX    |                      |     |  |  |  |  |

|                                       | Configuration | TBI                   | _PAG<7:0>  | Data EA<15:0>          |                      |     |  |  |  |  |

|                                       |               | 12                    | xxx xxxx   |                        |                      |     |  |  |  |  |

| Program Space Visibility              | User          | 0                     | PSVPAG<7:  | 0>(2) Data EA<14:0>(1) |                      |     |  |  |  |  |

| (Block Remap/Read)                    |               | 0                     | XXXX XXX   | xx                     | x xxx xxxx xxxx xxxx |     |  |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on PIC24F16KL402 family devices.

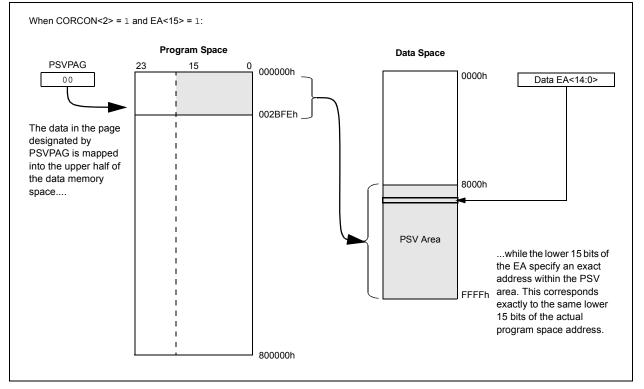

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into a 16K word page of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the MSb of the data space EA is '1' and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address (PSVPAG) register. This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the

24-bit program word are used to contain the data. The upper 8 bits of any program space location, used as data, should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

## Note: PSV access is temporarily disabled during Table Reads/Writes.

For operations that use PSV and are executed outside of a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle, in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles, in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

## FIGURE 4-7: PROGRAM SPACE VISIBILITY OPERATION

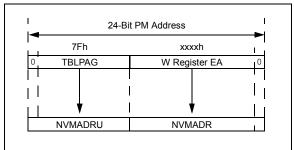

## 6.3 NVM Address Register

As with Flash program memory, the NVM Address Registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and selects the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", is unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

## 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Table Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

| Note: | Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | The C30 C compiler includes library<br>procedures to automatically perform the<br>Table Read and Table Write operations,<br>manage the Table Pointer and write<br>buffers, and unlock and initiate memory<br>write sequences. This eliminates the need<br>to create assembler macros or time<br>critical routines in C for each application. |

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the C30 compiler libraries.

## 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

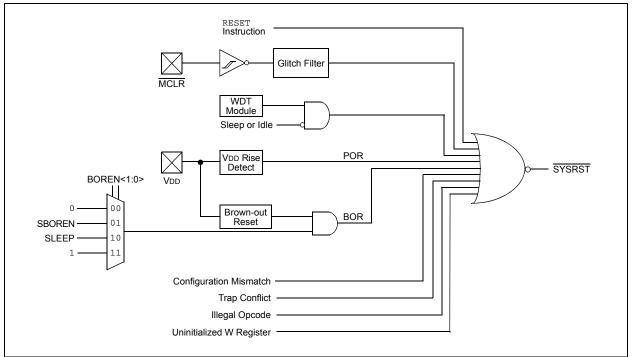

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- · UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on a Power-on Reset (POR) and unchanged by all other Resets.

**Note:** Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A POR will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value, after a device Reset, will be meaningful.

## FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

**REGISTER 7-1:**

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0     | 0 R/W-0                                | R/W-0 <sup>(3)</sup>                    | U-0             | U-0                   | U-0                        | R/W-0            | R/W-0           |  |  |  |

|-----------|----------------------------------------|-----------------------------------------|-----------------|-----------------------|----------------------------|------------------|-----------------|--|--|--|

| TRAP      | R IOPUWR                               | SBOREN                                  | _               | —                     | _                          | CM               | PMSLP           |  |  |  |

| bit 15    |                                        |                                         |                 |                       |                            |                  | bit 8           |  |  |  |

|           |                                        |                                         |                 |                       |                            |                  |                 |  |  |  |

| R/W-0     | 0 R/W-0                                | R/W-0                                   | R/W-0           | R/W-0                 | R/W-0                      | R/W-1            | R/W-1           |  |  |  |

| EXTR      | R SWR                                  | SWDTEN <sup>(2)</sup>                   | WDTO            | SLEEP                 | IDLE                       | BOR              | POR             |  |  |  |

| bit 7     |                                        |                                         |                 |                       |                            |                  | bit 0           |  |  |  |

|           |                                        |                                         |                 |                       |                            |                  |                 |  |  |  |

| Legend:   |                                        |                                         | :4              |                       | a a material in the second |                  |                 |  |  |  |

| R = Read  |                                        | W = Writable b                          | IT              | •                     | nented bit, read           |                  |                 |  |  |  |

| -n = Valu | e at POR                               | '1' = Bit is set                        |                 | '0' = Bit is cle      | ared                       | x = Bit is unkr  | nown            |  |  |  |

| bit 15    | TRAPR. Tra                             | p Reset Flag bit                        |                 |                       |                            |                  |                 |  |  |  |

| bit io    |                                        | Conflict Reset has                      | occurred        |                       |                            |                  |                 |  |  |  |

|           |                                        | Conflict Reset has                      |                 | b                     |                            |                  |                 |  |  |  |

| bit 14    | IOPUWR: III                            | egal Opcode or L                        | Jninitialized V | V Access Reset        | Flag bit                   |                  |                 |  |  |  |

|           | 1 = An illega                          | al opcode detecti                       | on, an illegal  | address mode          | or an Uninitial            | ized W register  | r is used as an |  |  |  |

|           |                                        | Pointer and cau                         |                 |                       |                            |                  |                 |  |  |  |

|           | -                                      | al opcode or Unin                       |                 | -                     | is not occurred            |                  |                 |  |  |  |

| bit 13    |                                        | oftware Enable/D                        |                 | R bit <sup>(3)</sup>  |                            |                  |                 |  |  |  |

|           |                                        | urned on in softw<br>urned off in softw |                 |                       |                            |                  |                 |  |  |  |

| bit 12-10 | Unimpleme                              | Unimplemented: Read as '0'              |                 |                       |                            |                  |                 |  |  |  |

| bit 9     | CM: Configu                            | ration Word Misn                        | natch Reset I   | Flag bit              |                            |                  |                 |  |  |  |

|           |                                        | uration Word Mis                        |                 |                       |                            |                  |                 |  |  |  |

|           | •                                      | uration Word Mis                        |                 |                       | ed                         |                  |                 |  |  |  |

| bit 8     |                                        | gram Memory Po                          | •               | •                     |                            |                  |                 |  |  |  |

|           |                                        | memory bias vo<br>memory bias vo        |                 |                       |                            |                  |                 |  |  |  |

| h:+ 7     |                                        | mal Reset (MCLF                         |                 |                       | y Sleep                    |                  |                 |  |  |  |

| bit 7     |                                        | r Clear (pin) Rese                      | ,               | ed                    |                            |                  |                 |  |  |  |

|           |                                        | r Clear (pin) Rese                      |                 |                       |                            |                  |                 |  |  |  |

| bit 6     | SWR: Softwa                            | are Reset (Instru                       | ction) Flag bi  | t                     |                            |                  |                 |  |  |  |

|           |                                        | instruction has t                       |                 |                       |                            |                  |                 |  |  |  |

|           |                                        | r instruction has r                     |                 |                       |                            |                  |                 |  |  |  |

| bit 5     | SWDTEN: S                              | oftware Enable/D                        | Disable of WE   | )T bit <sup>(2)</sup> |                            |                  |                 |  |  |  |

|           | 1 = WDT is e                           |                                         |                 |                       |                            |                  |                 |  |  |  |

| 1.11.4    | 0 = WDT is 0                           |                                         |                 |                       |                            |                  |                 |  |  |  |

| bit 4     |                                        | chdog Timer Time                        | -               |                       |                            |                  |                 |  |  |  |

|           |                                        | e-out has occurre                       |                 |                       |                            |                  |                 |  |  |  |

| Note 1.   | All of the Depart                      | tatua hita may ha                       | act or closer   | d in coffword C       | atting one of th           | ana hita in aaft | wara daga nat   |  |  |  |

| Note 1:   | All of the Reset s<br>cause a device F | •                                       | set of cleare   | eu în soitware. S     | beaung one of th           | IESE DIIS IN SOT | ware upes not   |  |  |  |

| 2:        | If the FWDTEN (                        |                                         | is '1' (unprog  | rammed), the V        | VDT is always o            | enabled, regard  | dless of the    |  |  |  |

|           | SWDTEN bit set                         | -                                       |                 | ,-                    |                            |                  |                 |  |  |  |

| 3.        | The SBOREN bi                          | it is forced to '0' v                   | vhen disabler   | d by the Config       | iration hits BO            | REN<1.0> (FP     | POR<1.0>        |  |  |  |

**3:** The SBOREN bit is forced to '0' when disabled by the Configuration bits, BOREN<1:0> (FPOR<1:0>). When the Configuration bits are set to enable SBOREN, the default Reset state will be '1'.

####

| U-0          | U-0                                                                                                                 | U-0                                | U-0              | U-0                   | U-0                   | U-0                   | U-0                   |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

|              | _                                                                                                                   |                                    |                  |                       |                       |                       | _                     |  |  |  |  |

| oit 15       |                                                                                                                     |                                    |                  |                       |                       |                       | bit                   |  |  |  |  |

| R/W-0        | R/W-0                                                                                                               |                                    |                  |                       |                       | R/W-0                 | R/W-0                 |  |  |  |  |

| -            |                                                                                                                     | R/W-0                              | R/W-0            | R/W-0                 | R/W-0                 |                       |                       |  |  |  |  |

| PM1          | PM0                                                                                                                 | DC1B1                              | DC1B0            | CCP1M3 <sup>(2)</sup> | CCP1M2 <sup>(2)</sup> | CCP1M1 <sup>(2)</sup> | CCP1M0 <sup>(2)</sup> |  |  |  |  |

| oit 7        |                                                                                                                     |                                    |                  |                       |                       |                       | bit                   |  |  |  |  |

| Legend:      |                                                                                                                     |                                    |                  |                       |                       |                       |                       |  |  |  |  |

| R = Readal   | ble bit                                                                                                             | W = Writable                       | bit              | U = Unimplen          | nented bit, read      | d as '0'              |                       |  |  |  |  |

| -n = Value a | at POR                                                                                                              | '1' = Bit is set                   |                  | '0' = Bit is clea     | ared                  | x = Bit is unkr       | nown                  |  |  |  |  |

| oit 15-8     | Unimplemen                                                                                                          | ted: Read as '                     | י'               |                       |                       |                       |                       |  |  |  |  |

| bit 7-6      | -                                                                                                                   | hanced PWM (                       |                  | ration bits           |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | 2> = 00, 01, 10                    |                  |                       |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | ssigned as a ca                    |                  | ompare output;        | P1B, P1C and          | P1D are assign        | ed as port pir        |  |  |  |  |

|              | <u>If CCP1M&lt;3:2</u>                                                                                              | •                                  |                  |                       |                       | 0                     |                       |  |  |  |  |

|              |                                                                                                                     | ge output reve                     | rse: P1B is mo   | dulated; P1C is       | active; P1A a         | nd P1D are ina        | ctive                 |  |  |  |  |

|              |                                                                                                                     | dge output: P                      | 1A, P1B are      | modulated wit         | h dead-band           | control; P1C          | and P1D a             |  |  |  |  |

|              |                                                                                                                     | d as port pins                     |                  |                       |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | ge output forwa<br>utput: P1A, P1E |                  |                       |                       | are inactive          | 9                     |  |  |  |  |

| L:L T 4      | -                                                                                                                   | -                                  |                  |                       |                       |                       |                       |  |  |  |  |

| bit 5-4      |                                                                                                                     | PWM Duty Cyc                       |                  |                       | Daule bits            |                       |                       |  |  |  |  |

|              | Unused.                                                                                                             | Compare mode                       | <u>s</u> :       |                       |                       |                       |                       |  |  |  |  |

|              | PWM mode:                                                                                                           |                                    |                  |                       |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | e the two Leas                     | t Significant bi | ts (bit 1 and bit     | 0) of the 10-b        | it PWM duty cy        | cle. The eid          |  |  |  |  |

|              |                                                                                                                     | ant bits (DC1B<                    |                  |                       |                       |                       | , e. e. e. e. g       |  |  |  |  |

| bit 3-0      | -                                                                                                                   | ECCP1 Modu                         | -                |                       |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | mode: P1A an                       |                  |                       | nd P1D are acti       | ve-low                |                       |  |  |  |  |

|              |                                                                                                                     | mode: P1A an                       |                  |                       |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | l mode: P1A an                     |                  |                       |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | I mode: P1A an                     |                  | 0                     |                       | 0                     |                       |  |  |  |  |

|              |                                                                                                                     | pare mode: Spe                     |                  |                       |                       |                       |                       |  |  |  |  |

|              | 1010 = Compare mode: Generates software interrupt on compare match (CCP1IF bit is set, CCP1 pir reflects I/O state) |                                    |                  |                       |                       |                       |                       |  |  |  |  |

|              | 1001 = Compare mode: Initializes CCP1 pin high; on compare match, forces CCP1 pin low (CCP1IF bi                    |                                    |                  |                       |                       |                       |                       |  |  |  |  |

|              | is set                                                                                                              |                                    |                  | <b>J</b> , <b>F F</b> | ,                     | P                     | <b>\</b>              |  |  |  |  |

|              | 1000 = Com<br>bit is                                                                                                | pare mode: Init                    | ializes CCP1 p   | oin low; on com       | pare match, fo        | rces CCP1 pin         | high (CCP1            |  |  |  |  |

|              |                                                                                                                     | ure mode: Ever                     | y 16th rising e  | dge                   |                       |                       |                       |  |  |  |  |

|              | 0110 = Captu                                                                                                        | ure mode: Ever                     | y 4th rising ed  |                       |                       |                       |                       |  |  |  |  |

|              | •                                                                                                                   | ure mode: Ever                     |                  |                       |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | ure mode: Ever                     | y falling edge   |                       |                       |                       |                       |  |  |  |  |

|              | 0011 = Rese                                                                                                         | rved<br>bare mode: Tog             | ales output on   | match (CCD1)          | E bit is cot)         |                       |                       |  |  |  |  |

|              | 0010 = Comp<br>0001 = Rese                                                                                          |                                    | gies output on   |                       |                       |                       |                       |  |  |  |  |

|              |                                                                                                                     | ure/Compare/P                      | WM is disabled   | d (resets CCP1        | module)               |                       |                       |  |  |  |  |

| Note 1:      | This register is im                                                                                                 | plemented only                     | y on PIC24FX)    | (KL40X/30X de         | evices. For all o     | other devices, C      | CCP1CON is            |  |  |  |  |

|              | configured as Reg                                                                                                   |                                    |                  |                       |                       | ,                     |                       |  |  |  |  |

| -            | 000414 -0-0- 1                                                                                                      |                                    |                  |                       |                       |                       |                       |  |  |  |  |

2: CCP1M<3:0> = 1011 will only reset the timer and not start the A/D conversion on a CCP1 match.

## REGISTER 17-7: SSPxCON3: MSSPx CONTROL REGISTER 3 (I<sup>2</sup>C<sup>™</sup> MODE)

| bit 7 Au<br>bit 6 Pi<br>bit 6 Pi<br>bit 5 Si<br>bit 4 Bi<br>$\frac{ 2 }{1}$<br>bit 3 Si<br>bit 2 Si                                                                                                                                                                                                                        | R<br><b>CKTIM:</b> Ack<br>= Indicates<br>= Not an Acc<br><b>CIE:</b> Stop C<br>= Enables in<br>= Stop dete<br><b>CIE:</b> Start C<br>= Enables in<br>= Start dete<br><b>DEN:</b> Buffen<br><u>C Master m</u><br>nis bit is igno                 | cknowledge sec<br>ondition Interru<br>nterrupt on det<br>ction interrupts<br>condition Interru<br>nterrupt on det<br>ection interrupts<br>r Overwrite Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | o'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup>                | '0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition<br>1)<br>tart or Restart o | set on the 8 <sup>th</sup><br>ing edge of the                             | x = Bit is unkr<br>falling edge of f             |                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------|------------------------|

| R-0ACKTIM(2)bit 7Legend:R = Readable bit-n = Value at PObit 15-8Uibit 7Aubit 6PCbit 5SCbit 5SCbit 4Bi $\frac{12}{1}$ bit 3SIbit 3SIbit 2SI                                                                                                                                                                                 | PCIE<br>R<br>R<br>CKTIM: Ack<br>Indicates<br>Not an Ac<br>CIE: Stop C<br>Enables in<br>Stop dete<br>CIE: Start C<br>Enables in<br>Start dete<br>OEN: Buffer<br>CMaster m<br>is bit is igno                                                      | SCIE<br>W = Writable<br>'1' = Bit is set<br>ated: Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru<br>nterrupt on det<br>ection interrupts<br>condition Interru<br>nterrupt on det<br>ection interrupts<br>r Overwrite Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BOEN<br>bit<br>0'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup> | SDAHT<br>U = Unimpler<br>'0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition   | SBCDE<br>nented bit, read<br>ared<br>set on the 8 <sup>th</sup>           | AHEN<br>d as '0'<br>x = Bit is unki              | R/W-0<br>DHEN<br>bit ( |

| ACKTIM(2)bit 7Legend:<br>R = Readable bit<br>-n = Value at PObit 15-8Ui<br>bit 7bit 5Si<br>0bit 6Pi<br>0bit 5Si<br>0bit 4 $\frac{12}{1}$<br>0bit 3Si<br>0bit 3Si<br>0bit 2Si<br>                                                                                                                                           | PCIE<br>R<br>R<br>CKTIM: Ack<br>Indicates<br>Not an Ac<br>CIE: Stop C<br>Enables in<br>Stop dete<br>CIE: Start C<br>Enables in<br>Start dete<br>OEN: Buffer<br>CMaster m<br>is bit is igno                                                      | SCIE<br>W = Writable<br>'1' = Bit is set<br>ated: Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru<br>nterrupt on det<br>ection interrupts<br>condition Interru<br>nterrupt on det<br>ection interrupts<br>r Overwrite Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BOEN<br>bit<br>0'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup> | SDAHT<br>U = Unimpler<br>'0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition   | SBCDE<br>nented bit, read<br>ared<br>set on the 8 <sup>th</sup>           | AHEN<br>d as '0'<br>x = Bit is unki              | DHEN<br>bit (          |

| ACKTIM(2)bit 7Legend:<br>R = Readable bit<br>-n = Value at PObit 15-8Ui<br>bit 7bit 5Si<br>0bit 6Pi<br>0bit 5Si<br>0bit 4 $\frac{12}{1}$<br>0bit 3Si<br>0bit 3Si<br>0bit 2Si<br>                                                                                                                                           | PCIE<br>R<br>R<br>CKTIM: Ack<br>Indicates<br>Not an Ac<br>CIE: Stop C<br>Enables in<br>Stop dete<br>CIE: Start C<br>Enables in<br>Start dete<br>OEN: Buffer<br>CMaster m<br>is bit is igno                                                      | SCIE<br>W = Writable<br>'1' = Bit is set<br>ated: Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge sec<br>ondition Interru<br>nterrupt on det<br>ection interrupts<br>condition Interru<br>nterrupt on det<br>ection interrupts<br>r Overwrite Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BOEN<br>bit<br>0'<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1)</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1)</sup> | SDAHT<br>U = Unimpler<br>'0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition   | SBCDE<br>nented bit, read<br>ared<br>set on the 8 <sup>th</sup>           | AHEN<br>d as '0'<br>x = Bit is unki              | DHEN<br>bit (          |

| bit 7<br>Legend:<br>R = Readable bit<br>-n = Value at PO<br>bit 15-8 Ui<br>bit 7 A(<br>bit 6 P(<br>1<br>0<br>bit 5 S(<br>1<br>0<br>bit 5 S(<br>1<br>0<br>bit 4 B(<br>1<br>0<br>bit 3 S(<br>0<br>bit 3 S(<br>0<br>bit 2 S(<br>1<br>0<br>0<br>bit 2 S(<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | R<br><b>CKTIM:</b> Ack<br>Indicates<br>Not an Act<br>Indicates<br>Not an Act<br><b>CIE</b> : Stop C<br>Enables in<br>Stop dete<br><b>CIE</b> : Start C<br>Enables in<br>Start dete<br><b>DEN:</b> Buffer<br><u>C Master m</u><br>is bit is igno | W = Writable<br>'1' = Bit is set<br><b>ited:</b> Read as '<br>knowledge Tim-<br>the I <sup>2</sup> C bus is i<br>cknowledge set<br>ondition Interru-<br>nterrupt on det-<br>ction interrupts<br>condition Interru-<br>nterrupt on det-<br>ction interrupts<br>r Overwrite Ena-<br>tode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit<br>e Status bit <sup>(2)</sup><br>n an Acknowle<br>quence, cleare<br>upt Enable bit<br>ection of a Sto<br>are disabled <sup>(1</sup><br>upt Enable bit<br>ection of the S<br>are disabled <sup>(1</sup>                 | U = Unimpler<br>'0' = Bit is cle<br>edge sequence,<br>d on the 9 <sup>th</sup> risi<br>p condition            | nented bit, read<br>ared<br>set on the 8 <sup>th</sup><br>ing edge of the | d as '0'<br>x = Bit is unkr<br>falling edge of f | nown                   |