Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 4KB (1.375K x 24)                                                            |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                |                                                                              |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            |                                                                              |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | 14-TSSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04kl100-e-st |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                  | Pin N         | umber                             |               |     |                  |                                           |  |

|----------|----------------------------------|---------------|-----------------------------------|---------------|-----|------------------|-------------------------------------------|--|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | I/O | Buffer           | Description                               |  |

| PGEC1    | 5                                | 2             | 5                                 | 2             | I/O | ST               | ICSP™ Clock 1                             |  |

| PCED1    | 4                                | 1             | 4                                 | 1             | I/O | ST               | ICSP Data 1                               |  |

| PGEC2    | 2                                | 19            | 22                                | 19            | I/O | ST               | ICSP Clock 2                              |  |

| PGED2    | 3                                | 20            | 21                                | 18            | I/O | ST               | ICSP Data 2                               |  |

| PGEC3    | 10                               | 7             | 15                                | 12            | I/O | ST               | ICSP Clock 3                              |  |

| PGED3    | 9                                | 6             | 14                                | 11            | I/O | ST               | ICSP Data 3                               |  |

| RA0      | 2                                | 19            | 2                                 | 27            | I/O | ST               | PORTA Pins                                |  |

| RA1      | 3                                | 20            | 3                                 | 28            | I/O | ST               |                                           |  |

| RA2      | 7                                | 4             | 9                                 | 6             | I/O | ST               |                                           |  |

| RA3      | 8                                | 5             | 10                                | 7             | I/O | ST               |                                           |  |

| RA4      | 10                               | 7             | 12                                | 9             | I/O | ST               |                                           |  |

| RA5      | 1                                | 18            | 1                                 | 26            | I   | ST               |                                           |  |

| RA6      | 14                               | 11            | 20                                | 17            | I/O | ST               |                                           |  |

| RA7      | _                                | _             | 19                                | 16            | I/O | ST               |                                           |  |

| RB0      | 4                                | 1             | 4                                 | 1             | I/O | ST               | PORTB Pins                                |  |

| RB1      | 5                                | 2             | 5                                 | 2             | I/O | ST               |                                           |  |

| RB2      | 6                                | 3             | 6                                 | 3             | I/O | ST               |                                           |  |

| RB3      |                                  |               | 7                                 | 4             | I/O | ST               |                                           |  |

| RB4      | 9                                | 6             | 11                                | 8             | I/O | ST               |                                           |  |

| RB5      | _                                | _             | 14                                | 11            | I/O | ST               |                                           |  |

| RB6      | _                                | _             | 15                                | 12            | I/O | ST               |                                           |  |

| RB7      | 11                               | 8             | 16                                | 13            | I/O | ST               |                                           |  |

| RB8      | 12                               | 9             | 17                                | 14            | I/O | ST               |                                           |  |

| RB9      | 13                               | 10            | 18                                | 15            | I/O | ST               |                                           |  |

| RB10     | _                                | _             | 21                                | 18            | I/O | ST               |                                           |  |

| RB11     | _                                | _             | 22                                | 19            | I/O | ST               |                                           |  |

| RB12     | 15                               | 12            | 23                                | 20            | I/O | ST               |                                           |  |

| RB13     | 16                               | 13            | 24                                | 21            | I/O | ST               |                                           |  |

| RB14     | 17                               | 14            | 25                                | 22            | I/O | ST               |                                           |  |

| RB15     | 18                               | 15            | 26                                | 23            | I/O | ST               | ]                                         |  |

| REFO     | 18                               | 15            | 26                                | 23            | 0   |                  | Reference Clock Output                    |  |

| SCK1     | 15                               | 12            | 22                                | 19            | I/O | ST               | MSSP1 SPI Serial Input/Output Clock       |  |

| SCK2     | 18                               | 15            | 14                                | 11            | I/O | ST               | MSSP2 SPI Serial Input/Output Clock       |  |

| SCL1     | 12                               | 9             | 17                                | 14            | I/O | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Clock Input/Output |  |

| SCL2     | 18                               | 15            | 7                                 | 4             | I/O | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C Clock Input/Output |  |

| SCLKI    | 10                               | 7             | 12                                | 9             | Ι   | ST               | Digital Secondary Clock Input             |  |

| SDA1     | 13                               | 10            | 18                                | 15            | I/O | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Data Input/Output  |  |

| SDA2     | 2                                | 19            | 2                                 | 27            | I/O | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C Data Input/Output  |  |

| SDI1     | 17                               | 14            | 21                                | 18            | Ι   | ST               | MSSP1 SPI Serial Data Input               |  |

| SDI2     | 2                                | 19            | 19                                | 16            | I   | ST               | MSSP2 SPI Serial Data Input               |  |

| SDO1     | 16                               | 13            | 24                                | 21            | 0   |                  | MSSP1 SPI Serial Data Output              |  |

| SDO2     | 3                                | 20            | 15                                | 12            | 0   | —                | MSSP2 SPI Serial Data Output              |  |

|          | TL = TTL ii                      |               |                                   |               |     |                  | nitt Trigger input buffer                 |  |

#### **TABLE 1-4:** PIC24F16KL40X/30X FAMILY PINOUT DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

# 5.0 FLASH PROGRAM MEMORY

| Note: | This data sheet summarizes the features of this group of PIC24F devices. It is not |

|-------|------------------------------------------------------------------------------------|

|       | intended to be a comprehensive reference                                           |

|       | source. For more information on Flash                                              |

|       | Programming, refer to the "dsPIC33/PIC24                                           |

|       | Family Reference Manual", "Program                                                 |

|       | Memory" (DS39715).                                                                 |

The PIC24F16KL402 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24F device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program mode Entry voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed. Run-Time Self Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

# 5.1 Table Instructions and Flash Programming

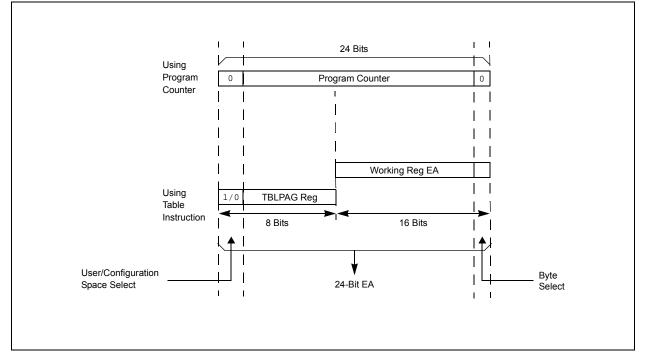

Regardless of the method used, Flash memory programming is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

# 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing it is not recommended.

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. For more information, refer to **Section 5.5 "Programming Operations"**.

# 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM_INSTRUCTION_PER_ROW 64

int __attribute__ ((space(auto_psv))) progAddr = &progAddr; // Global variable located in Pgm Memory

unsigned int offset;

unsigned int i;

// Buffer of data to write

unsigned int progData[2*NUM_INSTRUCTION_PER_ROW];

//Set up NVMCON for row programming

NVMCON = 0 \times 4004;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = &progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM_INSTRUCTION_PER_ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2i

// Increment address

}

```

#### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts                  |

|------|-------------|---|---------------------------------------|

|      |             |   | for next 5 instructions               |

| MOV  | #0x55, W0   |   |                                       |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                      |

| MOV  | #0xAA, W1   | ; |                                       |

| MOV  | W1, NVMKEY  | ; | Write the AA key                      |

| BSET | NVMCON, #WR | ; | Start the erase sequence              |

| NOP  |             | ; | 2 NOPs required after setting WR      |

| NOP  |             | ; |                                       |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed |

| BRA  | \$-2        | ; |                                       |

|      |             |   |                                       |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

#### REGISTER 8-13: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0   | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-------|-----|-----|-----|-----|-------|

|        | —   | _     | _   |     | _   | _   | _     |

| bit 15 | •   |       |     |     |     |     | bit 8 |

|        |     |       |     |     |     |     |       |

| U-0    | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| —      | —   | T3GIE | —   | —   | —   | —   | —     |

| bit 7  |     |       |     |     |     |     | bit 0 |

| DIT | 1 |

|-----|---|

|     |   |

bit 1

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-6 | Unimplemented: Read as '0'                       |

|----------|--------------------------------------------------|

| bit 5    | T3GIF: Timer3 External Gate Interrupt Enable bit |

|          | 1 = Interrupt request is enabled                 |

|          | 0 = Interrupt request is not enabled             |

|          |                                                  |

Unimplemented: Read as '0' bit 4-0

#### **REGISTER 8-14: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                 | U-0   |

|-------|-----|-----|-----|-----|-----------------------|-----------------------|-------|

| _     | —   | —   | —   | —   | BCL2IE <sup>(1)</sup> | SSP2IE <sup>(1)</sup> | —     |

| bit 7 |     |     |     |     |                       |                       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

BCL2IE: MSSP2 I<sup>2</sup>C<sup>™</sup> Bus Collision Interrupt Enable bit<sup>(1)</sup> bit 2

- 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

- SSP2IF: MSSP2 SPI/I<sup>2</sup>C Event Interrupt Enable bit<sup>(1)</sup>

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 Unimplemented: Read as '0'

- Note 1: These bits are unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0                               | U-0                              | U-0                                      | U-0             | U-0                                 | U-0                   | U-0    | R/W-0  |  |

|-----------------------------------|----------------------------------|------------------------------------------|-----------------|-------------------------------------|-----------------------|--------|--------|--|

| _                                 | —                                | —                                        | —               | —                                   | —                     | —      | HLVDIE |  |

| bit 15                            |                                  |                                          |                 |                                     |                       |        | bit 8  |  |

|                                   |                                  |                                          |                 |                                     |                       |        |        |  |

| U-0                               | U-0                              | U-0                                      | U-0             | U-0                                 | R/W-0                 | R/W-0  | U-0    |  |

|                                   |                                  | <u> </u>                                 |                 | —                                   | U2ERIE <sup>(1)</sup> | U1ERIE |        |  |

| bit 7                             |                                  |                                          |                 |                                     |                       |        | bit 0  |  |

|                                   |                                  |                                          |                 |                                     |                       |        |        |  |

| Legend:                           |                                  |                                          |                 |                                     |                       |        |        |  |

| R = Readable bit W = Writable bit |                                  |                                          |                 | U = Unimplemented bit, read as '0'  |                       |        |        |  |

| -n = Value a                      | at POR                           | '1' = Bit is set                         | t               | '0' = Bit is cleared x = Bit is unk |                       |        | nown   |  |

|                                   |                                  |                                          |                 |                                     |                       |        |        |  |

| bit 15-9                          | Unimplemer                       | nted: Read as '                          | 0'              |                                     |                       |        |        |  |

| bit 8                             | HLVDIE: Hig                      | h/Low-Voltage                            | Detect Interrup | ot Enable bit                       |                       |        |        |  |

|                                   |                                  | request is enat                          |                 |                                     |                       |        |        |  |

|                                   | •                                | request is not e                         |                 |                                     |                       |        |        |  |

| bit 7-3                           | Unimplemer                       | nted: Read as '                          | 0'              |                                     |                       |        |        |  |

| bit 2                             | U2ERIE: UA                       | RT2 Error Inter                          | rupt Enable bit | (1)                                 |                       |        |        |  |

|                                   | 1 = Interrupt request is enabled |                                          |                 |                                     |                       |        |        |  |

|                                   | •                                | 0 = Interrupt request is not enabled     |                 |                                     |                       |        |        |  |

| bit 1                             |                                  | U1ERIE: UART1 Error Interrupt Enable bit |                 |                                     |                       |        |        |  |

|                                   |                                  | request is enab<br>request is not e      |                 |                                     |                       |        |        |  |

| bit 0                             |                                  | nted: Read as '                          |                 |                                     |                       |        |        |  |

|                                   |                                  |                                          |                 |                                     |                       |        |        |  |

Note 1: This bit is unimplemented on PIC24FXXKL10X and PIC24FXXKL20X devices.

#### REGISTER 8-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0                     | U-0       | U-0              | U-0 | U-0                  | U-0              | U-0                | U-0     |

|-------------------------|-----------|------------------|-----|----------------------|------------------|--------------------|---------|

| _                       | —         | —                | _   | —                    | —                | —                  | —       |

| bit 15                  |           |                  |     | -                    |                  |                    | bit 8   |

|                         |           |                  |     |                      |                  |                    |         |

| U-0                     | U-0       | U-0              | U-0 | U-0                  | U-0              | U-0                | R/W-0   |

| —                       | —         | —                | —   | —                    | —                | —                  | ULPWUIE |

| bit 7                   |           |                  |     |                      |                  |                    | bit 0   |

|                         |           |                  |     |                      |                  |                    |         |

| Legend:                 |           |                  |     |                      |                  |                    |         |

| R = Readable            | e bit     | W = Writable     | bit | U = Unimplem         | nented bit, read | l as '0'           |         |

| -n = Value at POR '1' = |           | '1' = Bit is set |     | '0' = Bit is cleared |                  | x = Bit is unknown |         |

| <u>.</u>                |           |                  |     |                      |                  |                    |         |

| bit 15-1                | Unimpleme | nted: Read as '  | o'  |                      |                  |                    |         |

| L:1 0                   |           |                  | A   |                      |                  |                    |         |

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable Bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### REGISTER 8-25: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0          | U-0                        | U-0                 | U-0              | U-0                                     | U-0              | U-0      | U-0   |

|--------------|----------------------------|---------------------|------------------|-----------------------------------------|------------------|----------|-------|

| —            | _                          | —                   | —                | —                                       | —                | —        | —     |

| bit 15       |                            |                     |                  |                                         |                  |          | bit 8 |

|              |                            |                     |                  |                                         |                  |          |       |

| U-0          | R/W-1                      | R/W-0               | R/W-0            | U-0                                     | U-0              | U-0      | U-0   |

| _            | T3GIP2                     | T3GIP1              | T3GIP0           | —                                       | —                | —        | —     |

| bit 7        |                            |                     |                  |                                         |                  |          | bit 0 |

|              |                            |                     |                  |                                         |                  |          |       |

| Legend:      |                            |                     |                  |                                         |                  |          |       |

| R = Readab   | le bit                     | W = Writable        | bit              | U = Unimplem                            | nented bit, read | l as '0' |       |

| -n = Value a | t POR                      | '1' = Bit is set    |                  | '0' = Bit is cleared x = Bit is unknown |                  |          |       |

|              |                            |                     |                  |                                         |                  |          |       |

| bit 15-7     | Unimplemented: Read as '0' |                     |                  |                                         |                  |          |       |

| bit 6-4      | T3GIP<2:0>:                | Timer3 Externa      | al Gate Interru  | pt Priority bits                        |                  |          |       |

|              | 111 = Interru              | pt is Priority 7 (l | highest priority | / interrupt)                            |                  |          |       |

|              | •                          |                     |                  |                                         |                  |          |       |

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

#### 10.3 Ultra Low-Power Wake-up

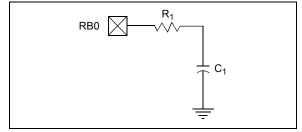

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption. This feature provides a low-power technique for periodically waking up the device from Sleep mode.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0. When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

A series resistor, between RB0 and the external capacitor, provides overcurrent protection for the RB0/AN2/ULPWU pin and enables software calibration of the time-out (see Figure 10-1).

#### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

#### EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

| / / * * * * * * * * * * * * * * * * * *                                     |

|-----------------------------------------------------------------------------|

| // 1. Charge the capacitor on RB0                                           |

| / / * * * * * * * * * * * * * * * * * *                                     |

| TRISBbits.TRISB0 = 0;                                                       |

| LATBbits.LATB0 = 1;                                                         |

| for(i = 0; i < 10000; i++) Nop();                                           |

| / / * * * * * * * * * * * * * * * * * *                                     |

| //2. Stop Charging the capacitor on RB0                                     |

| / / * * * * * * * * * * * * * * * * * *                                     |

| TRISBbits.TRISB0 = 1;                                                       |

| / / * * * * * * * * * * * * * * * * * *                                     |

| //3. Enable ULPWU Interrupt                                                 |

| //*************************************                                     |

| IFS5bits.ULPWUIF = 0;                                                       |

| IEC5bits.ULPWUIE = 1;                                                       |

| IPC20bits.ULPWUIP = 0x7;                                                    |

| / / * * * * * * * * * * * * * * * * * *                                     |

| //4. Enable the Ultra Low Power Wakeup module and allow capacitor discharge |

| / / * * * * * * * * * * * * * * * * * *                                     |

| ULPWCONbits.ULPEN = 1;                                                      |

| ULPWCONbits.ULPSINK = 1;                                                    |

| //*************************************                                     |

| //5. Enter Sleep Mode                                                       |

| //*************************************                                     |

| Sleep();                                                                    |

| //for Sleep, execution will resume here                                     |

|                                                                             |

# 15.0 TIMER4 MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704).

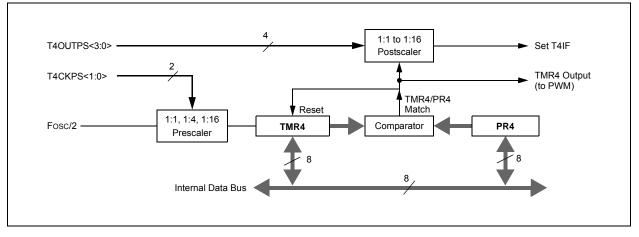

The Timer4 module is implemented in PIC24FXXKL30X/40X devices only. It has the following features:

- Eight-bit Timer register (TMR4)

- Eight-bit Period register (PR4)

- Readable and writable (all registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR4 match of PR4

The Timer4 module has a control register shown in Register 15-1. Timer4 can be shut off by clearing control bit, TMR4ON (T4CON<2>), to minimize power consumption. The prescaler and postscaler selection of Timer4 is controlled by this register.

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMR4 register

- · A write to the T4CON register

- Any device Reset (POR, BOR, MCLR or WDT Reset)

TMR4 is not cleared when T4CON is written.

Figure 15-1 is a simplified block diagram of the Timer4 module.

#### FIGURE 15-1: TIMER4 BLOCK DIAGRAM

| U-0       | U-0                            | U-0                     | U-0            | U-0                                     | U-0    | U-0      | U-0     |  |

|-----------|--------------------------------|-------------------------|----------------|-----------------------------------------|--------|----------|---------|--|

| _         |                                | <u> </u>                | —              | <u> </u>                                | —      | <u> </u> |         |  |

| pit 15    |                                |                         |                |                                         |        |          | bit 8   |  |

|           |                                |                         |                |                                         |        |          |         |  |

| U-0       | R/W-0                          | R/W-0                   | R/W-0          | R/W-0                                   | R/W-0  | R/W-0    | R/W-0   |  |

|           | T4OUTPS3                       | T4OUTPS2                | T4OUTPS1       | T4OUTPS0                                | TMR4ON | T4CKPS1  | T4CKPS0 |  |

| oit 7     |                                |                         |                |                                         |        |          | bit C   |  |

|           |                                |                         |                |                                         |        |          |         |  |

| egend:    |                                |                         |                |                                         |        |          |         |  |

| R = Reada |                                | W = Writable            | bit            | U = Unimplem                            |        |          |         |  |

| n = Value | at POR                         | '1' = Bit is set        |                | '0' = Bit is cleared x = Bit is unknown |        |          |         |  |

| oit 15-7  |                                | ted. Deed oo W          | <b>,</b>       |                                         |        |          |         |  |

|           | -                              | ted: Read as '          |                | <b>_</b>                                |        |          |         |  |

| oit 6-3   |                                | <b>0&gt;:</b> Timer4 Ou | tput Postscale | Select bits                             |        |          |         |  |

|           | 1111 = 1:16  <br>1110 = 1:15   |                         |                |                                         |        |          |         |  |

|           | •                              | OSISCAIE                |                |                                         |        |          |         |  |

|           | •                              |                         |                |                                         |        |          |         |  |

|           | •                              |                         |                |                                         |        |          |         |  |

|           | 0001 = 1:2 P<br>0000 = 1:1 P   |                         |                |                                         |        |          |         |  |

| oit 2     | TMR4ON: Tir                    | ner4 On bit             |                |                                         |        |          |         |  |

|           | 1 = Timer4 is<br>0 = Timer4 is |                         |                |                                         |        |          |         |  |

| oit 1-0   | T4CKPS<1:0                     | >: Timer4 Cloc          | k Prescale Sel | ect bits                                |        |          |         |  |

|           | 10 = Prescale                  | er is 16                |                |                                         |        |          |         |  |

|           |                                |                         |                |                                         |        |          |         |  |

|           | 01 = Prescale                  | -                       |                |                                         |        |          |         |  |

# REGISTER 15-1: T4CON: TIMER4 CONTROL REGISTER

# 17.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP)

| Note: | This data sheet summarizes the features    |

|-------|--------------------------------------------|

|       | of this group of PIC24F devices. It is not |

|       | intended to be a comprehensive refer-      |

|       | ence source. For more information on       |

|       | MSSP, refer to the "dsPIC33/PIC24          |

|       | Family Reference Manual".                  |

The Master Synchronous Serial Port (MSSP) module is an 8-bit serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, Shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The SPI interface supports these modes in hardware:

- Master mode

- Slave mode

- · Daisy-Chaining Operation in Slave mode

- Synchronized Slave operation

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode with 10-Bit And 7-Bit Addressing and Address Masking

- Byte NACKing

- Selectable Address and Data Hold and Interrupt Masking

# 17.1 I/O Pin Configuration for SPI

In SPI Master mode, the MSSP module will assert control over any pins associated with the SDOx and SCKx outputs. This does not automatically disable other digital functions associated with the pin, and may result in the module driving the digital I/O port inputs. To prevent this, the MSSP module outputs must be disconnected from their output pins while the module is in SPI Master mode. While disabling the module temporarily may be an option, it may not be a practical solution in all applications.

The SDOx and SCKx outputs for the module can be selectively disabled by using the SDOxDIS and SCKxDIS bits in the PADCFG1 register (Register 17-10). Setting the bit disconnects the corresponding output for a particular module from its assigned pin.

| R/W-0                      | R-0                                                                                            | R/W-0                                                                                                                       | R/W-0                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|----------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|------------------|-----------------|-------|

| ADRC                       | EXTSAM                                                                                         | PUMPEN                                                                                                                      | SAMC4                                 | SAMC3             | SAMC2            | SAMC1           | SAMC0 |

| bit 15                     | ·                                                                                              | •                                                                                                                           |                                       | -                 |                  |                 | bit 8 |

| U-0                        | U-0                                                                                            | R/W-0                                                                                                                       | R/W-0                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                            |                                                                                                | ADCS5                                                                                                                       | ADCS4                                 | ADCS3             | ADCS2            | ADCS1           | ADCS0 |

| bit 7                      |                                                                                                |                                                                                                                             |                                       |                   |                  |                 | bit ( |

| Legend:                    |                                                                                                |                                                                                                                             |                                       |                   |                  |                 |       |

| R = Readab                 | ole bit                                                                                        | W = Writable                                                                                                                | bit                                   | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value a               | at POR                                                                                         | '1' = Bit is set                                                                                                            |                                       | '0' = Bit is clea | ared             | x = Bit is unkr | iown  |

| bit 15<br>bit 14<br>bit 13 | 1 = A/D inten<br>0 = Clock der<br><b>EXTSAM:</b> Ext<br>1 = A/D is stil<br>0 = A/D is fin      | onversion Cloc<br>nal RC clock<br>rived from syste<br>tended Samplin<br>Il sampling afte<br>ished sampling<br>parge Pump En | em clock<br>ng Time bit<br>r SAMP = 0 |                   |                  |                 |       |

|                            | 1 = Charge p                                                                                   | ump for switch                                                                                                              | es is enabled                         |                   |                  |                 |       |

| bit 12-8                   | SAMC<4:0>:<br>11111 = 31 T<br>•<br>•<br>•<br>00001 = 1 TA                                      | Auto-Sample T<br>AD                                                                                                         | īme bits                              |                   |                  |                 |       |

| bit 7-6                    | Unimplemen                                                                                     | ted: Maintain a                                                                                                             | <b>s</b> '0'                          |                   |                  |                 |       |

| bit 5-0                    | ADCS<5:0>:<br>11111 = 64 •<br>11110 = 63 •<br>•<br>•<br>•<br>•<br>00001 = 2 • T<br>00000 = Tcy | Тсү                                                                                                                         | n Clock Select                        | bits              |                  |                 |       |

### REGISTER 19-3: AD1CON3: A/D CONTROL REGISTER 3

| R/P-1               | R/P-1                                 | R/P-1                | R/P-1                                 | R/P-1             | U-0              | R/P-1             | R/P-1                      |

|---------------------|---------------------------------------|----------------------|---------------------------------------|-------------------|------------------|-------------------|----------------------------|

| MCLRE <sup>(1</sup> | ) BORV1 <sup>(2)</sup>                | BORV0 <sup>(2)</sup> | I2C1SEL <sup>(3)</sup>                | PWRTEN            |                  | BOREN1            | BOREN0                     |

| bit 7               |                                       |                      |                                       |                   |                  |                   | bit C                      |

| Logondi             |                                       |                      |                                       |                   |                  |                   |                            |

| Legend:             |                                       |                      |                                       |                   |                  | 1                 |                            |

| R = Reada           |                                       | P = Program          |                                       | •                 | nented bit, read |                   |                            |

| -n = Value          | at POR                                | '1' = Bit is set     |                                       | '0' = Bit is clea | ared             | x = Bit is unkr   | nown                       |

| bit 7               |                                       | R Pin Enable         | hit(1)                                |                   |                  |                   |                            |

|                     |                                       |                      | A5 input pin is o                     | lisabled          |                  |                   |                            |

|                     |                                       |                      | ; MCLR is disa                        |                   |                  |                   |                            |

| bit 6-5             | BORV<1:0>:                            | Brown-out Res        | set Enable bits <sup>(</sup>          | 2)                |                  |                   |                            |

|                     | 11 = Brown-o                          | ut Reset is set      | to the low trip p                     | point             |                  |                   |                            |

|                     |                                       |                      | to the middle to                      |                   |                  |                   |                            |

|                     |                                       |                      | to the high trip<br>POR is enable ו   |                   |                  | ad)               |                            |

| bit 4               |                                       | -                    | I <sup>2</sup> C <sup>™</sup> Pin Map | -                 | DON 13 SEIECI    | eu)               |                            |

|                     |                                       |                      | 1/SDA1 pins (R                        | U U               |                  |                   |                            |

|                     |                                       |                      | L1/SDA1 pins (                        | ,                 | nd ASDA1/RB      | 5)                |                            |

| bit 3               |                                       | wer-up Timer         |                                       |                   |                  |                   |                            |

|                     | 1 = PWRT is                           | enabled              |                                       |                   |                  |                   |                            |

|                     | 0 = PWRT is                           | disabled             |                                       |                   |                  |                   |                            |

| bit 2               | Unimplemen                            | ted: Read as '       | 0'                                    |                   |                  |                   |                            |

| bit 1-0             | BOREN<1:0>                            | Brown-out R          | eset Enable bit                       | S                 |                  |                   |                            |

|                     |                                       |                      | dware; SBOREI                         |                   |                  |                   |                            |

|                     |                                       |                      | hile device is a                      |                   | oled in Sleep; S | BOREN bit is o    | disabled                   |

|                     |                                       |                      | the SBOREN b<br>dware; SBORE          | •                 | Ч                |                   |                            |

|                     |                                       |                      | ·                                     |                   |                  |                   |                            |

|                     | The MCLRE fuse                        |                      |                                       |                   |                  | node entry. This  | s prevents a               |

|                     | user from accider                     |                      |                                       |                   | age test entry.  |                   |                            |

|                     | Refer to Table 26-                    |                      |                                       |                   | rogrommod (-     | 1) in all other a | $lowiooo for l^2$          |

|                     | Implemented in 28 functionality to be |                      | nny. This dit pos                     | muon must de p    | rogrammed (=     | ⊥) in all other c | ievices for I <sup>2</sup> |

#### **REGISTER 23-6: FPOR: RESET CONFIGURATION REGISTER**

#### 23.3 Unique ID

A read-only Unique ID value is stored at addresses, 800802h through 800808h. This factory programmed value is unique to each microcontroller produced in the PIC24F16KL402 family. To access this region, use Table Read instructions or Program Space Visibility. To ensure a globally Unique ID across other Microchip microcontroller families, the "Unique ID" value should be further concatenated with the family and Device ID values stored at address, FF0000h.

### REGISTER 23-8: DEVID: DEVICE ID REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   |     | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R      | R      | R      | R      | R      | R      | R      | R      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 | FAMID1 | FAMID0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV7  | DEV6 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-8 **FAMID<7:0>:** Device Family Identifier bits 01001011 = PIC24F16KL402 family

bit 7-0 **DEV<7:0>:** Individual Device Identifier bits 00000001 = PIC24F04KL100

00000010 = PIC24F04KL101

00000101 = PIC24F08KL200 00000110 = PIC24F08KL201

00001010 = PIC24F08KL301 00000000 = PIC24F08KL302

00001110 = PIC24F08KL401 00000100 = PIC24F08KL402 00011110 = PIC24F16KL401 00010100 = PIC24F16KL402

### 24.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 24.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| Assembly<br>Mnemonic |        | Assembly Syntax  | Description                                                                | # of<br>Words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | # of<br>Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Status Flags<br>Affected |

|----------------------|--------|------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| GOTO                 | GOTO   | Expr             | Go to Address                                                              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | None                     |

|                      | GOTO   | Wn               | Go to Indirect                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | None                     |

| INC                  | INC    | f                | f = f + 1                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C, DC, N, OV, Z          |

|                      | INC    | f,WREG           | WREG = f + 1                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C, DC, N, OV, Z          |

|                      | INC    | Ws,Wd            | Wd = Ws + 1                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C, DC, N, OV, Z          |

| INC2                 | INC2   | f                | f = f + 2                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C, DC, N, OV, Z          |

|                      | INC2   | f,WREG           | WREG = f + 2                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C, DC, N, OV, Z          |