#### Microchip Technology - PIC24F04KL100-I/P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 4KB (1.375K x 24)                                                           |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 14-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04kl100-i-p |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                  | Pin Number    | •                        |     |        |                                                                               |  |  |

|----------|----------------------------------|---------------|--------------------------|-----|--------|-------------------------------------------------------------------------------|--|--|

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 20-Pin<br>QFN | 14-Pin<br>PDIP/<br>TSSOP | I/O | Buffer | Description                                                                   |  |  |

| CVREF    | 17                               | 14            | 11                       | Ι   | ANA    | Comparator Voltage Reference Output                                           |  |  |

| CVREF+   | 2                                | 19            | 2                        | I   | ANA    | Comparator Reference Positive Input Voltage                                   |  |  |

| CVREF-   | 3                                | 20            | 3                        | I   | ANA    | Comparator Reference Negative Input Voltage                                   |  |  |

| HLVDIN   | 15                               | 12            | 6                        | I   | ST     | High/Low-Voltage Detect Input                                                 |  |  |

| INT0     | 11                               | 8             | 12                       | I   | ST     | Interrupt 0 Input                                                             |  |  |

| INT1     | 17                               | 14            | 11                       | I   | ST     | Interrupt 1 Input                                                             |  |  |

| INT2     | 14                               | 11            | 10                       | I   | ST     | Interrupt 2 Input                                                             |  |  |

| MCLR     | 1                                | 18            | 1                        | I   | ST     | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |  |  |

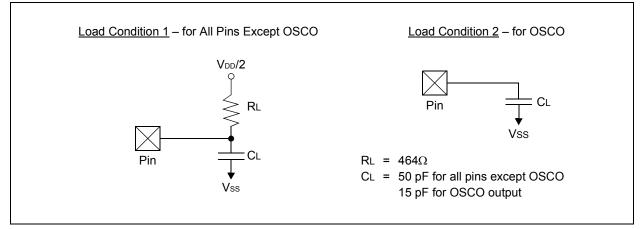

| OSCI     | 7                                | 4             | 4                        | I   | ANA    | Main Oscillator Input                                                         |  |  |

| OSCO     | 8                                | 5             | 5                        | 0   | ANA    | Main Oscillator Output                                                        |  |  |

| PGEC1    | 5                                | 2             | _                        | I/O | ST     | ICSP™ Clock 1                                                                 |  |  |

| PCED1    | 4                                | 1             | _                        | I/O | ST     | ICSP Data 1                                                                   |  |  |

| PGEC2    | 2                                | 19            | 2                        | I/O | ST     | ICSP Clock 2                                                                  |  |  |

| PGED2    | 3                                | 20            | 3                        | I/O | ST     | ICSP Data 2                                                                   |  |  |

| PGEC3    | 10                               | 7             | 7                        | I/O | ST     | ICSP Clock 3                                                                  |  |  |

| PGED3    | 9                                | 6             | 6                        | I/O | ST     | ICSP Data 3                                                                   |  |  |

| RA0      | 2                                | 19            | 2                        | I/O | ST     | PORTA Pins                                                                    |  |  |

| RA1      | 3                                | 20            | 3                        | I/O | ST     | 7                                                                             |  |  |

| RA2      | 7                                | 4             | 4                        | I/O | ST     | 7                                                                             |  |  |

| RA3      | 8                                | 5             | 5                        | I/O | ST     |                                                                               |  |  |

| RA4      | 10                               | 7             | 7                        | I/O | ST     | 7                                                                             |  |  |

| RA5      | 1                                | 18            | 1                        | I   | ST     | 7                                                                             |  |  |

| RA6      | 14                               | 11            | 10                       | I/O | ST     | 7                                                                             |  |  |

| RB0      | 4                                | 1             |                          | I/O | ST     | PORTB Pins                                                                    |  |  |

| RB1      | 5                                | 2             |                          | I/O | ST     |                                                                               |  |  |

| RB2      | 6                                | 3             |                          | I/O | ST     |                                                                               |  |  |

| RB4      | 9                                | 6             | 6                        | I/O | ST     |                                                                               |  |  |

| RB7      | 11                               | 8             | —                        | I/O | ST     |                                                                               |  |  |

| RB8      | 12                               | 9             | 8                        | I/O | ST     | 1                                                                             |  |  |

| RB9      | 13                               | 10            | 9                        | I/O | ST     |                                                                               |  |  |

| RB12     | 15                               | 12            | _                        | I/O | ST     |                                                                               |  |  |

| RB13     | 16                               | 13            | —                        | I/O | ST     | 1                                                                             |  |  |

| RB14     | 17                               | 14            | 11                       | I/O | ST     | 1                                                                             |  |  |

| RB15     | 18                               | 15            | 12                       | I/O | ST     | 1                                                                             |  |  |

| REFO     | 18                               | 15            | 12                       | 0   | —      | Reference Clock Output                                                        |  |  |

#### PIC24F16KL20X/10X FAMILY PINOUT DESCRIPTIONS (CONTINUED) **TABLE 1-5:**

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C^{TM}/SMBus$  input buffer

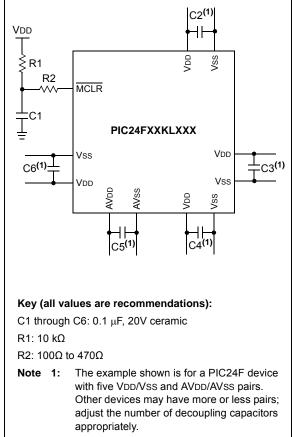

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

#### 2.1 Basic Connection Requirements

Getting started with the PIC24F16KL402 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.4 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.5 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

Note: The AVDD and AVSS pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

| TABLE 3-1: 0 | CPU CORE REGISTERS |

|--------------|--------------------|

|--------------|--------------------|

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | REPEAT Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

#### 6.0 DATA EEPROM MEMORY

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information on Data       |

|       | EEPROM, refer to the "dsPIC33/PIC24        |

|       | Family Reference Manual", "Data            |

|       | EEPROM" (DS39720).                         |

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFFFh. For PIC24FXXKL4XX devices, the size of the data EEPROM is 256 words (7FFE00h to 7FFFFh). For PIC24FXXKL3XX devices, the size of the data EEPROM is 128 words (7FFF0h to 7FFFFh). The data EEPROM is not implemented in PIC24F08KL20X or PIC24F04KL10X devices.

The data EEPROM is organized as 16-bit wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

#### 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle, and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

#### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

| //Disable Interrupts For 5 instr | uctions |

|----------------------------------|---------|

| asm volatile("disi #5");         |         |

| //Issue Unlock Sequence          |         |

| asm volatile ("mov #0x55, W0     | \n"     |

| "mov W0, NVMKEY                  | \n"     |

| "mov #0xAA, W1                   | \n"     |

| "mov W1, NVMKEY                  | \n");   |

| // Perform Write/Erase operation | S       |

| asm volatile ("bset NVMCON, #WR  | \n"     |

| "nop                             | \n"     |

| "nop                             | \n");   |

#### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

| R/W-0              | R-0, HSC                                                                                                                                                                                                                                                                           | U-0              | U-0            | U-0               | U-0              | U-0             | U-0    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-------------------|------------------|-----------------|--------|

| ALTIVT             | DISI                                                                                                                                                                                                                                                                               | —                | —              | —                 | —                | —               | —      |

| bit 15             |                                                                                                                                                                                                                                                                                    |                  |                |                   |                  |                 | bit 8  |

|                    |                                                                                                                                                                                                                                                                                    |                  |                |                   |                  |                 |        |

| U-0                | U-0                                                                                                                                                                                                                                                                                | U-0              | U-0            | U-0               | R/W-0            | R/W-0           | R/W-0  |

| —                  | _                                                                                                                                                                                                                                                                                  | —                |                |                   | INT2EP           | INT1EP          | INT0EP |

| bit 7              |                                                                                                                                                                                                                                                                                    |                  |                |                   |                  |                 | bit 0  |

|                    |                                                                                                                                                                                                                                                                                    |                  |                |                   |                  |                 |        |

| Legend:            |                                                                                                                                                                                                                                                                                    | HSC = Hardwa     | are Settable/C | learable bit      |                  |                 |        |

| R = Readable       | e bit                                                                                                                                                                                                                                                                              | W = Writable b   | bit            | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value at      | POR                                                                                                                                                                                                                                                                                | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

| bit 14<br>bit 13-3 | <ul> <li>1 = Uses Alternate Interrupt Vector Table</li> <li>0 = Uses standard (default) vector table</li> <li>DISI: DISI Instruction Status bit</li> <li>1 = DISI instruction is active</li> <li>0 = DISI instruction is not active</li> <li>Unimplemented: Read as '0'</li> </ul> |                  |                |                   |                  |                 |        |

| bit 2<br>bit 1     | <pre>INT2EP: External Interrupt 2 Edge Detect Polarity Select bit 1 = Interrupt on negative edge 0 = Interrupt on positive edge INT1EP: External Interrupt 1 Edge Detect Polarity Select bit 1 = Interrupt on negative edge 0 = Interrupt on negative edge</pre>                   |                  |                |                   |                  |                 |        |

| bit 0              | <ul> <li>a Interrupt on positive edge</li> <li>INTOEP: External Interrupt 0 Edge Detect Polarity Select bit</li> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul>                                                                             |                  |                |                   |                  |                 |        |

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER2

#### REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0          | R/W-1                   | R/W-0                                                   | R/W-0            | U-0              | U-0             | U-0                | U-0   |

|--------------|-------------------------|---------------------------------------------------------|------------------|------------------|-----------------|--------------------|-------|

| _            | U1RXIP2                 | U1RXIP1                                                 | U1RXIP0          |                  | _               | _                  |       |

| bit 15       |                         |                                                         | L                |                  | l               |                    | bit 8 |

|              |                         |                                                         |                  |                  |                 |                    |       |

| U-0          | U-0                     | U-0                                                     | U-0              | U-0              | R/W-1           | R/W-0              | R/W-0 |

| _            | —                       | —                                                       | —                | _                | T3IP2           | T3IP1              | T3IP0 |

| bit 7        |                         |                                                         | •                |                  |                 |                    | bit 0 |

|              |                         |                                                         |                  |                  |                 |                    |       |

| Legend:      |                         |                                                         |                  |                  |                 |                    |       |

| R = Readab   | le bit                  | W = Writable                                            | bit              | U = Unimpler     | nented bit, rea | d as '0'           |       |

| -n = Value a | t POR                   | '1' = Bit is set                                        |                  | '0' = Bit is cle | ared            | x = Bit is unknown |       |

| bit 14-12    |                         | >: UART1 Rece<br>pt is Priority 7 (<br>pt is Priority 1 | •                |                  |                 |                    |       |

|              | 000 = Interru           | pt source is dis                                        |                  |                  |                 |                    |       |

| bit 11-3     | •                       | ted: Read as '                                          |                  |                  |                 |                    |       |

| bit 2-0      | T3IP<2:0>: ⊺            | imer3 Interrupt                                         | Priority bits    |                  |                 |                    |       |

|              | 111 = Interru<br>•<br>• | pt is Priority 7(                                       | highest priority | interrupt)       |                 |                    |       |

|              | •                       |                                                         |                  |                  |                 |                    |       |

#### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC oscillator. OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step-size is an approximation and is neither characterized nor tested.

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <b><sup>(2)</sup></b> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|--------------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                           | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                                |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit |                            |                    |

|----------------------------|---------------------------------------|----------------------------|--------------------|

| HS = Hardware Settable bit | CO = Clearable Only bit               | SO = Settable Only bit     |                    |

| R = Readable bit           | W = Writable bit                      | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR          | '1' = Bit is set                      | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15 Unimplemented: Read as '0'

#### bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

- bit 11 Unimplemented: Read as '0'

#### bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(1)</sup>

- 111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)

- 110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (SOSC)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)

- 010 = Primary Oscillator (XT, HS, EC)

- 001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)

- 000 = 8 MHz FRC Oscillator (FRC)

#### **Note 1:** Reset values for these bits are determined by the FNOSC<2:0> Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

- **3:** When SOSC is selected to run from a digital clock input rather than an external crystal (SOSCSRC = 0), this bit has no effect.

#### 11.3 Input Change Notification

The Input Change Notification (ICN) function of the I/O ports allows the PIC24F16KL402 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 23 external signals that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the Change Notification (CN) module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately, using the CNPD1 and CNPD2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to VSS by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

**Note:** Pull-ups and pull-downs on Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE (ASSEMBLY LANGUAGE)

| MOV  | #0xFF00, W0 | ; Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|------|-------------|-------------------------------------------------------------|

| MOV  | W0, TRISB   |                                                             |

| MOV  | #0x00FF, W0 | ; Enable PORTB<15:8> digital input buffers                  |

| MOV  | W0, ANSB    |                                                             |

| NOP  |             | ; Delay 1 cycle                                             |

| BTSS | PORTB, #13  | ; Next Instruction                                          |

|      |             |                                                             |

#### EXAMPLE 11-2: PORT WRITE/READ EXAMPLE (C LANGUAGE)

| TRISB = 0xFF00;          | // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|--------------------------|--------------------------------------------------------------|

| ANSB = $0 \times 00 FF;$ | // Enable PORTB<15:8> digital input buffers                  |

| NOP();                   | // Delay 1 cycle                                             |

| if(PORTBbits.RB13 == 1)  | // execute following code if PORTB pin 13 is set.            |

| {                        |                                                              |

| }                        |                                                              |

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                     | U-0                                                                                     | U-0                                                | U-0                                       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|

| _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                         | <u> </u>                                                                                |                                                    | —                                         |

| bit 15       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    | bit 8                                     |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    |                                           |

| U-0          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                   | R/W-0                                                                                   | R/W-0                                              | R/W-0                                     |

|              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DCxB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DCxB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CCPxM3 <sup>(1)</sup>                                                                                                                   | CCPxM2 <sup>(1)</sup>                                                                   | CCPxM1 <sup>(1)</sup>                              | CCPxM0 <sup>(1)</sup>                     |

| bit 7        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    | bit (                                     |

| Legend:      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |                                                                                         |                                                    |                                           |

| R = Readal   | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U = Unimplem                                                                                                                            | nented bit, read                                                                        | l as '0'                                           |                                           |